A Resistor-Network Model of Dickson Charge Pump Using Steady-State Analysis

Abstract

:1. Introduction

- Unlike the reported models, the RN model can describe the electrical characteristics of the DCP over the whole frequency range in the SSL and the FSL regions;

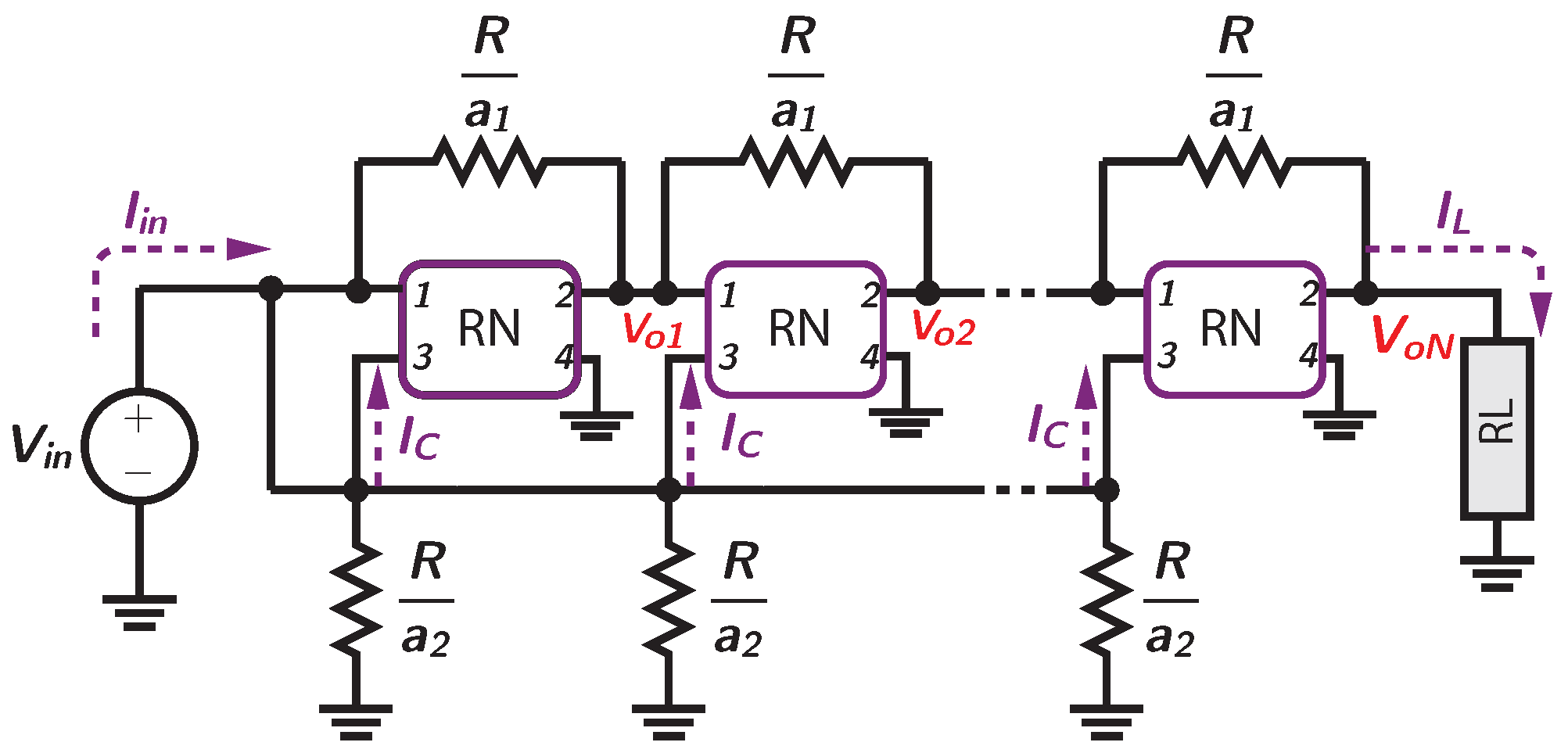

- Unlike the reported models, the proposed model provides access to clock levels, switching frequency, and internal nodes between charge pump stages by modeling each stage individually and then cascading them to model N-stage DCP. Thus, the proposed model assists with studying the voltages and currents for each stage as well as the losses caused by the parasitic capacitances. Further, the model helps with exploring the impact of the feedback network on the behavior of the DCP, including stage modulation for maximum power transfer, and pulse frequency modulation;

- Since the proposed model uses a linear resistive network, the computation speed is inevitably enhanced without extra complications;

- The proposed model highlights the effects of both top- and bottom-plate parasitic capacitances and how they impact the power performance and the maximum power transfer of the DCP over the entire frequency range.

2. RN Model Derivation and Analysis

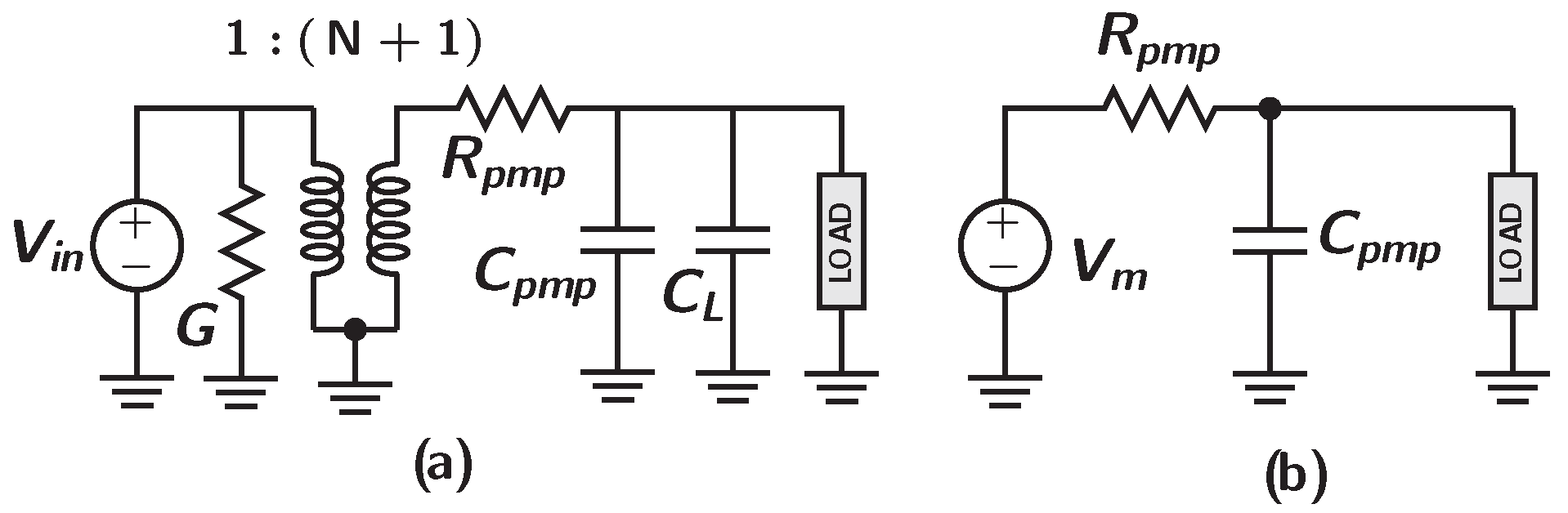

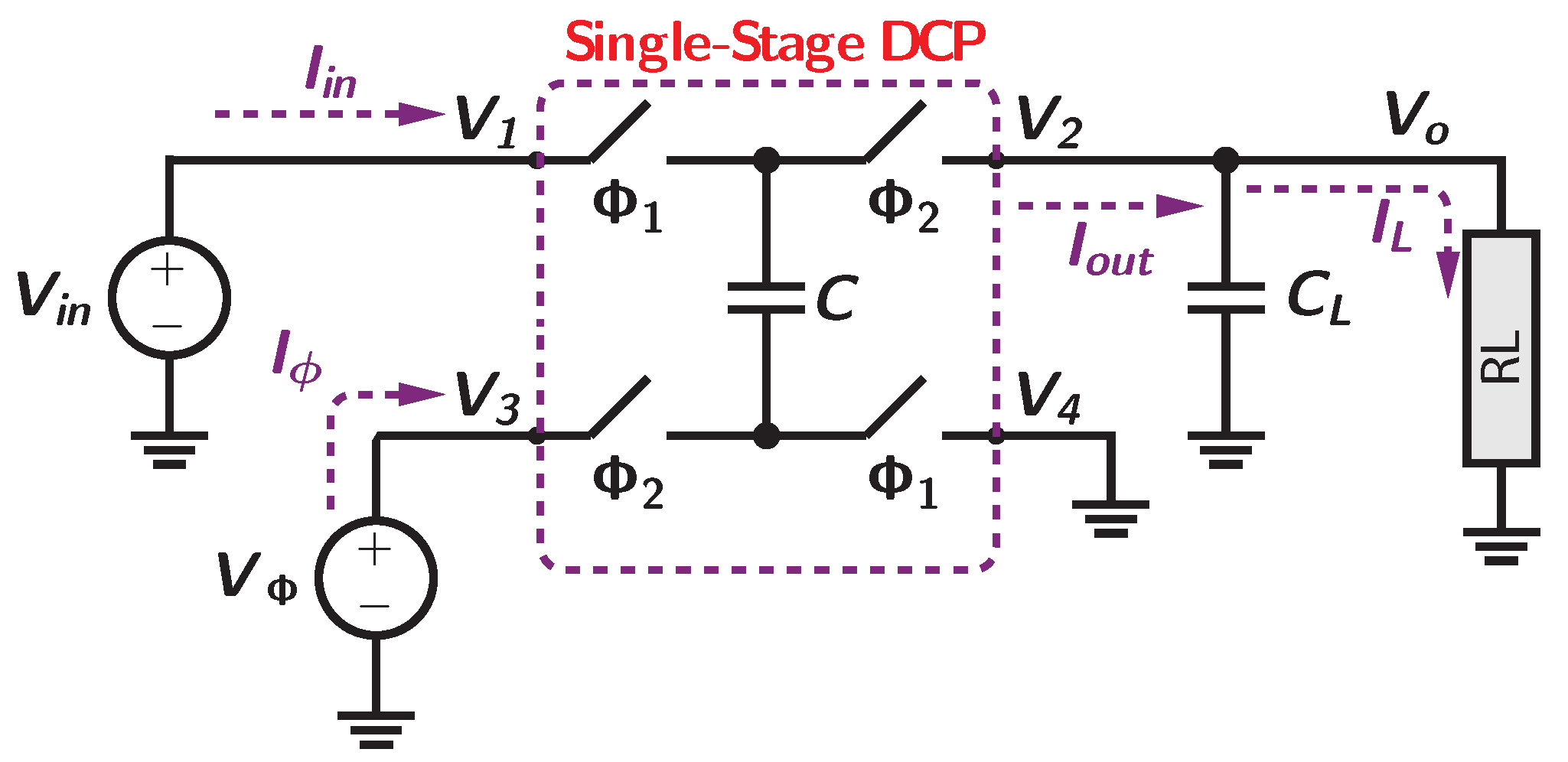

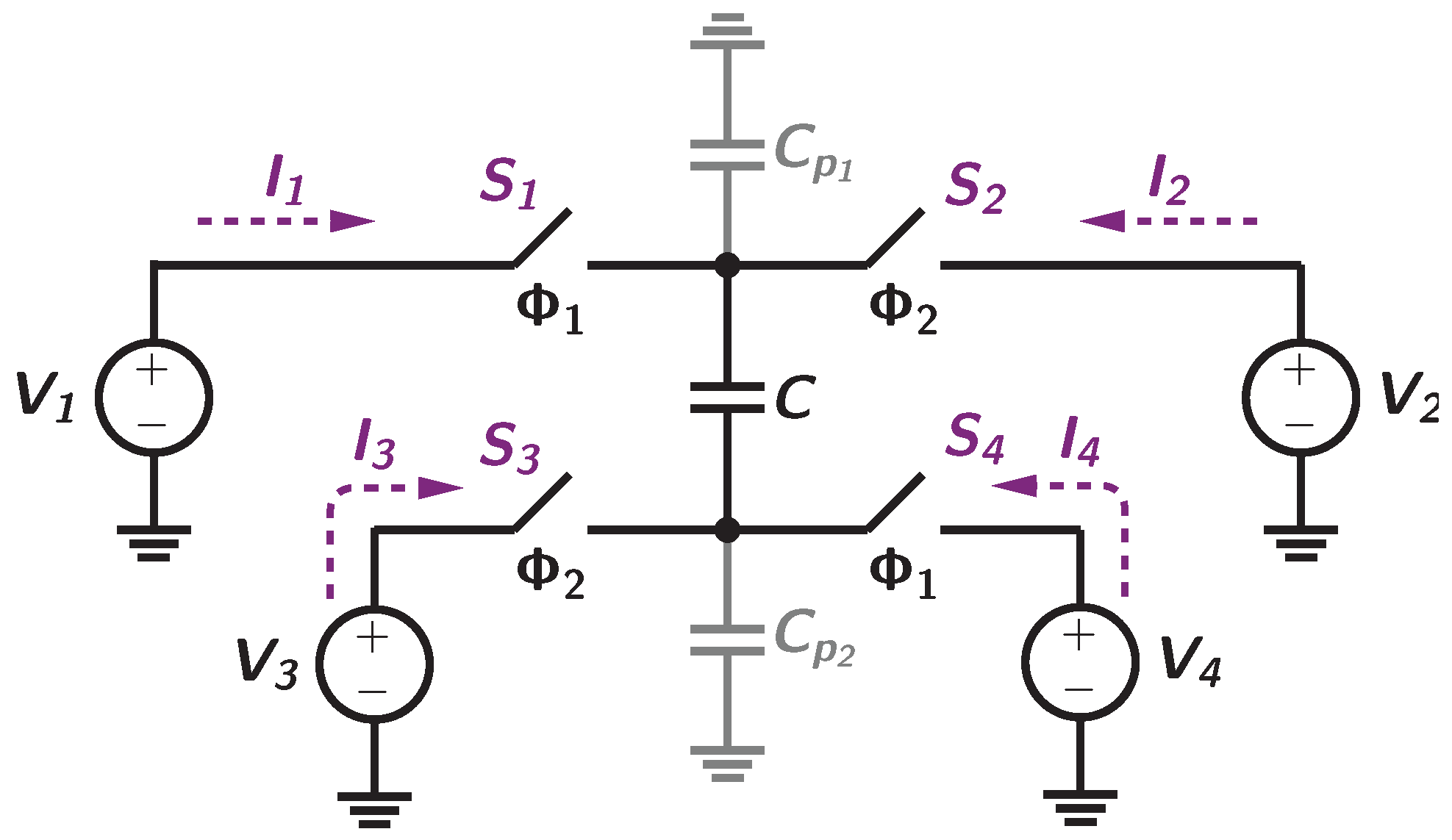

2.1. Single-Stage DCP Model Derivation

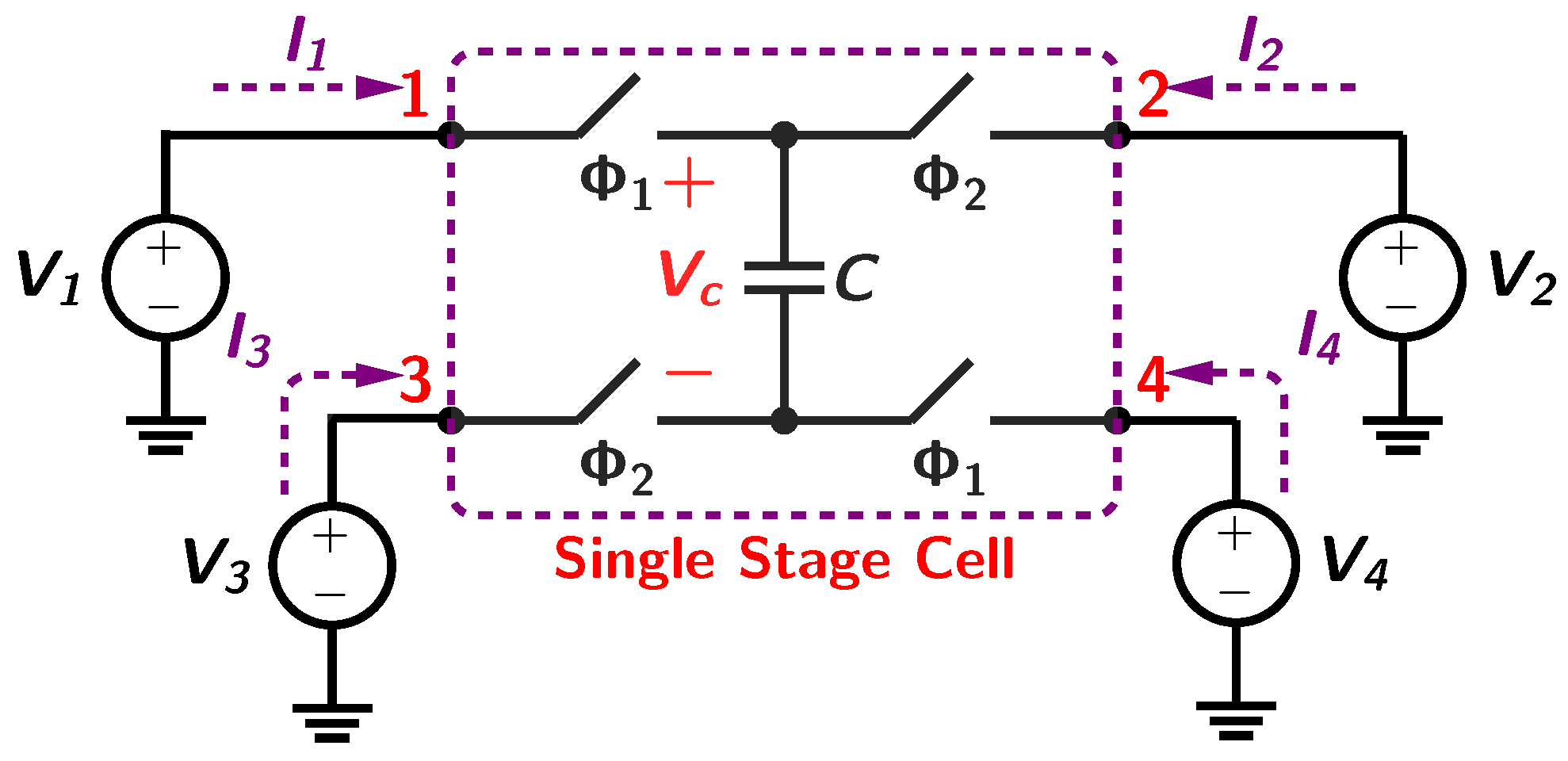

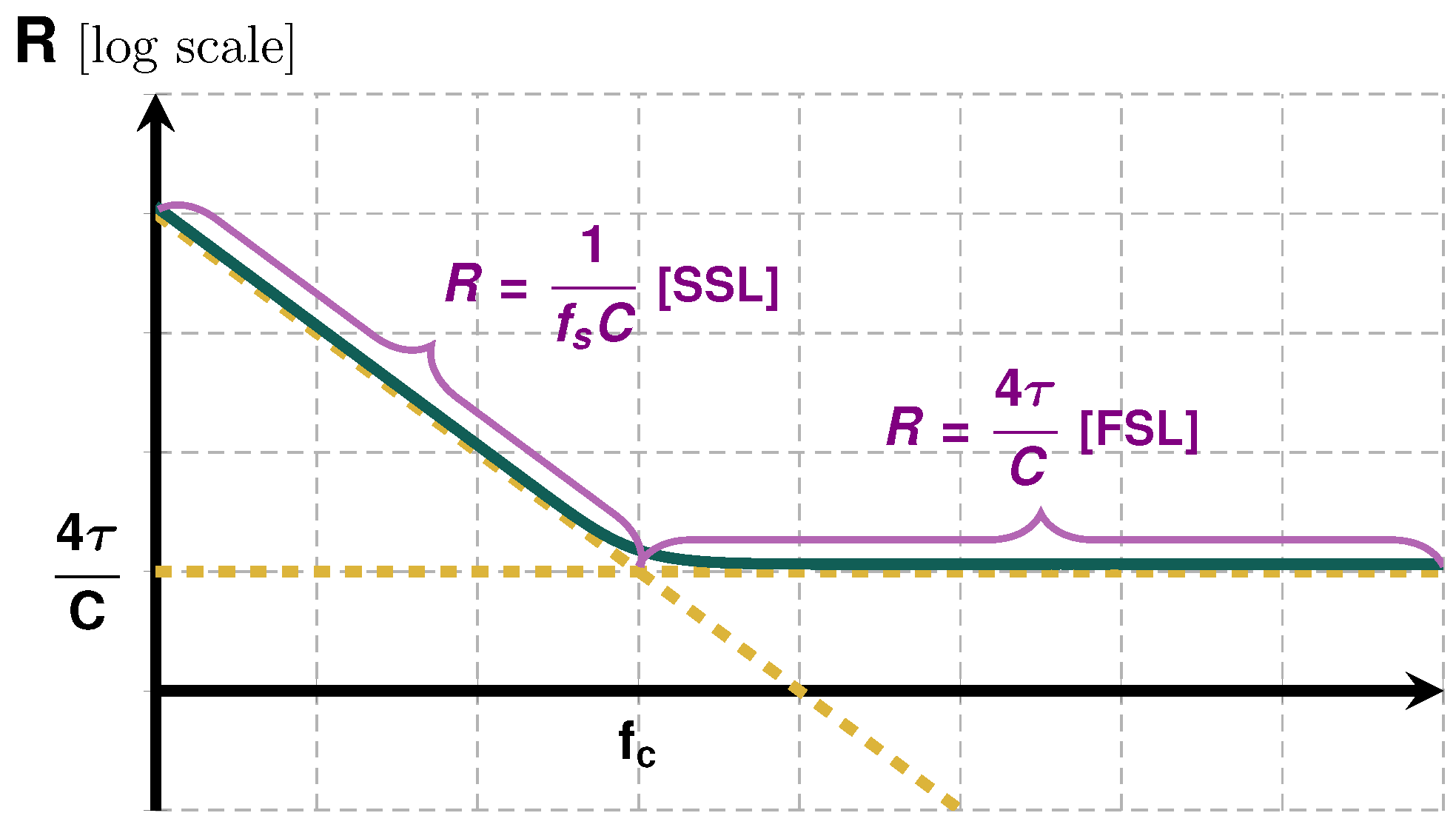

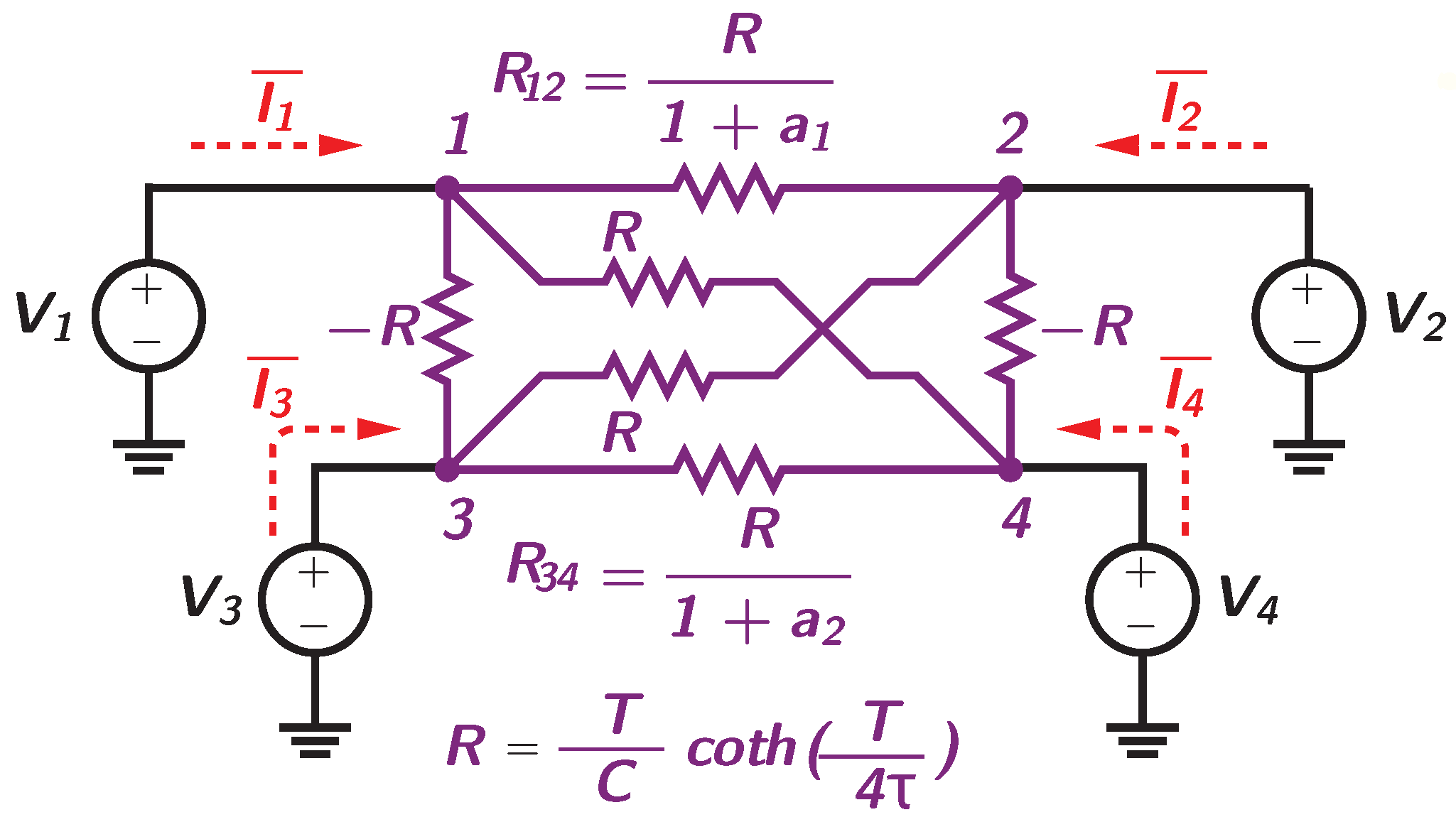

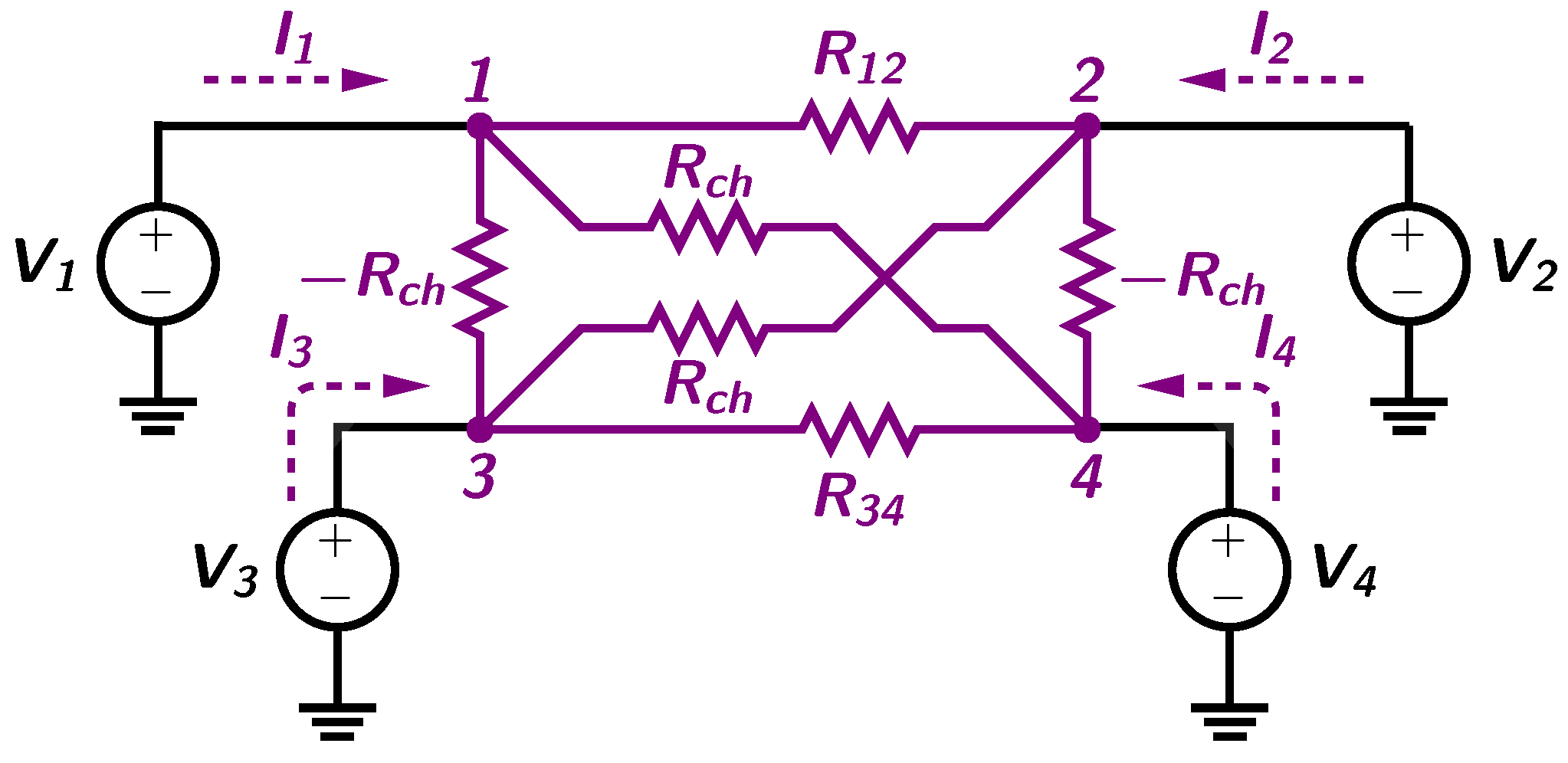

2.2. Proposed RN Model

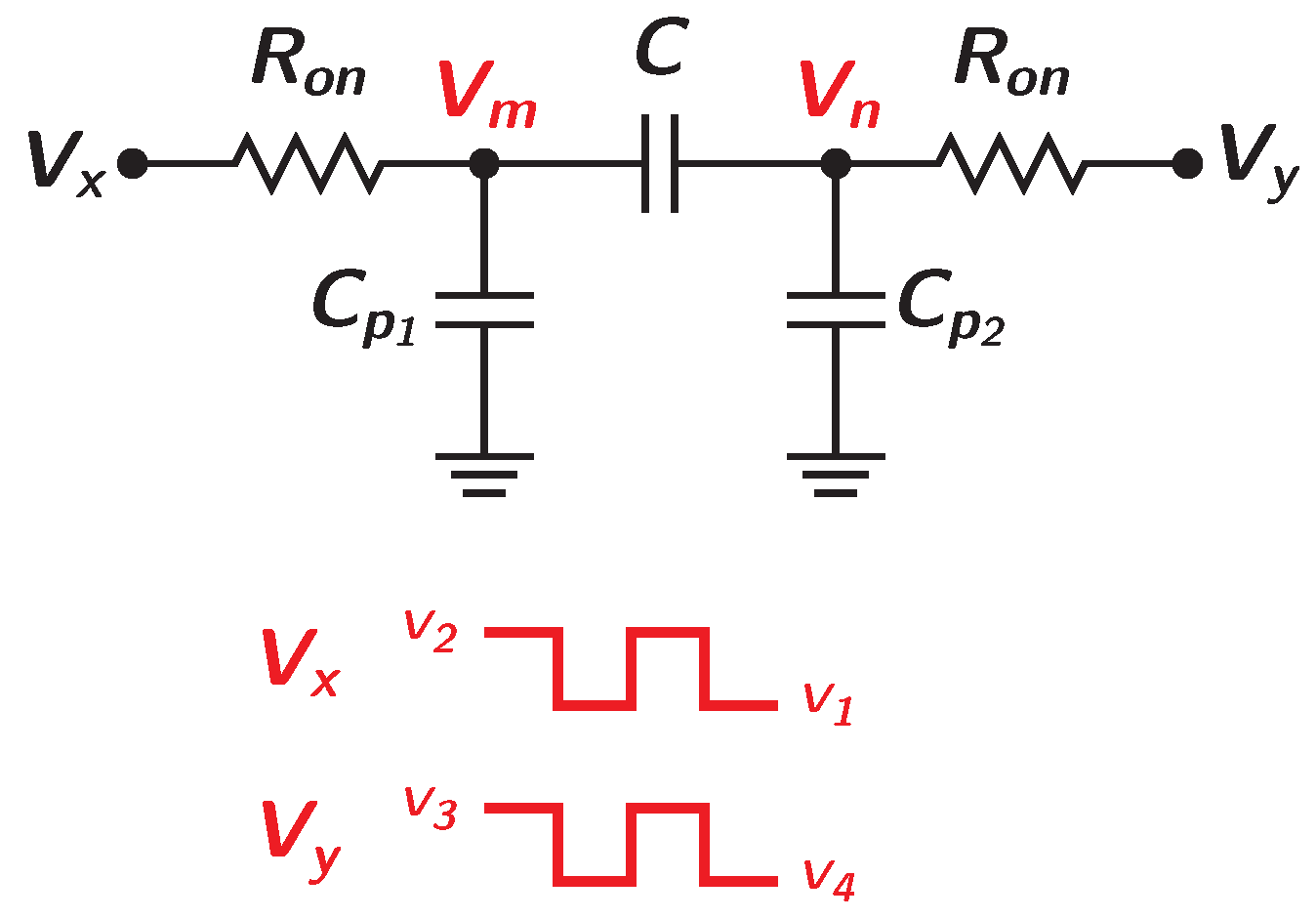

2.3. The Effect of Switch ON-Resistance ()

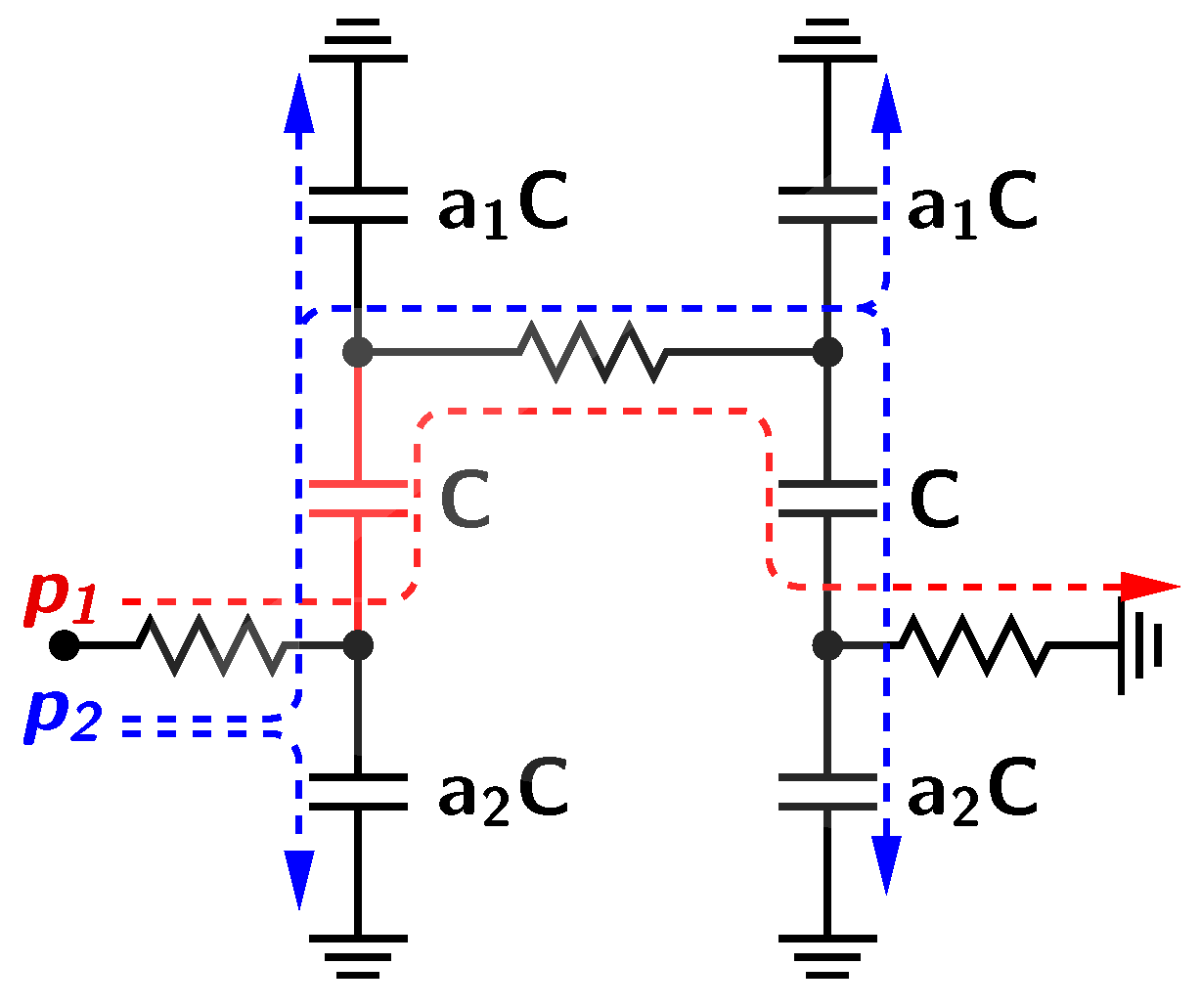

2.4. The Effect of Parasitic Capacitance ()

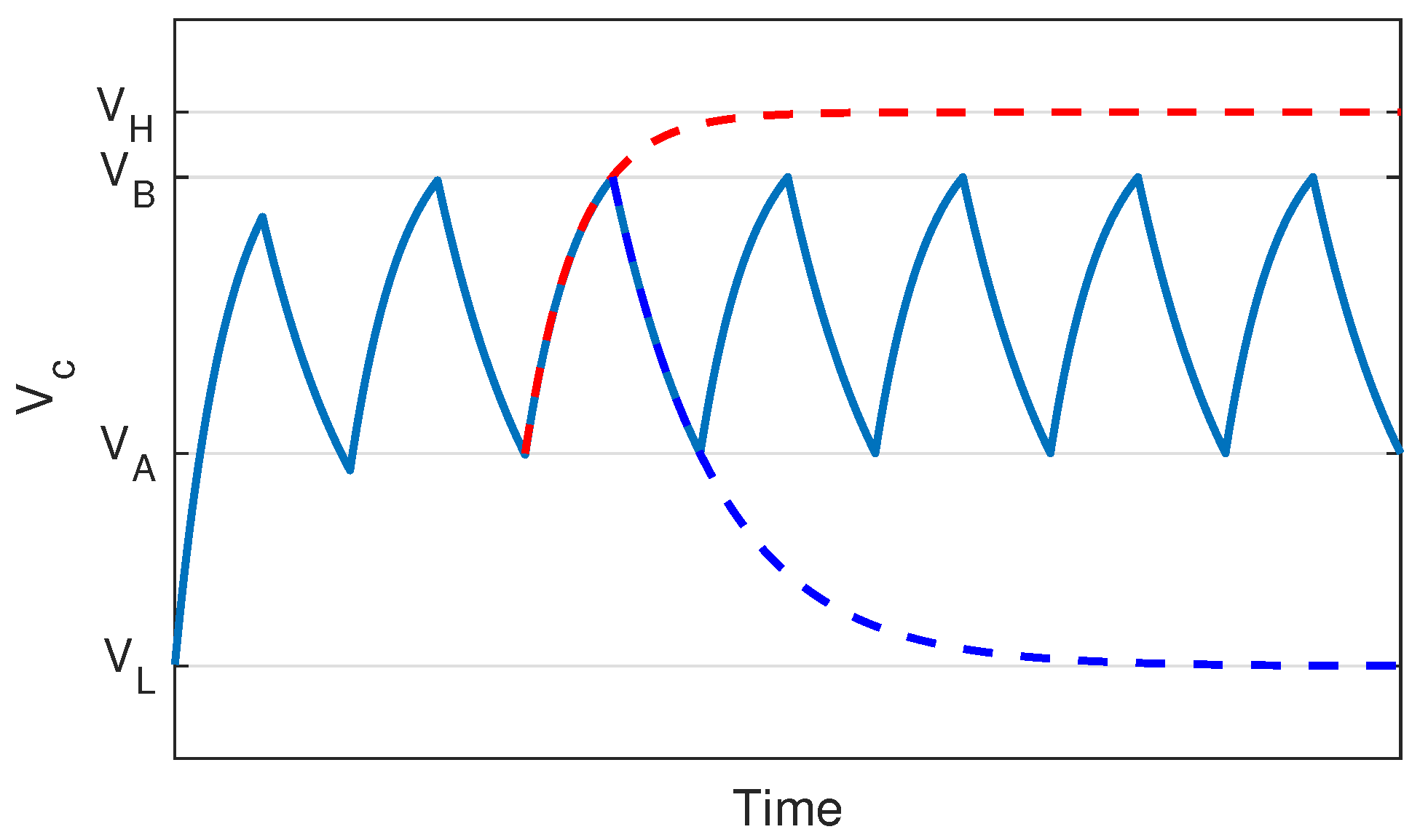

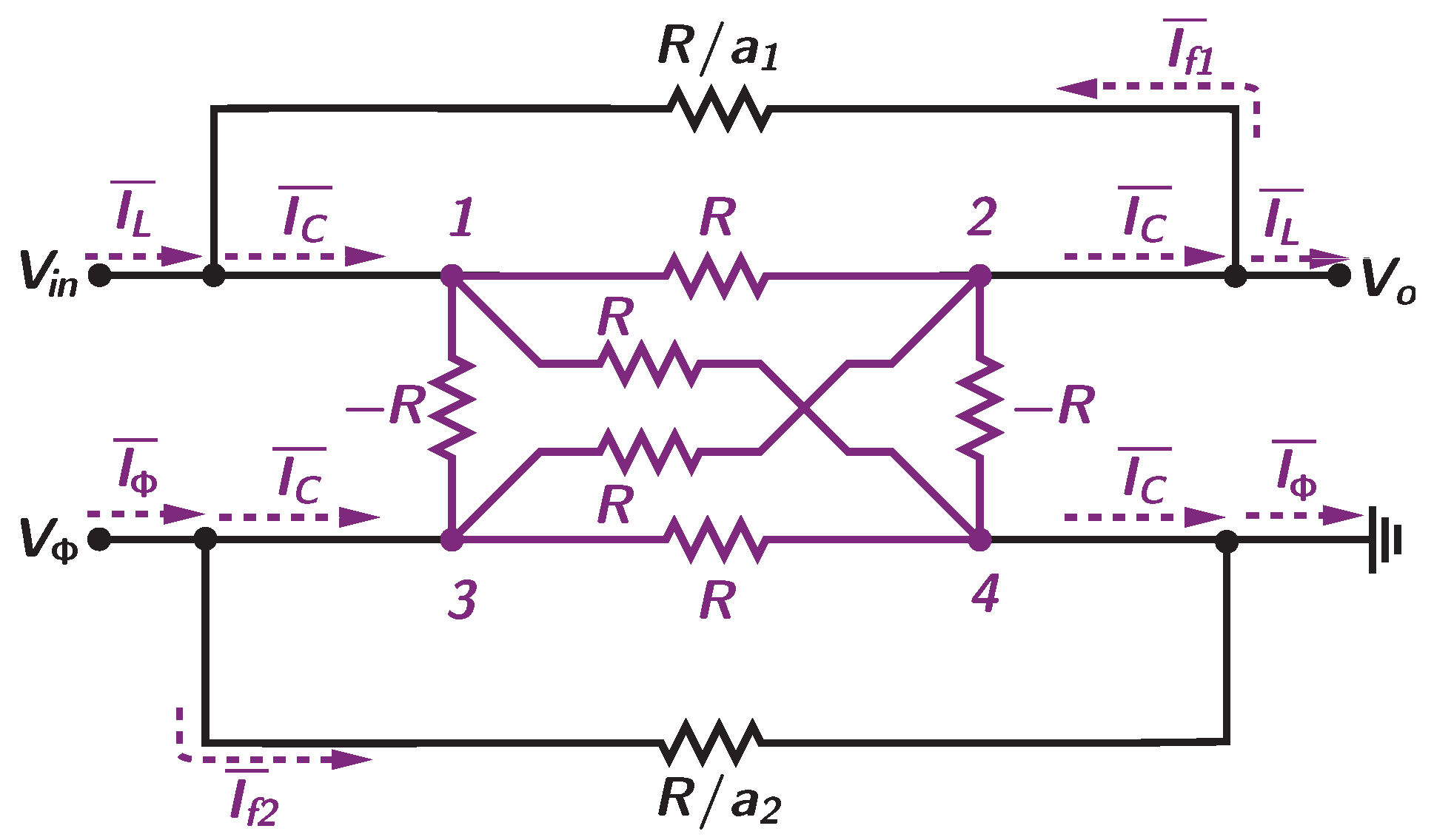

2.5. Maximum Power Transfer Methodologies

2.6. Generalization of RN Model

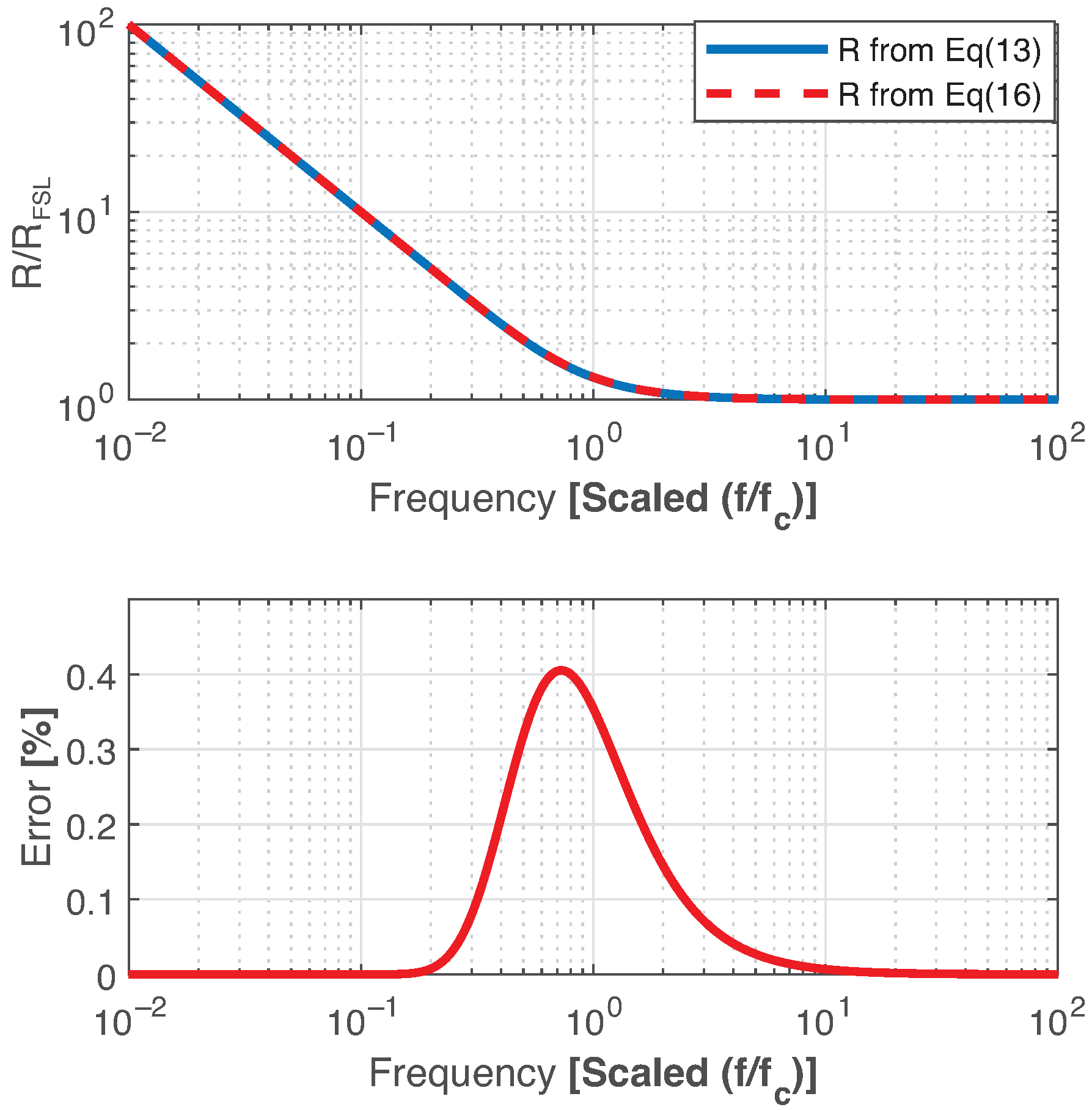

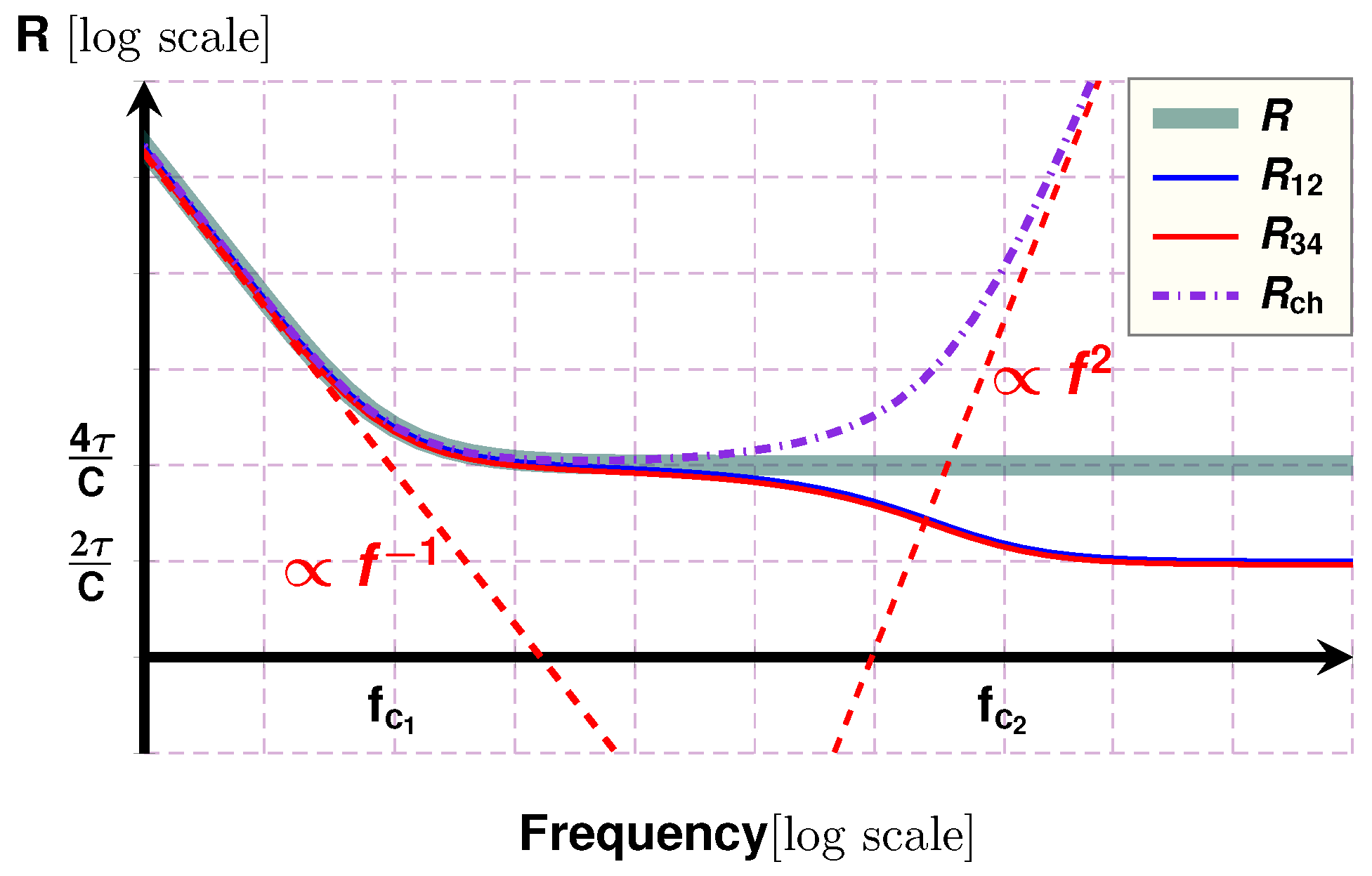

- The circuit in Figure 8 has two distinct real poles:Note that is much smaller than , and therefore, the second corner frequency, , is much larger than the first corner frequency, ;

- The resistor between terminals 1 and 2, , can be expressed as a combination of two parallel resistors , and :where:

- Similarly, the resistor between terminals 3 and 4, , is a combination of two parallel resistors ( and ):where:

- The other four resistors, denoted as in the RN-G model, can be calculated as:where:

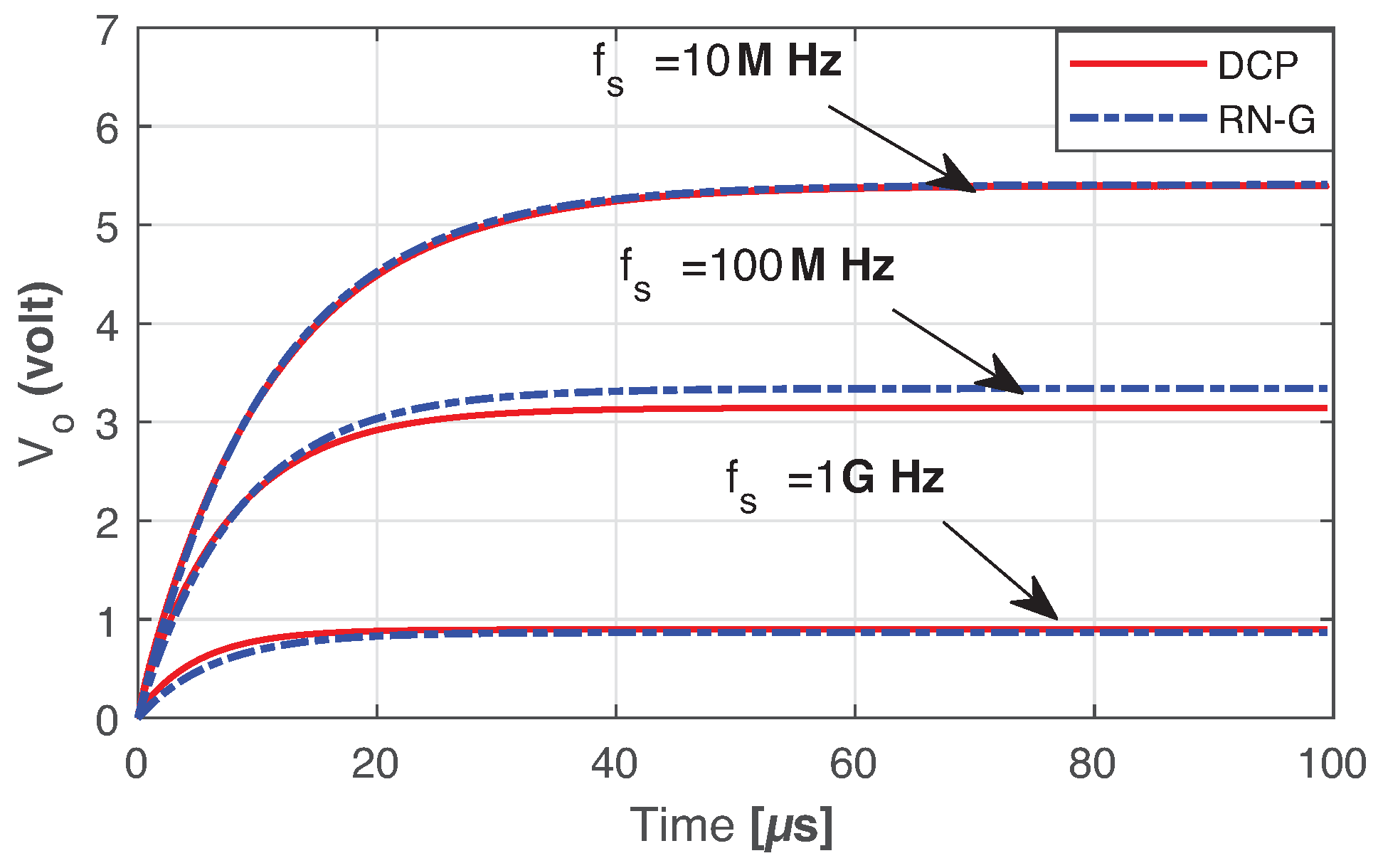

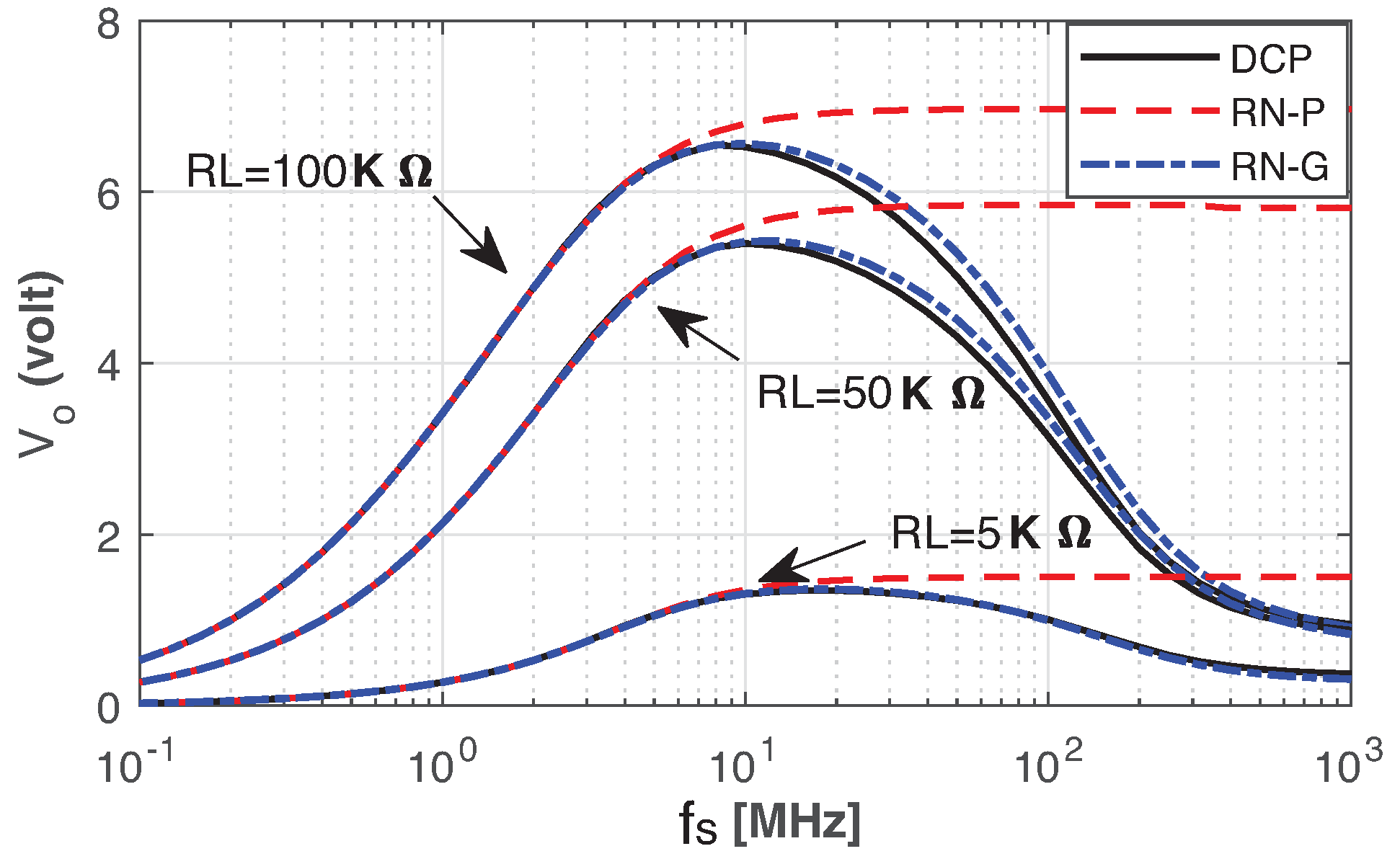

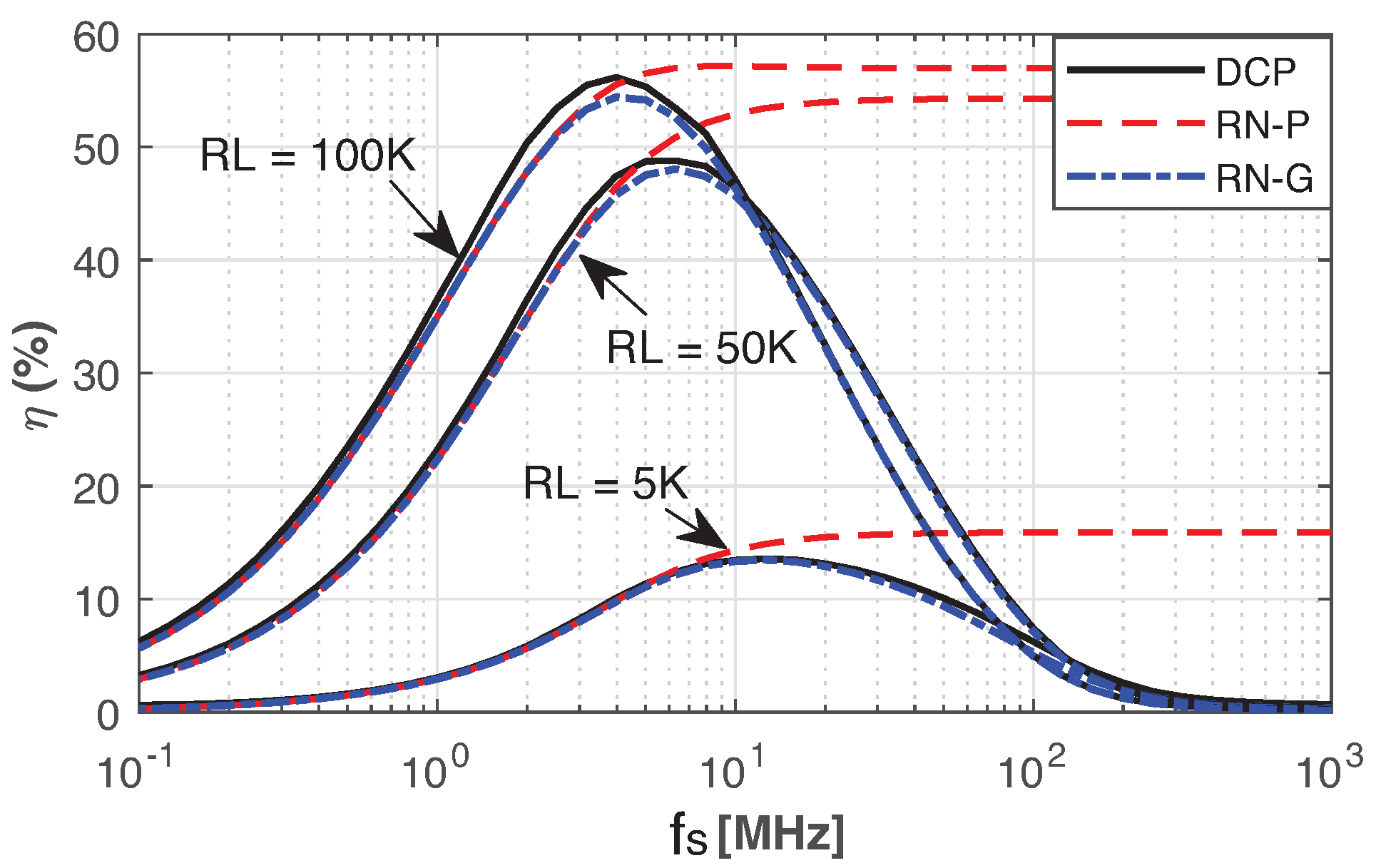

3. Simulation Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| Input voltage | |

| Clock high-voltage level | |

| Output voltage | |

| Voltage conversion ratio | |

| Charge pump output resistance | |

| Switches ON-resistance | |

| Equivalent output resistance | |

| Modeled resistance between i and j terminals | |

| C | Charge pump fly capacitor |

| Charge pump output capacitance | |

| Charge pump load capacitance | |

| Top- and bottom-plate capacitance | |

| R | Equivalent switching resistance |

| Average value of from () to () | |

| Corner frequency | |

| Switching frequency () | |

| Top and bottom parasitic ratios | |

| Charging and discharging time constants |

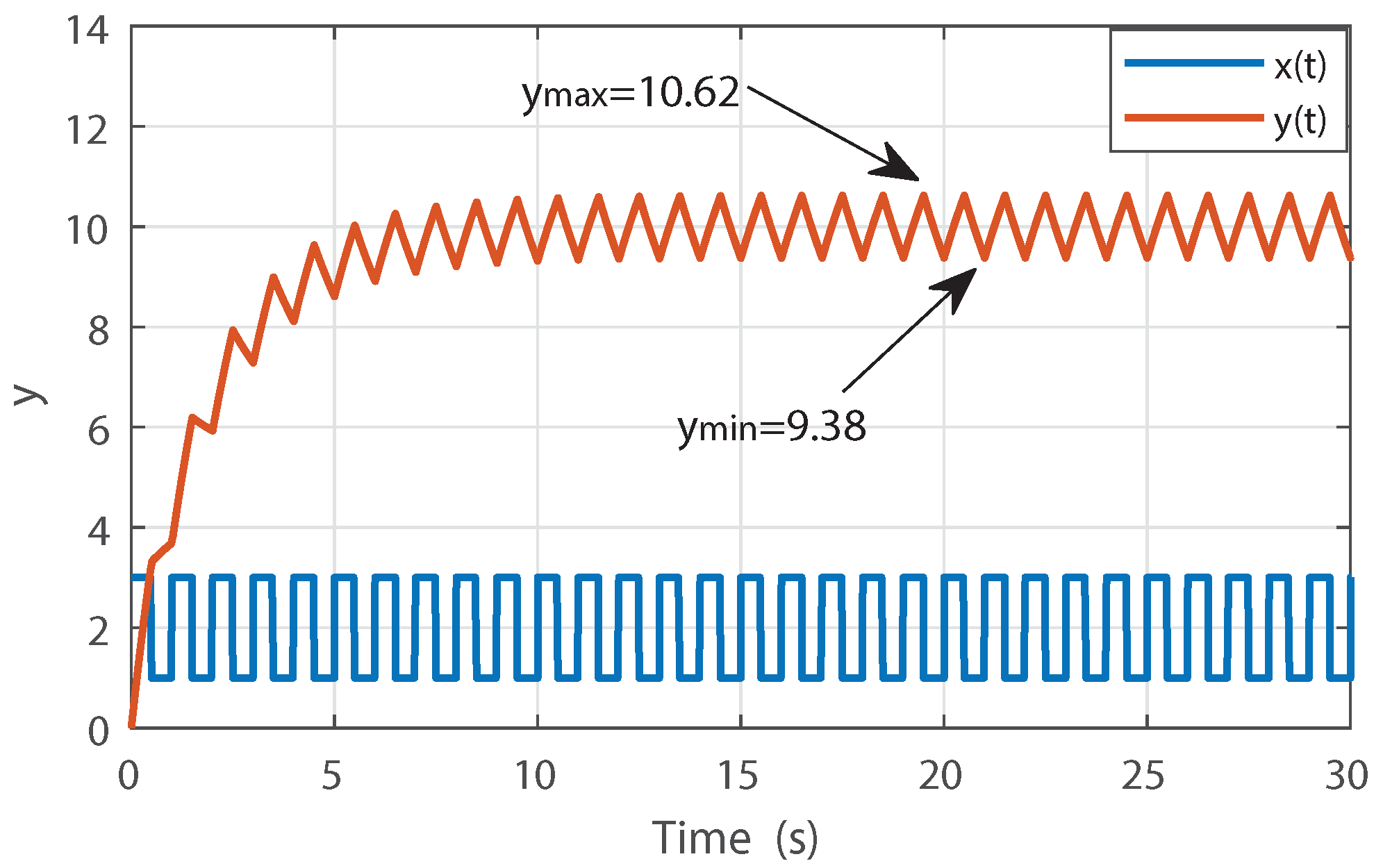

Appendix A. Square Wave Steady-State Response of Single-Pole LTI System

Appendix B. Analysis of Single-Stage CP with Non-Symmetric Charging and Discharging Schemes

Appendix C. Analysis of Ron and Cp Effects for the RN-G Model

- ;

- ;

- ;

- .

References

- Wong, O.; Wong, H.; Tam, W.; Kok, C. A comparative study of charge pumping circuits for flash memory applications. Microelectron. Reliab. 2012, 52, 670–687. [Google Scholar] [CrossRef]

- Mahmoud, A.; Alhawari, M.; Mohammad, B.; Saleh, H.; Ismail, M. A gain-controlled, low-leakage Dickson charge pump for energy-harvesting applications. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 1114–1123. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.; Palumbo, G. A Review of Charge Pump Topologies for the Power Management of IoT Nodes. Electronics 2019, 8, 480. [Google Scholar] [CrossRef] [Green Version]

- Chen, P.; Cheng, H.; Lo, C. A Single-Inductor Triple-Source Quad-Mode Energy-Harvesting Interface With Automatic Source Selection and Reversely Polarized Energy Recycling. IEEE J. Solid State Circuits 2019, 54, 2671–2679. [Google Scholar] [CrossRef]

- Alhawari, M.; Mohammad, B.; Saleh, H.; Ismail, M. An Efficient Polarity Detection Technique for Thermoelectric Harvester in L-based Converters. IEEE Trans. Circuits Syst. Regul. Pap. 2017, 64, 705–716. [Google Scholar] [CrossRef]

- Ma, D.; Bondade, R. Fundamental Charge Pump Topologies and Design Principles. In Reconfigurable Switched-Capacitor Power Converters; Springer: New York, NY, USA, 2013; ISBN 978-1-4614-4187-8. [Google Scholar]

- Seeman, M.; Sanders, S. Analysis and Optimization of Switched-Capacitor DC-DC Converters. IEEE Trans. Power Electron. 2008, 23, 841–851. [Google Scholar] [CrossRef]

- Ferro, E.; Brea, V.; Lopez, P.; Cabello, D. Dynamic Model of Switched-Capacitor DCDC Converters in the Slow-Switching Limit Including Charge Reusing. IEEE Trans. Power Electron. 2017, 32, 5293–5311. [Google Scholar] [CrossRef]

- Pasternak, S.; Kiani, M.; Rentmeister, J.; Stauth, J. Modeling and Performance Limits of Switched-Capacitor DC-DC Converters Capable of Resonant Operation With a Single Inductor. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1746–1760. [Google Scholar] [CrossRef]

- Tanzawa, T. Dickson charge pump circuit design with parasitic resistance in power lines. In Proceeding of the IEEE International Symposium on Circuits and Systems, Taipei, Taiwan, 24–27 May 2009; pp. 1763–1766. [Google Scholar]

- Erickson, R.; Maksimovic, D. Fundamentals of Power Electronics; Springer International Publishing: Cham, Switzerland, 2020. [Google Scholar]

- Hella, M.M.; Mercier, P. Power Management Integrated Circuits; CRC Press: Cham, Switzerland, 2016. [Google Scholar]

- Gregori, S.; Rotunno, R.E. z-Domain analysis of Dickson charge pumps. In Proceeding of the IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, Monaco, 11–14 December 2016; pp. 185–188. [Google Scholar]

- Ballo, A.; Bottaro, M.; Grasso, A.D.; Palumbo, G. A General Behavioral Model of Charge Pump DC-DC converters. In Proceeding of the International Conference on Electrical, Communication, and Computer Engineering (ICECCE), Istanbul, Turkey, 12–13 June 2020; pp. 1–4. [Google Scholar]

- Ballo, A.; Grasso, A.D.; Palumbo, G.; Tanzawa, T. Charge Pumps for Ultra-Low-Power Applications: Analysis, Design, and New Solutions. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2895–2901. [Google Scholar] [CrossRef]

- Ballo, A.; Bottaro, M.; Grasso, A.D.; Palumbo, G. Regulated Charge Pumps: A Comparative Study by Means of Verilog-AMS. Electronics 2020, 9, 998. [Google Scholar] [CrossRef]

- Tanzawa, T. On-chip High-Voltage Generator Design; Springer International Publishing: Cham, Switzerland, 2016. [Google Scholar]

- Tanzawa, T. A Switch-Resistance-Aware Dickson Charge Pump Model for Optimizing Clock Frequency. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 336–340. [Google Scholar] [CrossRef]

- Tanzawa, T. A Behavior Model of a Dickson Charge Pump Circuit for Designing a Multiple Charge Pump System Distributed in LSIs. IEEE Trans. Circuits Syst. Express Briefs 2010, 57, 527–530. [Google Scholar] [CrossRef]

- Tan, Y.; Ishikuro, H. A Discrete-Time Model for Frequency Modulated Charge Pumps with Synchronized Controller. In Proceeding of the IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Springfield, MA, USA, 9–12 August 2020; pp. 929–932. [Google Scholar]

- Ma, D.; Bondade, R. Switched-Capacitor Power Converter Design and Modeling in z-Domain. In Reconfigurable Switched-Capacitor Power Converters; Springer: New York, NY, USA, 2013; ISBN 978-1-4614-4187-8. [Google Scholar]

- Cabrini, A.; Gobbi, L.; Torelli, G. Theoretical and Experimental Analysis of Dickson Charge Pump Output Resistance. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems, Island of Kos, Greece, 21–24 May 2006; p. 4. [Google Scholar] [CrossRef]

- Tanzawa, T. A Behavior Model of an On-Chip High Voltage Generator for Fast, System-Level Simulation. IEEE Trans. Very Large Scale Integr. Syst. 2012, 20, 2351–2355. [Google Scholar] [CrossRef]

- Karagozler, M.E.; Goldstein, S.C.; Ricketts, D.S. Analysis and Modeling of Capacitive Power Transfer in Microsystems. IEEE Trans. Circuits Syst. Regul. Pap. 2012, 59, 1557–1566. [Google Scholar] [CrossRef] [Green Version]

- Sommariva, A. Solving the two capacitor paradox through a new asymptotic approach. IEEE Proc. Circuits Devices Syst. 2003, 150, 227. [Google Scholar] [CrossRef]

- Tanzawa, T. On the Output Impedance and an Output Current–Power Efficiency Relationship of Dickson Charge Pump Circuits. IEEE Trans. Circuits Syst. II 2018, 65, 1664–1667. [Google Scholar] [CrossRef]

- Dickson, J.F. On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique. IEEE J. Solid State Circuits 1976, 11, 374–378. [Google Scholar] [CrossRef]

- Talkhooncheh, A.; Yu, Y.; Agarwal, A.; Kuo, W.; Chen, K.; Wang, M.; Hoskuldsdottir, G.; Gao, W.; Emami, A. A Biofuel-Cell-Based Energy Harvester With 86% Peak Efficiency and 0.25-V Minimum Input Voltage Using Source-Adaptive MPPT. IEEE J. Solid State Circuits 2021, 56, 715–728. [Google Scholar] [CrossRef]

- Aloqlah, A.S.; Alhawari, M. Demystifying Maximum Power Transfer Methodologies for Charge Pumps: An Analytical Approach. Proceeding of the IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, MI, USA, 9–11 August 2021; pp. 978–981. [Google Scholar]

- Liu, X.; Ravichandran, K.; Sanchez-Sinencio, E. A Switched Capacitor Energy Harvester Based on a Single-Cycle Criterion for MPPT to Eliminate Storage Capacitor. IEEE Trans. Circuits Syst. Regul. Pap. 2018, 65, 793–803. [Google Scholar] [CrossRef]

- Liu, X.; Huang, L.; Ravichandran, K.; Sanchez-Sinencio, E. A Highly Efficient Reconfigurable Charge Pump Energy Harvester With Wide Harvesting Range and Two-Dimensional MPPT for Internet of Things. IEEE J. Solid State Circuits 2016, 51, 1302–1312. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| N | 8 |

| 10 MHz | |

| C | 50 pF |

| 500 pF | |

| 5% | |

| 5% | |

| 500 | |

| 50 k | |

| 1 volt | |

| 50% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Aloqlah, A.S.; Alhawari, M. A Resistor-Network Model of Dickson Charge Pump Using Steady-State Analysis. Energies 2022, 15, 1899. https://doi.org/10.3390/en15051899

Aloqlah AS, Alhawari M. A Resistor-Network Model of Dickson Charge Pump Using Steady-State Analysis. Energies. 2022; 15(5):1899. https://doi.org/10.3390/en15051899

Chicago/Turabian StyleAloqlah, Abdullah S., and Mohammad Alhawari. 2022. "A Resistor-Network Model of Dickson Charge Pump Using Steady-State Analysis" Energies 15, no. 5: 1899. https://doi.org/10.3390/en15051899

APA StyleAloqlah, A. S., & Alhawari, M. (2022). A Resistor-Network Model of Dickson Charge Pump Using Steady-State Analysis. Energies, 15(5), 1899. https://doi.org/10.3390/en15051899