Open Circuit Fault Mitigation in a Nine-Level Modified Packed E-Cell Inverter

Abstract

1. Introduction

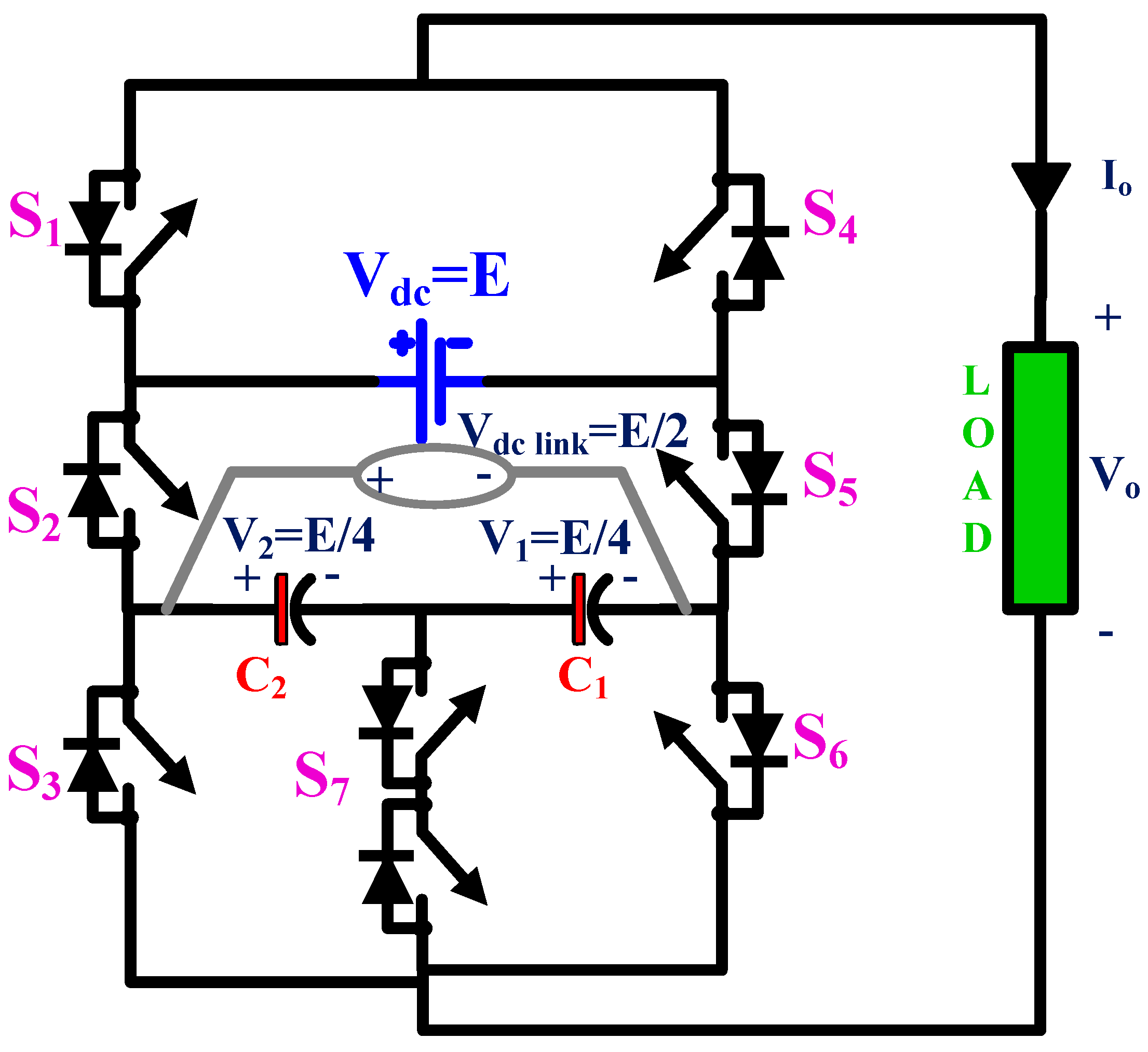

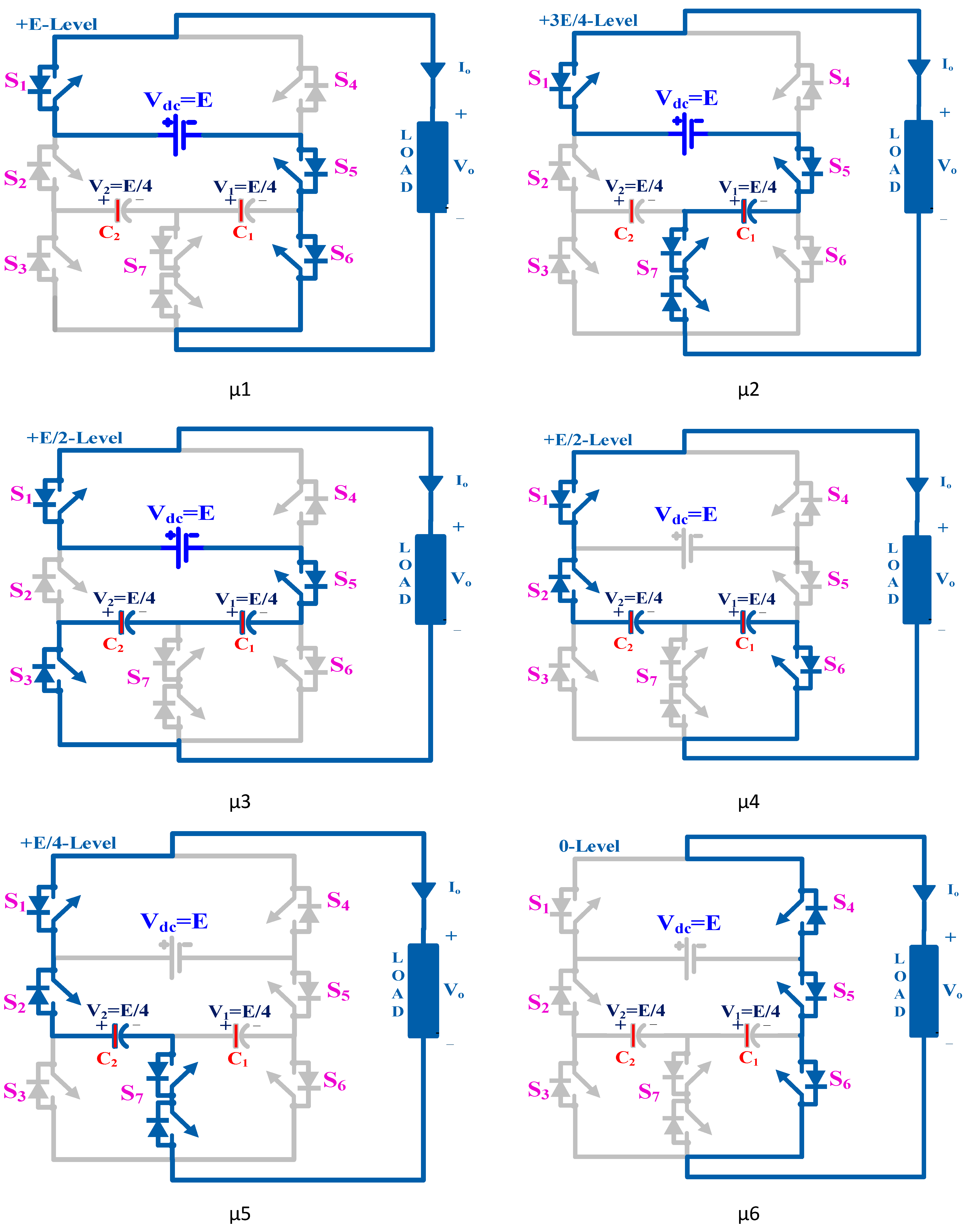

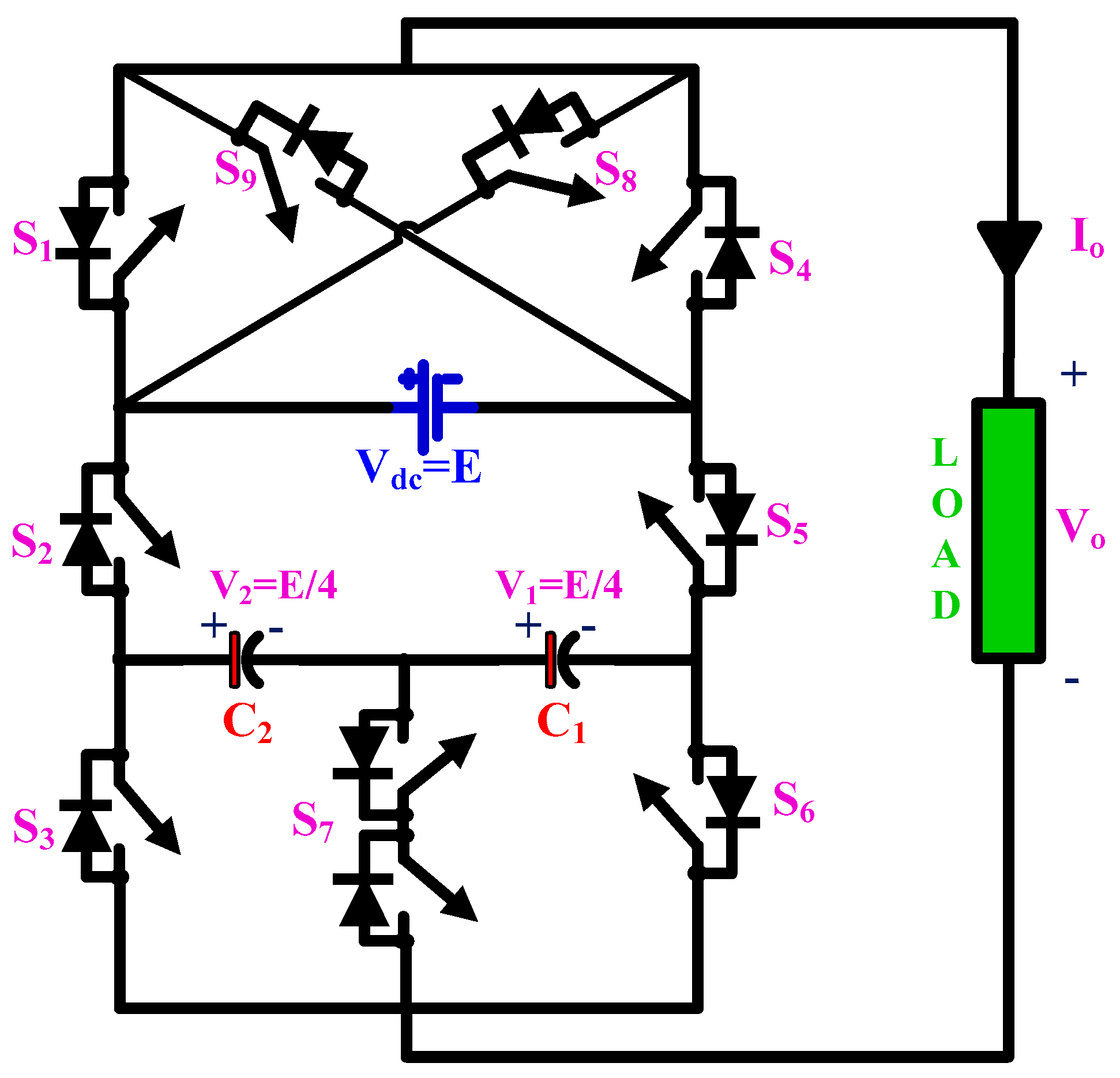

2. Existing Nine-Level MLI Topology

3. Modified Nine-Level PEC9 FT MLI

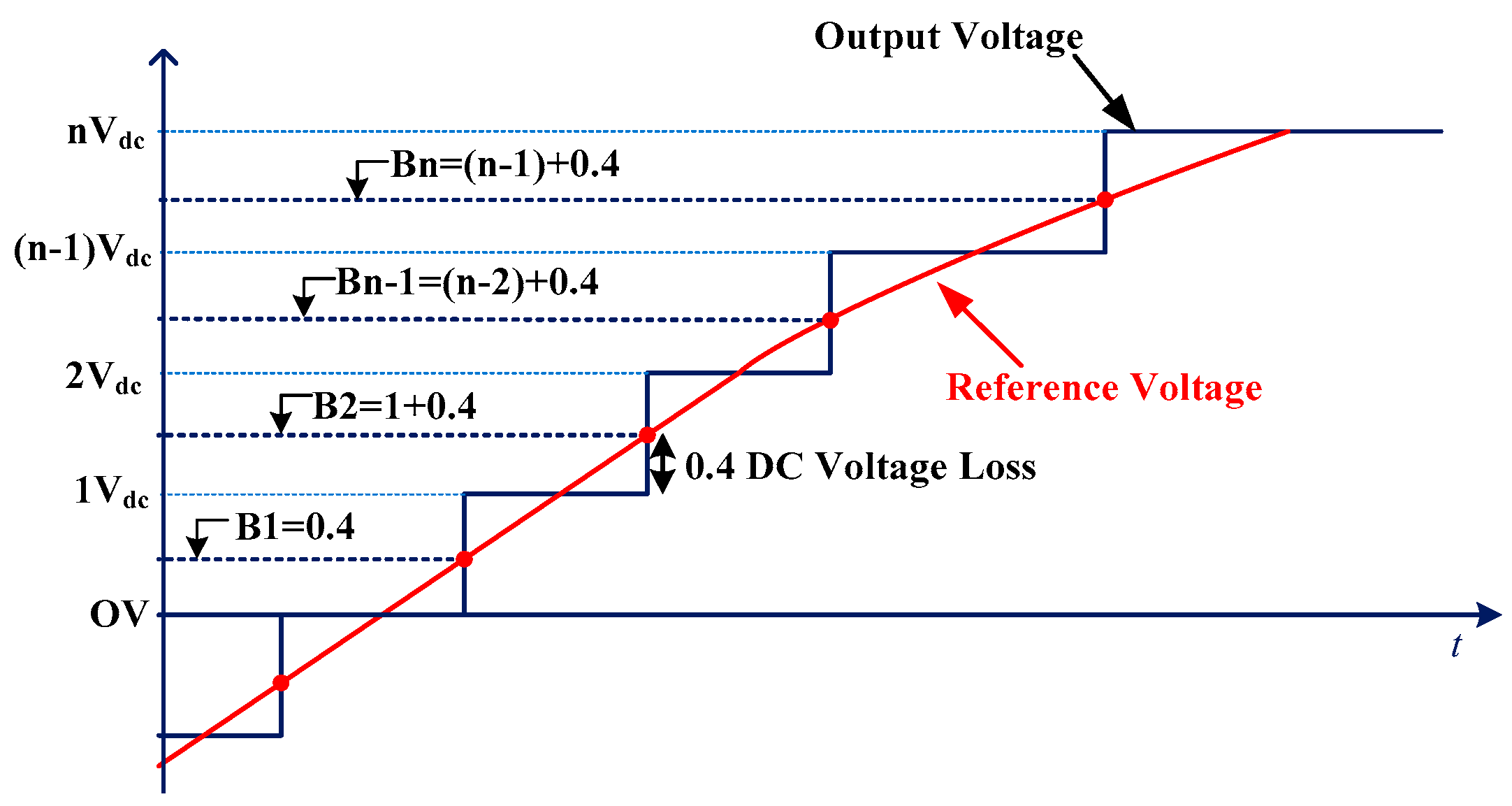

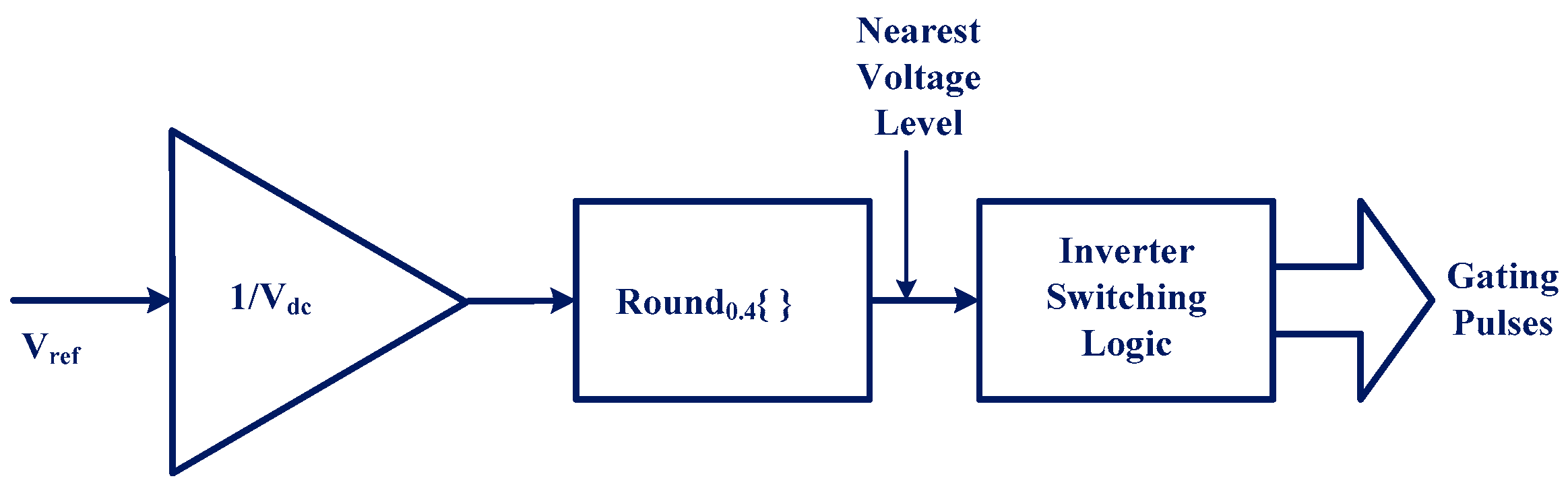

4. Modulation Strategy

| B1 | B2 | B3 | B4 | …… | Bn−1 | Bn |

| 0.4 | 1 + 0.4 | 2 + 0.4 | 3 + 0.4 | …… | (n − 2) + 0.4 | (n − 1) + 0.4 |

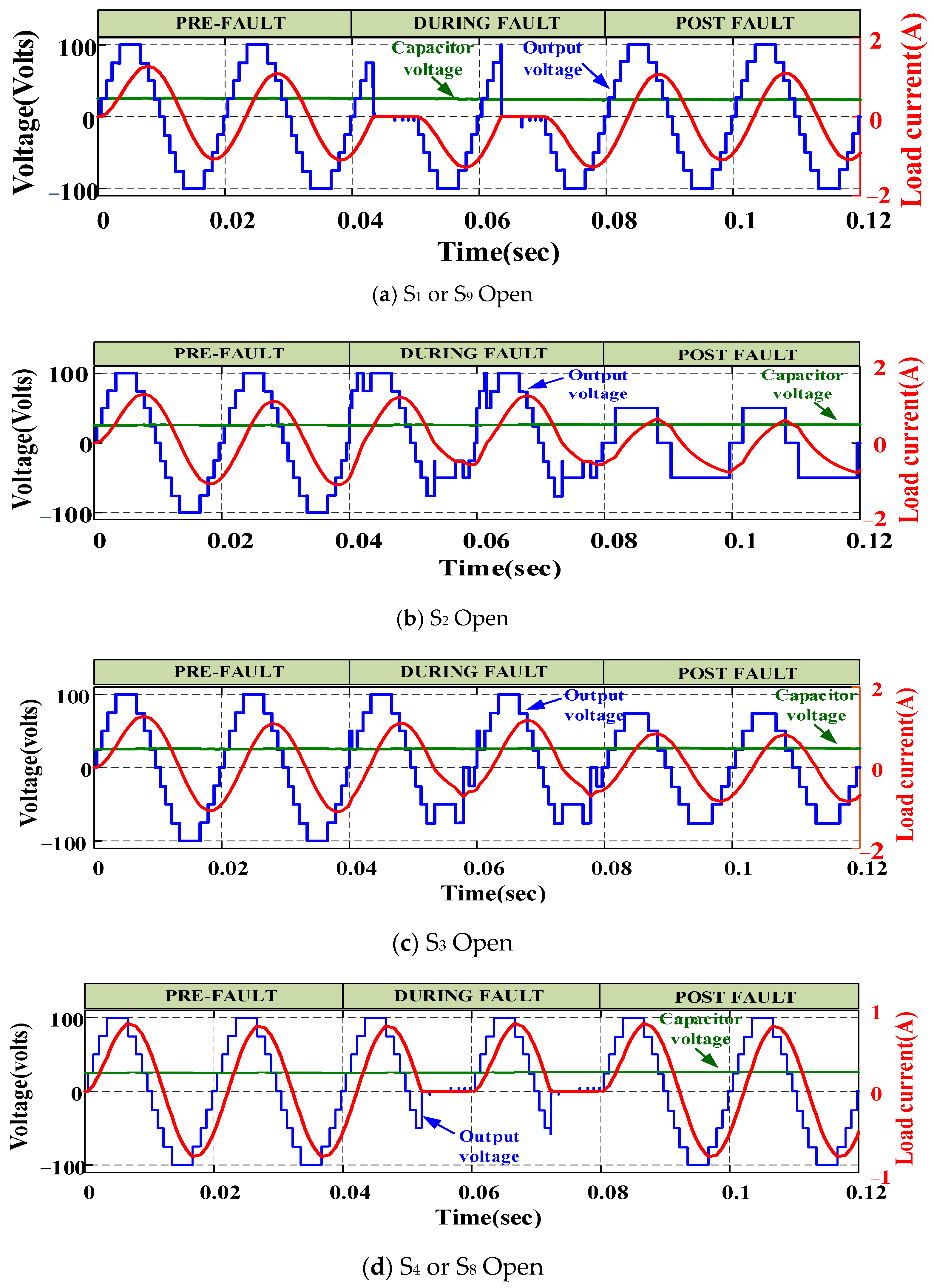

5. Results and Discussion

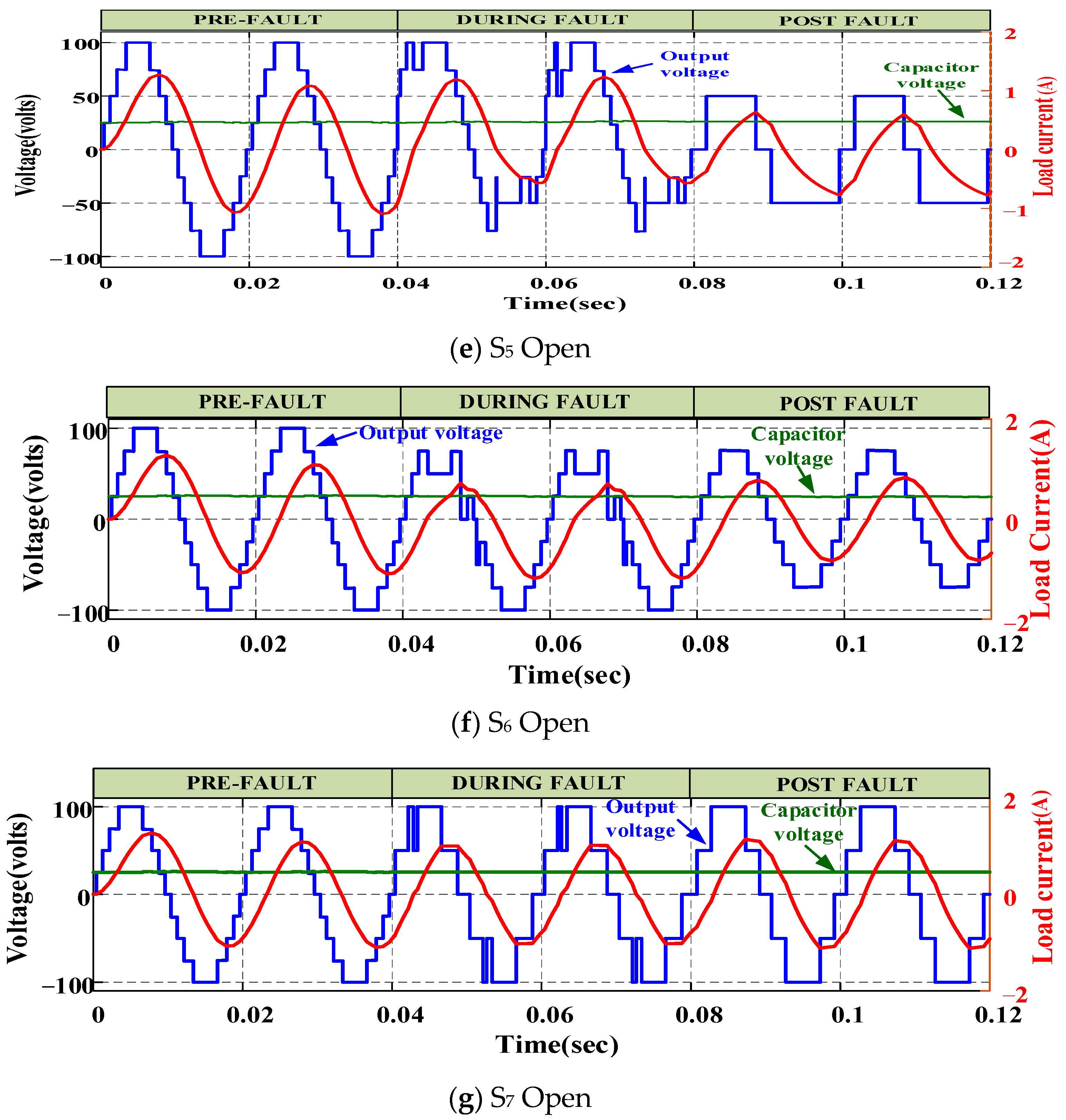

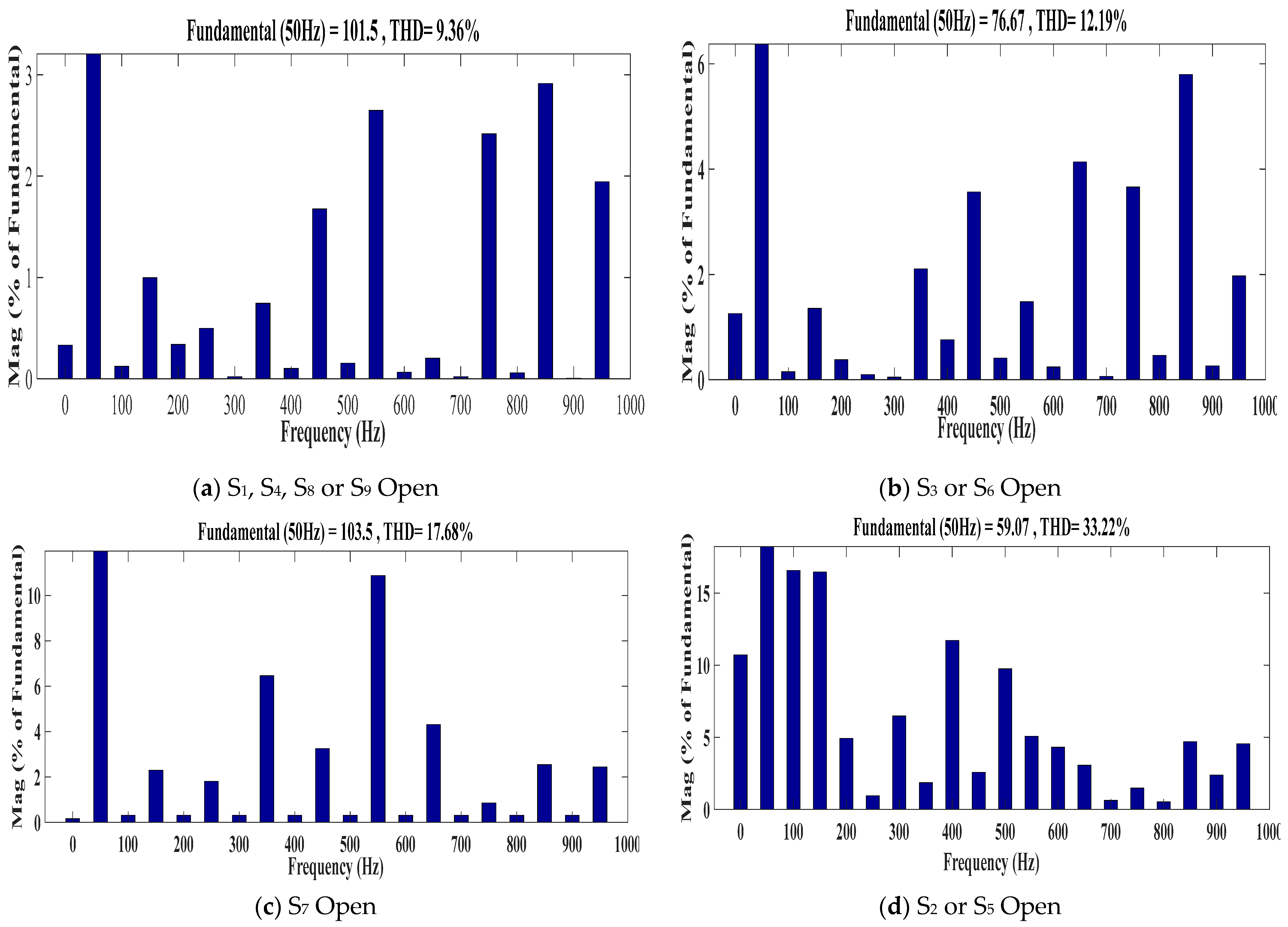

5.1. Simulation Results

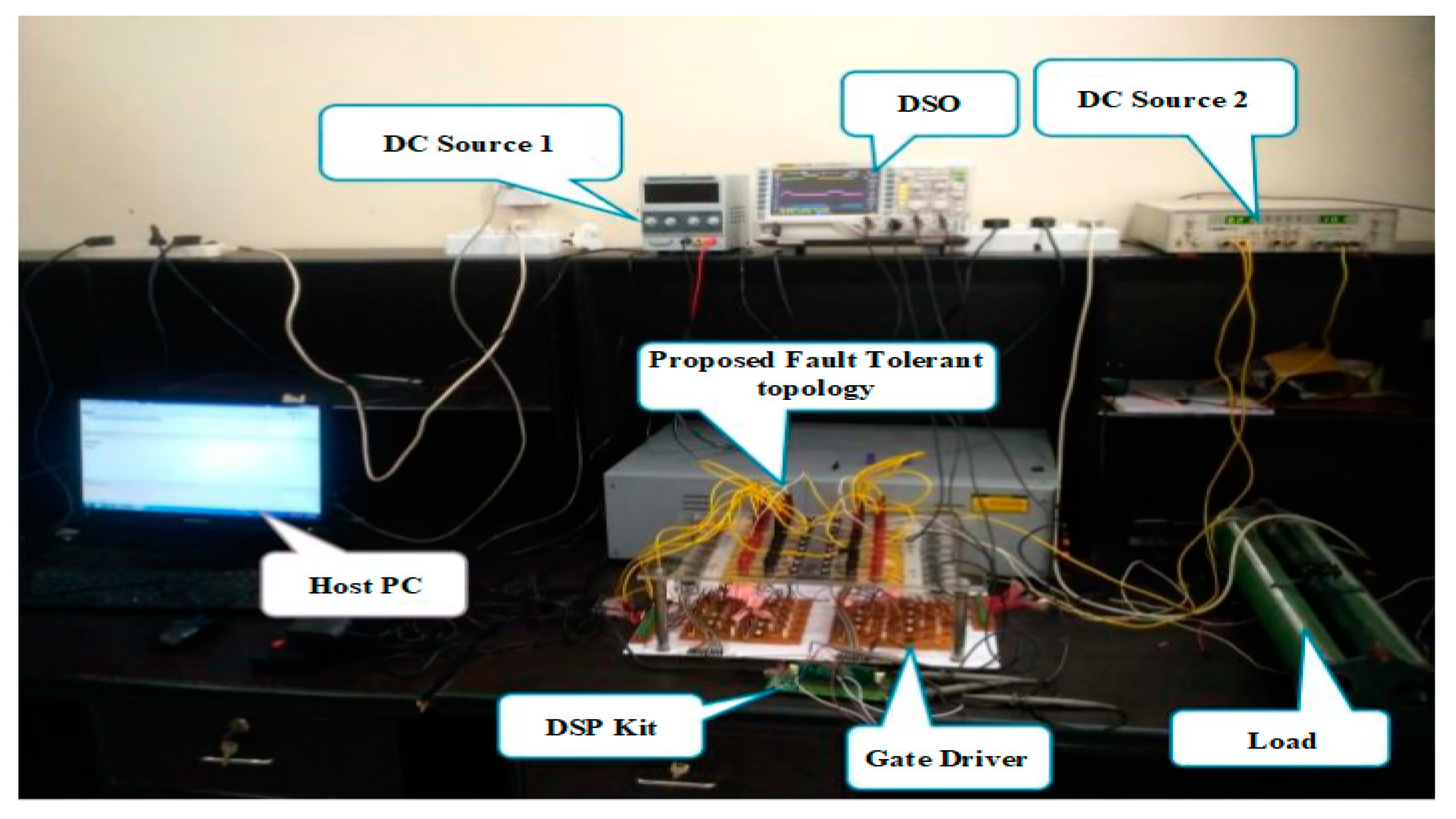

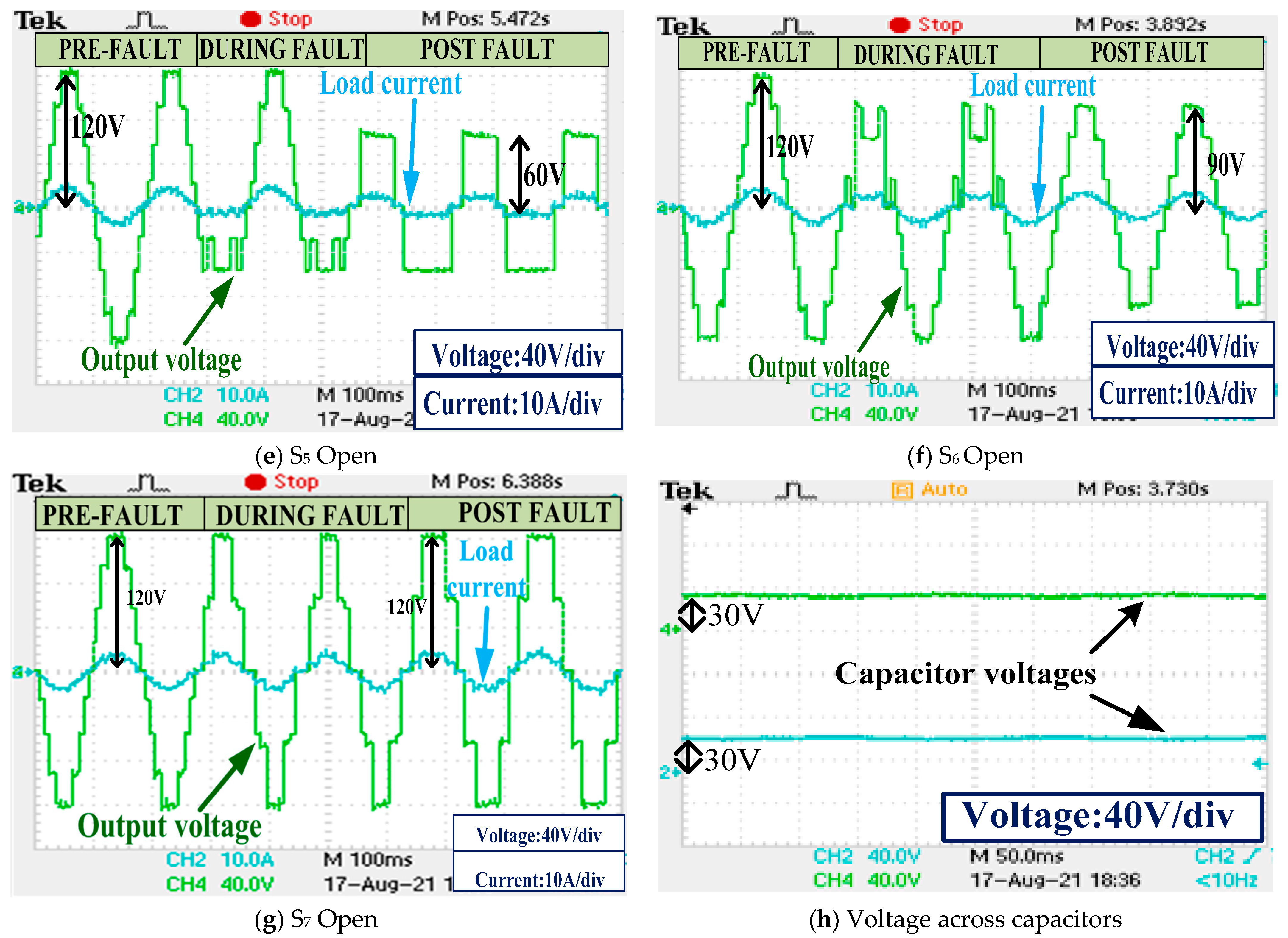

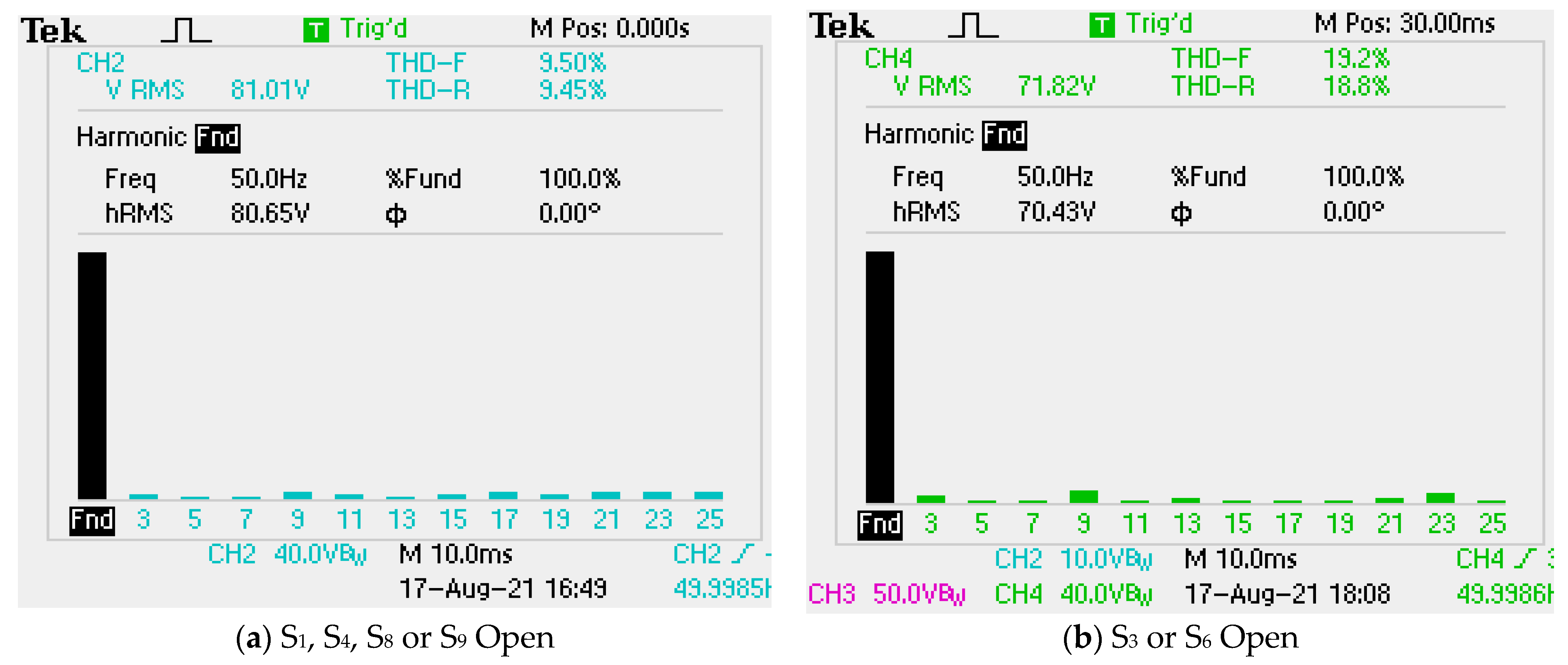

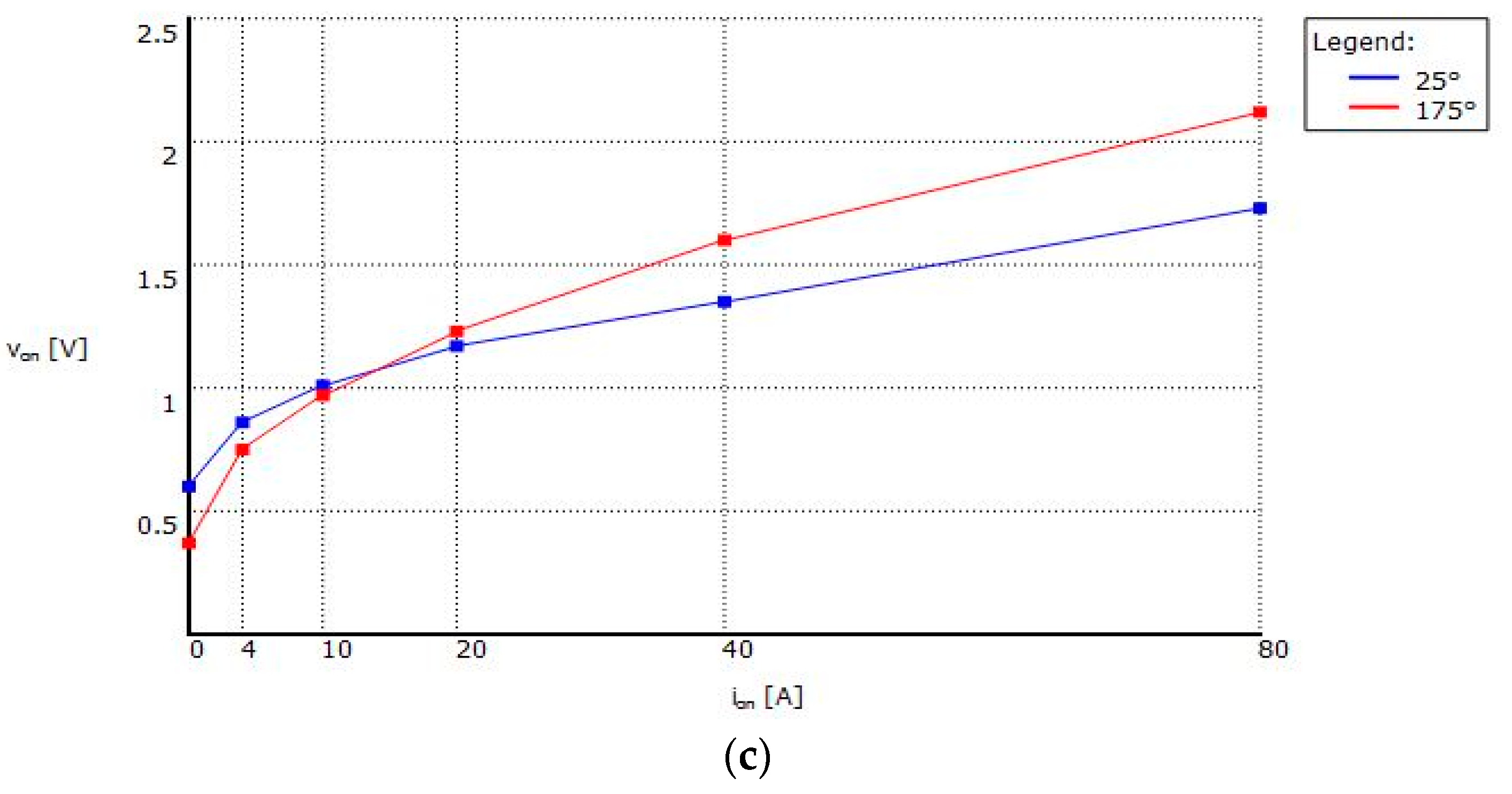

5.2. Experimental Results

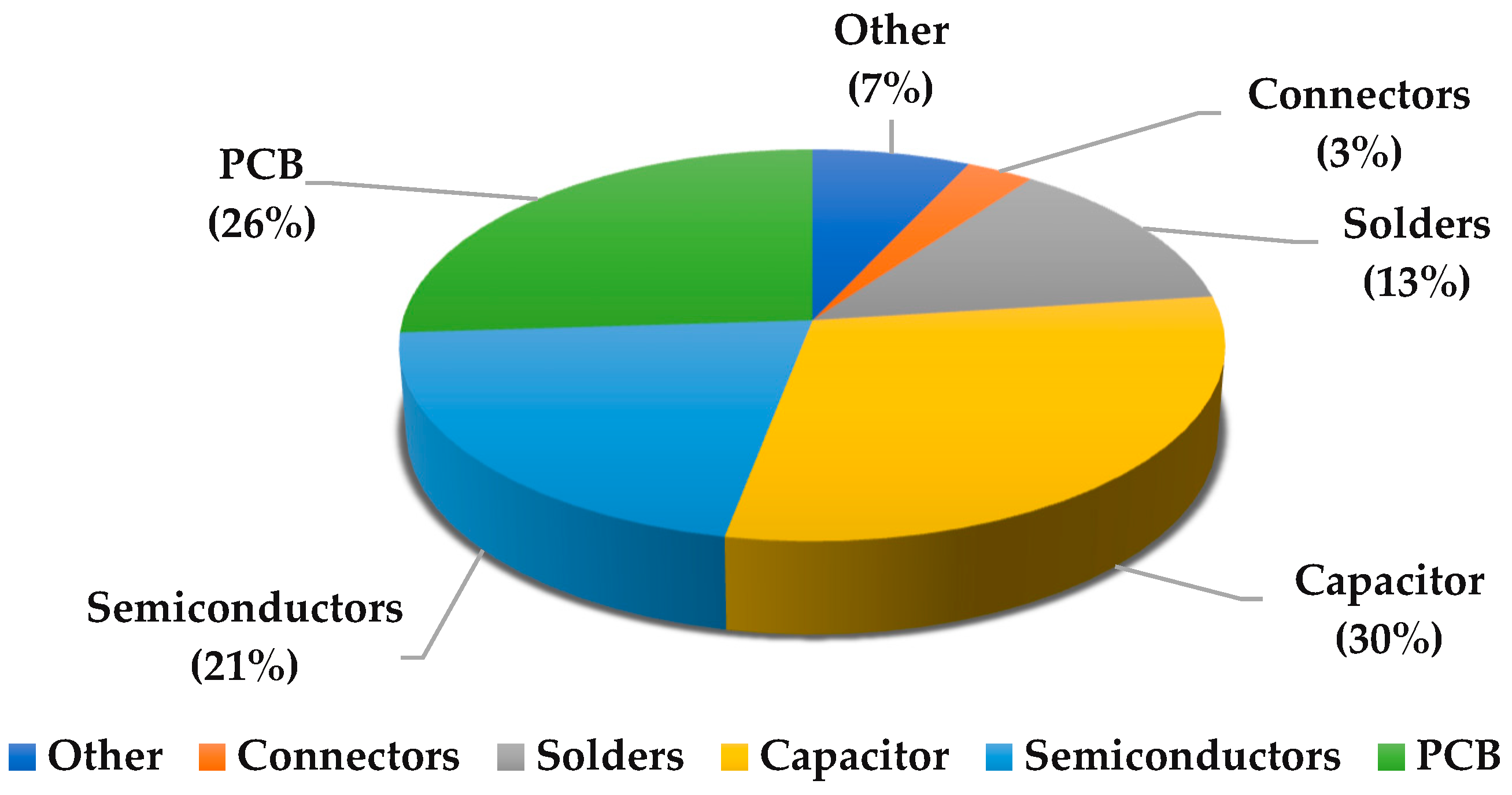

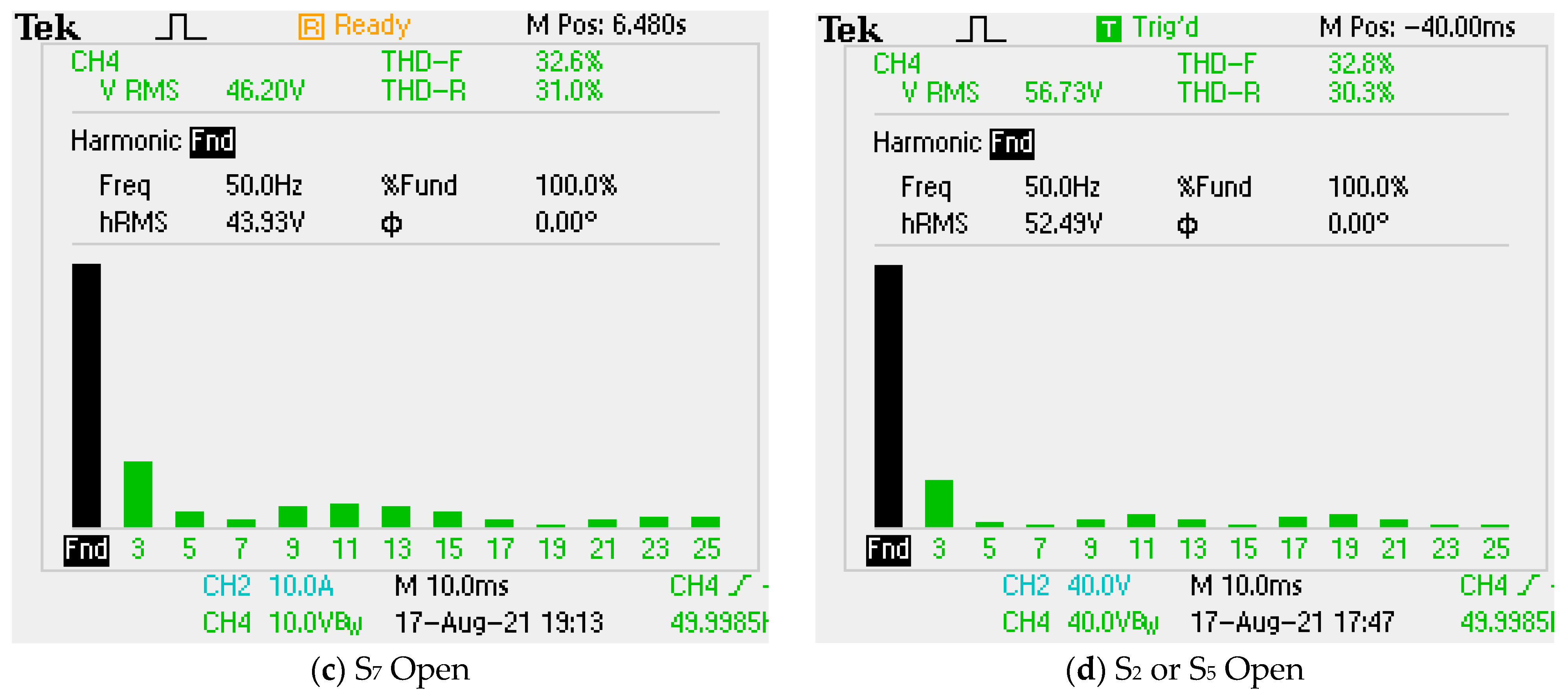

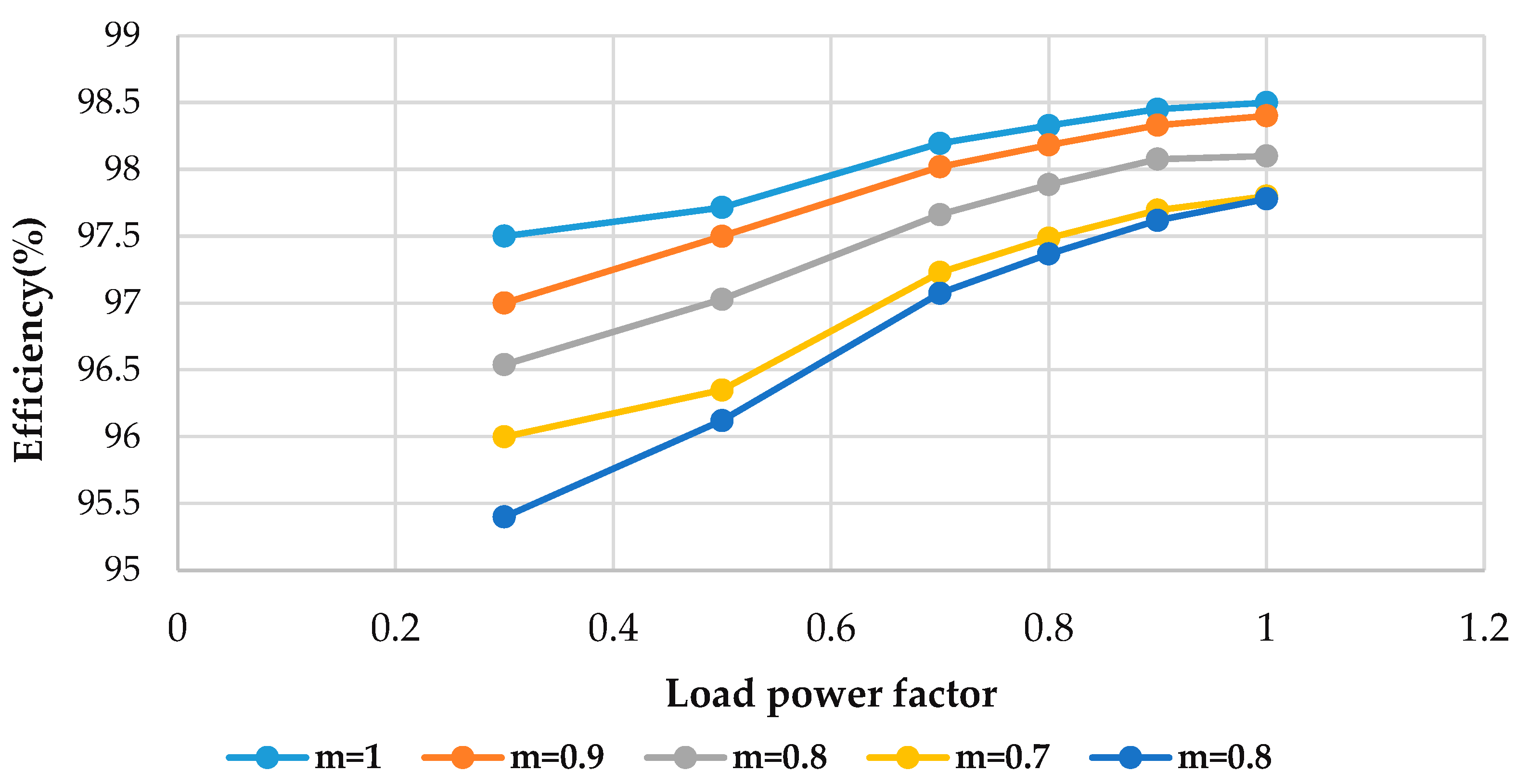

5.3. Power Loss Analysis

5.3.1. Switching Losses

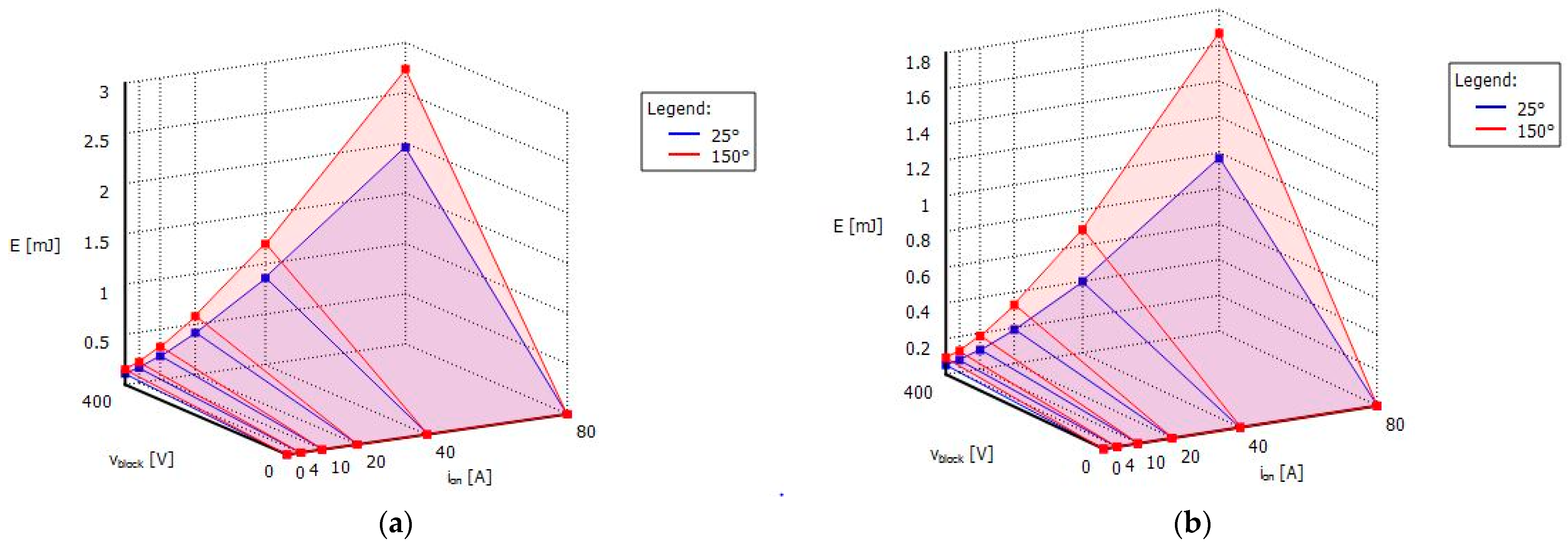

5.3.2. Conduction Losses (PC)

5.3.3. Capacitor Ripple Losses (PR)

5.4. Comparison with Recent Topologies

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.A. The age of multilevel converters arrives. IEEE Ind. Electron. Mag. 2008, 2, 28–39. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medium-voltage multilevel converters—State of the art, challenges, and requirements in industrial applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Chappa, A.; Gupta, S.; Sahu, L.K.; Gautam, S.P.; Gupta, K.K. Symmetrical and Asymmetrical Reduced Device Multilevel Inverter Topology. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 9, 885–896. [Google Scholar] [CrossRef]

- Liu, Y.; Ge, B.; Abu-Rub, H.; Peng, F.Z. An Effective Control Method for Quasi-Z-Source Cascade Multilevel Inverter-Based Grid-Tie Single-Phase Photovoltaic Power System. IEEE Trans. Ind. Inform. 2013, 10, 399–407. [Google Scholar] [CrossRef]

- Debnath, S.; Saeedifard, M. A New Hybrid Modular Multilevel Converter for Grid Connection of Large Wind Turbines. IEEE Trans. Sustain. Energy 2013, 4, 1051–1064. [Google Scholar] [CrossRef]

- Haw, L.K.; Dahidah, M.S.A.; Almurib, H. SHE–PWM Cascaded Multilevel Inverter With Adjustable DC Voltage Levels Control for STATCOM Applications. IEEE Trans. Power Electron. 2014, 29, 6433–6444. [Google Scholar] [CrossRef]

- Jung, J.-J.; Cui, S.; Lee, J.-H.; Sul, S.-K. A new topology of multilevel VSC converter for a hybrid HVDC transmission system. IEEE Trans. Power Electron. 2016, 32, 4199–4209. [Google Scholar] [CrossRef]

- Feldman, R.; Tomasini, M.; Amankwah, E.; Clare, J.C.; Wheeler, P.W.; Trainer, D.R.; Whitehouse, R.S. A Hybrid Modular Multilevel Voltage Source Converter for HVDC Power Transmission. IEEE Trans. Ind. Appl. 2013, 49, 1577–1588. [Google Scholar] [CrossRef]

- Yang, S.; Xiang, D.; Bryant, A.; Mawby, P.; Ran, L.; Tavner, P. Condition Monitoring for Device Reliability in Power Electronic Converters: A Review. IEEE Trans. Power Electron. 2010, 25, 2734–2752. [Google Scholar] [CrossRef]

- Choupan, R.; Golshannavaz, S.; Nazarpour, D.; Barmala, M. A new structure for multilevel inverters with fault-tolerant capability against open circuit faults. Electr. Power Syst. Res. 2018, 168, 105–116. [Google Scholar] [CrossRef]

- Mirafzal, B. Survey of Fault-Tolerance Techniques for Three-Phase Voltage Source Inverters. IEEE Trans. Ind. Electron. 2014, 61, 5192–5202. [Google Scholar] [CrossRef]

- Choi, U.-M.; Lee, K.-B.; Blaabjerg, F. Diagnosis and Tolerant Strategy of an Open-Switch Fault for T-Type Three-Level Inverter Systems. IEEE Trans. Ind. Appl. 2013, 50, 495–508. [Google Scholar] [CrossRef]

- Caseiro, L.; Cruz, S.; Mendes, A. Fault tolerance in back-to-back three-level neutral-point-clamped induction motor drives. In Proceedings of the 7th IET International Conference on Power Electronics, Machines and Drives (PEMD 2014), Manchester, UK, 8–10 April 2014. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Robles, E.; Gabiola, I.; Zaragoza, J.; Villate, J.L.; Boroyevich, D. Three-Level Converter Topologies With Switch Breakdown Fault-Tolerance Capability. IEEE Trans. Ind. Electron. 2008, 55, 982–995. [Google Scholar] [CrossRef]

- Richardeau, F.; Pham, T.T.L. Reliability Calculation of Multilevel Converters: Theory and Applications. IEEE Trans. Ind. Electron. 2012, 60, 4225–4233. [Google Scholar] [CrossRef]

- Druant, J.; Vyncke, T.; De Belie, F.; Sergeant, P.; Melkebeek, J. Adding inverter fault detection to model-based predictive control for flying-capacitor inverters. IEEE Trans. Ind. Electron. 2014, 62, 2054–2063. [Google Scholar] [CrossRef]

- Kandasamy, K.; Vilathgamuwa, M.; Tseng, K.J. Inter-module state-of-charge balancing and fault-tolerant operation of cascaded H-bridge converter using multi-dimensional modulation for electric vehicle application. IET Power Electron. 2015, 8, 1912–1919. [Google Scholar] [CrossRef]

- Song, W.; Huang, A.Q. Fault-Tolerant Design and Control Strategy for Cascaded H-Bridge Multilevel Converter-Based STATCOM. IEEE Trans. Ind. Electron. 2009, 57, 2700–2708. [Google Scholar] [CrossRef]

- Song, Y.; Wang, B. Analysis and Experimental Verification of a Fault-Tolerant HEV Powertrain. IEEE Trans. Power Electron. 2013, 28, 5854–5864. [Google Scholar] [CrossRef]

- Kumar, V.V.S.P.; Fernandes, B.G. A Fault-Tolerant Single-Phase Grid-Connected Inverter Topology with Enhanced Reliability for Solar PV Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1254–1262. [Google Scholar] [CrossRef]

- Sivakumar, K. A Fault-Tolerant Single-Phase Five-Level Inverter for Grid-Independent PV Systems. IEEE Trans. Ind. Electron. 2015, 62, 7569–7577. [Google Scholar] [CrossRef]

- Mhiesan, H.; Wei, Y.; Siwakoti, Y.P.; Mantooth, H.A. A Fault-Tolerant Hybrid Cascaded H-Bridge Multilevel Inverter. IEEE Trans. Power Electron. 2020, 35, 12702–12715. [Google Scholar] [CrossRef]

- Prakash, G.; Subramani, C.; Bharatiraja, C.; Shabin, M. A low cost single phase grid connected reduced switch PV inverter based on Time Frame Switching Scheme. Int. J. Electr. Power Energy Syst. 2016, 77, 100–111. [Google Scholar] [CrossRef]

- Dewangan, N.K.; Gupta, S.; Gupta, K.K. Approach to synthesis of fault tolerant reduced device count multilevel inverters (FT RDC MLIs). IET Power Electron. 2019, 12, 476–482. [Google Scholar] [CrossRef]

- Vijeh, M.; Rezanejad, M.; Samadaei, E.; Bertilsson, K. A General Review of Multilevel Inverters Based on Main Submodules: Structural Point of View. IEEE Trans. Power Electron. 2019, 34, 9479–9502. [Google Scholar] [CrossRef]

- Kumar, D.; Nema, R.K.; Gupta, S. Investigation of fault-tolerant capabilities of some recent multilevel inverter topologies. Int. J. Electron. 2021, 108, 1957–1976. [Google Scholar] [CrossRef]

- Chen, A.; Hu, L.; Chen, L.; Deng, Y.; He, X. A Multilevel Converter Topology with Fault-Tolerant Ability. IEEE Trans. Power Electron. 2005, 20, 405–415. [Google Scholar] [CrossRef]

- Aguayo-Alquicira, J.; Vásquez-Libreros, I.; De Léon-Aldaco, S.; Ponce-Silva, M.; Lozoya-Ponce, R.; Flores-Rodríguez, E.; García-Morales, J.; Reyes-Severiano, Y.; Carrillo-Santos, L.; Marín-Reyes, M.; et al. Reconfiguration Strategy for Fault Tolerance in a Cascaded Multilevel Inverter Using a Z-Source Converter. Electronics 2021, 10, 574. [Google Scholar] [CrossRef]

- Jalhotra, M.; Kumar, L.; Gautam, S.P.; Gupta, S. Development of fault-tolerant MLI topology. IET Power Electron. 2018, 11, 1416–1424. [Google Scholar] [CrossRef]

- Kwak, Y.-G.; Heo, D.-H.; Kim, S.-P.; Song, S.-G.; Park, S.-J.; Kang, F.-S. Reliability and Economic Efficiency Analysis of 4-Leg Inverter Compared with 3-Leg Inverters. Electronics 2021, 10, 87. [Google Scholar] [CrossRef]

- Abbasi, S.; Ghadimi, A.A.; Abolmasoumi, A.H.; Miveh, M.R.; Jurado, F. Enhanced Control Scheme for a Three-Phase Grid-Connected PV Inverter under Unbalanced Fault Conditions. Electronics 2020, 9, 1247. [Google Scholar] [CrossRef]

- Sharifzadeh, M.; Al-Haddad, K. Packed E-Cell (PEC) Converter Topology Operation and Experimental Validation. IEEE Access 2019, 7, 93049–93061. [Google Scholar] [CrossRef]

- Sharifzadeh, M.; Babaie, M.; Sebaaly, F.; Mehrasa, M.; Chouinard, G.; Al-Haddad, K. Low Switching Frequency Operation of PEC9 Multilevel Inverter Using Modified SHM-PWM. In Proceedings of the IECON 2020 the 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; pp. 4215–4220. [Google Scholar] [CrossRef]

- Hu, P.; Jiang, D. A Level-Increased Nearest Level Modulation Method for Modular Multilevel Converters. IEEE Trans. Power Electron. 2014, 30, 1836–1842. [Google Scholar] [CrossRef]

- Dewangan, N.; Jalhotra, M.; Sahu, L.K.; Gautam, S.P.; Gupta, S. Fault Tolerant Analysis of Single Phase Multilevel Inverter. In Proceedings of the 2018 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Chennai, India, 18–21 December 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Kumar, V.; Singh, S.; Jain, S. Fault Tolerant T-Type Cross Connected Source Nine Level Inverter. In Proceedings of the 2020 IEEE 9th Power India International Conference (PIICON), Murthal, India, 28 February–1 March 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Chappa, A.; Gupta, S.; Sahu, L.K.; Gupta, K.K. A Fault-Tolerant Multilevel Inverter Topology With Preserved Output Power and Voltage Levels Under Pre- and Postfault Operation. IEEE Trans. Ind. Electron. 2020, 68, 5756–5764. [Google Scholar] [CrossRef]

- Kumar, M.S.; Borghate, V.B.; Karasani, R.R.; Sabyasachi, S.; Suryawanshi, H.M. A fault-tolerant modular multilevel inverter topology. Int. J. Circuit Theory Appl. 2018, 46, 1028–1043. [Google Scholar] [CrossRef]

| Modes | S1 | S2 | S3 | S4 | S5 | S6 | S7 | Io | C1 | C2 | Output Voltage Magnitude | Output Level |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| µ1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | >0 | - | - | Vdc | +E |

| µ2 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | >0 | ↓ | - | Vdc − V1 | +3E/4 |

| µ3 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | >0 | ↓ | ↓ | Vdc − V1 − V2 | +E/2 |

| µ4 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | >0 | ↑ | ↑ | V1 + V2 | +E/2 |

| µ5 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | >0 | - | ↑ | V2 | +E/4 |

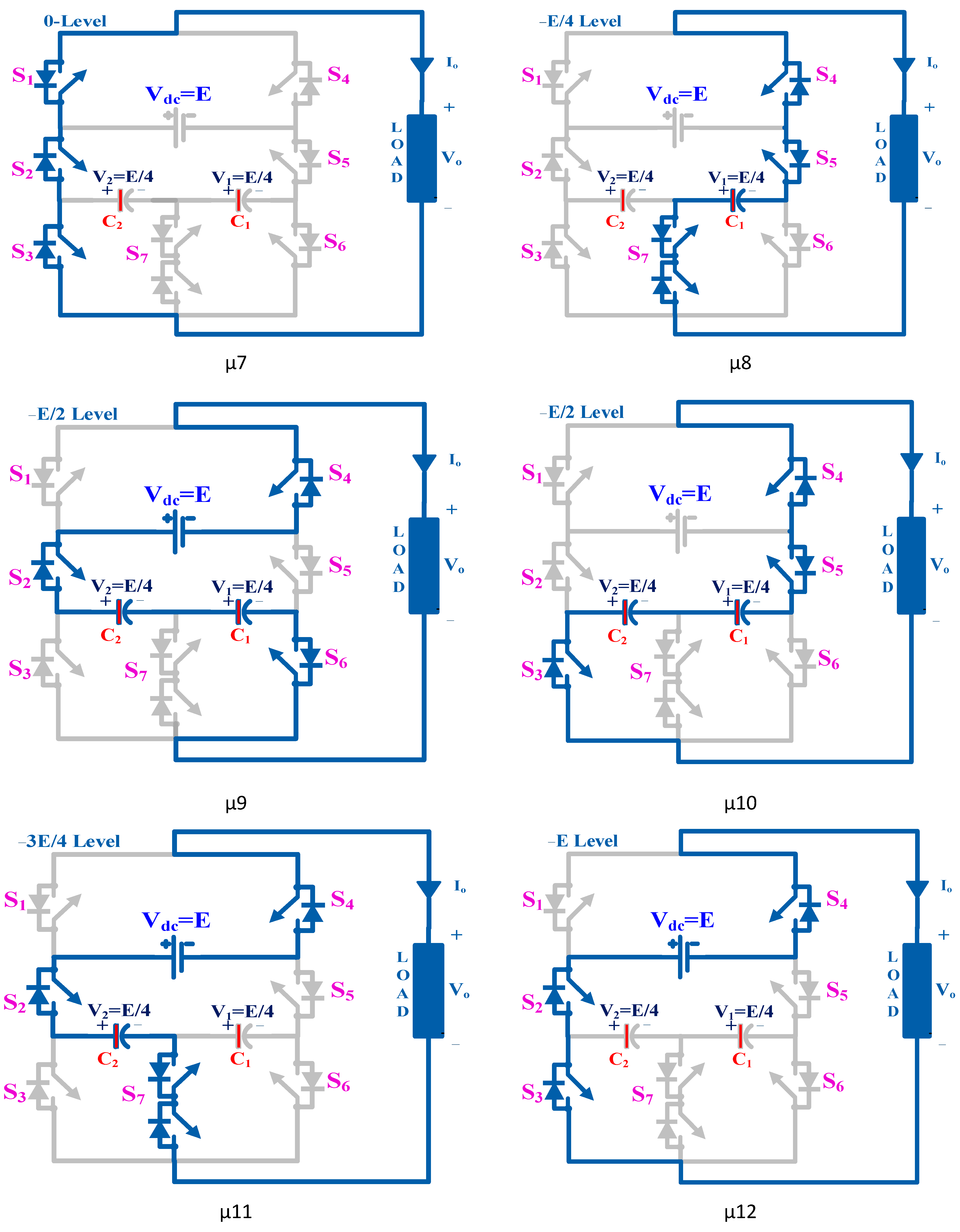

| µ6 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | >0 | - | - | 0 | 0 |

| µ7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | >0 | - | - | 0 | 0 |

| µ8 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | >0 | ↓ | - | −V1 | −E/4 |

| µ9 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | >0 | ↑ | ↑ | −Vdc + V1 + V2 | −E/2 |

| µ10 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | >0 | ↓ | ↓ | −V1 − V2 | −E/2 |

| µ11 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | >0 | - | ↑ | −Vdc + V2 | −3E/4 |

| µ12 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | >0 | - | - | Vdc | −E |

| µ13 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | <0 | - | - | Vdc | +E |

| µ14 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | <0 | ↑ | - | Vdc − V1 | +3E/4 |

| µ15 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | <0 | ↑ | ↑ | Vdc − V1 − V2 | +E/2 |

| µ16 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | <0 | ↓ | ↓ | V1 + V2 | +E/2 |

| µ17 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | <0 | - | ↓ | V2 | +E/4 |

| µ18 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | <0 | - | - | 0 | 0 |

| µ19 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | <0 | - | - | 0 | 0 |

| µ20 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | <0 | ↑ | - | −V1 | −E/4 |

| µ21 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | <0 | ↓ | ↓ | −Vdc + V1 + V2 | −E/2 |

| µ22 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | <0 | ↑ | ↑ | −V1 − V2 | −E/2 |

| µ23 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | <0 | - | ↓ | −Vdc + V2 | −3E/4 |

| µ24 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | <0 | - | - | Vdc | −E |

| Failed Switch | Operating Modes Available | Operation Level |

|---|---|---|

| S1 | µ6, µ8, µ9, µ10, µ11, µ12 | SHUT DOWN |

| S2 | µ1, µ2, µ3, µ6, µ8, µ10 | 3 Levels |

| S3 | µ1, µ2, µ4, µ5, µ6, µ8, µ9, µ11 | 7 Levels |

| S4 | µ1, µ2, µ3, µ4, µ5, µ7 | SHUT DOWN |

| S5 | µ4, µ5, µ7, µ9, µ11, µ12 | 3 Levels |

| S6 | µ2, µ3, µ5, µ7, µ8, µ10, µ11, µ12 | 7 Levels |

| S7 | µ1, µ3, µ4, µ6, µ7, µ9, µ10, µ12 | 5 Levels |

| Modes | Prioritization Number | S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | S9 | Output Voltage Magnitude | Output Level |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| µ1 | A11 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | +Vdc | +E |

| A12 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | +Vdc | ||

| µ2 | A21 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | +Vdc − V1 | +3E/4 |

| A22 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | +Vdc − V1 | ||

| µ3 | A31 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | +Vdc − V1 − V2 | +E/2 |

| A32 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | +V1 + V2 | ||

| A33 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | +Vdc − V1 − V2 | ||

| A34 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | +V1 + V2 | ||

| µ4 | A41 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | +V2 | +E/4 |

| A42 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | +V2 | ||

| µ5 | A51 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| A52 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| A53 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | ||

| A54 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | ||

| µ6 | A61 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | −V1 | −E/4 |

| A62 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | −V1 | ||

| µ7 | A71 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | −Vdc + V1 + V2 | −E/2 |

| A72 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | −V1 − V2 | ||

| A73 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | −Vdc + V1 + V2 | ||

| A74 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | −V1 − V2 | ||

| µ8 | A81 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | −Vdc + V2 | −3E/4 |

| A82 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | −Vdc + V2 | ||

| µ9 | A91 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | −Vdc | −E |

| A92 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | −Vdc |

| Parameters | Attributes |

|---|---|

| DC Voltage Source 1 | 100 Volts |

| DC Voltage Source 2 | 50 Volts |

| Switches (S1 to S9) | IGBT/Diode |

| Switching frequency | 50 Hz |

| Fundamental frequency | 50 Hz |

| Load (R, L) | 100 Ω, 250 mH |

| Capacitors (C1 and C2) | 2500 µf each |

| Modulation Index | 1 |

| Parameters | Attributes |

|---|---|

| DC source 1 | 120 V |

| DC source 2 | 60 V |

| Capacitors (C1 and C2) | 2500 µF each |

| Switches | IGBT FGA25N120 |

| Load (purely resistive) | 200 Ω |

| DSP Kit | C2000, Texas instruments |

| Optocoupler | TLP 250 (TOSHIBA) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Khan, S.A.; Sarwar, A.; Tariq, M.; Urooj, S.; Hossain, M.A. Open Circuit Fault Mitigation in a Nine-Level Modified Packed E-Cell Inverter. Energies 2022, 15, 7976. https://doi.org/10.3390/en15217976

Khan SA, Sarwar A, Tariq M, Urooj S, Hossain MA. Open Circuit Fault Mitigation in a Nine-Level Modified Packed E-Cell Inverter. Energies. 2022; 15(21):7976. https://doi.org/10.3390/en15217976

Chicago/Turabian StyleKhan, Shoeb Ahmad, Adil Sarwar, Mohd Tariq, Shabana Urooj, and Md Alamgir Hossain. 2022. "Open Circuit Fault Mitigation in a Nine-Level Modified Packed E-Cell Inverter" Energies 15, no. 21: 7976. https://doi.org/10.3390/en15217976

APA StyleKhan, S. A., Sarwar, A., Tariq, M., Urooj, S., & Hossain, M. A. (2022). Open Circuit Fault Mitigation in a Nine-Level Modified Packed E-Cell Inverter. Energies, 15(21), 7976. https://doi.org/10.3390/en15217976