Dynamic-State Analysis of Inverter Based on Cascode GaN HEMTs for PV Application

Abstract

1. Introduction

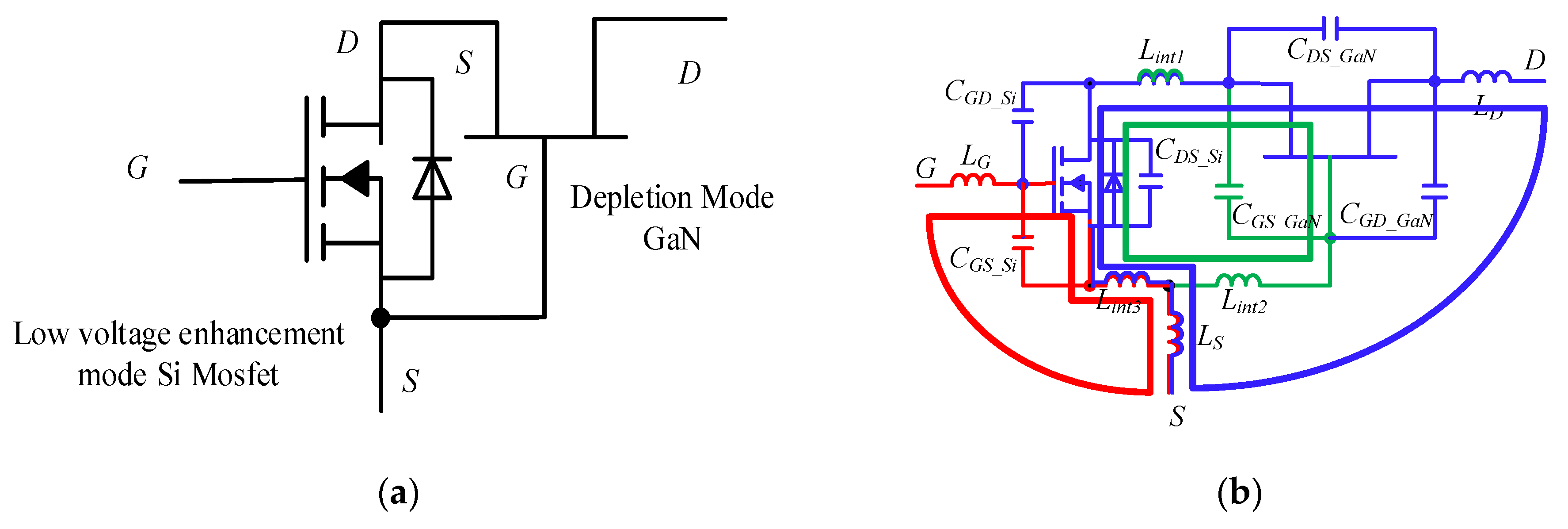

2. Characteristic and Model of Cascode GaN HEMT

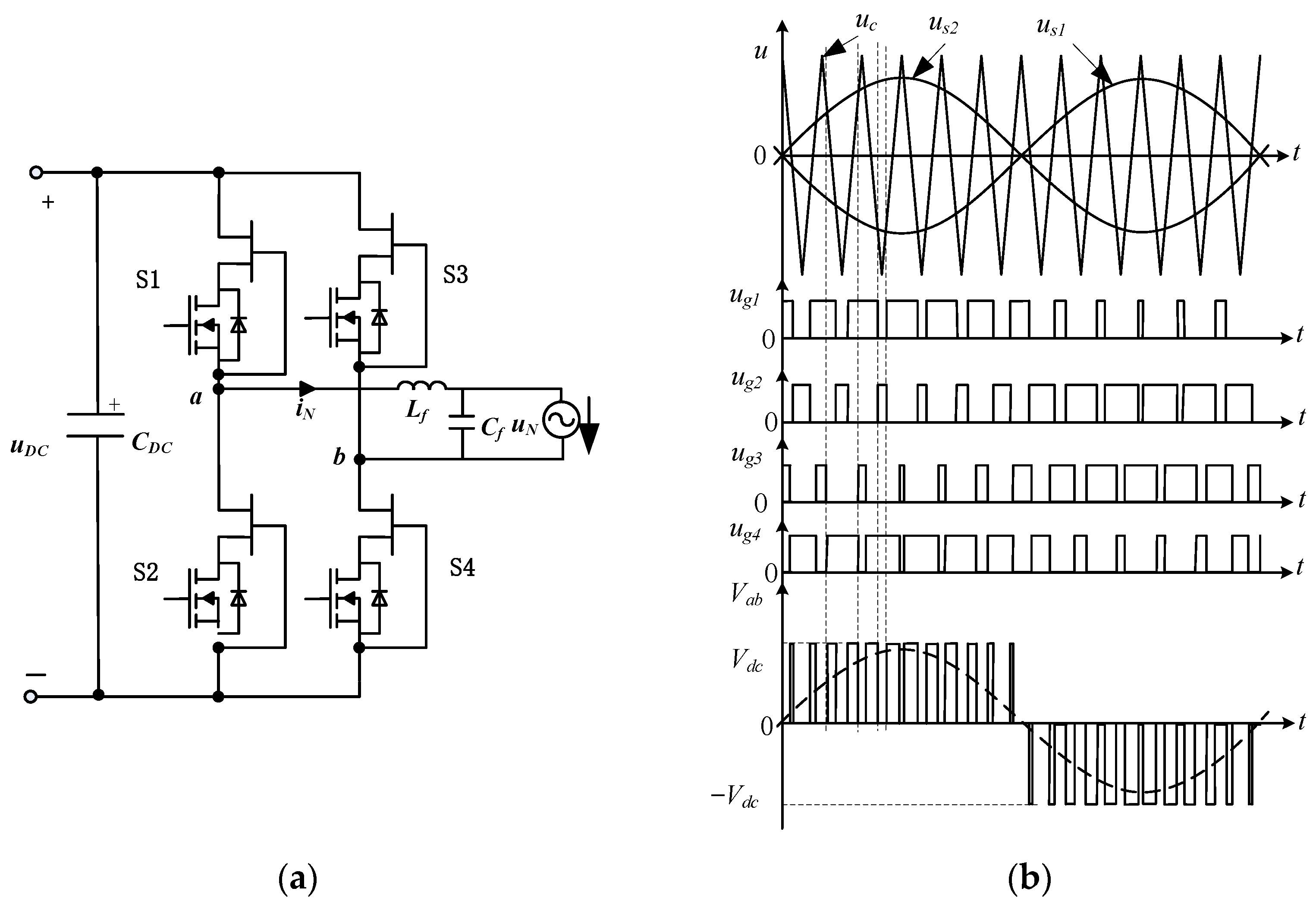

3. Dynamic Analysis of Inverter Based on Cascode GAN HEMT

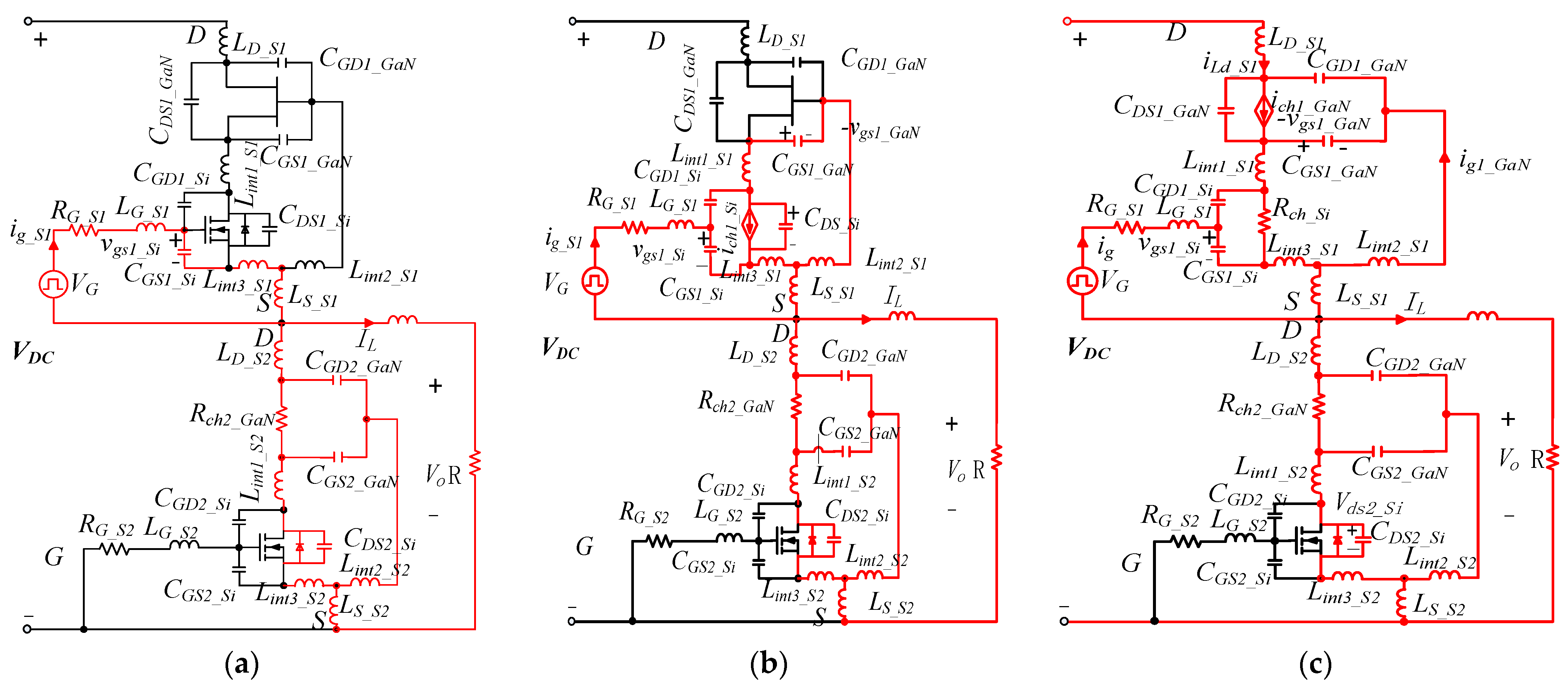

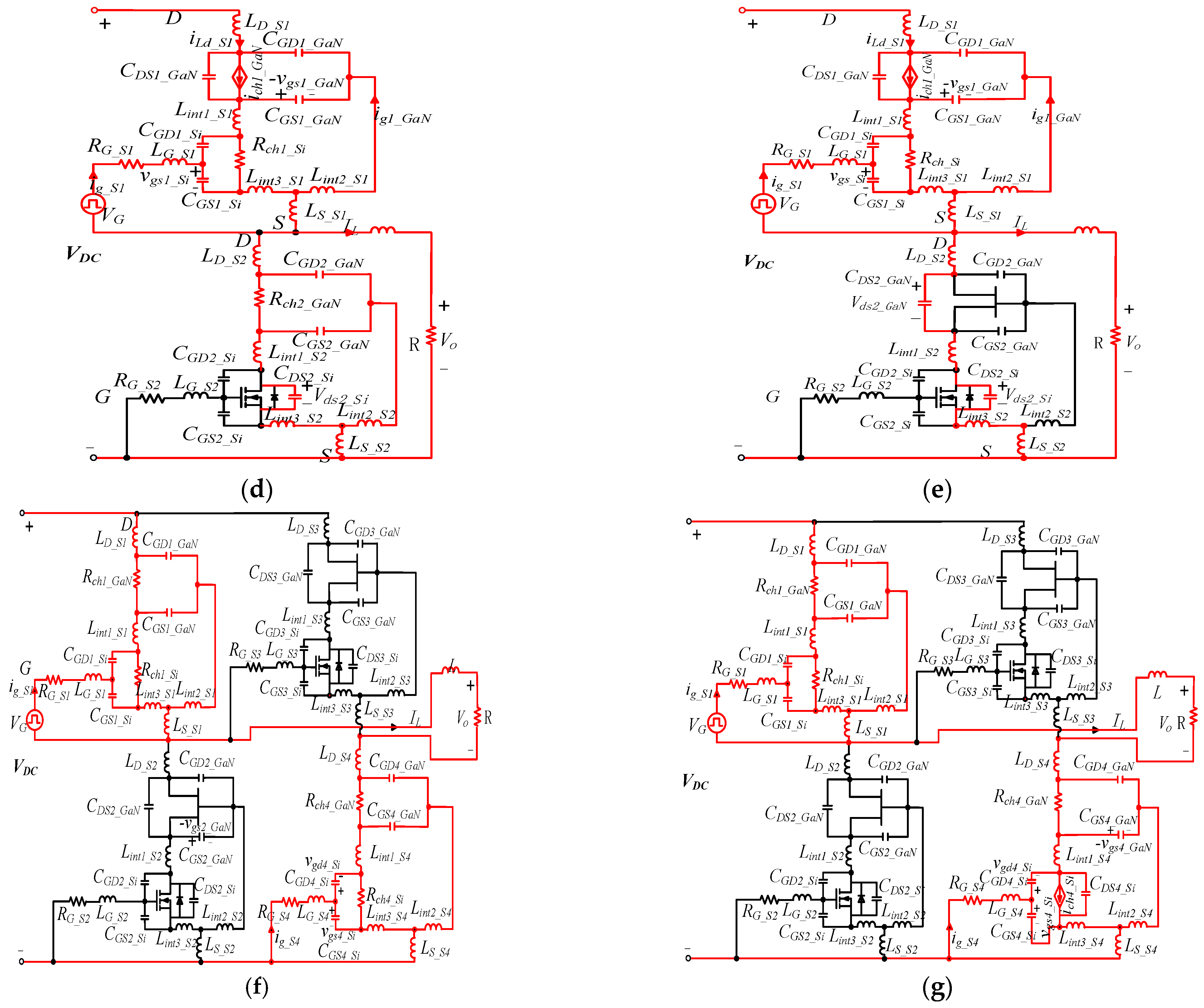

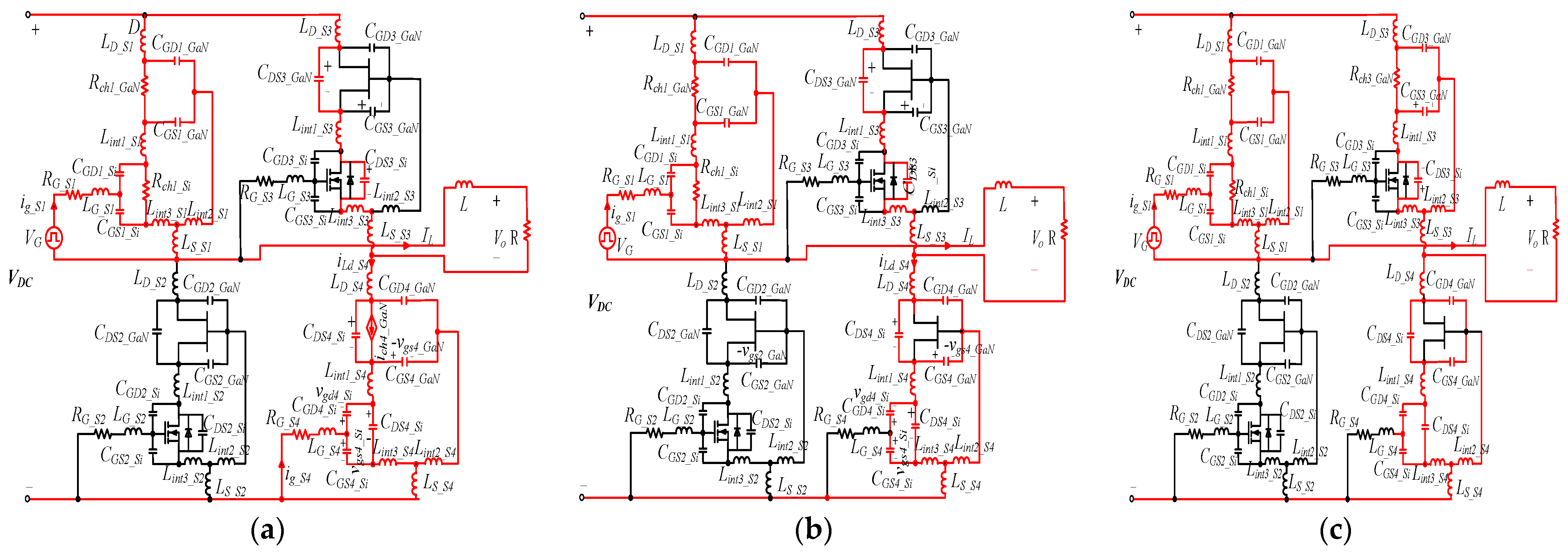

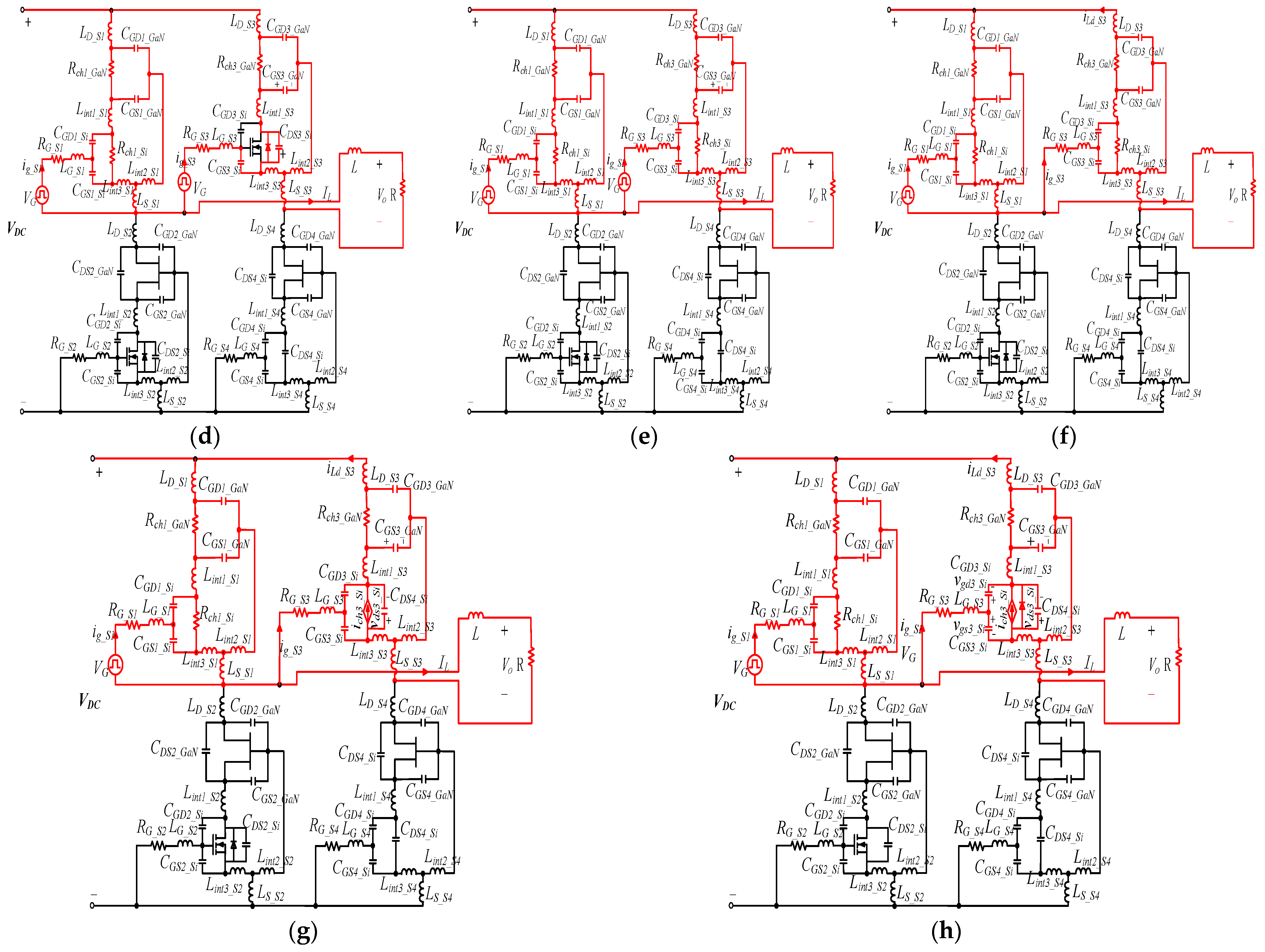

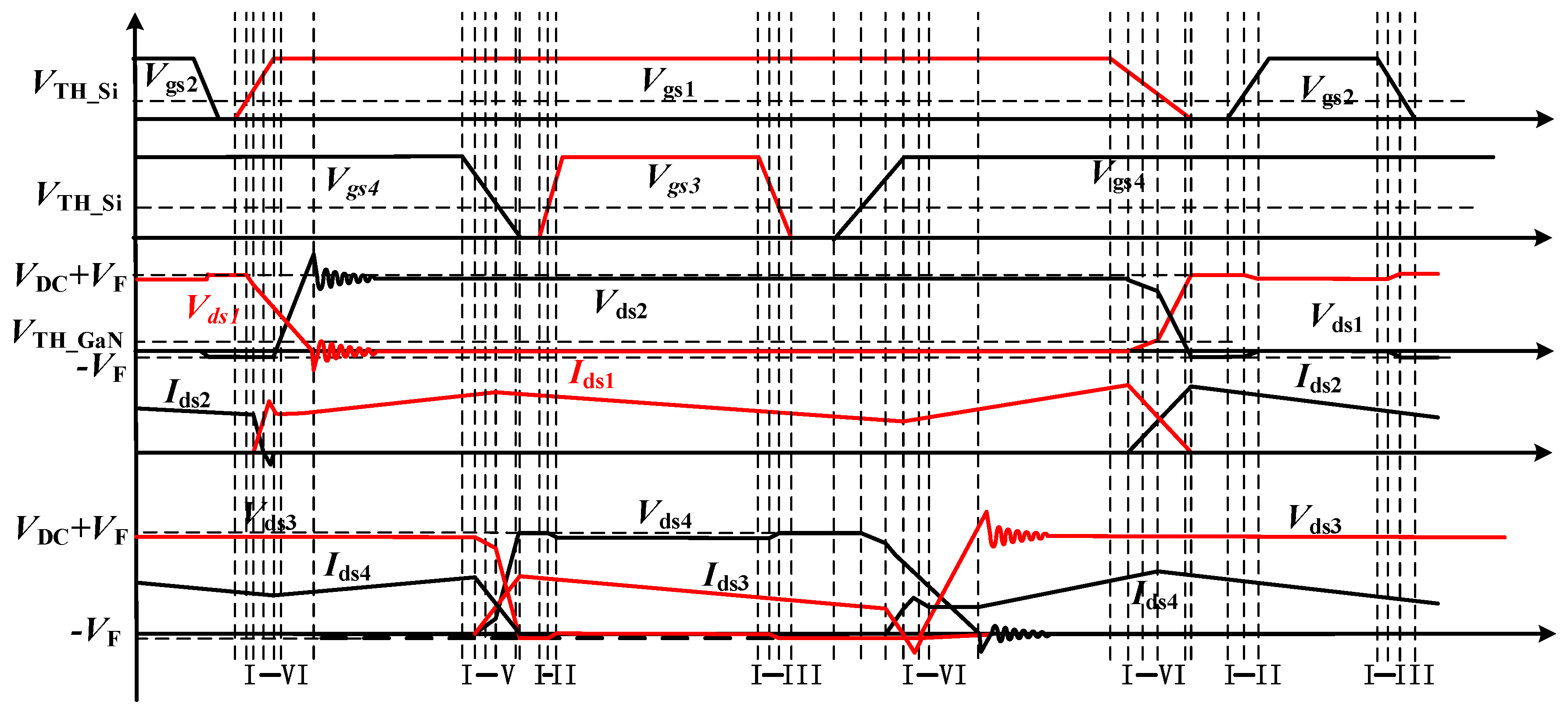

3.1. Positive Turn-On Process of the Bridge Leg Switches

3.2. Positive Turn-off Process of the Bridge Leg Switches

3.3. Reverse Turn-on Process of the Bridge Leg Switches

3.4. Reverse Turn-Off Process of the Bridge Leg Switches

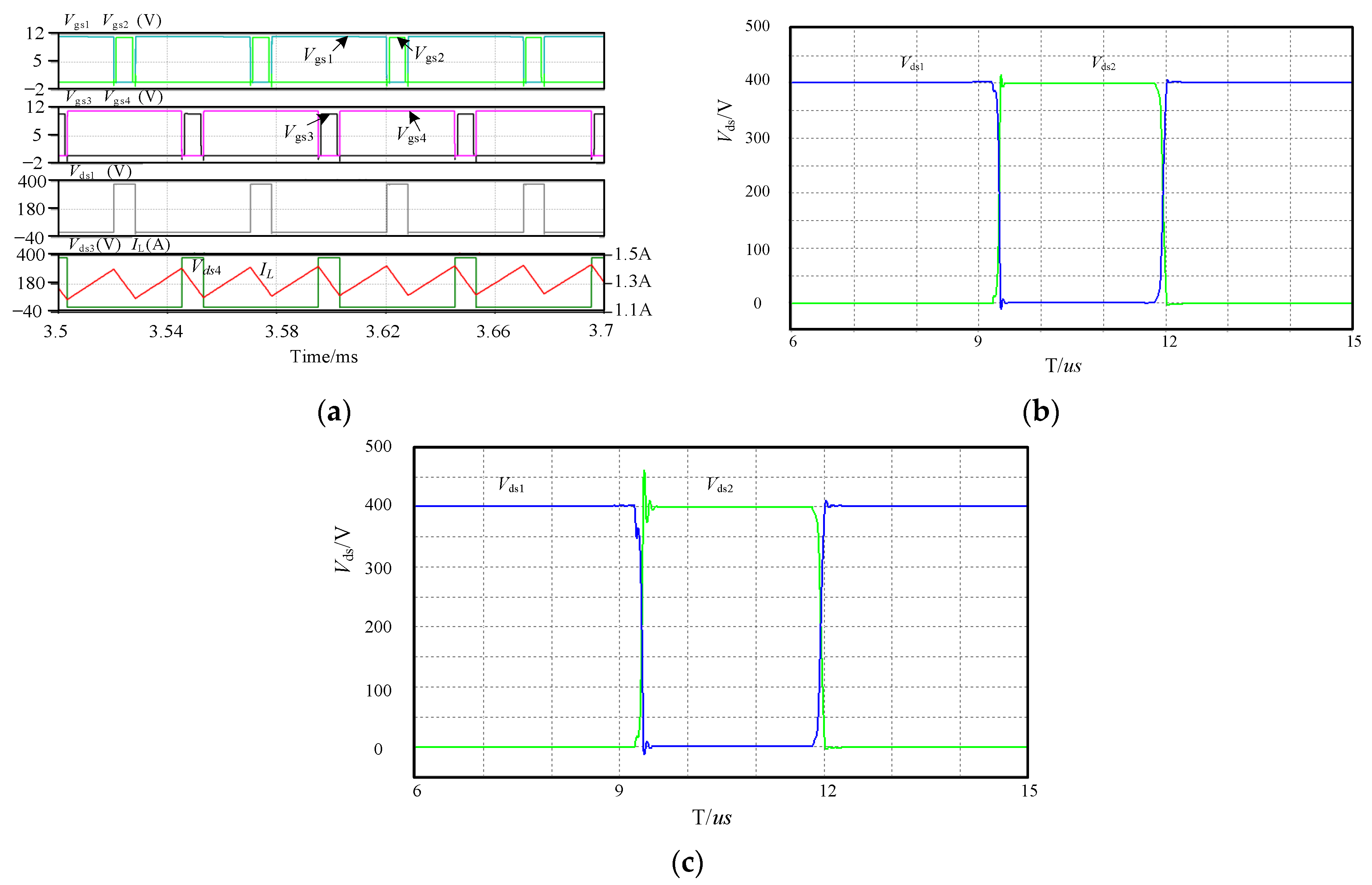

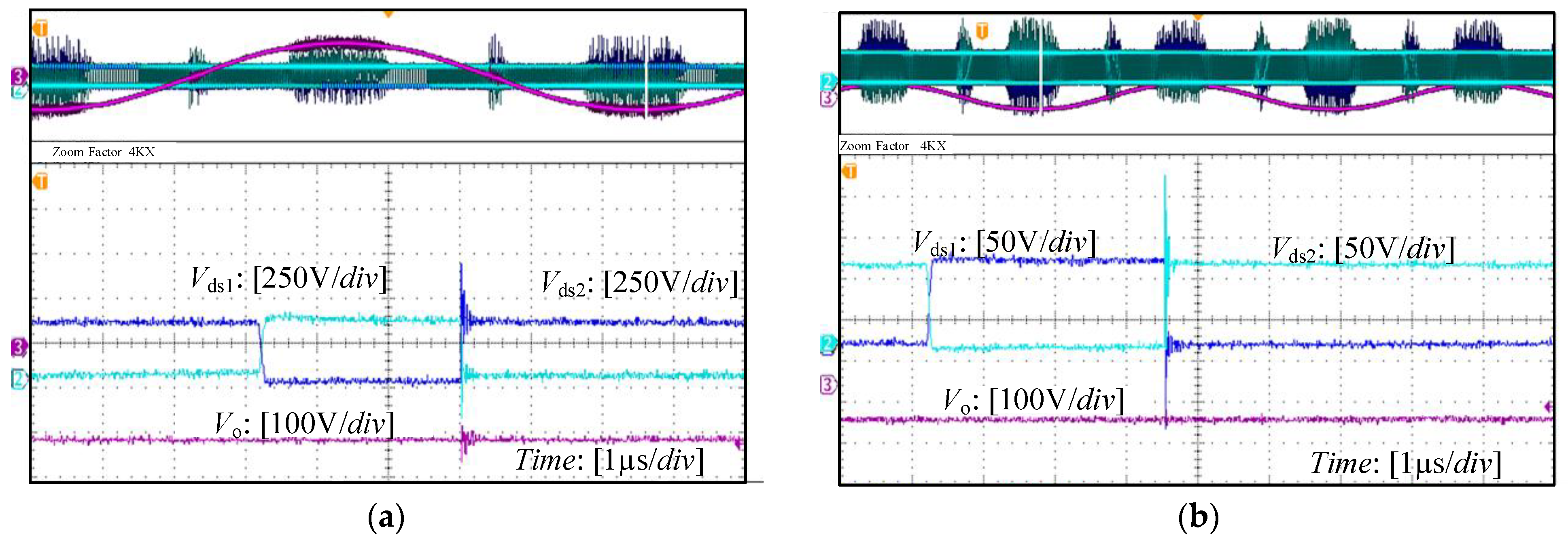

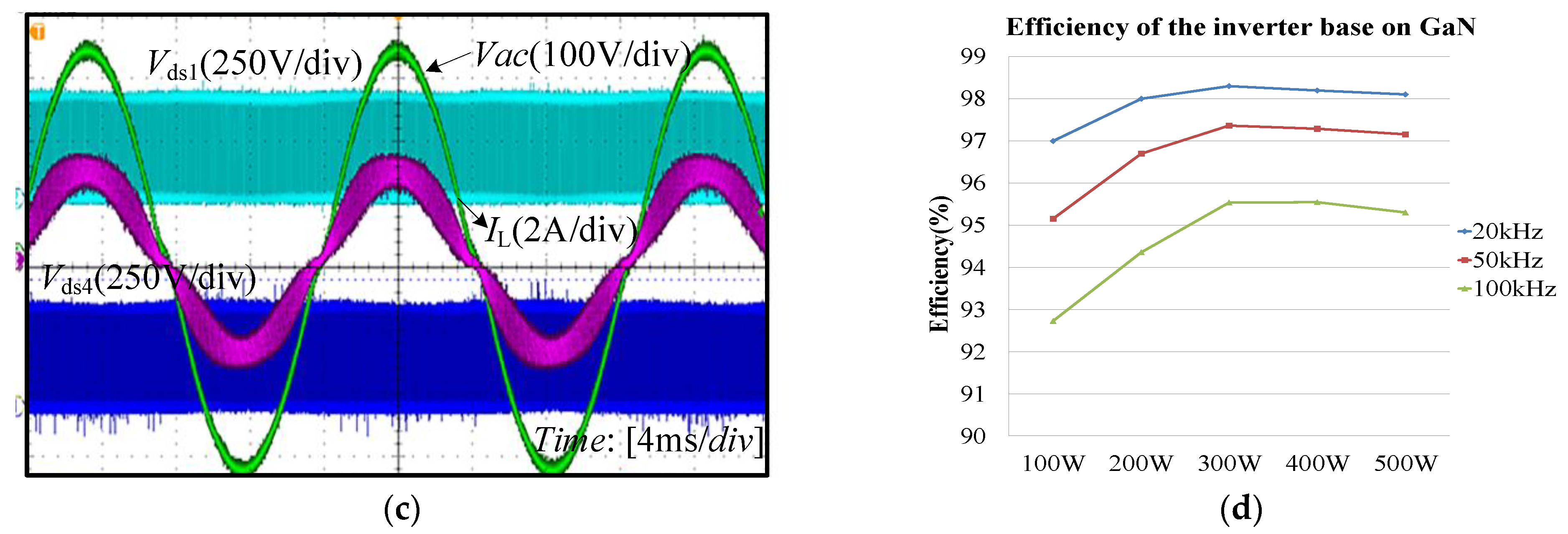

4. Simulation and Experimental Verifications

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Bai, F.; Cui, Y.; Yan, R.; Saha, T.K.; Gu, H.; Eghbal, D. Frequency Response of PV Inverters Toward High Renewable Penetrated Distribution Networks. CSEE J. Power Energy Syst. 2022, 8, 465–475. [Google Scholar]

- Gu, H.J.; Yan, R.F.; Saha, T.K. Review of system strength and inertia requirements for the national electricity market of Australia. CSEE J. Power Energy Syst. 2019, 5, 295–305. [Google Scholar]

- Alajmi, B.N.; Ahmed, K.H.; Adam, G.P.; Williams, B.W. Single-Phase Single-Stage Transformer less Grid-Connected PV System. IEEE Trans. Power Electron. 2012, 28, 2664–2676. [Google Scholar] [CrossRef]

- Barater, D.; Lorenzani, E.; Concari, C.; Franceschini, G.; Buticchi, G. Recent advances in single-phase transformerless photovoltaic inverters. IET Renew. Power Gener. 2016, 10, 260–273. [Google Scholar] [CrossRef]

- Freddy, T.K.S.; Rahim, N.A.; Hew, W.-P.; Che, H.S. Comparison and Analysis of Single-Phase Transformerless Grid-Connected PV Inverters. IEEE Trans. Power Electron. 2013, 29, 5358–5369. [Google Scholar] [CrossRef]

- Son, G.; Huang, Z.; Li, Q.; Lee, F.C. Analysis and Control of Critical Conduction Mode High-Frequency Single-Phase Transformerless PV Inverter. IEEE Trans. Power Electron. 2021, 36, 13188–13199. [Google Scholar] [CrossRef]

- Lidow, A.; Strydom, J.; de Rooij, M.; Ma, Y. GaN Transistorsfor Efficient Power Conversion; Power Conversion Publications: El Seguno, CA, USA, 2012. [Google Scholar]

- Boutros, K.S.; Chu, R.; Hughes, B. GaN power electronics for automotive application. In Proceedings of the IEEE Energytech, 2012, Cleveland, OH, USA, 29–31 May 2012; pp. 1–4. [Google Scholar]

- Morita, T.; Tamura, S.; Anda, Y.; Ishida, M.; Uemoto, Y.; Ueda, T.; Tanaka, T.; Ueda, D. 99.3% Efficiency of three-phase inverter for motor drive using GaN-based Gate injection transistors. In Proceedings of the 2011 Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 6–11 March 2011; pp. 481–484. [Google Scholar]

- Tamura, S.; Anda, Y.; Ishida, M.; Uemoto, Y.; Ueda, T.; Tanaka, T.; Ueda, D. Recent advances in gan power switching devices. In Proceedings of the 2010 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Monterey, CA, USA, 3–6 October 2010; pp. 1–4. [Google Scholar]

- Zhao, C.; Trento, B.; Jiang, L.; Jones, E.A.; Liu, B.; Zhang, Z.; Costinett, D.; Wang, F.F.; Tolbert, L.M.; Jansen, J.F.; et al. Design and implementation of a gan-based, 100-khz, 102-w/in3 single-phase inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 824–840. [Google Scholar] [CrossRef]

- Wang, K.; Yang, X.; Wang, L.; Jain, P. Instability Analysis and Oscillation Suppression of Enhancement-Mode GaN Devices in Half-Bridge Circuits. IEEE Trans. Power Electron. 2017, 33, 1585–1596. [Google Scholar]

- Zhang, Y.; Li, J.; Wang, J. Investigations on Driver and Layout for Paralleled GaN HEMTs in Low Voltage Application. IEEE Access 2019, 7, 179134–179142. [Google Scholar] [CrossRef]

- Jones, E.A.; Wang, F.F.; Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [Google Scholar] [CrossRef]

- Mu, M.; Lee, F.C. Design and Optimization of a 380–12V High-Frequency, High-Current LLC Converter with GaN Devices and Planar Matrix Transformers. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 854–862. [Google Scholar]

- Liu, Z.; Lee, F.C.; Li, Q.; Yang, Y. Design of GaN-based MHz totem-Pole PFC rectifier. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 799–807. [Google Scholar] [CrossRef]

- Huang, X.; Lee, F.C.; Li, Q.; Du, W. High-Frequency high-efficiency GaN-based interleaved crm bidirectional buck/boost converter with inverse coupled inductor. IEEE Trans. Power Electron. 2016, 31, 4343–4352. [Google Scholar] [CrossRef]

- Zhang, L.; Born, R.; Zhao, X.; Lai, J.S. A high efficiency inverter design for Google little box challenge. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 319–322. [Google Scholar]

- Morsy, A.S.; Bayern, M.; Enjeti, P. High power density single-phase inverter using GaN FETS and active power decoupling for Google little box challenge. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 323–327. [Google Scholar]

- Liu, Z.; Huang, X.; Mu, M.; Yang, Y.; Lee, F.C.; Li, Q. Design and evaluation of GaN-based dual-phase interleaved MHz critical mode PFC converter. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 611–616. [Google Scholar]

- Zhang, X.; Yao, C.; Lu, X.; Davidson, E.; Sievers, M.; Scott, M.J.; Xu, P.; Wang, J. A GaN transistor based 90W AC/DC adapter with a buck-PFC stage and an isolated Quasi-switched-capacitor DC/DC stage. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition, Fort Worth, TX, USA, 16–20 March 2014. [Google Scholar]

- Zhao, X.; Yeh, C.S.; Zhang, L.; Lai, J.S.; Labella, T. A 2-MHz wide-input hybrid resonant converter with ultra-compact planar coupled inductor for low power integrated on-chip applications. IEEE Trans. Ind. Appl. 2018, 54, 376–387. [Google Scholar] [CrossRef]

- Jenkins, L.L.; Wilson, C.G.; Moses, J.D.; Aggas, J.M.; Rhea, B.K.; Dean, R.N. The impact of parallel GaN HEMTs on efficiency of a 12-to-1 V buck converter. In Proceedings of the 2013 IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Columbus, OH, USA, 27–29 October 2013; pp. 197–200. [Google Scholar]

- Wu, Y.F. Paralleling high-speed GaN power HEMTs for quadrupled power output. In Proceedings of the Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 211–214. [Google Scholar]

- Zhu, T.; Zhuo, F.; Zhao, F.; Wang, F.; Zhao, T. Quantitative Model-Based False Turn-on Evaluation and Suppression for Cascode GaN Devices in Half-Bridge Applications. IEEE Trans. Power Electron. 2019, 34, 10166–10179. [Google Scholar] [CrossRef]

- Zhao, F.; Li, Y.; Chen, Z.; Yang, S.; Chen, J. Negative Conductance Modeling and Stability Analysis of High-frequency Oscillation Based on Cascode GaN Circuits. IEEE Access 2020, 8, 114100–114111. [Google Scholar] [CrossRef]

- Lu, J.; Bai, H.; Brown, A.; McAmmond, M.; Chen, D.; Styles, J. Design consideration of gate driver circuits and PCB parasitic parameters of paralleled E-mode GaN HEMTs in zero-voltage-switching applications. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 529–535. [Google Scholar]

- Yajing, Z.; Jiuhe, W.; Hong, L.; Lijie, W.; Yan, L.; Zheng, T.Q. The drive circuit design for paralleling operation of enhancement GaN HEMT in an isolated DC-DC converter. In Proceedings of the 2018 IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Xi’an, China, 16–18 May 2018. [Google Scholar]

- Li, H.; Munk-Nielsen, S.; Wang, X.; Maheshwari, R.; Beczkowski, S.; Uhrenfeldt, C.; Franke, W.-T. Influences of Device and Circuit Mismatches on Paralleling Silicon Carbide MOSFETs. IEEE Trans. Power Electron. 2015, 31, 621–634. [Google Scholar] [CrossRef]

- Pajnić, M.; Pejović, P.; Despotović, Ž.; Lazić, M.; Skender, M. Characterization and gate drive design of high voltage cascode GaN HEMT. In Proceedings of the 2017 International Symposium on Power Electronics (Ee), Novi Sad, Serbia, 19–21 October 2017; pp. 1–5. [Google Scholar]

- Efthymiou, L.; Camuso, G.; Longobardi, G.; Chien, T.; Chen, M.; Udrea, F. On the source of oscillatory behavior during switching of power enhancement mode GaN HEMTs. Energies 2017, 10, 407. [Google Scholar] [CrossRef]

- Chen, N.; Chimento, F.; Nawaz, M.; Wang, L. Dynamic characterization of parallel-connected high-power IGBT modules. IEEE Trans. Ind. Appl. 2015, 51, 539–546. [Google Scholar] [CrossRef]

- Wang, G.; Mookken, J.; Rice, J.; Schupbach, M. Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications. In Proceedings of the Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 16–20 March 2014; pp. 1478–1483. [Google Scholar]

- Liu, Z.; Huang, X.; Lee, F.C.; Li, Q. Simulation model development and verification for high voltage GaN HEMT in cascode structure. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 3579–3586. [Google Scholar]

- Huang, X.; Li, Q.; Liu, Z.; Lee, F.C. Analytical Loss Model of High Voltage GaN HEMT in Cascode Configuration. IEEE Trans. Power Electron. 2014, 29, 2208–2219. [Google Scholar] [CrossRef]

- Mitova, R.; Ghosh, R.; Mhaskar, U.; Klikic, D.; Wang, M.-X.; Dentella, A. Investigations of 600-V GaN HEMT and GaN Diode for Power Converter Applications. IEEE Trans. Power Electron. 2013, 29, 2441–2452. [Google Scholar] [CrossRef]

- Xu, Z.; Zhang, W.; Xu, F.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Investigation of 600 V GaN HEMTs for high efficiency and high temperature applications. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition, Fort Worth, TX, USA, 16–20 March 2014; pp. 131–136. [Google Scholar]

- Buetow, S.; Herzer, R. Characterization of GaN-HEMT in cascode topology and comparison with state of the art-power devices. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 196–199. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Y.; Li, J.; Wang, J.; Zheng, T.Q.; Jia, P. Dynamic-State Analysis of Inverter Based on Cascode GaN HEMTs for PV Application. Energies 2022, 15, 7791. https://doi.org/10.3390/en15207791

Zhang Y, Li J, Wang J, Zheng TQ, Jia P. Dynamic-State Analysis of Inverter Based on Cascode GaN HEMTs for PV Application. Energies. 2022; 15(20):7791. https://doi.org/10.3390/en15207791

Chicago/Turabian StyleZhang, Yajing, Jianguo Li, Jiuhe Wang, Trillion Q. Zheng, and Pengyu Jia. 2022. "Dynamic-State Analysis of Inverter Based on Cascode GaN HEMTs for PV Application" Energies 15, no. 20: 7791. https://doi.org/10.3390/en15207791

APA StyleZhang, Y., Li, J., Wang, J., Zheng, T. Q., & Jia, P. (2022). Dynamic-State Analysis of Inverter Based on Cascode GaN HEMTs for PV Application. Energies, 15(20), 7791. https://doi.org/10.3390/en15207791