Seven-Level Inverter with Reduced Switches for PV System Supporting Home-Grid and EV Charger

Abstract

1. Introduction

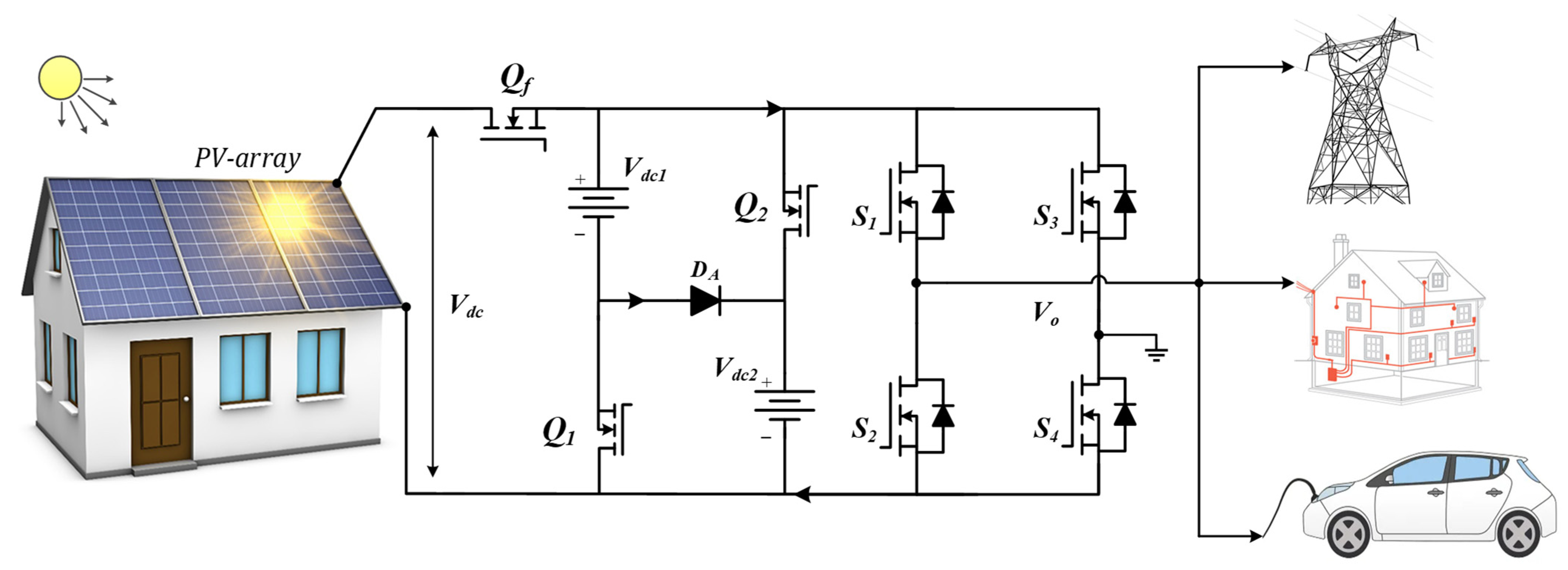

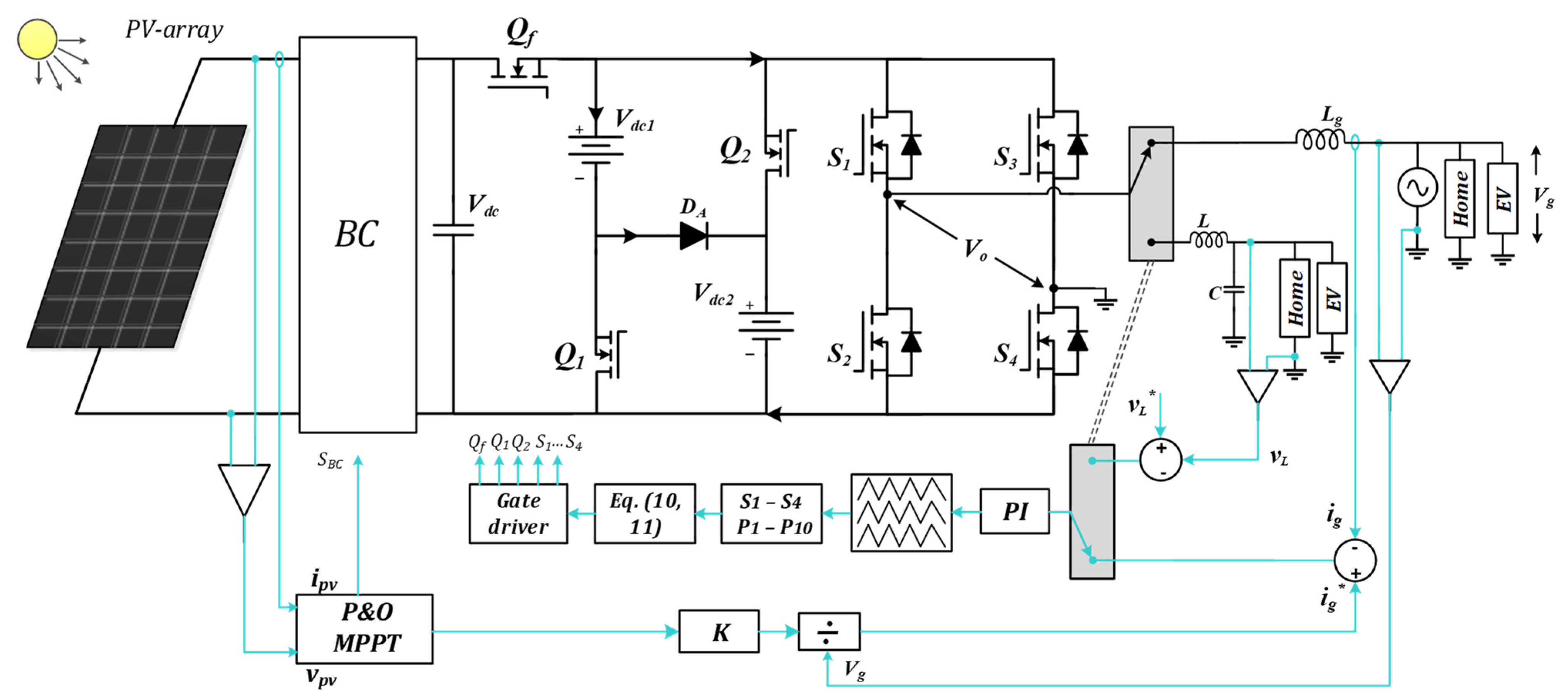

2. Proposed Multilevel PWM Inverter

2.1. Circuit Configuration and Operation Principal

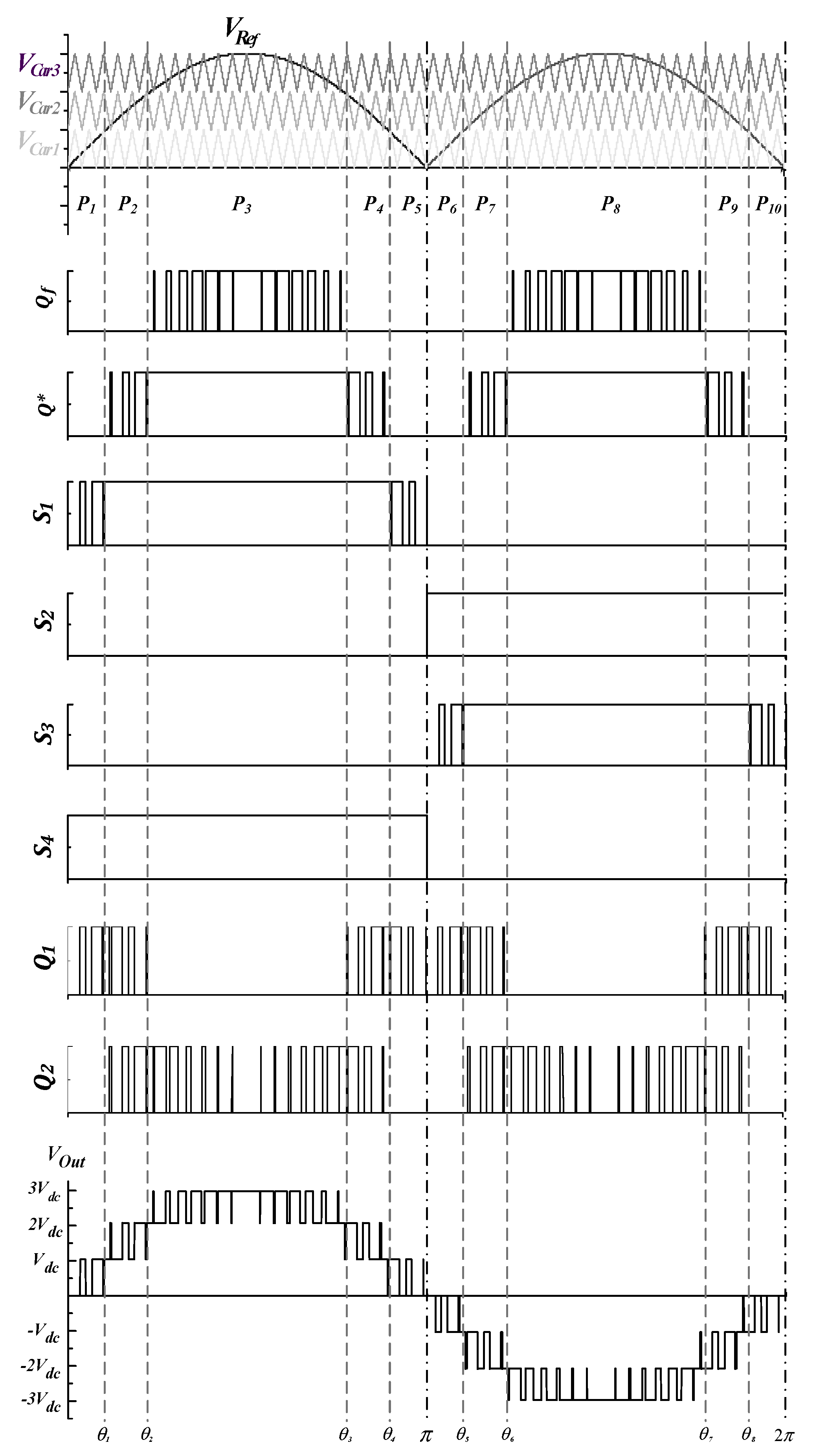

- Mode 1, the series switch (Qf) is ON to connect the DC-source Vdc to the front-end of H-bridge circuit. By switching-ON of the two switches S1 and S4, the inverter output voltage becomes +Vdc. At the same time, the two batteries (Vdc1 and Vdc2) charge through the diode (DA), as described in Figure 3a. Then, the reverse current path is illustrated in Figure 3b.

- Mode 2, switching-OFF Qf isolates the DC supply. At the same time, the switch (Q2) is turned on to apply a voltage of 2Vdc/3 to the H-bridge circuit and the second battery is disconnected from the circuit and diode DA is reversed. Turning-ON switches S1 and S4 of the main inverter results in generating output-voltage of positive +2Vdc/3, as clarified in Figure 3c. The reverse current path is depicted in Figure 3d.

- Mode 3, the series switch (Qf) as well as (Q2) are OFF-stated. Switch (Q1) is turned-ON to apply a DC-voltage of Vdc/3 to the H-bridge circuit. Similarly, turning-ON switches S1 and S4 of main circuit synthesizes output-voltage of +Vdc/3, as depicted in Figure 3e. The reverse current path is shown in Figure 3f.

- Mode 4, the zero output-voltage can be generated by voltage cancellation through the main H-bridge inverter. Voltage cancellation occurs by switching-ON (S1 and S3) or (S2 and S4) as shown in Figure 3g,h.

- Mode 5, the series switch (Qf) as well as (Q2) are OFF-stated same as to mode (3). The switch (Q1) is turned-ON to deliver DC voltage of Vdc/3 to H-Bridge input side. Turning-ON switches S2 and S3 of the main inverter generates an output-voltage of −Vdc/3, as shown in Figure 3i, where the reverse current path is depicted in Figure 3j.

- Mode 6, turning-OFF the series switch (Qf) and switching-ON (Q2) delivers a voltage of 2Vdc/3 to the H-bridge inverter similar to Figure 3c. At the same time, switching-ON switches (S2 and S3) of the main inverter synthesizes a negative output-voltage of (−2Vdc/3), as clarified in Figure 3k. The reverse current path is portrayed in Figure 3l.

- Mode 7, turning-ON the series switch (Qf) applies the total DC-voltage Vdc to front-end of H-Bridge inverter. By turning-ON the two switches S2 and S3, MLI output-voltage becomes −Vdc. At the same time, the two batteries (Vdc1 and Vdc2) are charging in series through diode (DA) similar to mode (1), as shown in Figure 3m. Besides, the current path of the reverse direction is shown in Figure 3n.

2.2. The Switching Patterns and Control Strategy

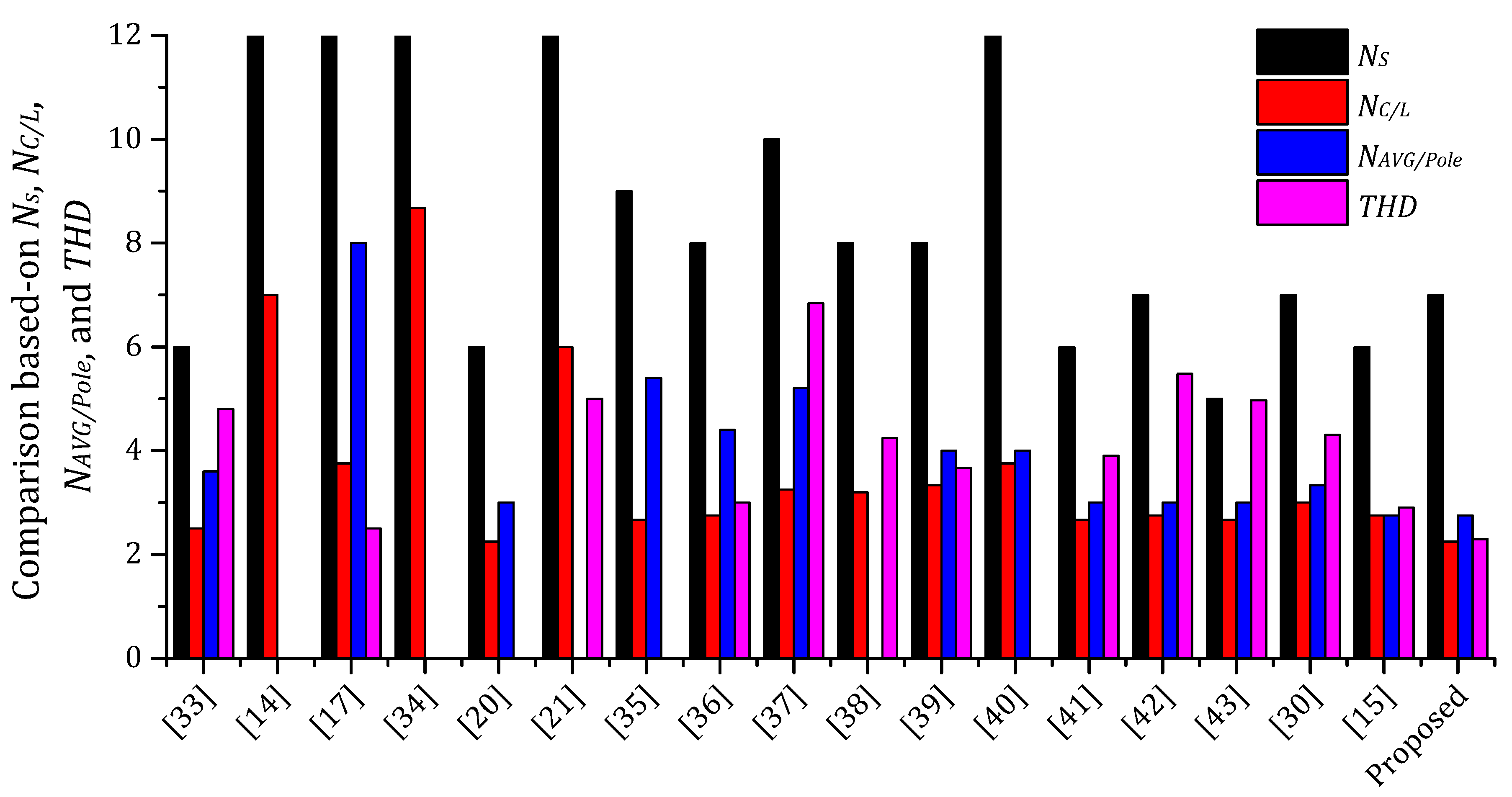

3. Comparative Study

- NC/L: Components per pole of output voltage level.

- NPole: Number of voltage levels per pole.

- NC: Number of capacitors.

- ND: Number of diodes.

- NS: Number of switching devices.

- NPS: Number of DC power supplies.

- NT: Number of transformers.

- NX: Number of additional components.

- Nlevel(0): number of active switches for the zero output-voltage synthesis.

- Nlevel(1): number of active switches for the first output-voltage level synthesis.

- Nlevel(2): number of active switches number for the second output-voltage level synthesis.

4. MLI Control Scheme

5. Simulation and Experimental Validations

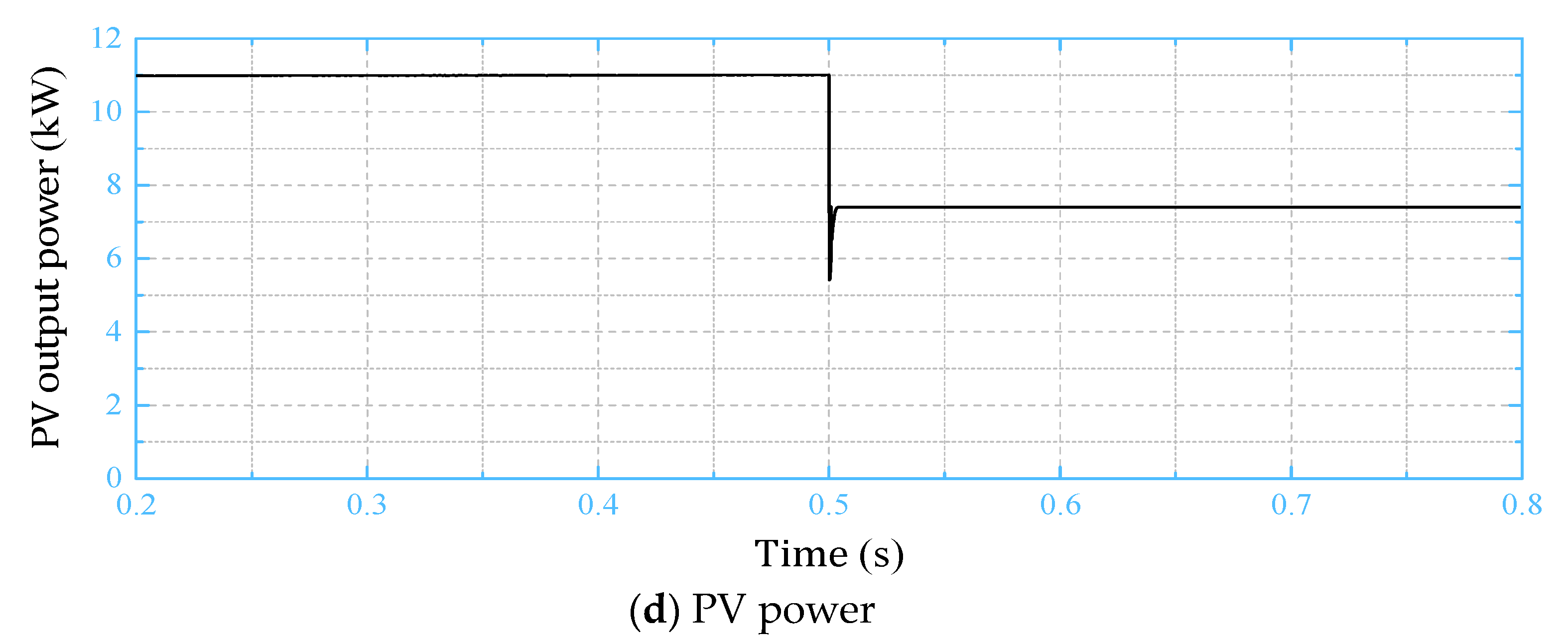

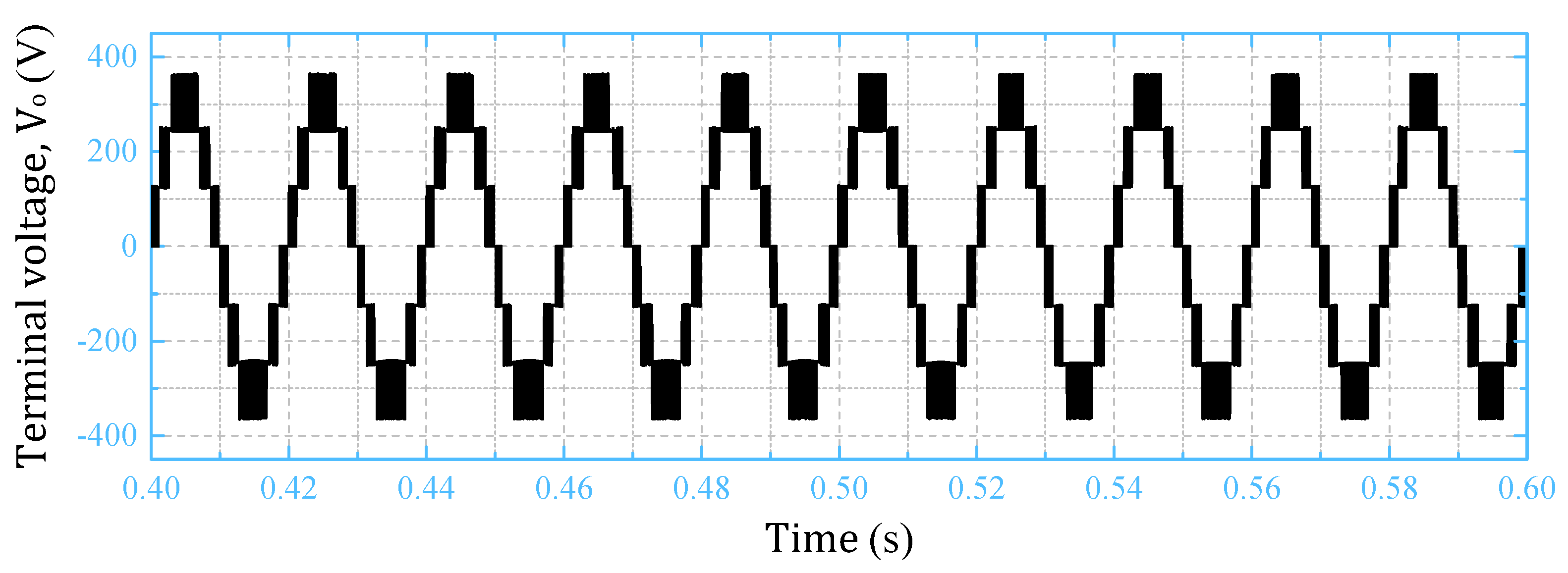

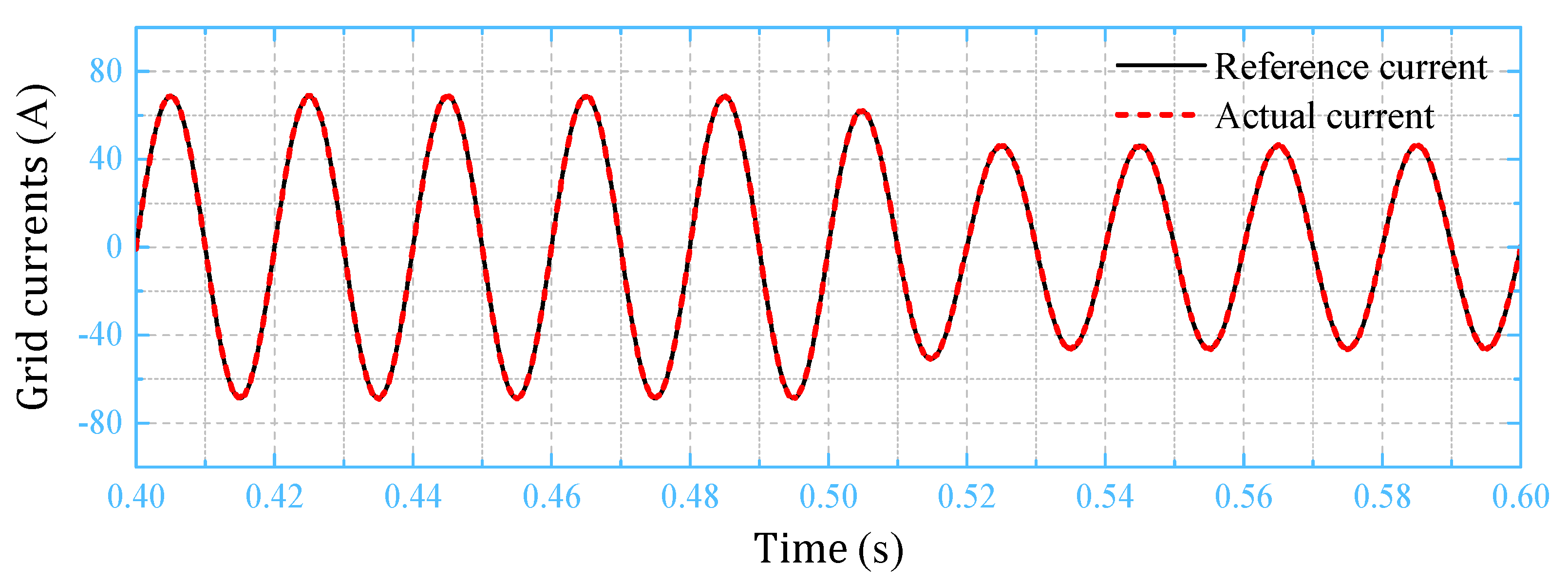

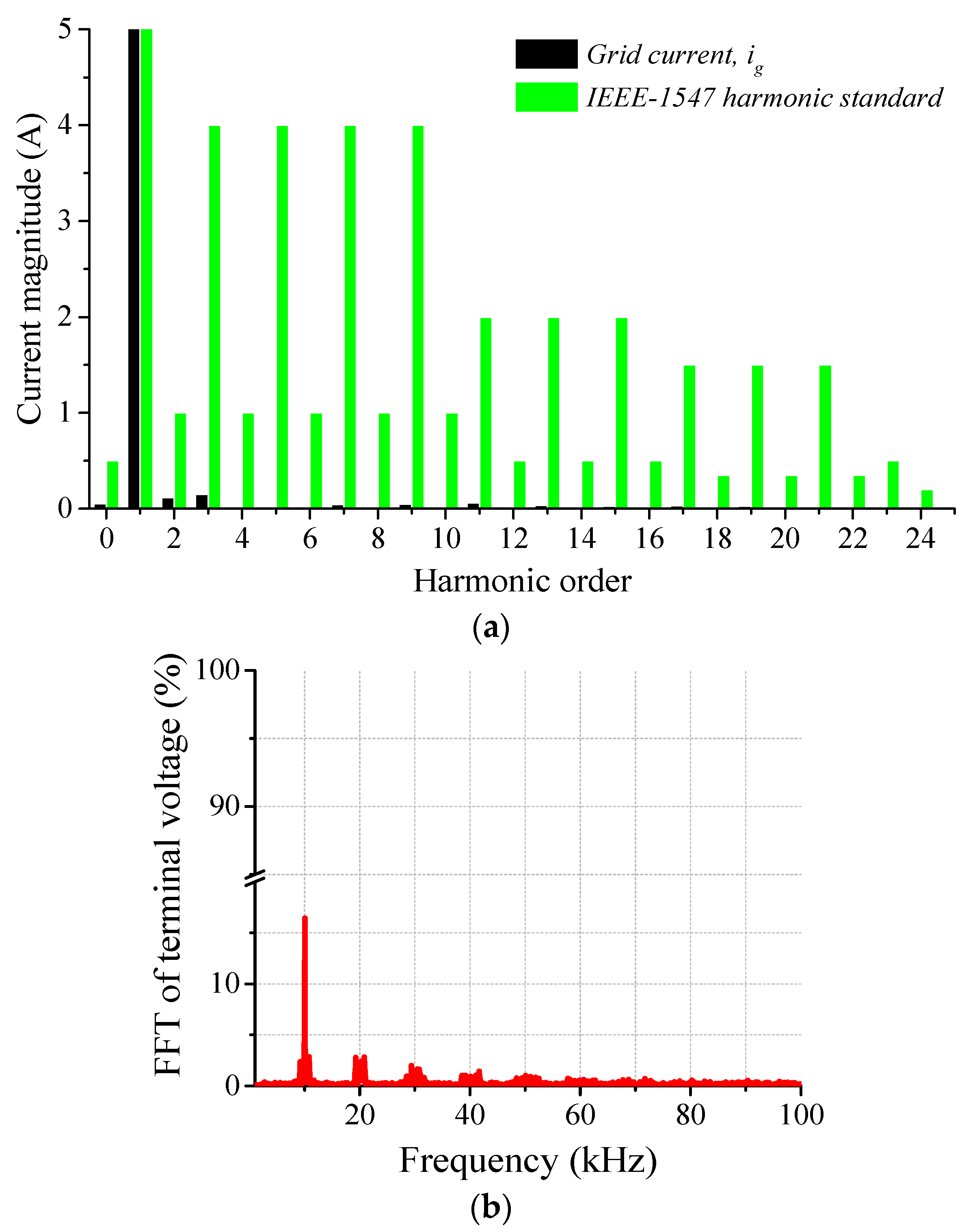

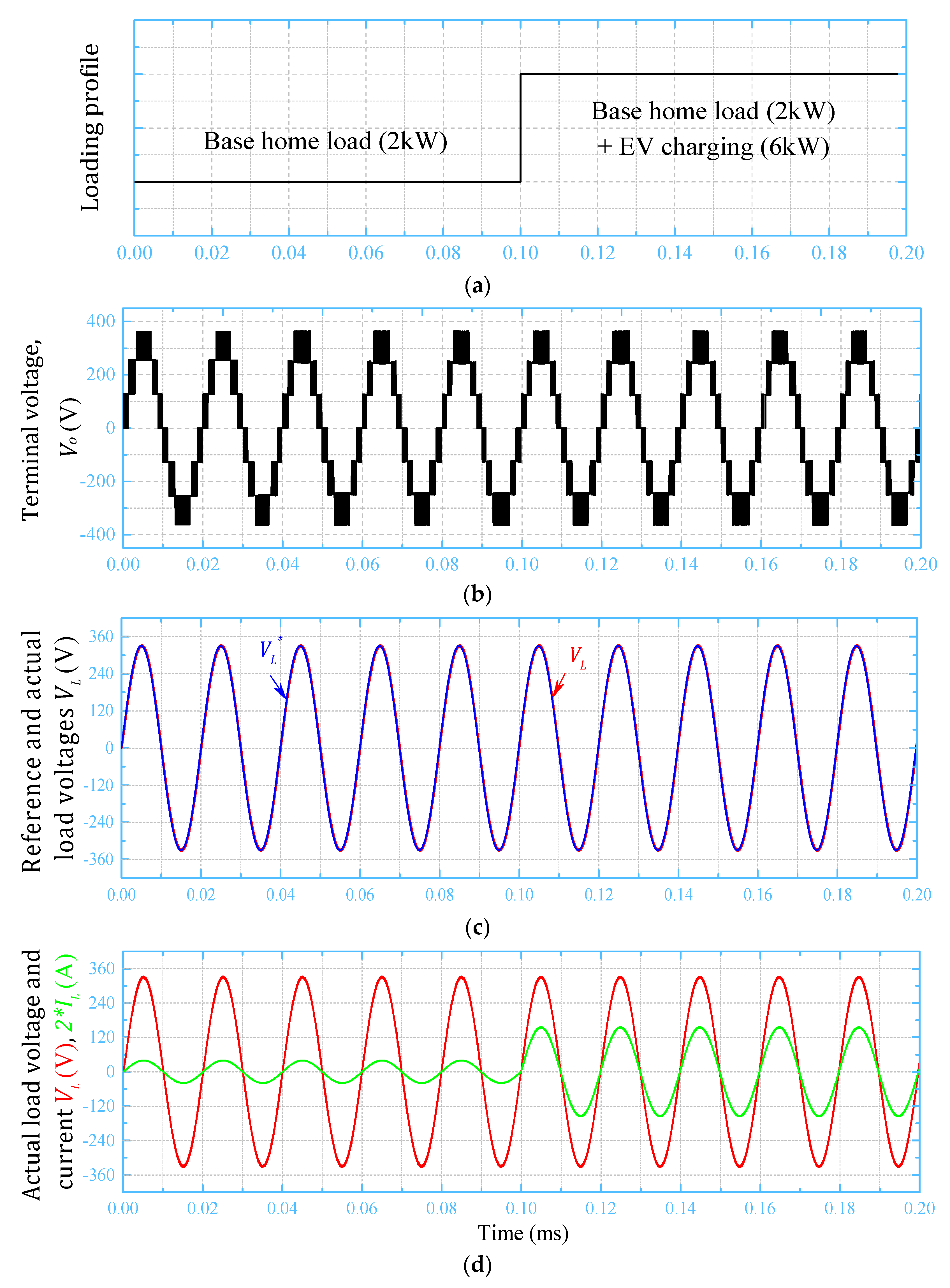

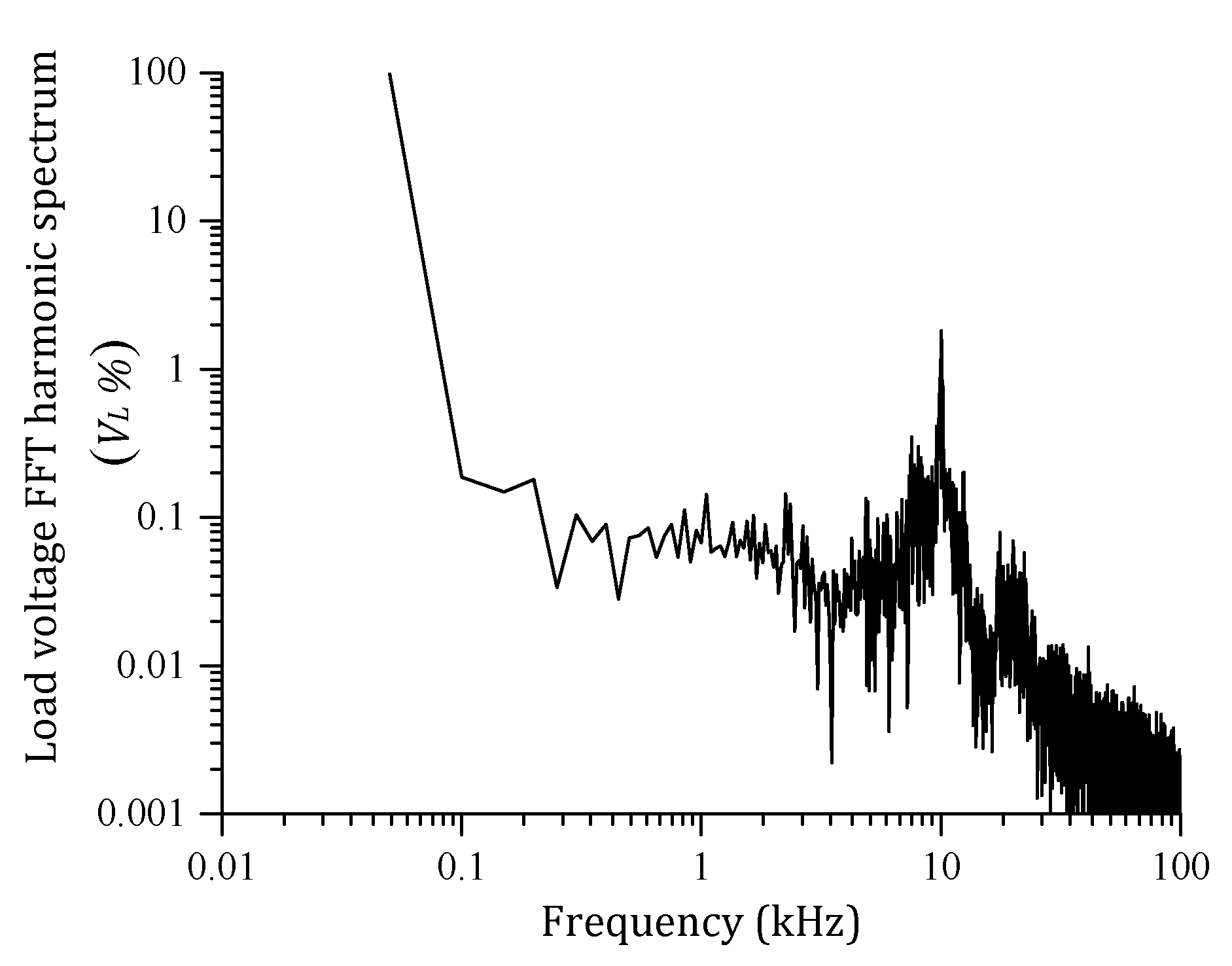

5.1. Simulation Results

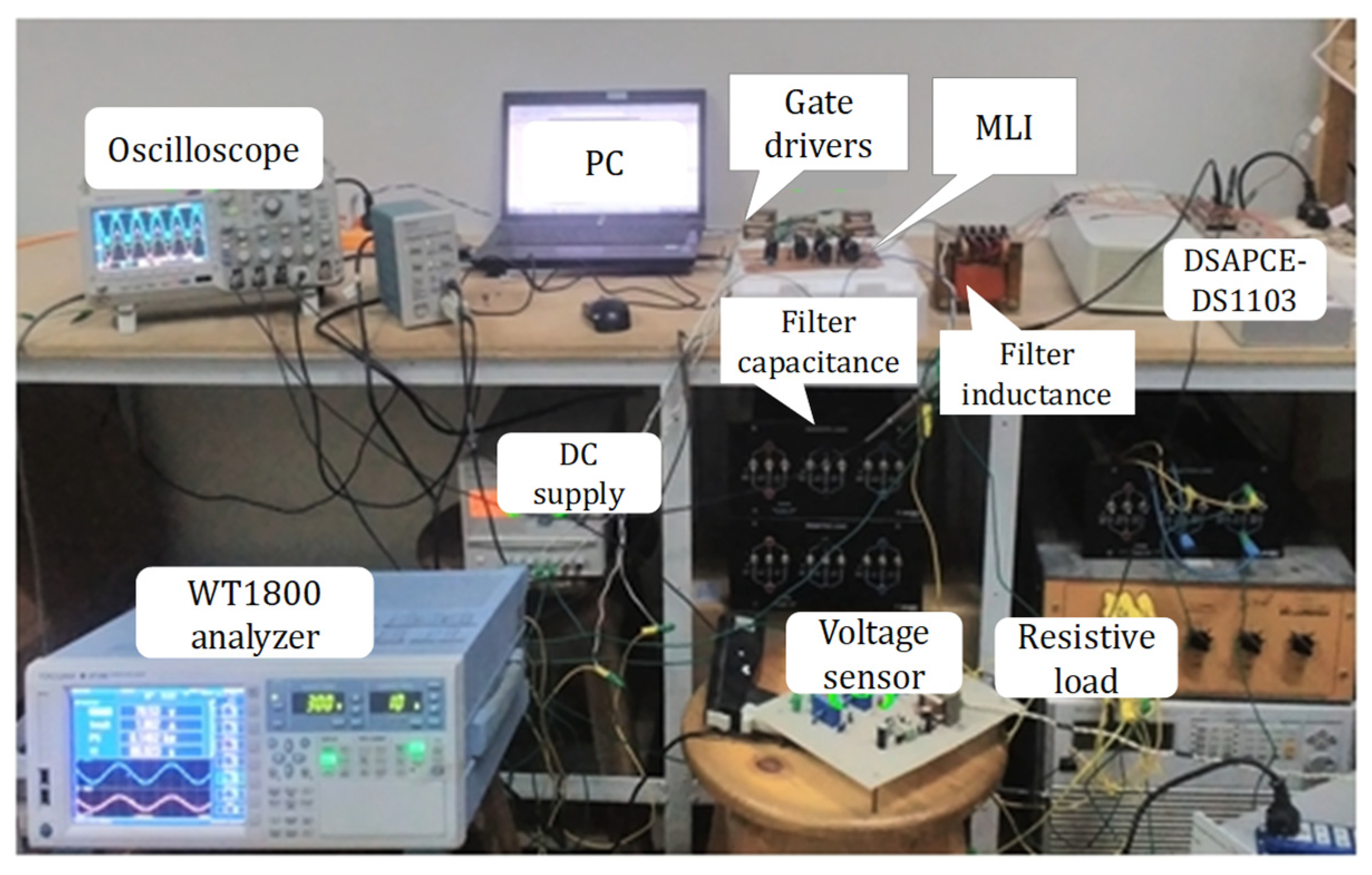

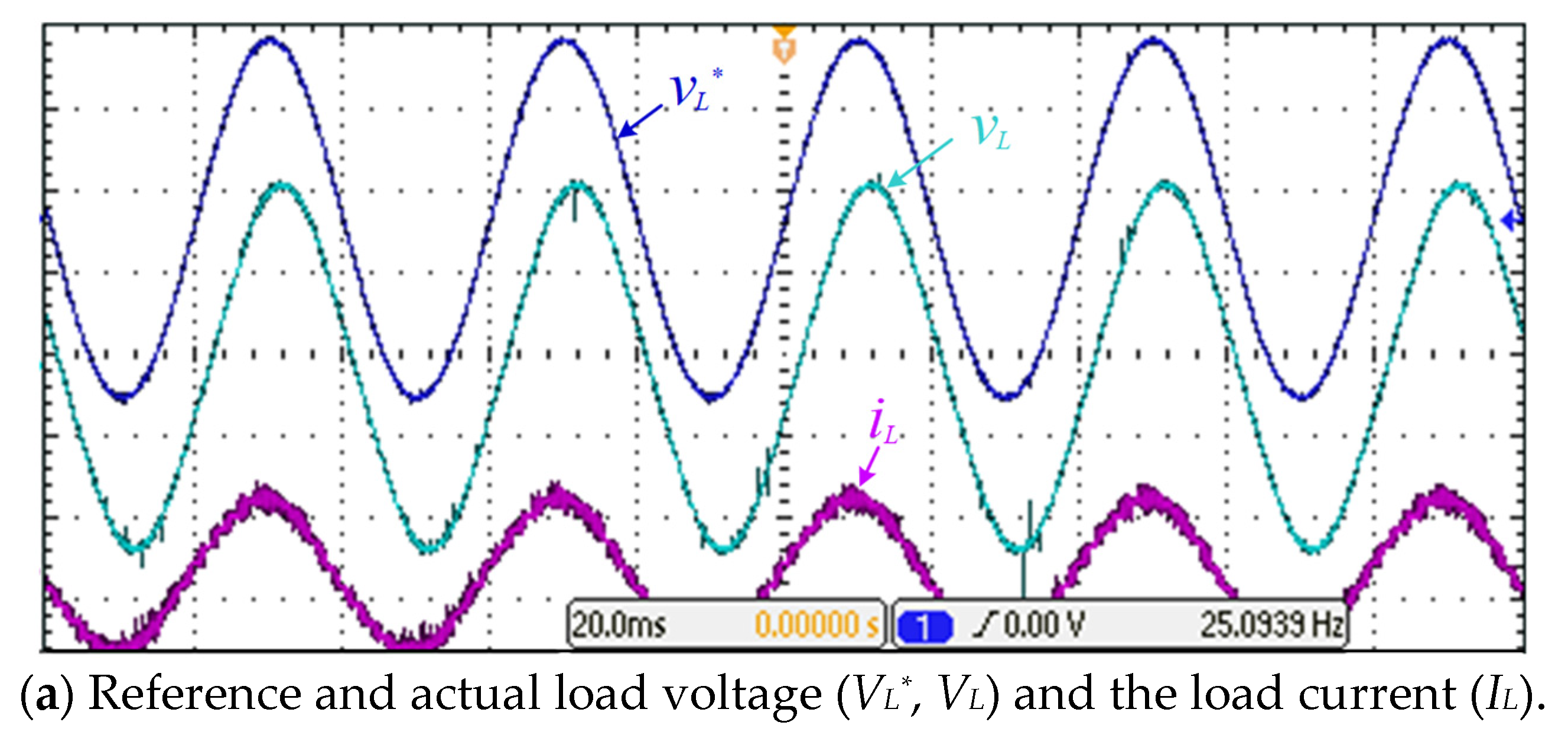

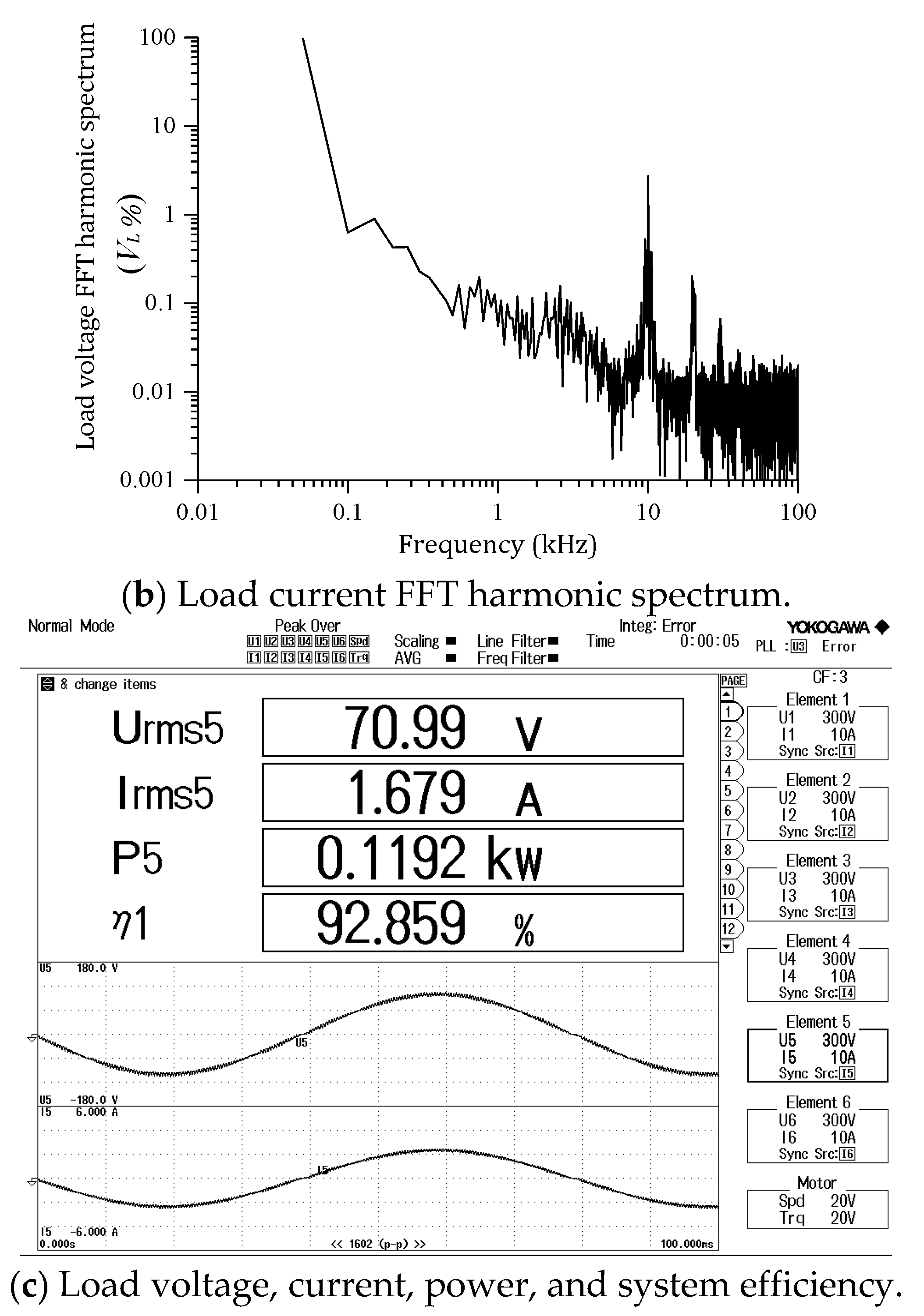

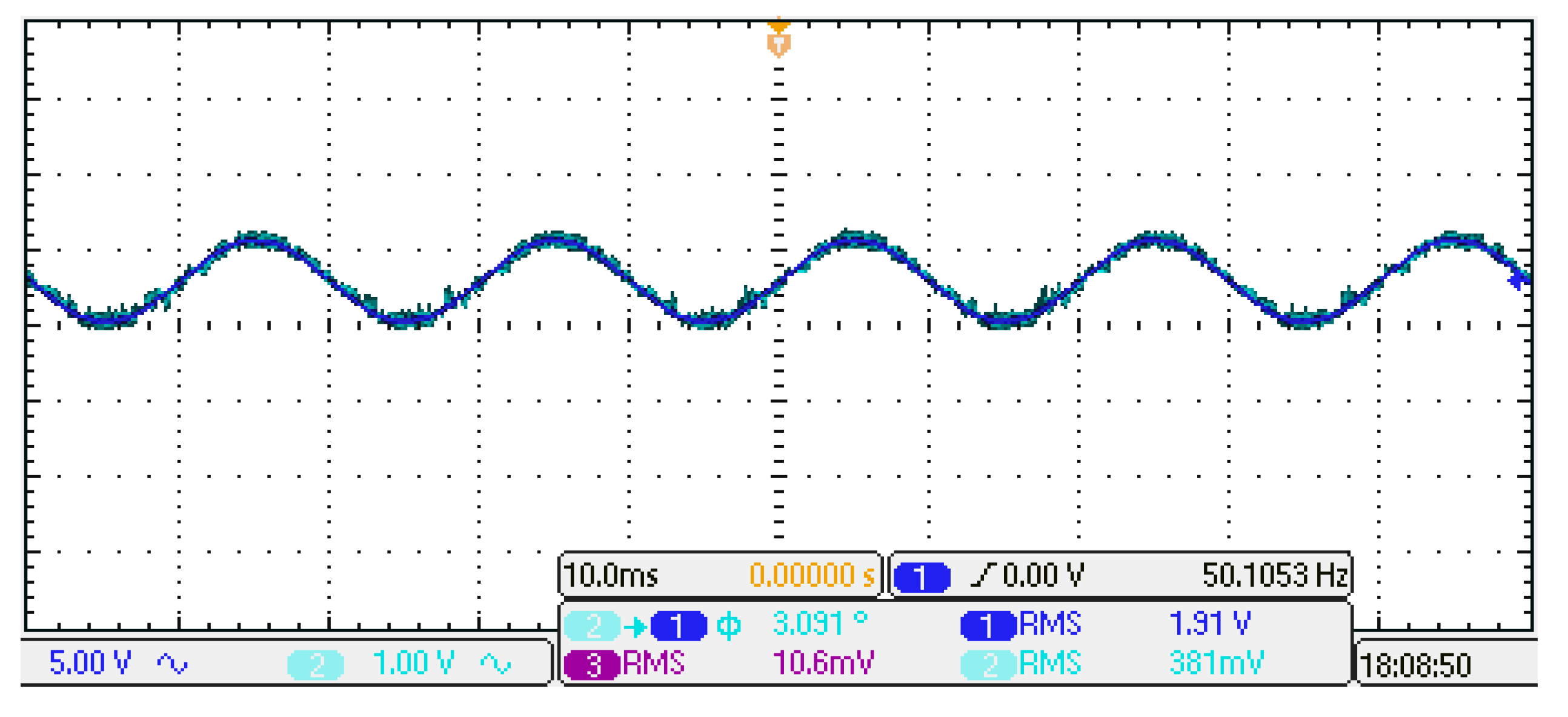

5.2. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| Ma | Modulation index |

| NPS | Number of DC power supplies |

| NS | Number of switching devices |

| ND | Number of diodes |

| NC | Capacitors Number |

| NT | Transformers Number |

| NX | Number of other additional components |

| NPole | Voltage levels number per pole |

| NC/L | Number of components per level |

| NAVG/Pole | Average number of ON-switches per pole |

| Am, Ac | Reference and carrier signal amplitudes |

| Pn | Modes of operation |

| θn | Switching angle |

| PV | Photovoltaic |

| EV | Electric vehicle |

| MLI | Multilevel inverter |

| THD | Total harmonic distortion |

| EMI | Electromagnetic interface |

| CHB-MLI | Cascaded H-bridge MLI |

| NPC-MLI | Neutral Point Clamped MLI |

| FC-MLI | Flying Capacitors MLI |

| SPWM | Sinusoidal pulse-width-modulation |

| MPPT | Maximum power point tracking |

| BC | Boost converter |

| SHE-PWM | Selective harmonic elimination PWM |

| P&O | Perturb and observe |

| FFT | Fast Fourier transform |

| DER | Distributed energy resources |

References

- Solangi, K.; Islam, M.; Saidur, R.; Rahim, N.; Fayaz, H. A review on global solar energy policy. Renew. Sustain. Energy Rev. 2011, 15, 2149–2163. [Google Scholar] [CrossRef]

- Ali, A.I.; Sayed, M.A.; Mohamed, E.E. Modified efficient perturb and observe maximum power point tracking technique for grid-tied PV system. Int. J. Electr. Power Energy Syst. 2018, 99, 192–202. [Google Scholar] [CrossRef]

- Sayed, M.A.; Mohamed, E.; Ali, A. Maximum Power Point Tracking Technique for Grid tie PV System. In Proceedings of the 7th International Middle-East Power System Conference, (MEPCON’15), Mansoura University, Dakahlia Governorate, Egypt, 15–17 December 2015. [Google Scholar]

- Ali, A.I.; Mohamed, E.E.; Sayed, M.A.; Saeed, M.S. Novel single-phase nine-level PWM inverter for grid connected solar PV farms. In Proceedings of the 2018 International Conference on Innovative Trends in Computer Eng. (ITCE), Aswan, Egypt, 19–21 February 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 345–440. [Google Scholar]

- Youssef, A.-R.; Ali, A.I.; Saeed, M.S.; Mohamed, E.E. Advanced multi-sector P&O maximum power point tracking technique for wind energy conversion system. Int. J. Electr. Power Energy Syst. 2019, 107, 89–97. [Google Scholar]

- Feloups, C.E.; Ali, A.I.; Mohamed, E.E. Design of single-phase seven-level inverter with reduced number of switching devices for PV applications. In Proceedings of the 2017 Nineteenth International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 19–21 December 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 817–822. [Google Scholar]

- Qiao, Q.; Zhao, F.; Liu, Z.; He, X.; Hao, H. Life cycle greenhouse gas emissions of Electric Vehicles in China: Combining the vehicle cycle and fuel cycle. Energy 2019, 177, 222–233. [Google Scholar] [CrossRef]

- Deb, S.; Tammi, K.; Kalita, K.; Mahanta, P. Impact of electric vehicle charging station load on distribution network. Energies 2018, 11, 178. [Google Scholar] [CrossRef]

- Ali, A.I.; Mohamed, E.E.; Youssef, A.-R. MPPT algorithm for grid-connected photovoltaic generation Syst. via model predictive controller. In Proceedings of the 2017 Nineteenth International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 19–21 December 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 895–900. [Google Scholar]

- Van Der Kam, M.; van Sark, W. Smart charging of electric vehicles with photovoltaic power and vehicle-to-grid technology in a microgrid; a case study. Appl. Energy 2015, 152, 20–30. [Google Scholar] [CrossRef]

- Colmenar-Santos, A.; de Palacio-Rodriguez, C.; Rosales-Asensio, E.; Borge-Diez, D. Estimating the benefits of vehicle-to-home in islands: The case of the Canary Islands. Energy 2017, 134, 311–322. [Google Scholar] [CrossRef]

- Pan, L.; Zhang, C. An integrated multifunctional bidirectional AC/DC and DC/DC converter for electric vehicles applications. Energies 2016, 9, 493. [Google Scholar] [CrossRef]

- Ali, A.I.M.; Sayed, M.A.; Takeshita, T. Isolated single-phase single-stage DC-AC cascaded transformer-based multilevel inverter for stand-alone and grid-tied applications. Int. J. Electr. Power Energy Syst. 2021, 125, 106534. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Ali, A.I.M.; Sayed, M.A.; Takeshita, T.; Hassan, A.M.; Azmy, A.M. A single-phase modular multilevel inverter based on controlled DC-cells under two SPWM techniques for renewable energy applications. Int. Trans. Electr. Energy Syst. 2021, 31, e12599. [Google Scholar] [CrossRef]

- Marchesoni, M.; Mazzucchelli, M.; Tenconi, S. A nonconventional power converter for plasma stabilization. IEEE Trans. Power Electron. 1990, 5, 212–219. [Google Scholar] [CrossRef]

- Vazquez, S.; Leon, J.I.; Carrasco, J.M.; Franquelo, L.G.; Galvan, E.; Reyes, M.; Sanchez, J.A.; Dominguez, E. Analysis of the power balance in the cells of a multilevel cascaded H-bridge converter. IEEE Trans. Ind. Electron. 2009, 57, 2287–2296. [Google Scholar] [CrossRef]

- Barros, J.D.; Silva, J.F.A.; Jesus, É.G. Fast-predictive optimal control of NPC multilevel converters. IEEE Trans. Ind. Electron. 2012, 60, 619–627. [Google Scholar] [CrossRef]

- Pouresmaeil, E.; Montesinos-Miracle, D.; Gomis-Bellmunt, O. Control scheme of three-level NPC inverter for integration of renewable energy resources into AC grid. IEEE Syst. J. 2011, 6, 242–253. [Google Scholar] [CrossRef]

- McGrath, B.P.; Holmes, D.G. Analytical determination of the capacitor voltage balancing dynamics for three-phase flying capacitor converters. IEEE Trans. Ind. Appl. 2009, 45, 1425–1433. [Google Scholar] [CrossRef]

- Zhang, L.; Waite, M.J.; Chong, B. Three-phase four-leg flying-capacitor multi-level inverter-based active power filter for unbalanced current operation. IET Power Electron. 2013, 6, 153–163. [Google Scholar] [CrossRef]

- Hinago, Y.; Koizumi, H. A single-phase multilevel inverter using switched series/parallel dc voltage sources. IEEE Trans. Ind. Electron. 2009, 57, 2643–2650. [Google Scholar] [CrossRef]

- Babaei, E. A cascade multilevel converter topology with reduced number of switches. IEEE Trans. Power Electron. 2008, 23, 2657–2664. [Google Scholar] [CrossRef]

- Li, Z.; Wang, P.; Li, Y.; Gao, F. A novel single-phase five-level inverter with coupled inductors. IEEE Trans. Power Electron. 2011, 27, 2716–2725. [Google Scholar] [CrossRef]

- Gupta, K.K.; Jain, S. Multilevel inverter topology based on series connected switched sources. IET Power Electron. 2013, 6, 164–174. [Google Scholar] [CrossRef]

- Babaei, E.; Laali, S.; Bayat, Z. A single-phase cascaded multilevel inverter based on a new basic unit with reduced number of power switches. IEEE Trans. Ind. Electron. 2014, 62, 922–929. [Google Scholar] [CrossRef]

- Vidales, B.; Monroy-Morales, J.L.; Rodríguez-Rodriguez, J.; Madrigal, M.; Torres-Lucio, D. A transformerless topology for a micro inverter with elevation factor of 1: 10 for photovoltaic applications. Int. J. Electr. Power Energy Syst. 2019, 109, 504–512. [Google Scholar] [CrossRef]

- Babaei, E.; Kangarlu, M.F.; Sabahi, M. Extended multilevel converters: An attempt to reduce the number of independent DC voltage sources in cascaded multilevel converters. IET Power Electron. 2014, 7, 157–166. [Google Scholar] [CrossRef]

- Ahmed, T.A.; Mohamed, E.E.; Youssef, A.-R.; Ibrahim, A.; Saeed, M.S.; Ali, A.I. Three phase modular multilevel inverter-based multi-terminal asymmetrical DC inputs for renewable energy applications. Eng. Sci. Technol. Int. J. 2020, 23, 831–839. [Google Scholar] [CrossRef]

- Ali, A.I.; Sayed, M.A.; Mohamed, E.E.; Azmy, A.M. Advanced single-phase nine-level converter for the integration of multiterminal DC supplies. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 7, 1949–1958. [Google Scholar] [CrossRef]

- Ali, A.I.M.; Sayed, M.A.; Takeshita, T. Analysis and Design of High-Power Single-Stage Three-Phase Differential-Based Flyback Inverter for Photovoltaic Applications. In Proceedings of the 2020 22nd European Conference on Power Electronics and Applications (EPE’20 ECCE Europe), Lyon, France, 7–11 September 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1–8. [Google Scholar]

- Ali, A.I.M.; Sayed, M.A.; Takeshita, T. New Cascaded-Transformers Multilevel Inverter for Renewable Distribution Systems. In Proceedings of the 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 3965–3971. [Google Scholar]

- Pereda, J.; Dixon, J. Cascaded multilevel converters: Optimal asymmetries and floating capacitor control. IEEE Trans. Ind. Electron. 2012, 60, 4784–4793. [Google Scholar] [CrossRef]

- Ali, A.I.; Mohamed, E.E.; Sayed, M.A.; Saeed, M.S.; Azmy, A.M. Design and Validation of a Single Phase Multilevel Inverter Utilizing Reduced Switches Number. In Proceedings of the 2018 Twentieth International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 18–20 December 2020; IEEE: Piscataway, NJ, USA, 2018; pp. 974–979. [Google Scholar]

- Wu, J.-C.; Wu, K.-D.; Jou, H.-L.; Chang, S.-K. Small-capacity grid-connected solar power generation system. IET Power Electron. 2014, 7, 2717–2725. [Google Scholar] [CrossRef]

- De, S.; Banerjee, D.; Gopakumar, K.; Ramchand, R.; Patel, C. Multilevel inverters for low-power application. IET Power Electron. 2011, 4, 384–392. [Google Scholar] [CrossRef]

- Kaliamoorthy, M.; Rajasekaran, V.; PraveenRaj, G. A novel single phase cascaded multilevel inverter for hybrid renewable energy sources. In Proceedings of the 2015 International Conference on Advanced Computing and Communication Systems, Haryana, India, 21–22 February 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 1–10. [Google Scholar]

- Hassan, A.M.; Yang, X.; Ali, A.I.M.; Ahmed, T.A.; Azmy, A.M. A Study of Level-Shifted PWM Single-phase 11-Level Multilevel Inverter. In Proceedings of the 2019 21st International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 17–19 December 2019; pp. 170–176. [Google Scholar]

- Rao, S.N.; Kumar, D.A.; Babu, C.S. New multilevel inverter topology with reduced number of switches using advanced modulation strategies. In Proceedings of the 2013 International Conference on Power, Energy and Control (ICPEC), Dindigul, India, 6–8 February 2013; IEEE: Piscataway, NJ, USA, 2013; pp. 693–699. [Google Scholar]

- Mudadla, D.; Sandeep, N.; Rao, G.R. Novel asymmetrical multilevel inverter topology with reduced number of switches for photovoltaic applications. In Proceedings of the 2015 International Conference on Computation of Power, Energy, Information and Communication (ICCPEIC), Melmaruvathur, India, 22–23 April 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 0123–0128. [Google Scholar]

- Ray, S.; Gupta, N.; Gupta, R.A. Hardware realization of proportional-resonant regulator based advanced current control strategy for cascaded H-bridge inverter based shunt active power filter. Int. Trans. Electr. Energy Syst. 2019, 29, e2714. [Google Scholar] [CrossRef]

- Sun, X.; Wang, B.; Zhou, Y.; Wang, W.; Du, H.; Lu, Z. A single DC source cascaded seven-level inverter integrating switched-capacitor techniques. IEEE Trans. Ind. Electron. 2016, 63, 7184–7194. [Google Scholar] [CrossRef]

- Noroozi, M.; Akbari, A.; Abrishamifar, A. A 5-level modified full-bridge stand-alone inverter with reduced number of switches. Int. Trans. Electr. Energy Syst. 2018, 28, e2638. [Google Scholar] [CrossRef]

- Ibrahim, S.A.; Palanimuthu, A.; Sathik, M.J. Symmetric switched diode multilevel inverter structure with minimised switch count. J. Eng. 2017, 2017, 469–478. [Google Scholar] [CrossRef]

- Jagabar Sathik, M.; Prabaharan, N.; Ibrahim, S.A.; Vijaykumar, K.; Blaabjerg, F. A new generalized switched diode multilevel inverter topology with reduced switch count and voltage on switches. Int. J. Circuit Theory Appl. 2020, 48, 619–637. [Google Scholar] [CrossRef]

- Ali, A.I.M.; Sayed, M.A.; Shawky, A.; Takeshita, T. Efficient Single-Stage Three-Phase Isolated Differential-Based Flyback Inverter with Selective Harmonic Compensation Strategy for Grid-Tied Applications. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1778–1785. [Google Scholar]

- Ali, A.I.M. Techniques for Photovoltaic Generation; South Valley University: Qena Governorate, Egypt, 2017. [Google Scholar]

- Mohamed, A.A.; Metwally, H.; El-Sayed, A.; Selem, S. Predictive neural network based adaptive controller for grid-connected PV systems supplying pulse-load. Sol. Energy 2019, 193, 139–147. [Google Scholar] [CrossRef]

- Mohamed, A.A.; El-Sayed, A.; Metwally, H.; Selem, S.I. Grid integration of a PV system supporting an EV charging station using Salp Swarm Optimization. Solar Energy 2020, 205, 170–182. [Google Scholar] [CrossRef]

- Teodorescu, R.; Liserre, M.; Rodriguez, P. Grid Converters for Photovoltaic and Wind Power Systms; John Wiley & Sons: Hoboken, NJ, USA, 2011; Volume 29. [Google Scholar]

| Comparison | Auxiliary Circuit Switching | Q* | Main Circuit Switching | Output-Voltage | |||||

|---|---|---|---|---|---|---|---|---|---|

| Qf | Q1 | Q2 | S1 | S2 | S3 | S4 | VOut | ||

| VCar1 < VRef | 1 | 1 | 1 | 1 | |||||

| VCar2 < VRef | 0 | ||||||||

| VCar3 < VRef | 0 | ||||||||

| VCar1 < VRef | 0 | 1 | 1 | 1 | |||||

| VCar2 < VRef | 0 | ||||||||

| VCar3 > VRef | 1 | ||||||||

| VCar1 < VRef | 0 | 0 | 1 | 1 | |||||

| VCar2 > VRef | 1 | ||||||||

| VCar3 > VRef | 0 | ||||||||

| VCar1 > VRef | 0 | 0 | 1 | 1 | 0 | ||||

| VCar2 > VRef | 0 | ||||||||

| VCar3 > VRef | 0 | ||||||||

| VCar1 > VRef | 0 | 0 | 1 | 1 | 0 | ||||

| VCar2 > VRef | 0 | ||||||||

| VCar3 > VRef | 0 | ||||||||

| VCar1 < VRef | 0 | 0 | 1 | 1 | |||||

| VCar2 > VRef | 1 | ||||||||

| VCar3 > VRef | 0 | ||||||||

| VCar1 < VRef | 0 | 1 | 1 | 1 | |||||

| VCar2 < VRef | 0 | ||||||||

| VCar3 > VRef | 1 | ||||||||

| VCar1 < VRef | 1 | 1 | 1 | 1 | |||||

| VCar2 < VRef | 0 | ||||||||

| VCar3 < VRef | 0 | ||||||||

| In Cited Paper: | NPole | NPS | NS | ND | NC | NT | NC/L | NAVG/Pole | THD (%) | Eff. (%) | PWM Technique | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Reference | Level | |||||||||||

| [35] | 7 | 4 | 2 | 6 | 2 | 0 | 0 | 2.5 | 3.6 | 4.8 | 94 | Fund. Frequency PWM |

| [14] | 5 | 3 | 1 | 12 | 6 | 2 | 0 | 7 | SPWM | |||

| [17] |

| 3 | 2 | 8 | 0 | 0 | 0 | 3.33 | Fund. Frequency PWM | |||

| 4 | 3 | 12 | 0 | 0 | 0 | 3.75 | 2.5 | -- | |||

| 5 | 4 | 16 | 0 | 0 | 0 | 4 | 8 | ||||

| [36] | 5 | 3 | 2 | 12 | 12 | 0 | 0 | 8.67 | MPC & SPWM | |||

| [20] |

| 3 | 1 | 4 | 0 | 1 | 0 | 2 | PSC-PWM | |||

| 4 | 1 | 6 | 0 | 2 | 0 | 2.25 | |||||

| 5 | 1 | 8 | 0 | 3 | 0 | 2.4 | 3 | ||||

| [21] | 5 | 3 | 1 | 12 | 0 | 5 | 0 | 6 | 5 | -- | 3D-PWM | |

| [37] | 6 | 0 | 9 | 4 | 3 | 0 | 2.67 | 5.4 | Fund. Frequency PWM | |||

| [38] |

| 3 | 2 | 6 | 0 | 0 | 0 | 2.67 | 2.67 | 3 | 88 | SPWM |

| 4 | 3 | 8 | 0 | 0 | 0 | 2.75 | |||||

| 5 | 4 | 10 | 0 | 0 | 0 | 2.8 | 4.4 | ||||

| [39] |

| 3 | 2 | 8 | 0 | 0 | 0 | 3.33 | 3.33 | SHE-PWM & SPWM | ||

| 4 | 3 | 10 | 0 | 0 | 0 | 3.25 | 6.84 | -- | |||

| 5 | 4 | 12 | 0 | 0 | 0 | 3.2 | 5.2 | ||||

| [40] | 5 | 4 | 8 | 4 | 0 | 0 | 3.2 | 4.24 | -- | Fund. Frequency PWM | ||

| [41] | 3 | 2 | 8 | 0 | 0 | 0 | 3.33 | 4 | 3.67 | -- | SHE-PWM & SPWM | |

| [42] | 4 | 1 | 12 | 0 | 2 | 0 | 3.75 | 4 | -- | 90 | CPS-SPWM | |

| [43] | 3 | 2 | 6 | 0 | 0 | 0 | 2.67 | 3 | 3.9 | -- | SPWM | |

| [44] | 4 | 3 | 7 | 1 | 0 | 0 | 2.75 | 3 | 5.48 | -- | SPWM | |

| [45] | 3 | 2 | 5 | 1 | 0 | 0 | 2.67 | 3 | 4.97 | -- | SPWM | |

| [30] |

| 4 | 3 | 7 | 2 | 0 | 0 | 3 | 3.33 | 4.3 | 84.5 | SPWM |

| 5 | 4 | 10 | 3 | 0 | 0 | 3.4 | 2.8 | 4 | 95 | ||

| [15] |

| 3 | 2 | 5 | 1 | 0 | 0 | 2.67 | 2.33 | 3 | 88.5 | Two SPWM |

| 4 | 3 | 6 | 2 | 0 | 0 | 2.75 | 2.75 | 2.9 | 90.3 | ||

| 5 | 4 | 7 | 3 | 0 | 0 | 2.8 | 3.2 | ||||

| Proposed MLI | 7-level | 4 | 1 | 7 | 1 | 0 | 0 | 2.25 | 2.75 | 3.73 | 92.86 | SPWM |

| Maximum Power (Pmpp) | 220 (W) |

| Voltage at MPP (Vmpp) | 47 (V) |

| Current at MPP (Impp) | 4.68 (A) |

| Open circuit voltage (Voc) | 58.8 (V) |

| Short circuit current (Isc) | 5.01 (A) |

| Maximum Power (Pmpp) | 11 (kW) |

| Voltage at MPP (Vmpp) | 235 (V) |

| Current at MPP (Impp) | 46.8 (A) |

| Open circuit voltage (Voc) | 294 (V) |

| Short circuit current (Isc) | 50.1 (A) |

| Input Voltage (Vin) | 105 V |

| Grid voltage (Vg) | 70 V, 50 Hz |

| Load resistance (R) | 43 (Ω) |

| LC filter | 1 mH, 10 µF |

| AC line frequency | 50 Hz |

| Switching frequency (FSW) | 10 kHz |

| PI controller gains, KP, KI | 0.081 A/V, 200 rad s−1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ali, A.I.M.; Sayed, M.A.; Mohamed, A.A.S. Seven-Level Inverter with Reduced Switches for PV System Supporting Home-Grid and EV Charger. Energies 2021, 14, 2718. https://doi.org/10.3390/en14092718

Ali AIM, Sayed MA, Mohamed AAS. Seven-Level Inverter with Reduced Switches for PV System Supporting Home-Grid and EV Charger. Energies. 2021; 14(9):2718. https://doi.org/10.3390/en14092718

Chicago/Turabian StyleAli, Ahmed Ismail M., Mahmoud A. Sayed, and Ahmed A. S. Mohamed. 2021. "Seven-Level Inverter with Reduced Switches for PV System Supporting Home-Grid and EV Charger" Energies 14, no. 9: 2718. https://doi.org/10.3390/en14092718

APA StyleAli, A. I. M., Sayed, M. A., & Mohamed, A. A. S. (2021). Seven-Level Inverter with Reduced Switches for PV System Supporting Home-Grid and EV Charger. Energies, 14(9), 2718. https://doi.org/10.3390/en14092718