Novel Single-Phase Grid-Tied NPC Five-Level Converter with an Inherent DC-Link Voltage Balancing Strategy for Power Quality Improvement

Abstract

1. Introduction

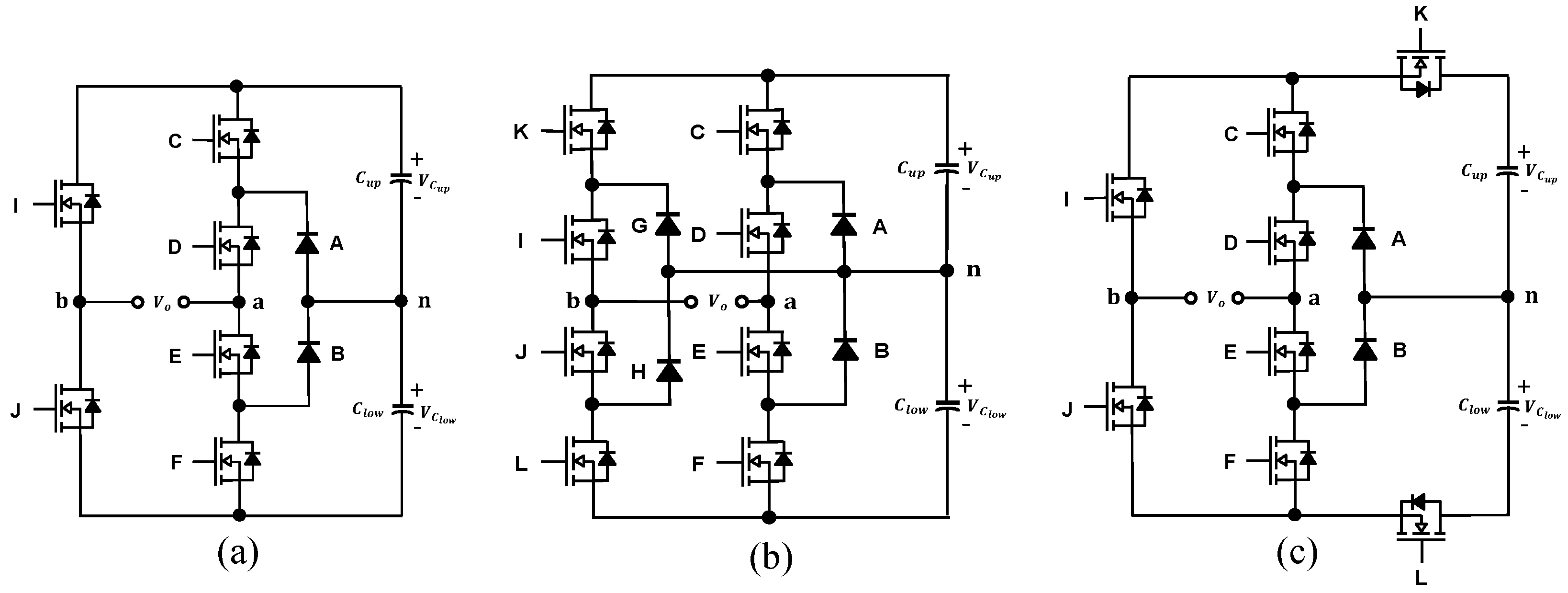

2. Proposed Single-Phase NPC Five-Level Converter

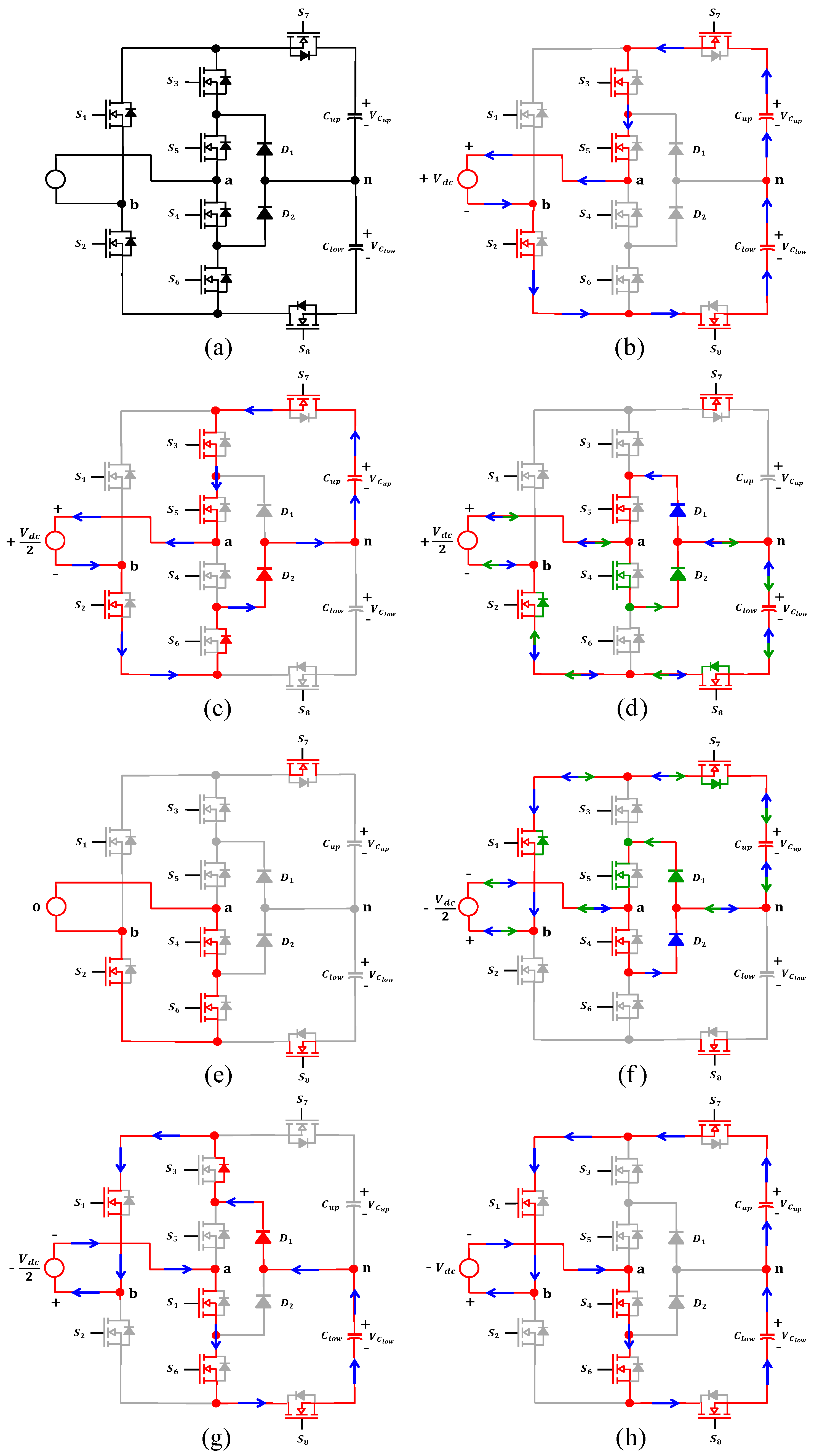

Current Flowing Paths of Proposed SPFLC and Voltage Balancing Strategy of DC-Link Split Capacitors

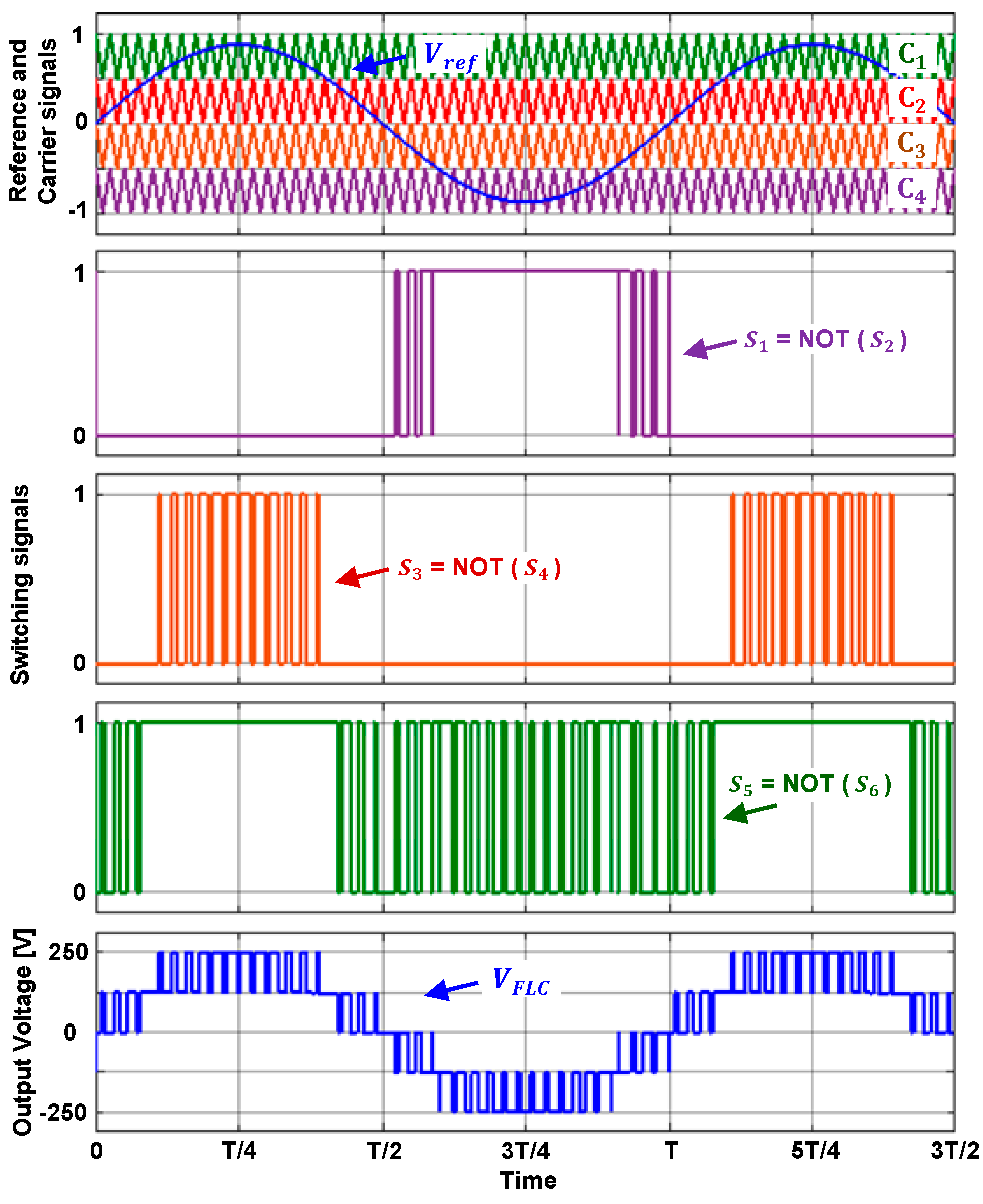

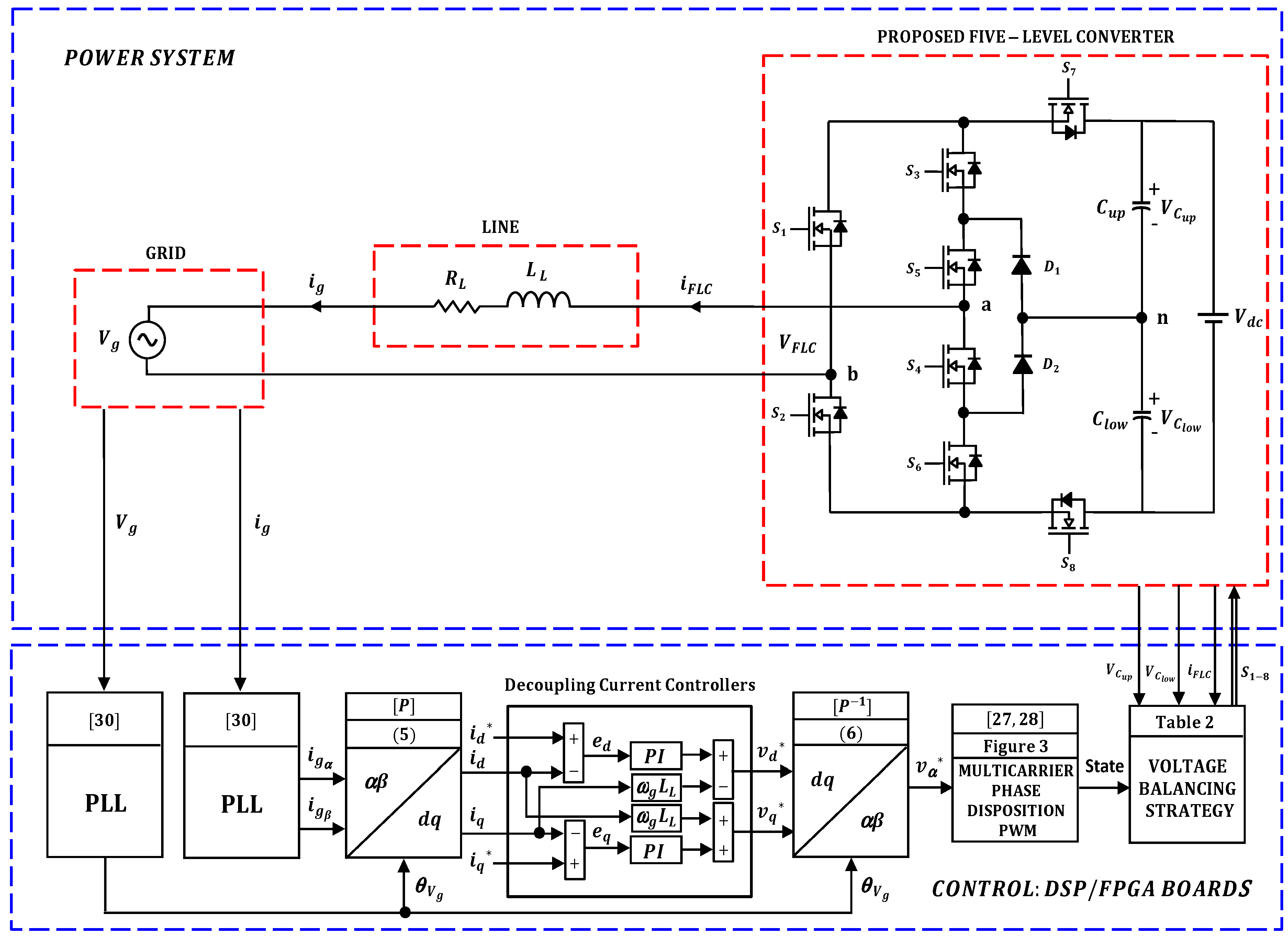

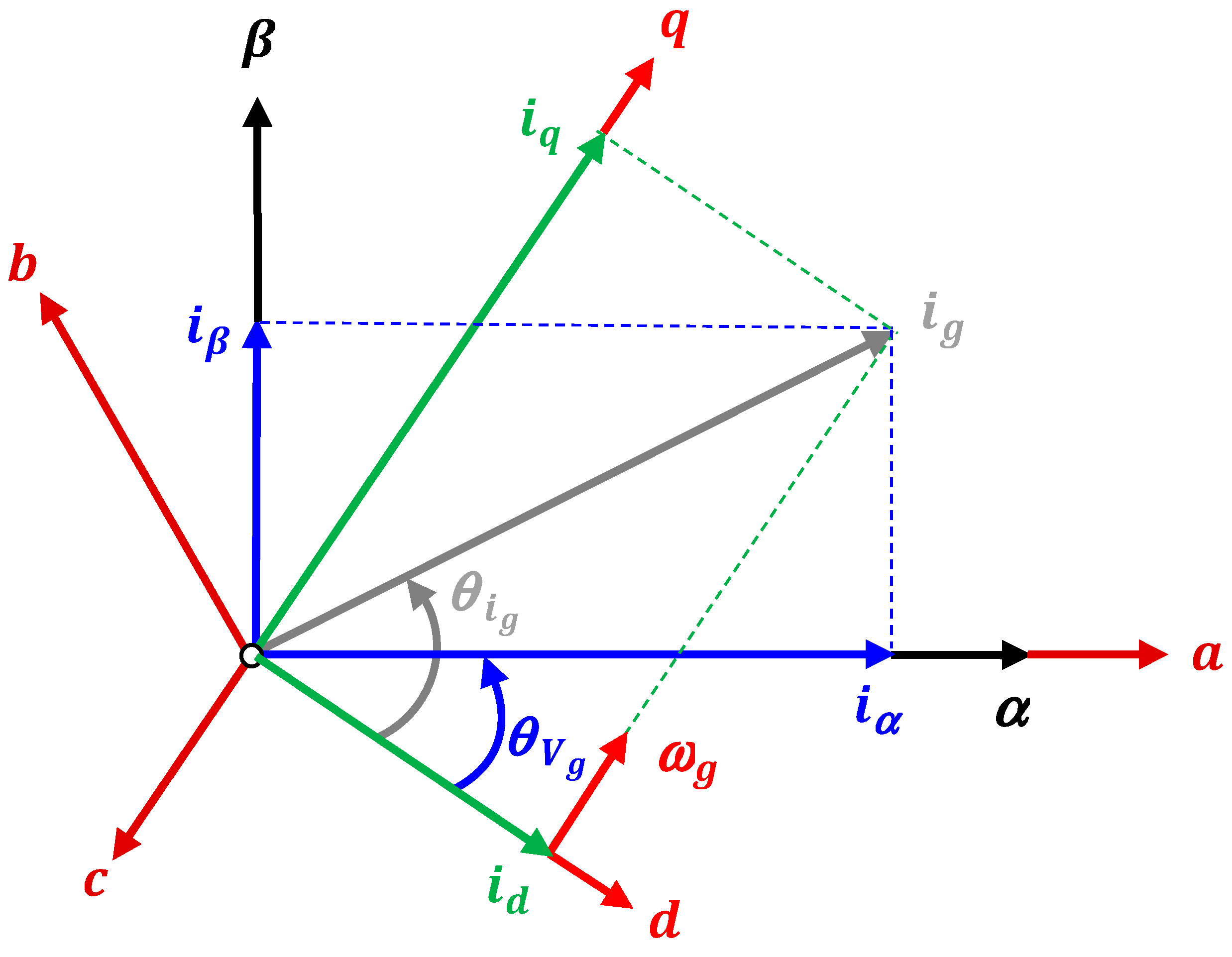

3. Vector Control of Proposed Grid-Tied SPFLC

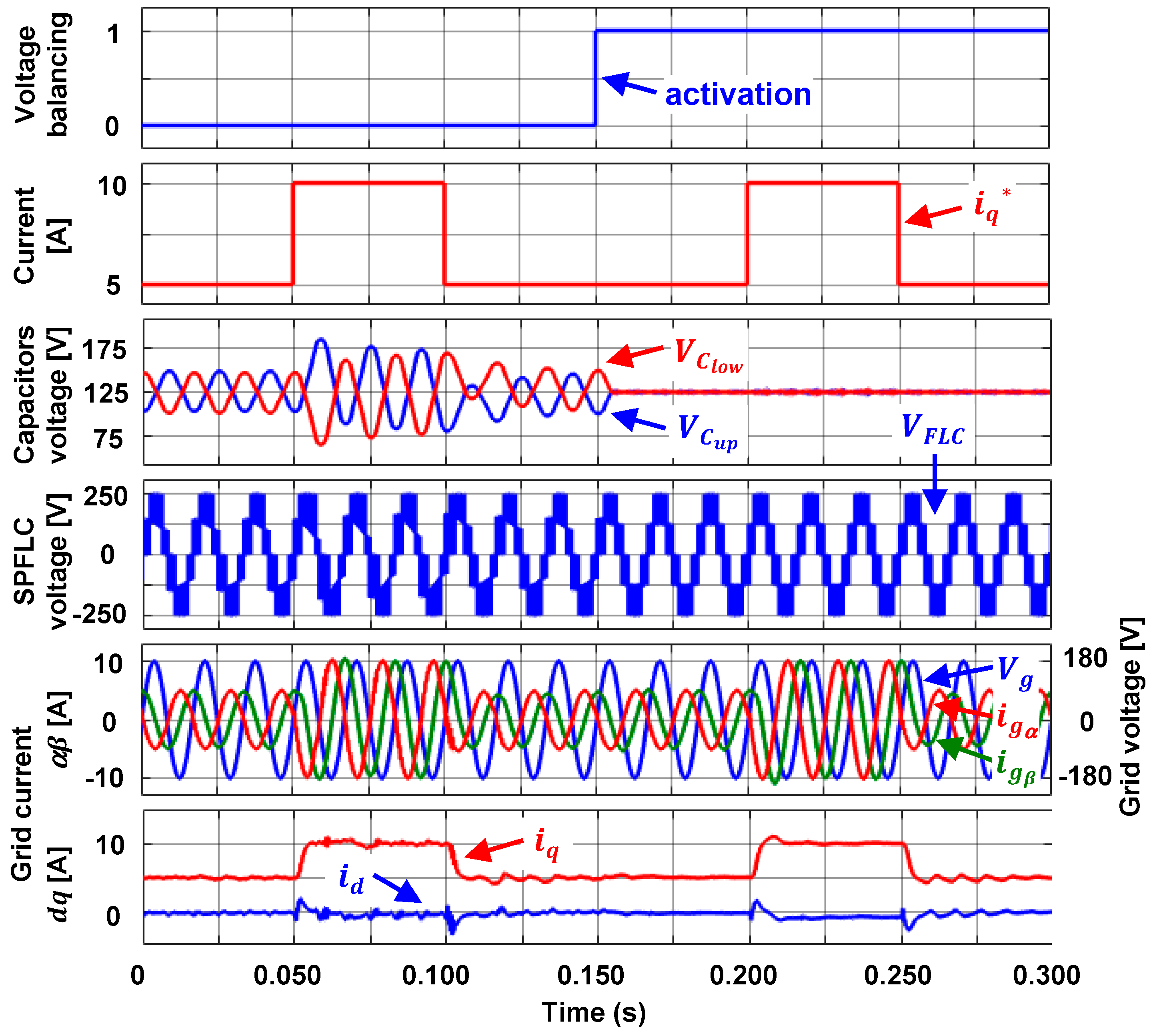

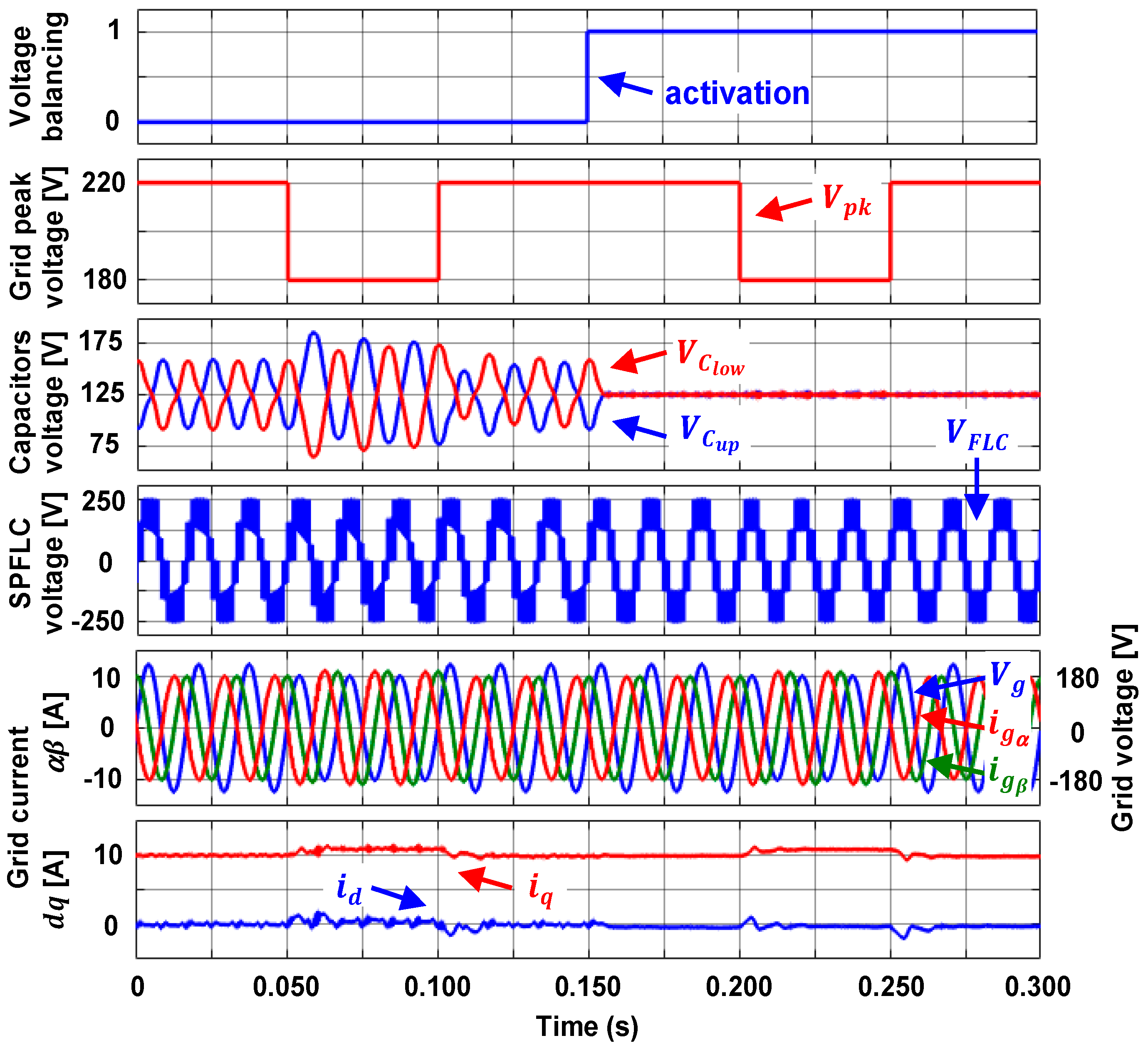

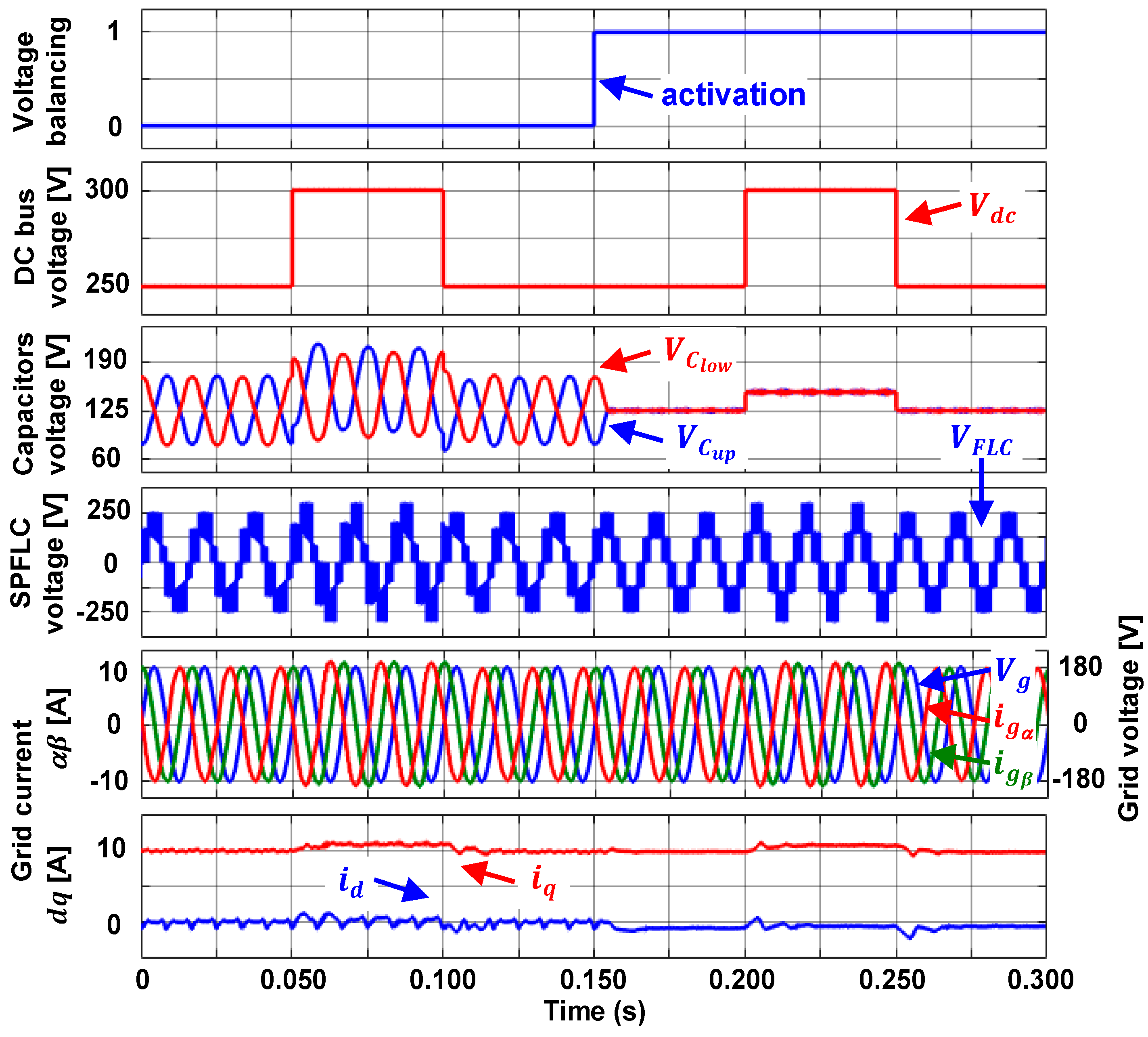

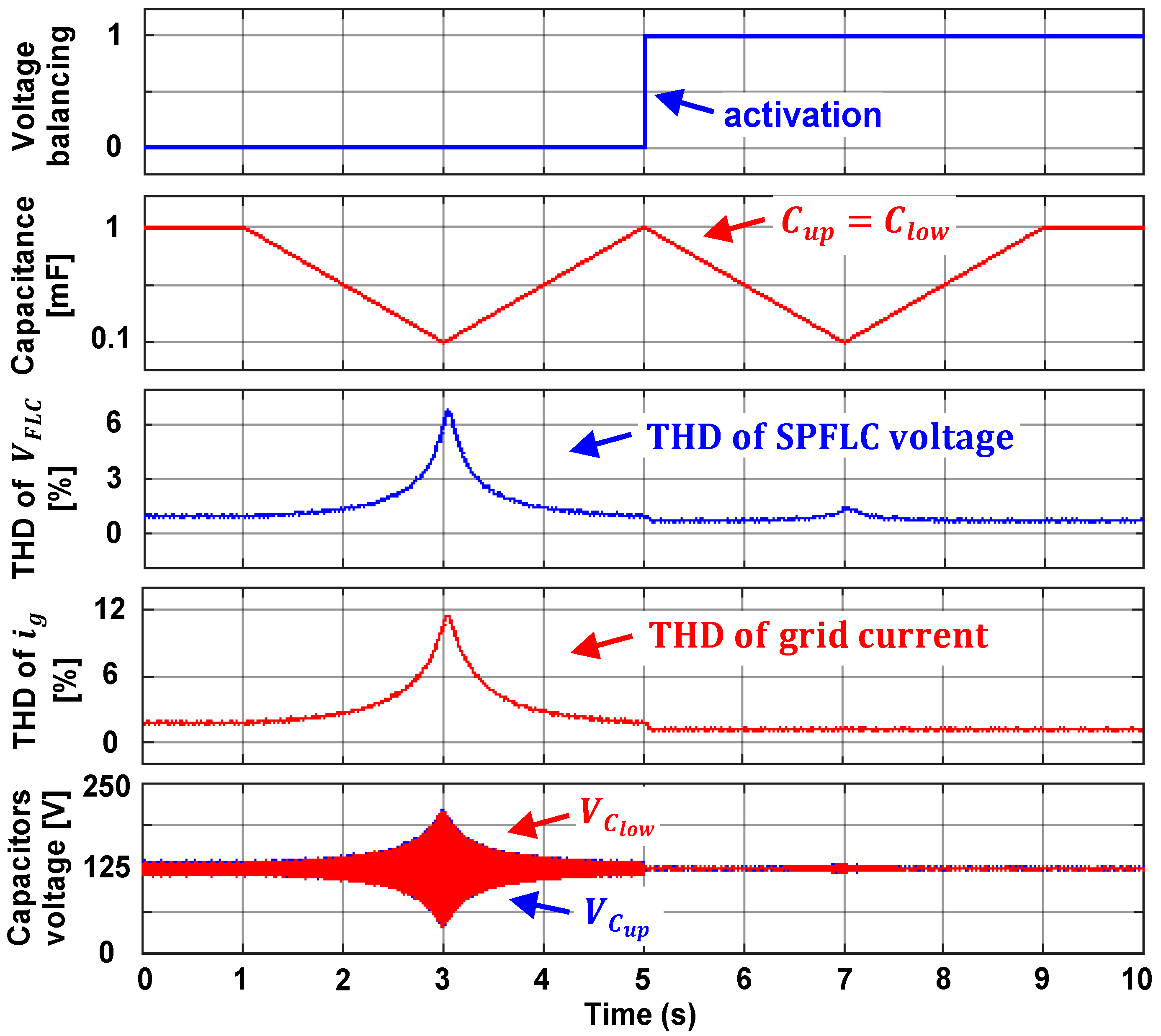

4. Simulation Results

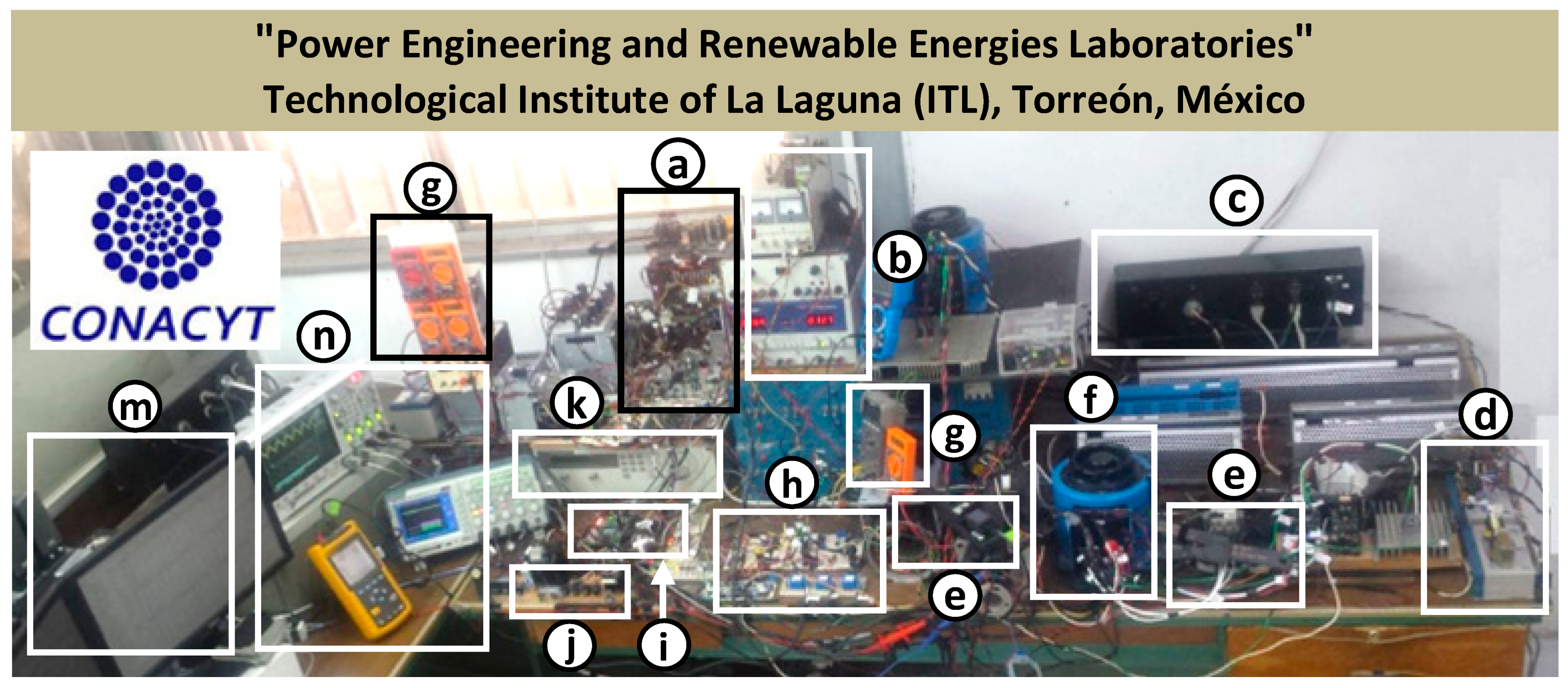

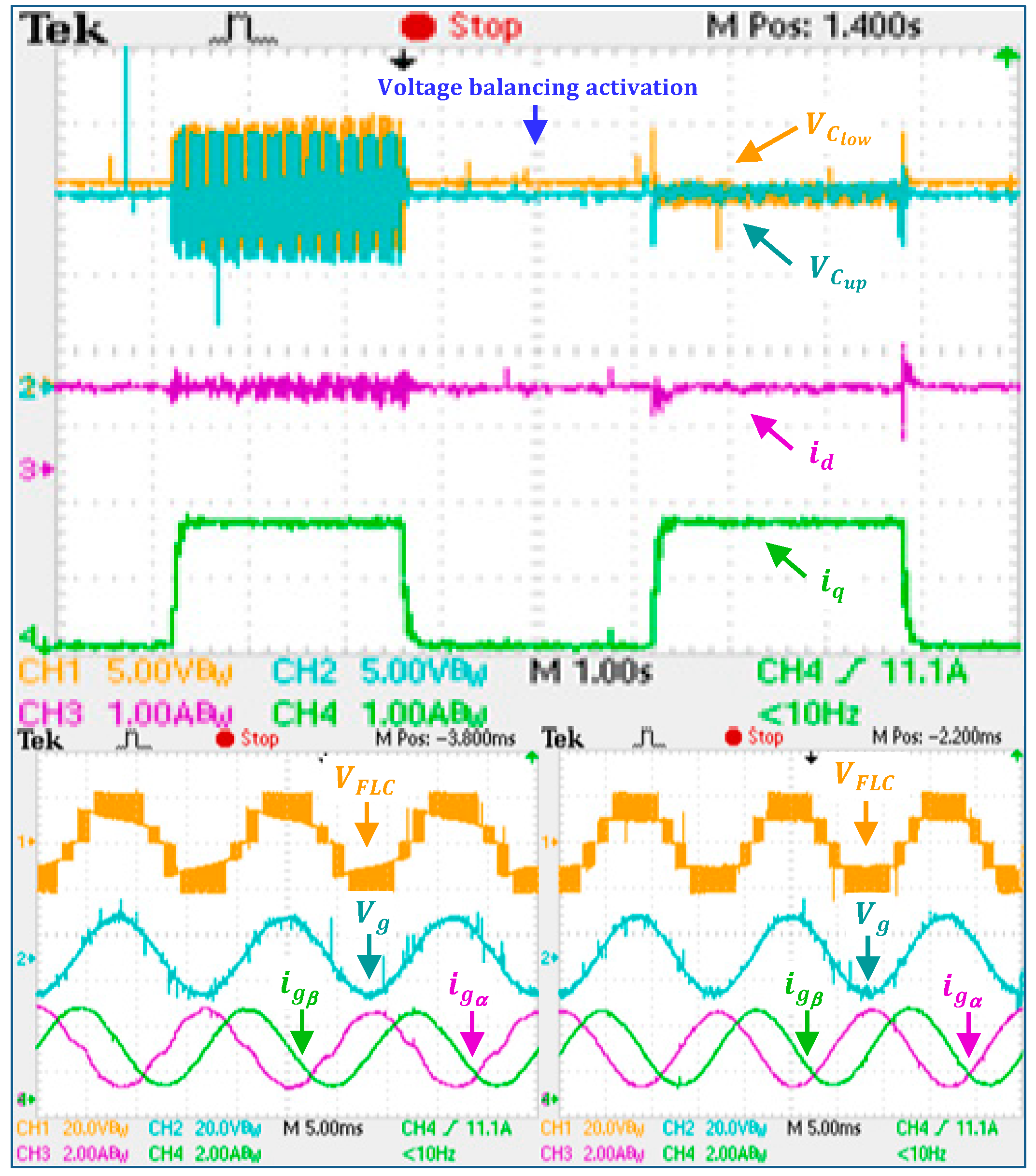

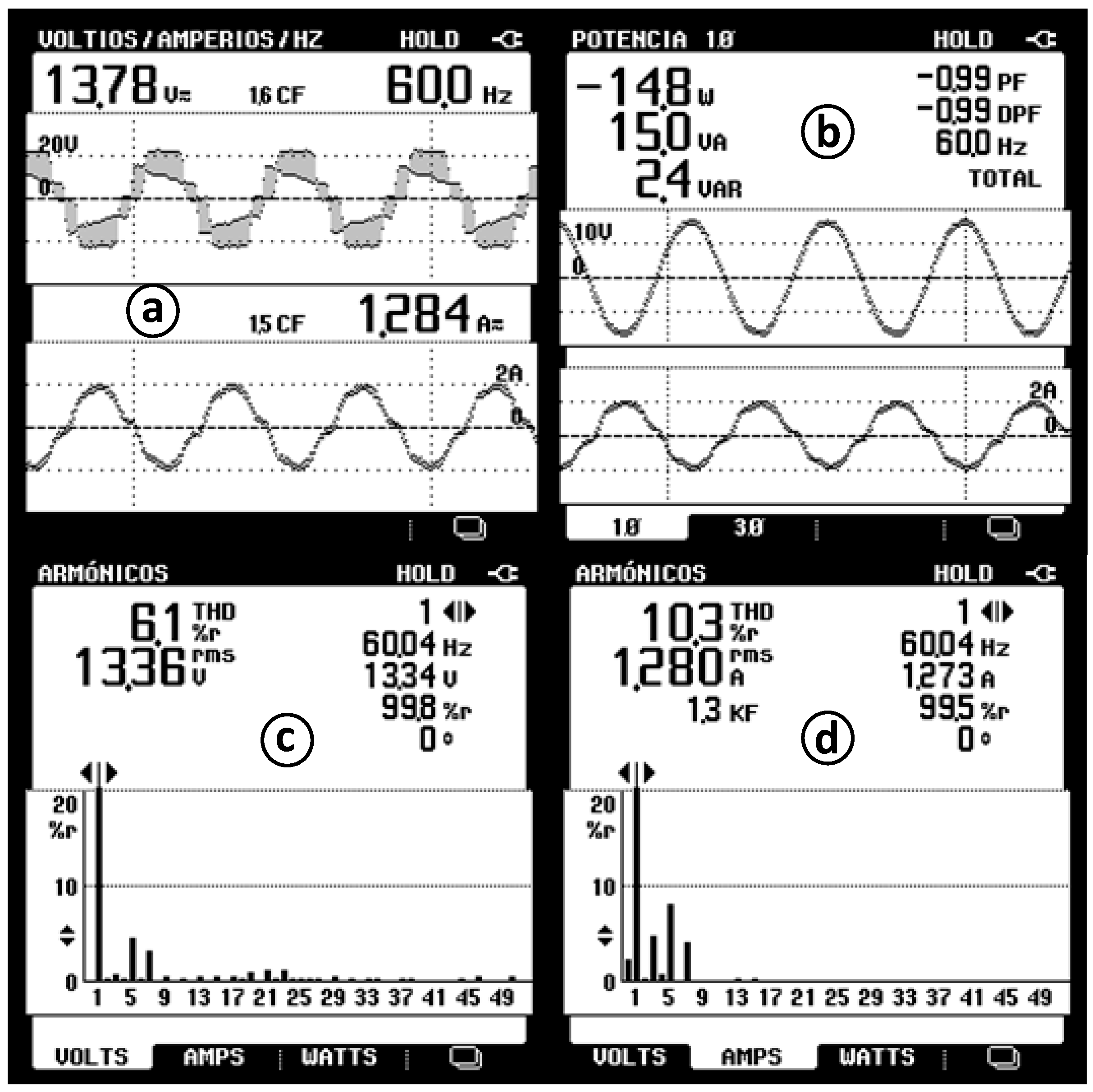

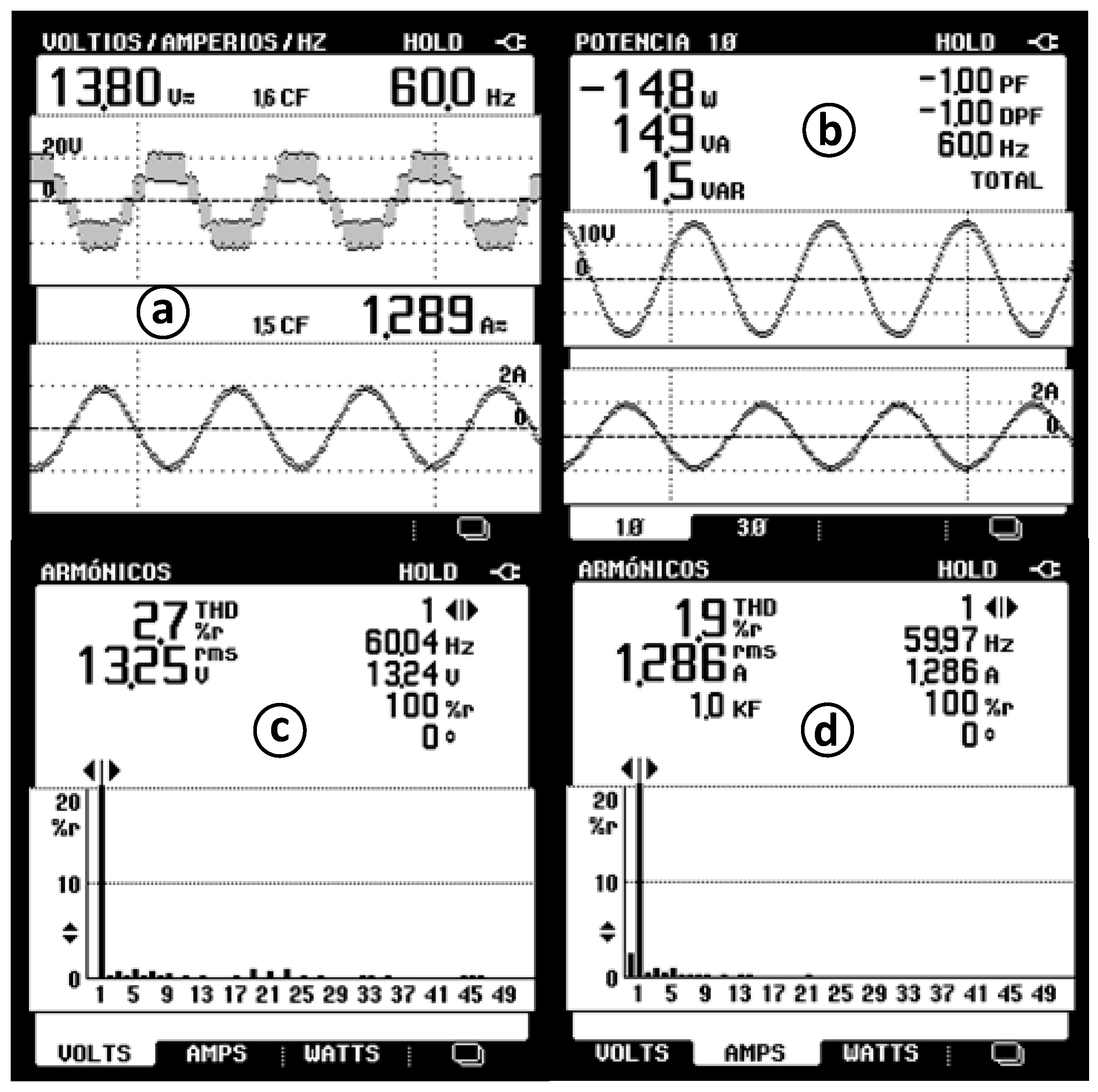

5. Experimental Results

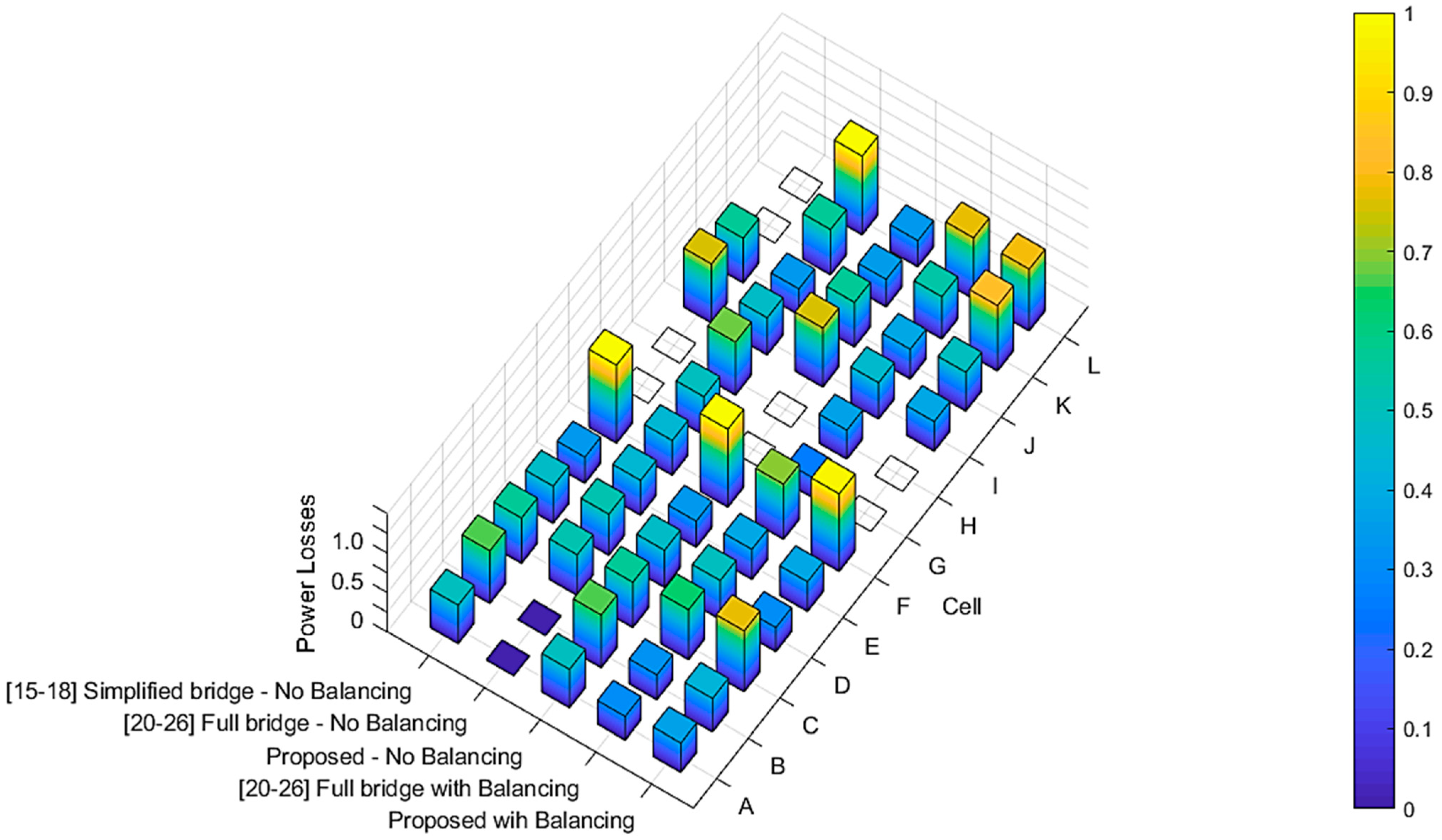

6. Discussion

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature

| , | direct and quadrature grid voltage components |

| , | direct and quadrature grid current components |

| , | stationary and rotating frames |

| , | variable in the stationary frame |

| , | variable in the rotating frame |

| , | grid current and grid voltage |

| , | sampling frequency and sampling time |

| , | phase of grid voltage and phase of grid current |

| angular frequency of grid | |

| DC bus voltage of FLC | |

| , | switching frequency and switching period |

| , | continuous time and fundamental period |

| T | transpose matrix |

| , | direct and inverse Park matrices |

| , | proportional and integral gains of PI controllers |

References

- Kuncham, S.K.; Annamalai, K.; Subrahmanyam, N. A two-stage T-type hybrid five-level transformerless inverter for PV applications. IEEE Trans. Power Electron. 2020, 35, 9510–9521. [Google Scholar] [CrossRef]

- Gautam, S.P.; Kumar, L.; Gupta, S.; Agrawal, N. A single-phase five-level inverter topology with switch fault-tolerance ca-pabilities. IEEE Trans. Power Electron. 2017, 64, 2004–2014. [Google Scholar]

- Monteiro, V.; Ferreira, J.C.; Melendez, A.A.N.; Afonso, J.L. Model predictive control applied to an improved five-level bidirectional converter. IEEE Trans. Ind. Electron. 2016, 63, 5879–5890. [Google Scholar] [CrossRef]

- Kang, K.-P.; Cho, Y.; Ryu, M.-H.; Baek, J.-W. A harmonic voltage injection based DC-link imbalance compensation technique for single-phase three-level neutral-point-clamped (NPC) inverters. Energies 2018, 11, 1886. [Google Scholar] [CrossRef]

- Jun, E.-S.; Kwak, S. A Highly efficient single-phase three-level neutral point clamped (NPC) converter based on predictive control with reduced number of commutations. Energies 2018, 11, 3524. [Google Scholar] [CrossRef]

- Jun, E.-S.; Nguyen, M.H.; Kwak, S. Model predictive control method based on deterministic reference voltage for single-phase three-level NPC converters. Appl. Sci. 2020, 10, 8840. [Google Scholar] [CrossRef]

- Zanasi, R.; Tebaldi, D. Modeling control and robustness assessment of multilevel flying-capacitor converters. Energies 2021, 14, 1903. [Google Scholar] [CrossRef]

- Kim, J.-M.; Song, G.-S.; Jung, J.-J. Zero-sequence voltage injection method for DC capacitor voltage balancing of wye-connected CHB converter under unbalanced grid and load conditions. Energies 2021, 14, 1019. [Google Scholar] [CrossRef]

- Saeedian, M.; Hosseini, S.M.; Adabi, J. A five-level step-up module for multilevel inverters: Topology, modulation strategy, and implementation. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 2215–2226. [Google Scholar] [CrossRef]

- Buticchi, G.; Lorenzani, E.; Franceschini, G. A five-level single-phase grid-connected converter for renewable distributed sys-tems. IEEE Trans. Power Electron. 2013, 60, 906–918. [Google Scholar]

- He, X.; Lin, X.; Peng, X.; Han, P.; Shu, Z.; Gao, S. Control strategy of single-phase three level neutral point clamped cascaded rectifier. Energies 2017, 10, 592. [Google Scholar]

- Peng, X.; He, X.; Han, P.; Guo, A.; Shu, Z.; Gao, S. Smooth switching technique for voltage balance management based on three-level neutral point clamped cascaded rectifier. Energies 2016, 9, 803. [Google Scholar] [CrossRef]

- Khan, S.A.; Islam, M.R.; Guo, Y.; Zhu, J. An amorphous alloy magnetic-bus-based SiC NPC converter with inherent voltage balancing for grid-connected renewable energy systems. IEEE Trans. Appl. Supercond. 2019, 29. [Google Scholar] [CrossRef]

- Rao, A.M.; Sivakumar, K. A Fault-tolerant single-phase five-level inverter for grid-independent PV systems. IEEE Trans. Ind. Electron. 2015, 62, 7569–7577. [Google Scholar] [CrossRef]

- Haddad, M.; Rahmani, S.; Hamadi, A.; Al-Haddad, K. New Single Phase Multilevel Reduced Count Devices to Perform Active Power Filter. In Proceedings of the Institute of Electrical and Electronics Engineers (IEEE), Fort Lauderdale, FL, USA, 9–12 April 2015; pp. 1–6. [Google Scholar]

- Javadi, A.; Abarzadeh, M.; Gregoire, L.-A.; Al-Haddad, K. Real-time HIL implementation of a single-phase distribution level THSeAF based on D-NPC converter using proportional-resonant controller for power quality platform. IEEE Access 2019, 7, 110372–110386. [Google Scholar] [CrossRef]

- Javadi, A.; Hamadi, A.; Ndtoungou, A.; Al-Haddad, K. Power quality enhancement of smart households using a multi-level-THSeAF with a PR controller. IEEE Trans. Smart Grid 2017, 8, 465–474. [Google Scholar] [CrossRef]

- Hamadi, A.; Rahmani, S.; Al-Haddad, K.; Addoweesh, K.; Hamadi, A. Micro Grid Based PMSG Feeding Isolated Loads. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 3160–3165. [Google Scholar]

- Zhou, T.; Shu, Z.; Lin, H.; Luo, D.; Chen, Y.; Guo, X. A high-power-density single-phase rectifier based on three-level neutral-point clamped circuits. Energies 2017, 10, 697. [Google Scholar] [CrossRef]

- Stala, R. Application of balancing circuit for DC-link voltages balance in a single-phase diode-clamped inverter with two three-level legs. IEEE Trans. Ind. Electron. 2010, 58, 4185–4195. [Google Scholar] [CrossRef]

- Song, W.; Feng, X.; Smedley, K.M. A carrier-based PWM strategy with the offset voltage injection for single-phase three-level neutral-point-clamped converters. IEEE Trans. Power Electron. 2013, 28, 1083–1095. [Google Scholar] [CrossRef]

- Wensheng, S.; Shunliang, W.; Chenglin, X.; Xinglai, G.; Xiaoyun, F. Single-phase three-level space vector pulse width modu-lation algorithm for grid-side railway traction converter and its relationship of carrier-based pulse width modulation. IET Electr. Syst. Transp. 2014, 4, 78–87. [Google Scholar]

- Wang, S.; Ma, J.; Liu, B.; Jiao, N.; Liu, T.; Wang, Y. Unified SVPWM algorithm and optimization for single-phase three-level npc converters. IEEE Trans. Power Electron. 2020, 35, 7702–7712. [Google Scholar] [CrossRef]

- Salaet, J.; Gilabert, A.; Bordonau, J.; Alepuz, S.; Cano, A.; Gimeno, L.M. Nonlinear control of neutral point in three-level single-phase converter by means of switching redundant states. IEE Electron. Lett. 2006, 42, 304–306. [Google Scholar] [CrossRef]

- Sanchez-Ruiz, A.; Abad, G.; Echeverria, I.; Torre, I.; Atutxa, I. Continuous phase-shifted selective harmonic elimination and DC-link voltage balance solution for h-bridge multilevel configurations, applied to 5L HNPC. IEEE Trans. Power Electron. 2016, 32, 2533–2545. [Google Scholar] [CrossRef]

- Lee, J.-S.; Kwak, R.; Lee, K.-B. Novel discontinuous PWM method for a single-phase three-level neutral point clamped inverter with efficiency improvement and harmonic reduction. IEEE Trans. Power Electron. 2018, 33, 9253–9266. [Google Scholar] [CrossRef]

- Calais, M.; Borle, L.J.; Agelidis, V.G. Analysis of Multicarrier PWM Methods for a Single-phase Five Level Inverter. In Proceedings of the 2001 IEEE 32nd Annual Power Electronics Specialists Conference (IEEE Cat. No.01CH37230), Vancouver, BC, Canada, 17–21 June 2001; pp. 1351–1356. [Google Scholar]

- Arab, N.; Vahedi, H.; Al-Haddad, K. LQR control of single-phase grid-tied PUC5 inverter with LCL filter. IEEE Trans. Ind. Electron. 2020, 67, 297–307. [Google Scholar] [CrossRef]

- Bahrani, B.; Rufer, A.; Kenzelmann, S.; Lopes, L.A.C. Vector control of single-phase voltage-source converters based on fictive-axis emulation. IEEE Trans. Ind. Appl. 2011, 47, 831–840. [Google Scholar] [CrossRef]

- Ziarani, A.; Konrad, A.; Sinclair, A. A novel time-domain method of analysis of pulsed sine wave signals. IEEE Trans. Instrum. Meas. 2003, 52, 809–814. [Google Scholar] [CrossRef]

| Feature | Number Of Components | Voltage Balancing | ||||

|---|---|---|---|---|---|---|

| Fl Npc Topology | Capacitors | Switches | Diodes | Total | Capability | Complexity |

| Simplified-Bridge (SB) [15,16,17,18] | 2 | 6 | 2 | 8 | NO | - |

| Full-Bridge (FB) [20,21,22,23,24,25,26] | 2 | 8 | 4 | 12 | YES | HIGH |

| Proposed | 2 | 8 | 2 | 10 | YES | LOW |

| Switching State | State of Switches | Flc Output Voltage | Voltage Balancing Algorithm Activated | Capacitors Unbalance Voltage (ΔV) | Flc Output Current Sign | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | ||||

| 2U | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | /2 | YES | ||

| 2L | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | NO/YES | OTHERWISE | ||

| 3 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | |||

| 4U | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | /2 | NO/YES | OTHERWISE | |

| 4L | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | YES | |||

| 5 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | ||||

| Parameter | Symbol | Value | Units | |

|---|---|---|---|---|

| Simulation | Experimental | |||

| Switching frequency | 5 | 5 | kHz | |

| Line resistance | 0.1 | 0.1 | Ω | |

| Line inductance | 5 | 3 | mH | |

| Grid voltage (peak) | 180 | 15 | V | |

| Grid frequency | 60 | 60 | Hz | |

| DC bus voltage | 250 | 25 | V | |

| Capacitance of split capacitors | , | 200 | 300 | μF |

| Sampling time/Time-step | 100 | 100 | μs | |

| Five-Level Npc Converter | Efficiency (%) | |

|---|---|---|

| Without Voltage Balancing | With Voltage Balancing | |

| Simplified-bridge [15,16,17,18] | 96.11 | - |

| Full-bridge [20,21,22,23,24,25,26] | 95.26 | 95.13 |

| Proposed | 95.55 | 95.37 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lara, J.; Masisi, L.; Hernandez, C.; Arjona, M.A.; Chandra, A. Novel Single-Phase Grid-Tied NPC Five-Level Converter with an Inherent DC-Link Voltage Balancing Strategy for Power Quality Improvement. Energies 2021, 14, 2644. https://doi.org/10.3390/en14092644

Lara J, Masisi L, Hernandez C, Arjona MA, Chandra A. Novel Single-Phase Grid-Tied NPC Five-Level Converter with an Inherent DC-Link Voltage Balancing Strategy for Power Quality Improvement. Energies. 2021; 14(9):2644. https://doi.org/10.3390/en14092644

Chicago/Turabian StyleLara, Jorge, Lesedi Masisi, Concepcion Hernandez, Marco A. Arjona, and Ambrish Chandra. 2021. "Novel Single-Phase Grid-Tied NPC Five-Level Converter with an Inherent DC-Link Voltage Balancing Strategy for Power Quality Improvement" Energies 14, no. 9: 2644. https://doi.org/10.3390/en14092644

APA StyleLara, J., Masisi, L., Hernandez, C., Arjona, M. A., & Chandra, A. (2021). Novel Single-Phase Grid-Tied NPC Five-Level Converter with an Inherent DC-Link Voltage Balancing Strategy for Power Quality Improvement. Energies, 14(9), 2644. https://doi.org/10.3390/en14092644