A CMOS Active Rectifier with Efficiency-Improving and Digitally Adaptive Delay Compensation for Wireless Power Transfer Systems

Abstract

:1. Introduction

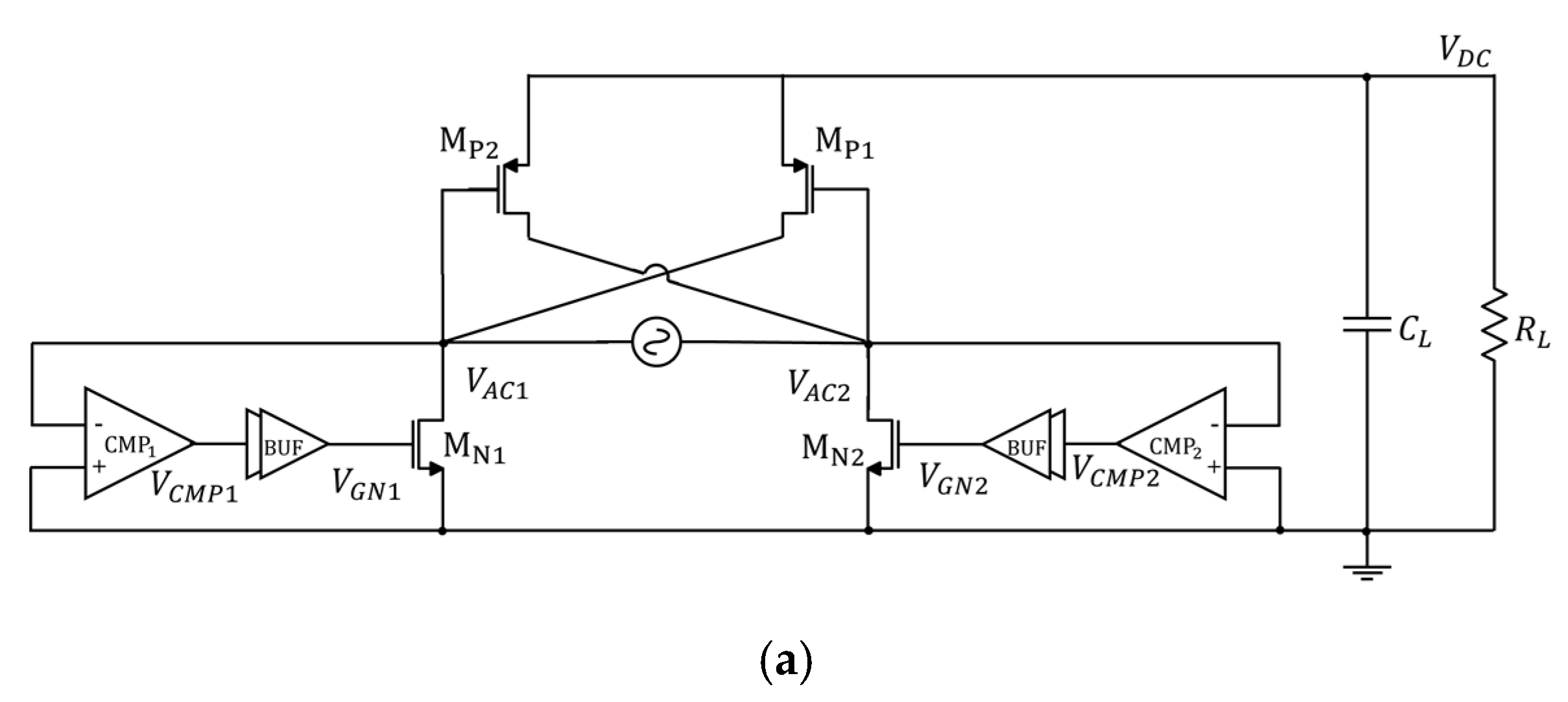

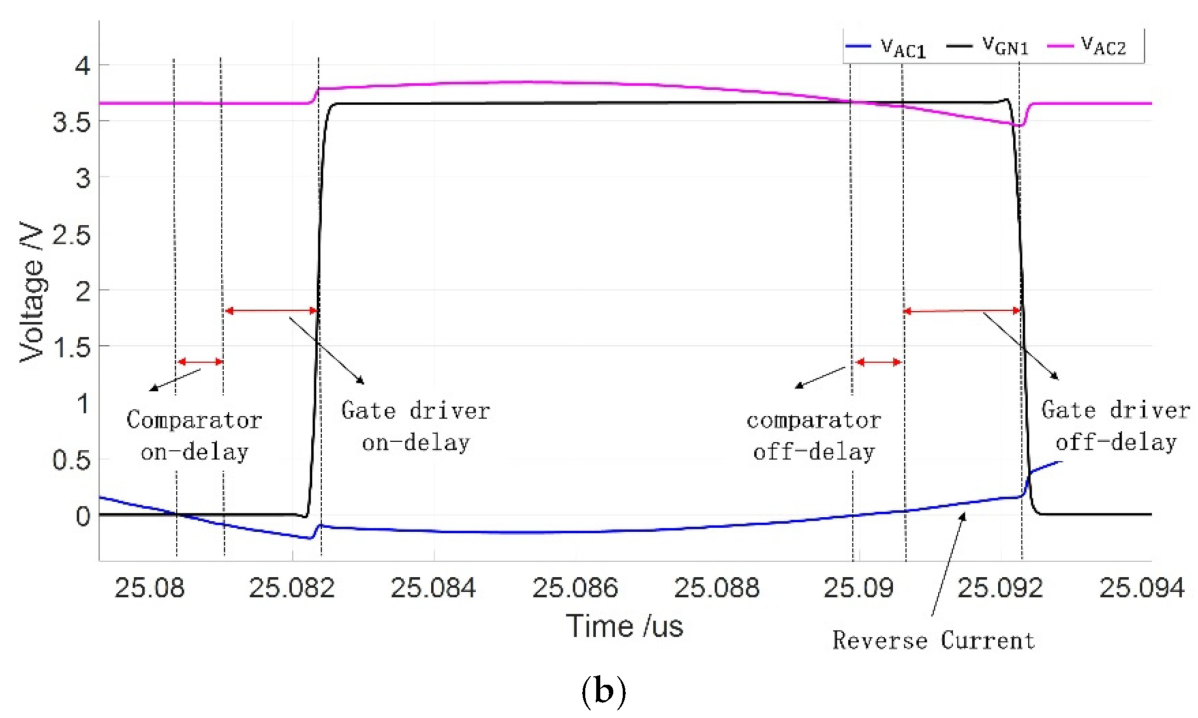

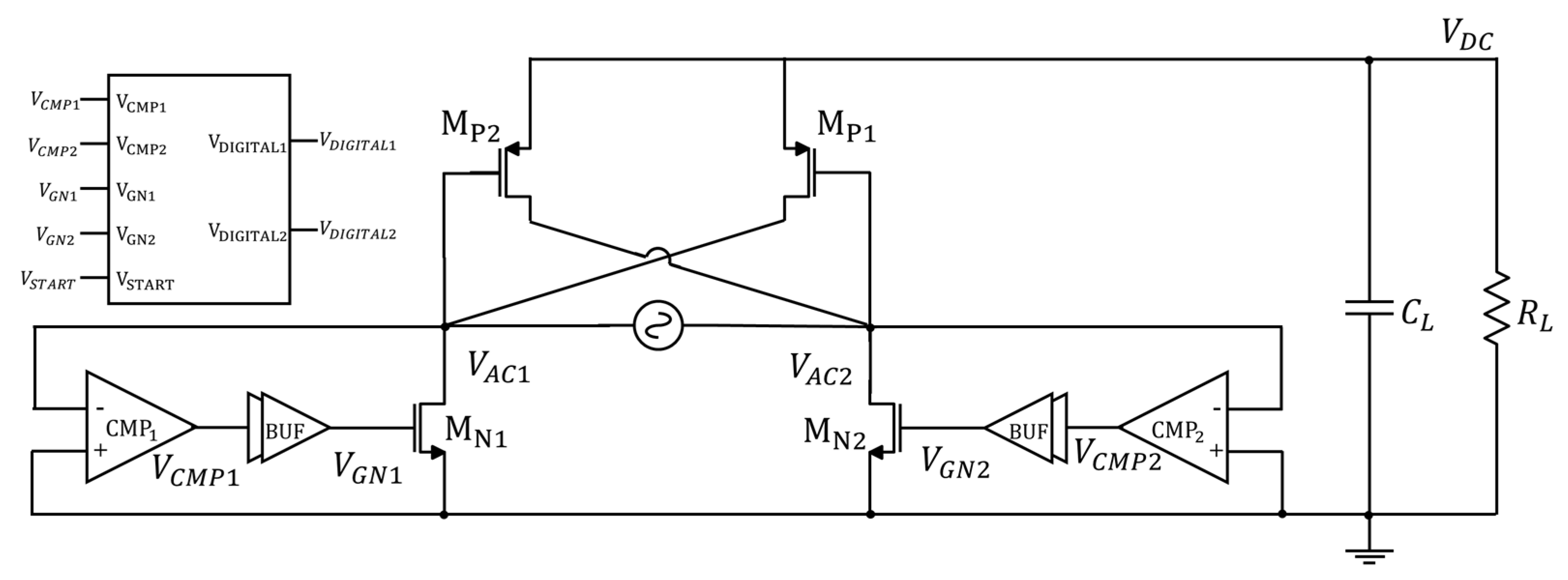

2. Introduction of Active Rectifier

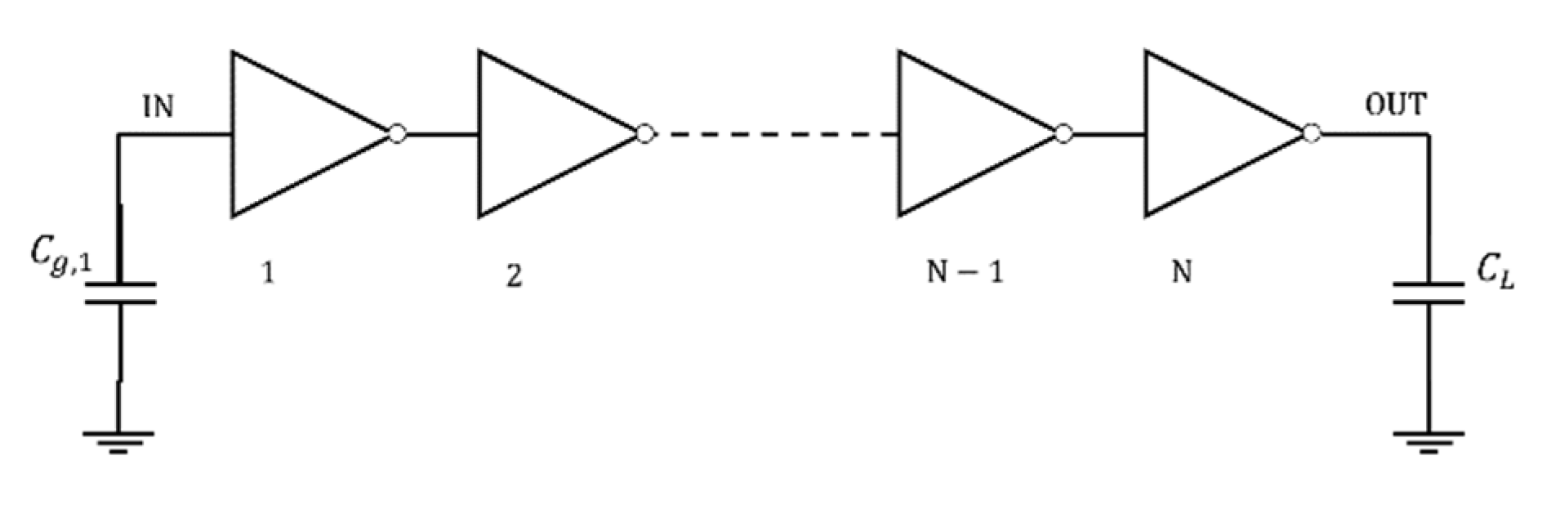

3. The Proposed Digitally Adaptive Delay Compensation Method

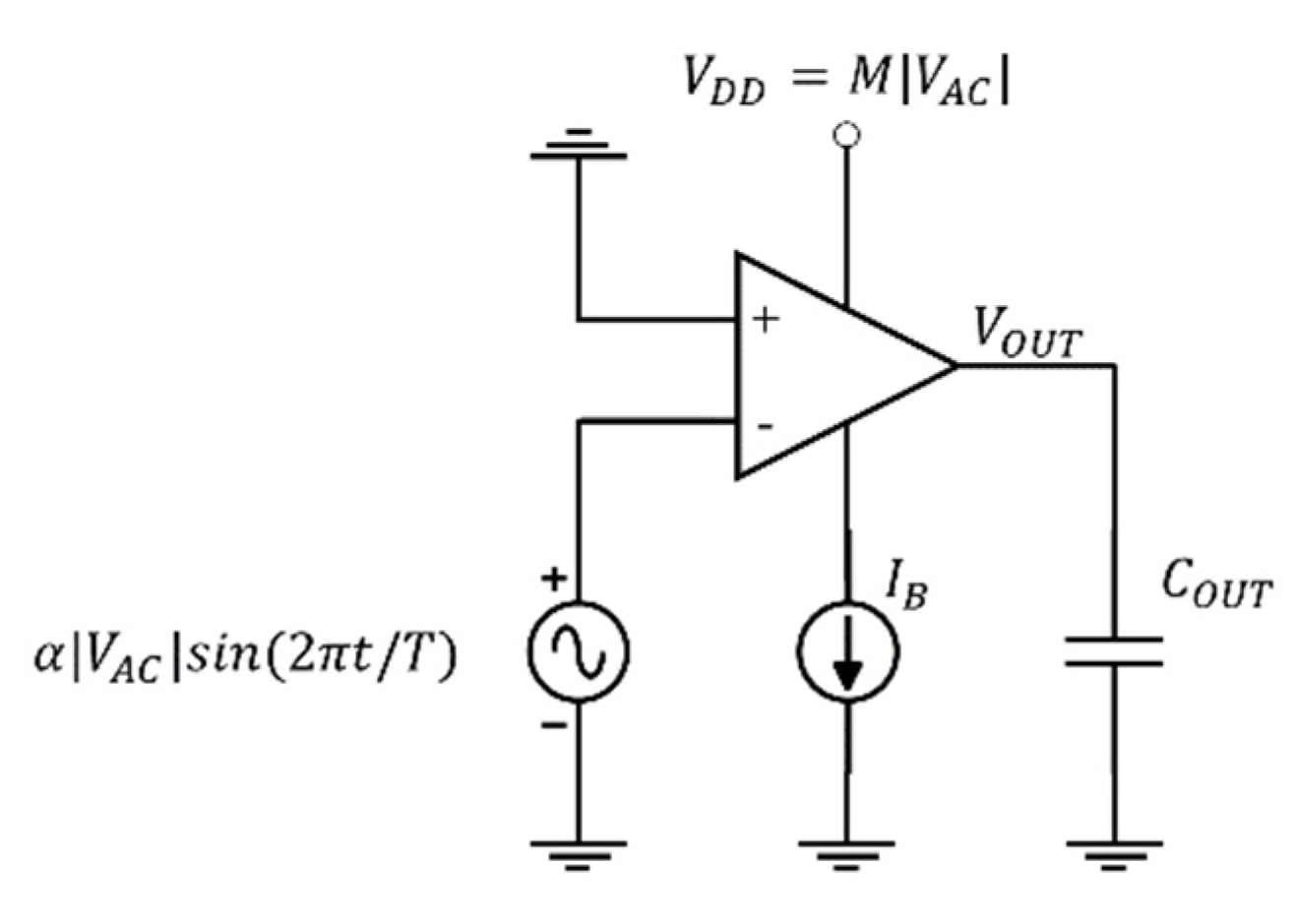

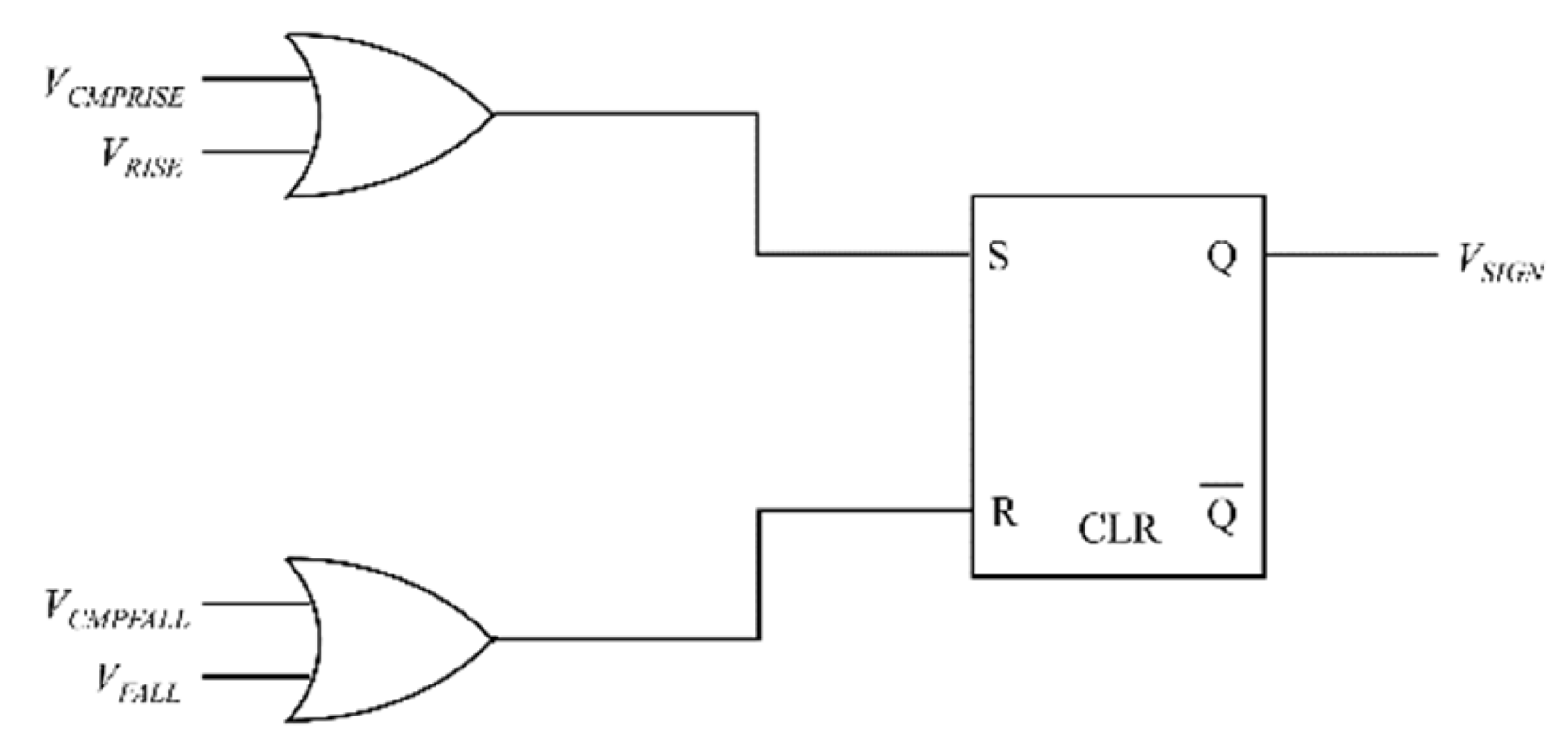

3.1. Turn-On Delay Compensation

3.2. Turn-Off Delay Compensation

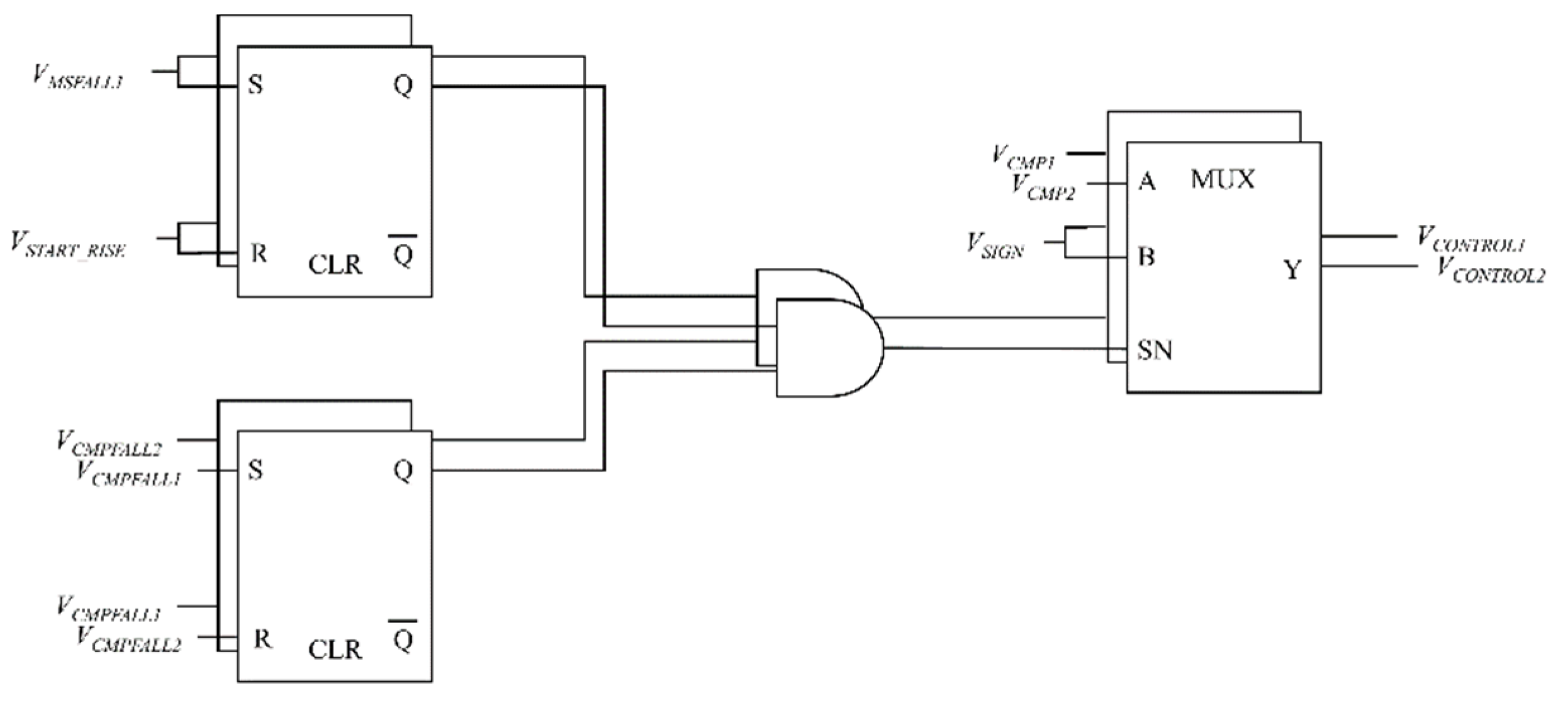

4. Control Design

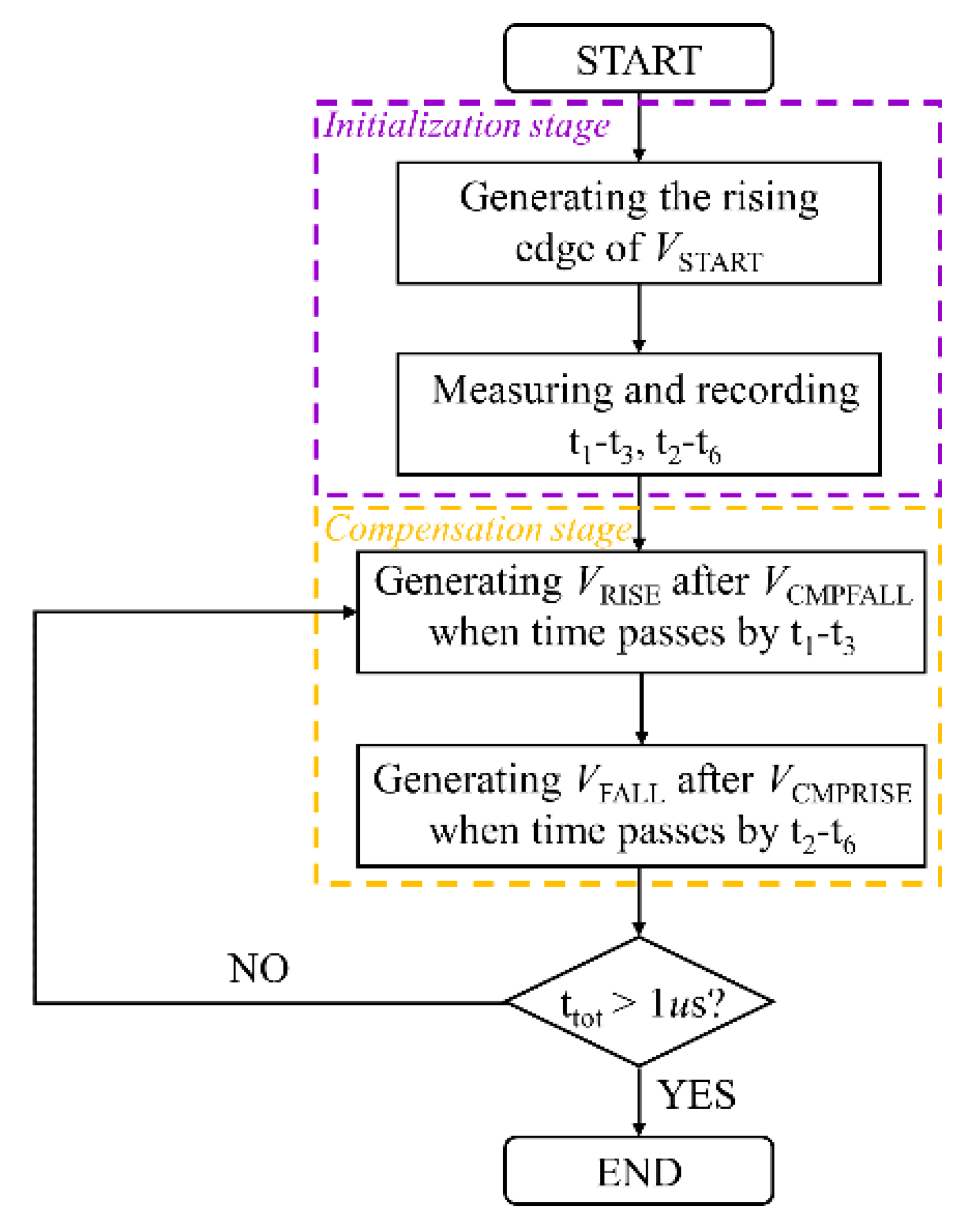

4.1. System Operation Process

- (1)

- After starting the system, the rising edge of VSTART is generated, which activates the initialization stage of the system operation process.

- (2)

- t1 and t2 are measured and recorded in preparation for the generation of compensation signals.

- (3)

- After the falling edge of the comparator’s output, the rising edge of the compensation signal is generated when time passes through (t1 − t3).

- (4)

- After the rising edge of the comparator’s output, the falling edge of the compensation signal is generated when time passes through (t2 − t6). Until now, the compensation signal of only one NMOS has been generated.

- (5)

- The delay compensation control circuit continuously performs step (3) and step (4) until a new rising edge of VSTART is generated, and this processing cycle reaches the end. The rising edge of VSTART is generated every 1 μs to recalibrate the compensation control circuit, and it will not stop being generated unless the wireless power transfer system containing the proposed rectifier is turned off or the generation of the calibration signal VSTART is stopped.

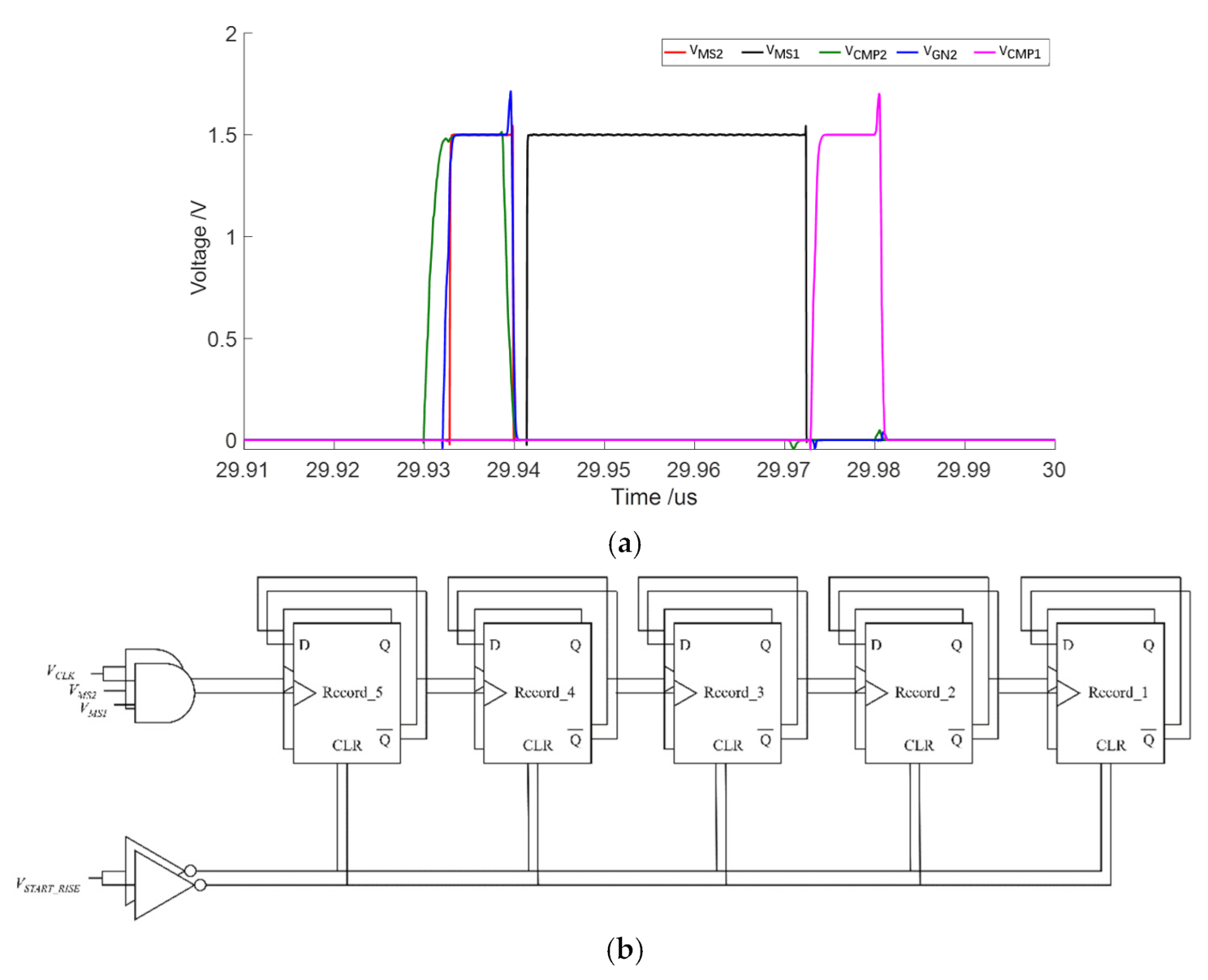

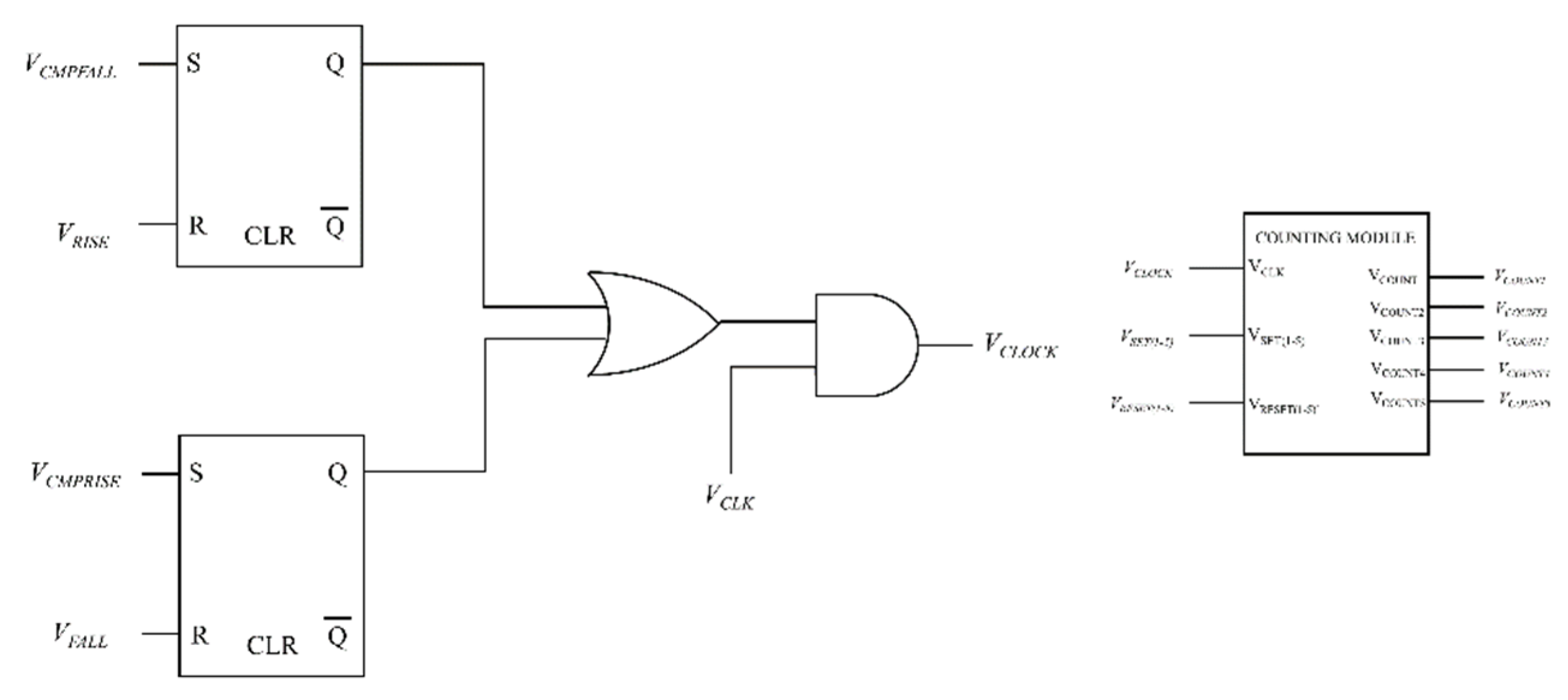

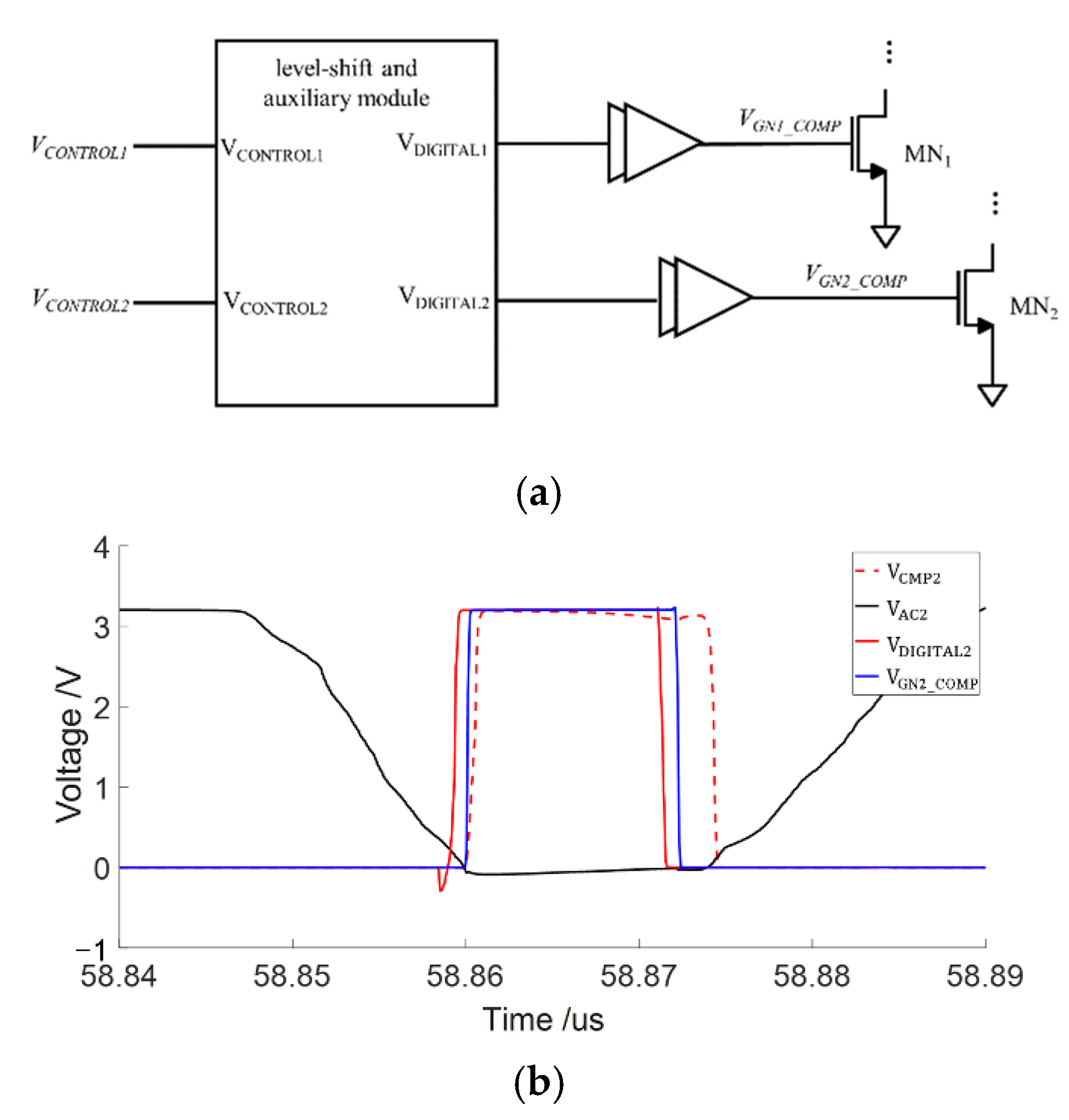

4.2. Circuit Implementation

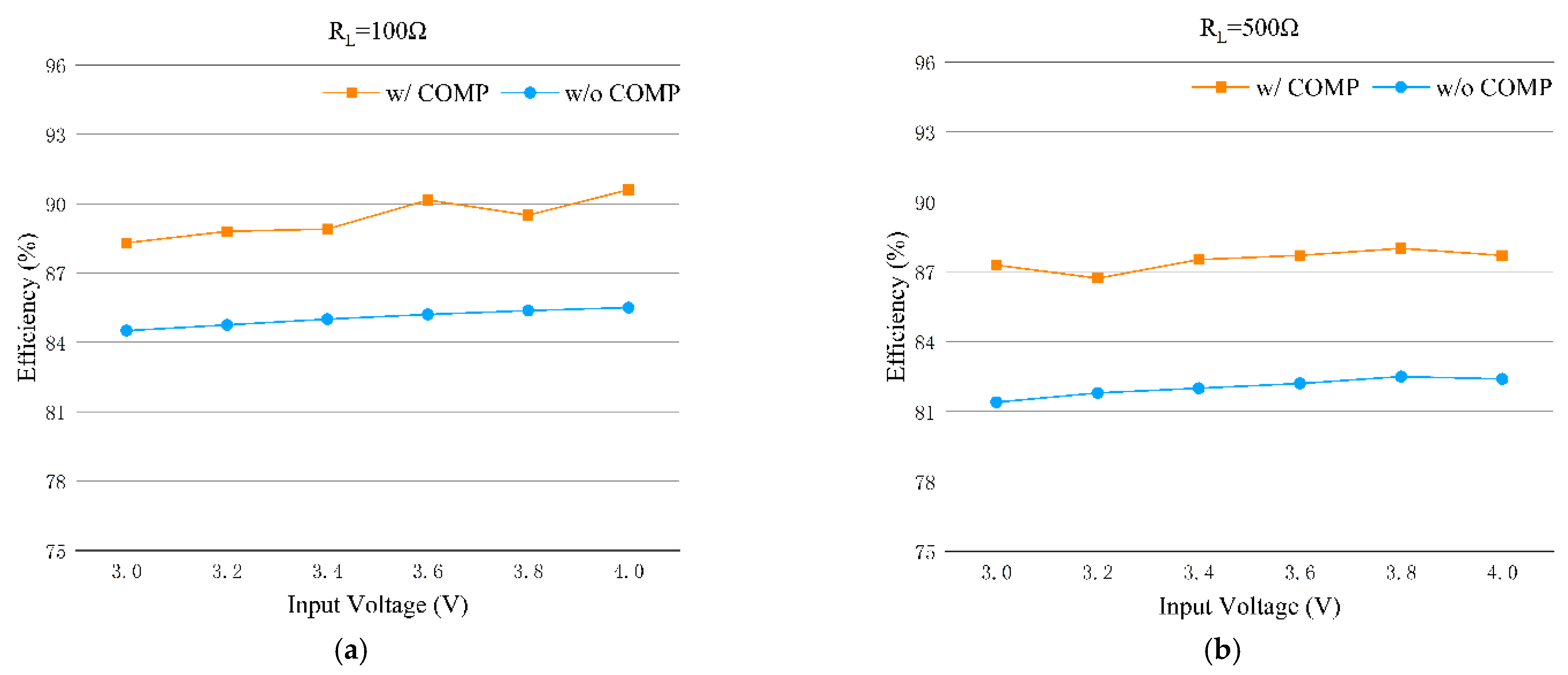

5. Simulation Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Junye, M.; Xian, T.; Wai Tung, N.; Mingming, Z. A High-Efficiency Active Rectifier with Adaptive Off-Delay Compensation for Wireless Power Transfer Systems. In Proceedings of the 2020 IEEE 5th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 23–25 October 2020; pp. 1–4. [Google Scholar]

- Lam, Y.H.; Ki, W.H.; Tsui, C.Y. Integrated low-loss CMOS active rectifier for wirelessly powered devices. IEEE Trans. Circuits Syst. II—Express Briefs 2006, 53, 1378–1382. [Google Scholar] [CrossRef]

- Guo, S.; Lee, H. An Efficiency-Enhanced CMOS Rectifier with Unbalanced-Biased Comparators for Transcutaneous-Powered High-Current Implants. IEEE J. Solid-State Circuits 2009, 44, 1796–1804. [Google Scholar] [CrossRef]

- Cha, H.K.; Park, W.T.; Je, M. A CMOS Rectifier with a Cross-Coupled Latched Comparator for Wireless Power Transfer in Biomedical Applications. IEEE Trans. Circuits Syst. II—Express Briefs 2012, 59, 409–413. [Google Scholar] [CrossRef]

- Cheng, L.; Ki, W.H.; Lu, Y.; Yim, T.S. Adaptive On/Off Delay-Compensated Active Rectifiers for Wireless Power Transfer Systems. IEEE J. Solid-State Circuits 2016, 51, 712–723. [Google Scholar]

- Kao, S.K. A CMOS Active Rectifier with Time Domain Technique to Enhance PCE. Electronics 2021, 10, 13. [Google Scholar] [CrossRef]

- Banerjee, A.; Bhattacharyya, T.K.; Nag, S. High efficiency CMOS active rectifier with adaptive delay compensation. Microelectron. J. 2021, 112, 105052. [Google Scholar] [CrossRef]

- Tong, X.; Li, M. A High-Efficiency Receiving Circuit for Wireless Power Transmission. In Proceedings of the 2019 14th IEEE Conference on Industrial Electronics and Applications (ICIEA), Xi’an, China, 19–21 June 2019; pp. 1185–1188. [Google Scholar]

- Luo, Z.; Lee, H. A 40.68MHz Active Rectifier with Cycle-Based On/Off-Delay Compensation for Biomedical Implants. In Proceedings of the ESSCIRC 2021—IEEE 47th European Solid State Circuits Conference (ESSCIRC), Grenoble, France, 13–22 September 2021; pp. 227–230. [Google Scholar]

- Lu, Y.; Ki, W.H. A 13.56 MHz CMOS Active Rectifier with Switched-Offset and Compensated Biasing for Biomedical Wireless Power Transfer Systems. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 334–344. [Google Scholar] [CrossRef] [PubMed]

- Lu, Y.; Ki, W. CMOS Integrated Circuit Design for Wireless Power Transfer; Springer: Berlin/Heidelberg, Germany, 2018. [Google Scholar]

- Rabaey, J.M.; Chandrakasan, A.; Nikolic, B. Digital Integrated Circuits: A Design Perspective, 2nd ed.; Prentice-Hall: Hoboken, NJ, USA, 2003. [Google Scholar]

- Lee, H.M.; Ghovanloo, M. An Integrated Power-Efficient Active Rectifier with Offset-Controlled High Speed Comparators for Inductively Powered Applications. IEEE Trans. Circuits Syst. I—Regul. Pap. 2011, 58, 1749–1760. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Huang, C.; Kawajiri, T.; Ishikuro, H. A Near-Optimum 13.56 MHz CMOS Active Rectifier with Circuit-Delay Real-Time Calibrations for High-Current Biomedical Implants. IEEE J. Solid-State Circuits 2016, 51, 1797–1809. [Google Scholar] [CrossRef]

- Xue, Z.M.; Fan, S.Q.; Li, D.; Zhang, L.N.; Gou, W.; Geng, L. A 13.56 MHz, 94.1% Peak Efficiency CMOS Active Rectifier with Adaptive Delay Time Control for Wireless Power Transmission Systems. IEEE J. Solid-State Circuits 2019, 54, 1744–1754. [Google Scholar] [CrossRef]

- Noh, K.; Amanor-Boadu, J.; Zhang, M.L.; Sanchez-Sinencio, E. A 13.56-MHz CMOS Active Rectifier with a Voltage Mode Switched-Offset Comparator for Implantable Medical Devices. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 2050–2060. [Google Scholar] [CrossRef]

- Wu, C.Y.; Qian, X.H.; Cheng, M.S.; Liang, Y.A.; Chen, W.M. A 13.56 MHz 40 mW CMOS High-Efficiency Inductive Link Power Supply Utilizing On-Chip Delay-Compensated Voltage Doubler Rectifier and Multiple LDOs for Implantable Medical Devices. IEEE J. Solid-State Circuits 2014, 49, 2397–2407. [Google Scholar] [CrossRef]

- Erfani, R.; Marefat, F.; Nag, S.; Mohseni, P. A 1–10-MHz Frequency-Aware CMOS Active Rectifier with Dual-Loop Adaptive Delay Compensation and >230-mW Output Power for Capacitively Powered Biomedical Implants. IEEE J. Solid-State Circuits 2020, 55, 756–766. [Google Scholar] [CrossRef]

- Oh, S.J.; Khan, D.; Jang, B.G.; Basim, M.; Asif, M.; Ali, I.; Pu, Y.; Yoo, S.S.; Lee, M.; Hwang, K.C.; et al. A 15-W Quadruple-Mode Reconfigurable Bidirectional Wireless Power Transceiver with 95% System Efficiency for Wireless Charging Applications. IEEE Trans. Power Electron. 2021, 36, 3814–3827. [Google Scholar] [CrossRef]

- Namgoong, G.; Choi, E.; Park, W.; Lee, B.; Park, H.; Ma, H.; Bien, F. 3–12-V Wide Input Range Adaptive Delay Compensated Active Rectifier for 6.78-MHz Loosely Coupled Wireless Power Transfer System. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2702–2713. [Google Scholar] [CrossRef]

| Parameters | Value |

|---|---|

| System Operation Frequency | 13.56 MHz |

| Input Voltage | 3~4 V |

| Load of Resistance | 100~500 Ω |

| Papers | Application | Technology | Frequency | Input Range | Type of MOSFET | Delay Compensation | Power Conversion Efficiency | FoM | POUT,max |

|---|---|---|---|---|---|---|---|---|---|

| TCAS-I’11 [13] | Biomedical WPT System | 0.5 μm | 13.56 MHz | 2.5–3.9 V | PMOS | On & Off | 68–80.2% (@500 Ω) | 0.111 | 20 mW |

| TBCAS’14 [10] | 0.18 μm | 13.56 MHz | 1.5–4 V | NMOS | Off | 82.2–90.1% (@500 Ω) | 0.060 | 24.8 mW | |

| JSSC’14 [17] | 65 nm | 13.56 MHz | 1.15–1.35 V | NMOS & PMOS | On & Off | 72.5–85% (@500 Ω) | N/A | 40 mW | |

| JSSC’16 [14] | 65 nm | 13.56 MHz | 1.3–2.5 V | NMOS | On & Off | 88.5–91.0% (@500 Ω) 91.3–94.6% (@100 Ω) | 0.057 | 248.1 mW | |

| VLSI’18 [16] | 0.35 μm | 13.56 MHz | 2.9–5.4 V | NMOS | On & Off | 84.6–86.1% (@500 Ω) 85.8–89.0% (@200 Ω) | N/A | 12.67 mW | |

| JSSC’19 [15] | 0.18 μm | 13.56 MHz | 1.0–2.5 V | NMOS | On & Off | 82.6–92.9% (@1000 Ω) 85.0–94.1% (@510 Ω) | N/A | 34.1 mW | |

| JSSC’20 [18] | 0.18 μm | 1–10 MHz | 1.8–5 V | PMOS | On & Off | 84.4–91.5% (@300 Ω) 85.2–91.8% (@100 Ω) | 0.022 | 231.6 mW | |

| MDPI Elec.’21 [6] | 0.18 μm | 13.56 MHz | 1.8–3.6 V | NMOS | On & Off | 83.0–90.3% (@100 Ω–1.3 kΩ) | 0.011 | 109 mW | |

| ESSCIRC’21 [9] | 0.18 μm | 40.68 MHz | 1.9–3.8 V | NMOS | On & Off | 81.6–85.1% (@200 Ω) 81.9–86.0% (@100 Ω) | N/A | 207 mW | |

| TPE’21 [19] | 0.18 μm | 85–500 kHz/6.78 MHz | N/A | NMOS | On & Off | 96.2% (@150 kHz) 93.6% (@6.78 MHz) | N/A | 15 W | |

| TCAS-I’21 [20] | 0.18 μm | 6.78 MHz | 3–10 V | NMOS | On & Off | 82.0–93.6% (@1 kΩ) 86.0–93.7% (@500 Ω) | N/A | 288 mW | |

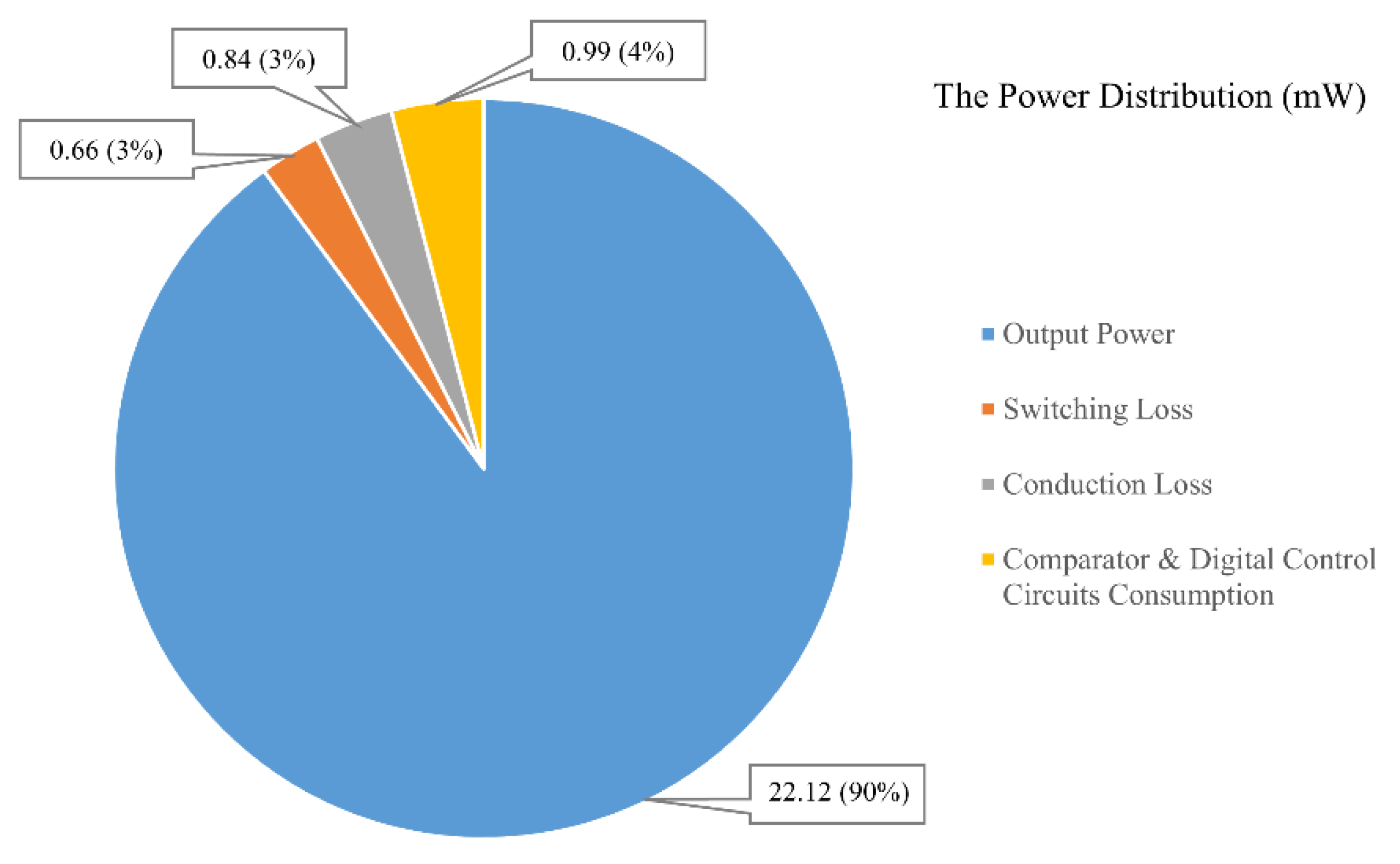

| This Work’21 | 0.18 μm | 13.56 MHz | 3–4 V | NMOS | On & Off | 87.2–88% * (@500 Ω) 88.3–90.6% * (@100 Ω) | 0.029 | 22.12 mW |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Y.; Ma, J.; Tang, X. A CMOS Active Rectifier with Efficiency-Improving and Digitally Adaptive Delay Compensation for Wireless Power Transfer Systems. Energies 2021, 14, 8089. https://doi.org/10.3390/en14238089

Zhang Y, Ma J, Tang X. A CMOS Active Rectifier with Efficiency-Improving and Digitally Adaptive Delay Compensation for Wireless Power Transfer Systems. Energies. 2021; 14(23):8089. https://doi.org/10.3390/en14238089

Chicago/Turabian StyleZhang, Yichen, Junye Ma, and Xian Tang. 2021. "A CMOS Active Rectifier with Efficiency-Improving and Digitally Adaptive Delay Compensation for Wireless Power Transfer Systems" Energies 14, no. 23: 8089. https://doi.org/10.3390/en14238089

APA StyleZhang, Y., Ma, J., & Tang, X. (2021). A CMOS Active Rectifier with Efficiency-Improving and Digitally Adaptive Delay Compensation for Wireless Power Transfer Systems. Energies, 14(23), 8089. https://doi.org/10.3390/en14238089