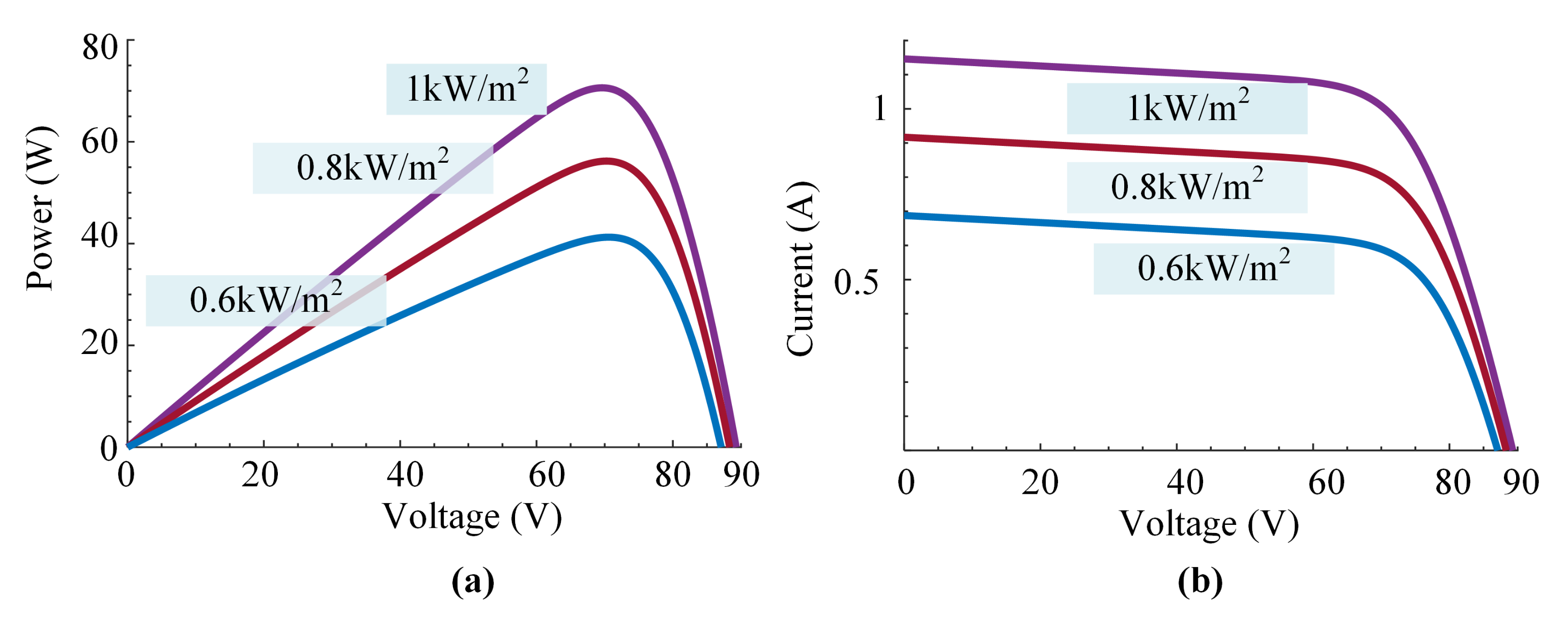

1. Introduction

The major goal of a Building Integrated Photovoltaic (BIPV) system is to create a net-zero energy buildings with lowering

emissions in the industry. According to the assessments on BIPV systems market, the global compound annual growth rate is expected to be over 45% from 2010 to 2021 [

1,

2]. The low-cost thin-film photovoltaic production methods will enhance the BIPV market growth. As a result, BIPV systems have evolved into architectural elements, demanding attributes such as reduced size, ease of grid integration, and the capacity to gather maximum energy in all weather conditions. Inverters that convert DC to AC with high efficiency as well as the low profile is necessary to meet these requirements. For BIPV applications, a microinverter based solution is the best option [

3,

4]. In this context, some of the advantages of this technique should be mentioned, including:

Individual Maximum Power Point Tracking (MPPT) systems capture the most energy;

For future development and maintenance, it is scalable with a plug-and-play option;

BIPV systems have a high power density while being light in weight;

Improved safety because the DC wire can be shortened and the AC cables come down from the roof.

In the market, there are many microinverters for PV modules [

5]. However, isolated systems, which are commonly utilised, increase size, weight, and expense. Multiple stage inverters are another frequent arrangement that decreases efficiency and lifespan [

6].

Table 1 shows a sample of microinverters that are available at the moment for commercial use. It demonstrates the maximum capacity, power efficiency, and gross weight of these inverters. It can be shown that at maximum power, the maximum efficiency varies from 94% to 96%. Single-stage transformerless inverters, on the other hand, are built for excellent performance with fewer parts and less energy loss [

7].

In [

8], various single-stage topologies were investigated. There are several subcategories in this field of research, depending on whether the topologies are formed from boost or buck-boost [

8]. The differential boost inverter, which consists of dual boost converters that creates a sinusoidal wave which has

phase shift, is described in [

9]. The main drawback to this setup is that the high-frequency switches are hard switched, resulting in substantial switching losses and electromagnetic interference. Switching loss issues are addressed in the buck boost half-bridge inverter topology described in [

10] by reducing the number of switches operating during each cycle of the reference voltage. Inconvenience with this inverter for BIPV application is that it needs two PV modules on the source side, one of which is used in the half-cycle. The boost microinverter described in [

11] was primarily based as a microinverter for roof-top solar Photovoltaic systems, but, the architecture was not suited for BIPV applications due to the usage of bulky inductors. Flying buck-boost inverter that is inductor-based has been described in [

12], this has reduced the switching losses through the employment of three power electronics switches for every half a cycle, however the number of components in the conduction path at a given time is higher in this topology, leading to an increased conduction loss. The buck-boost inverter introduced in [

13] has minimum switching losses and size with four switches. To boost the voltage, the inverter shown in [

14] employs a capacitor-based charge-pump model. It lacks buck-boost capabilities and control of MPPT testing is difficult because of the non symmetric input current, despite being double grounded to avoid leakage current.

Following a thorough analysis of the literature, the design of the single-stage microinverter with the aforementioned features has raised interest:

Buck-boosting with reduced losses and heat dissipation by using fewer conduction devices;

The influence of EMI and harmonic distortion is reduced when leakage current is kept under the standard limit;

Lower power ranges with higher efficiency;

Protection against shoot-through issues.

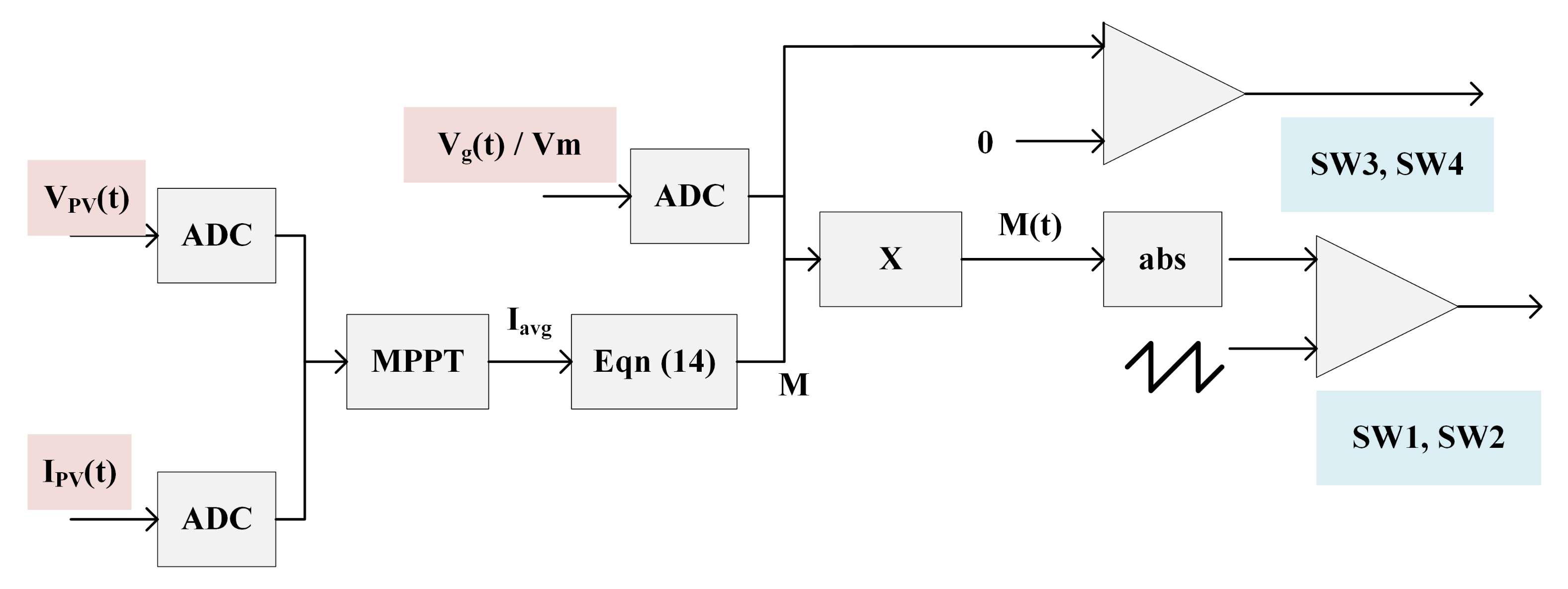

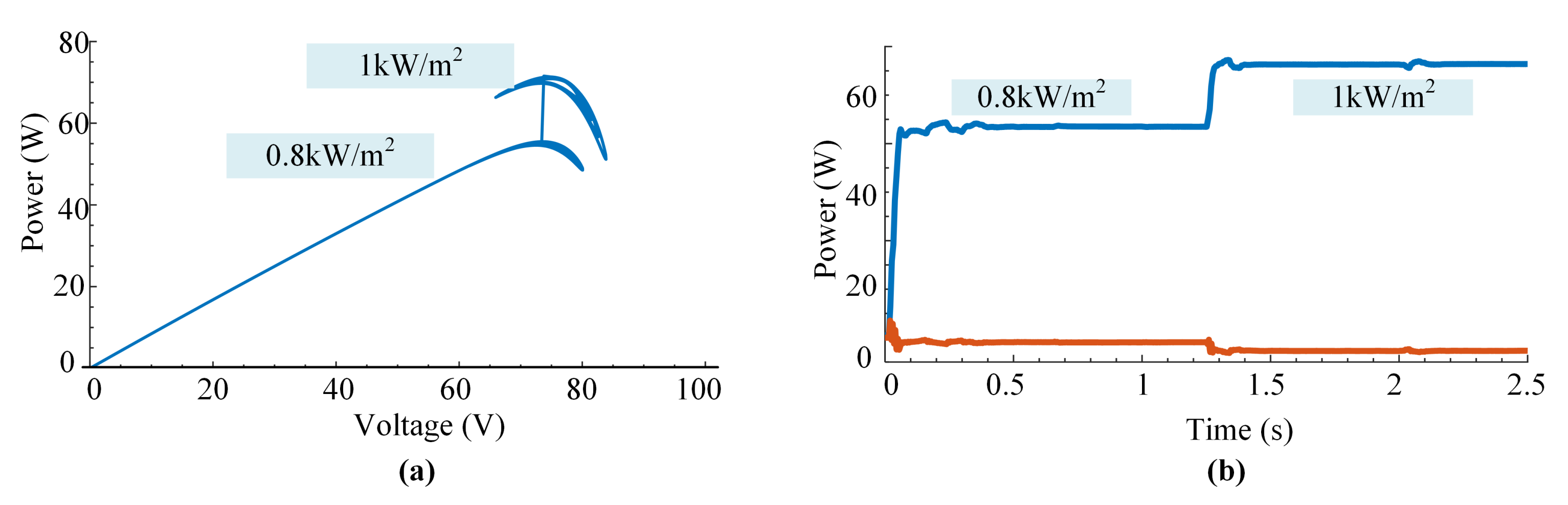

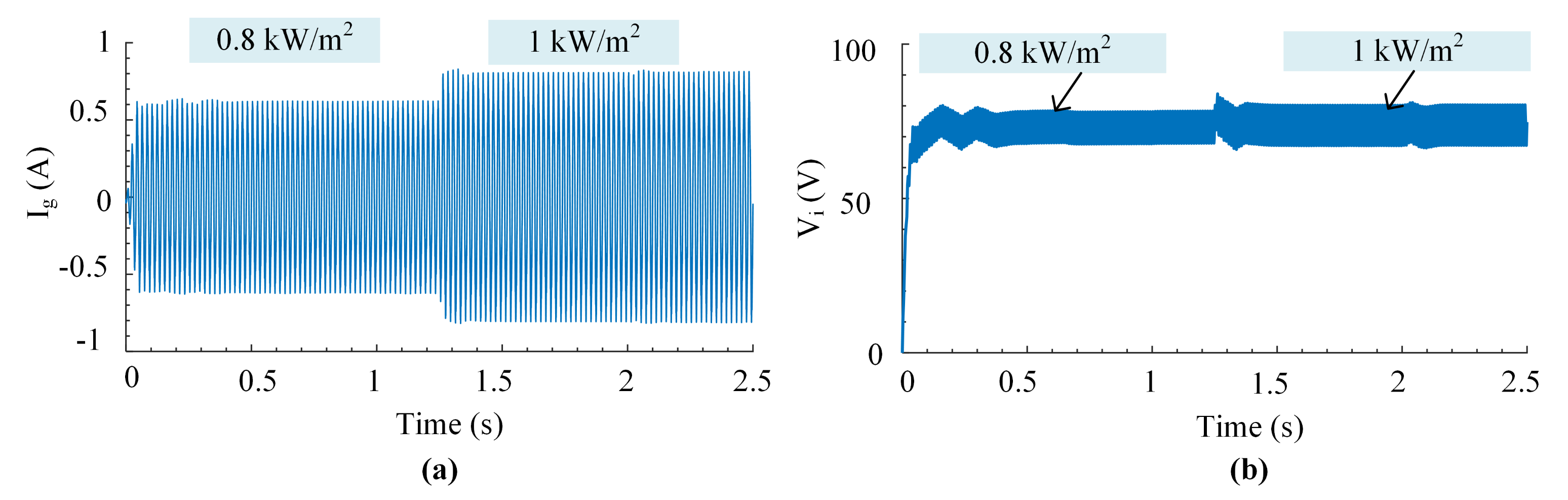

In this case, this article proposes the Buck-Boost Single-stage Microinverter (BBSM) topology to convert DC power to AC, which satisfies all of the aforementioned requirements. The PV system under consideration uses an appropriate switching approach that allows the inverter to run in Discontinuous Conducting Mode (DCM) and track maximum power using the Perturbation and Observation (

) technique [

15]. For the first time, this paper describes a number of unique and scientific additions to the BIPV system:

With fewer active and passive components, buck-boost capability has been realized.

In the lower power range, a better efficiency was achieved.

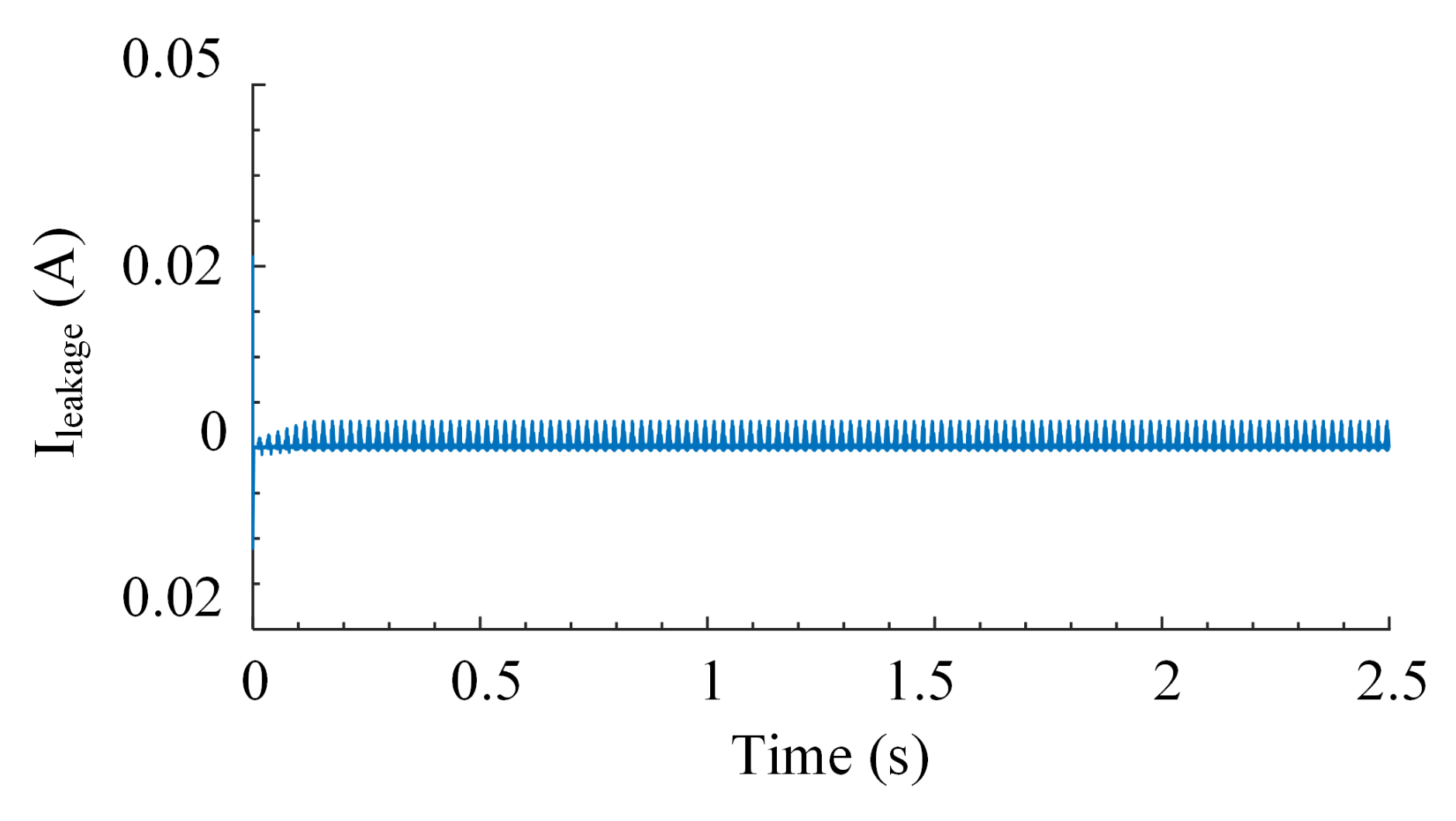

Leakage current value has been reduced within the limit.

The following is an overview of the paper’s structure: Principle of operation and analysis of the proposed topology is presented in the next section. Design of passive and active elements of BBSM topology is shown in

Section 3. This is followed by a loss analysis in

Section 4. In

Section 5, design validation of the topology is shown using simulation and experimental results. Finally, conclusions are presented in

Section 6.

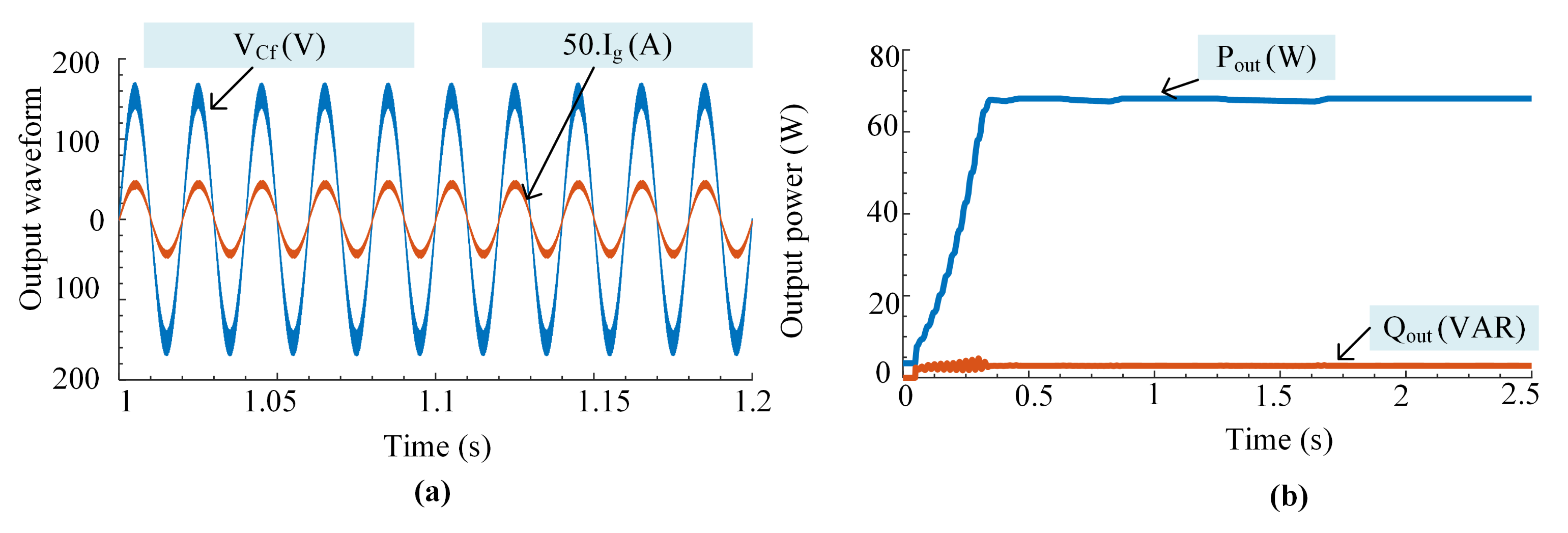

2. BBSM’s Operating Principles and Analysis

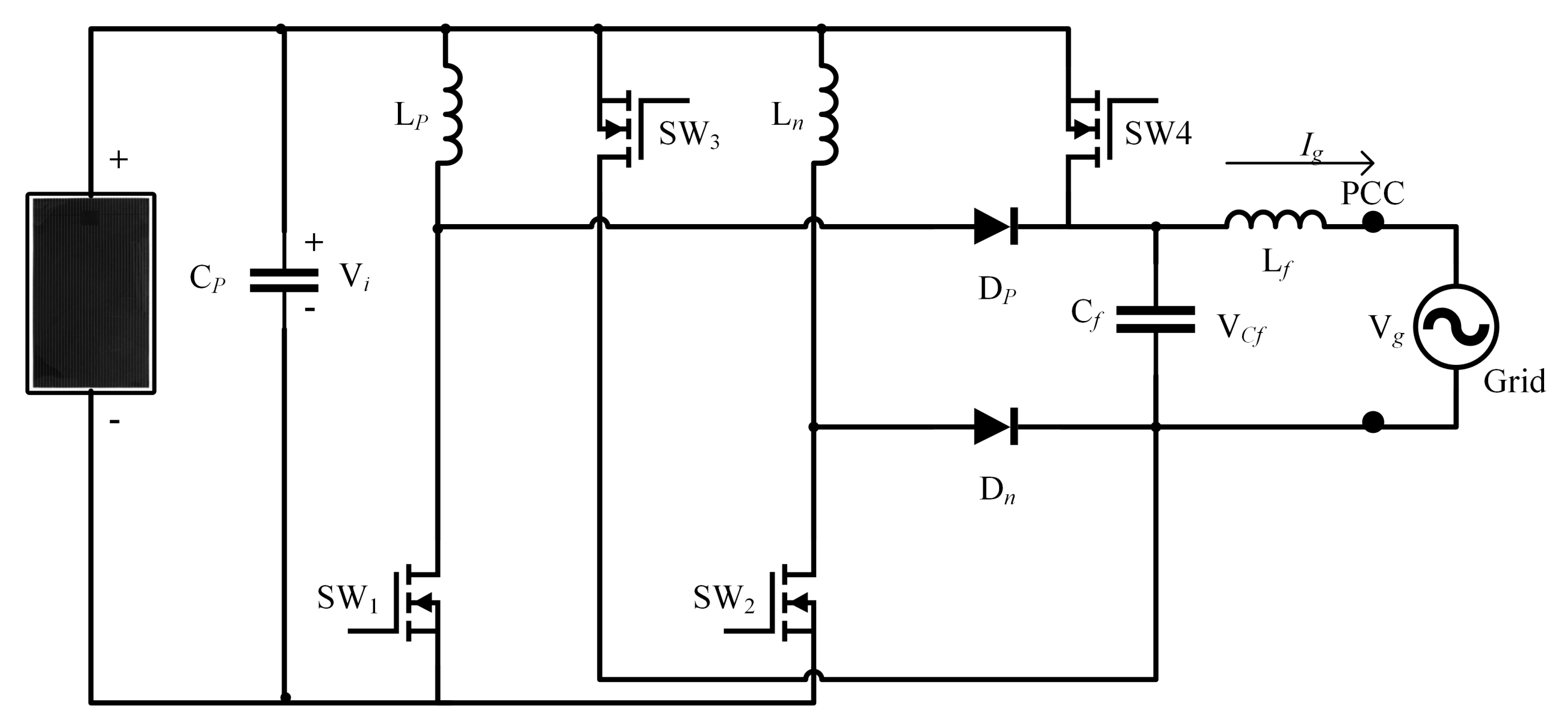

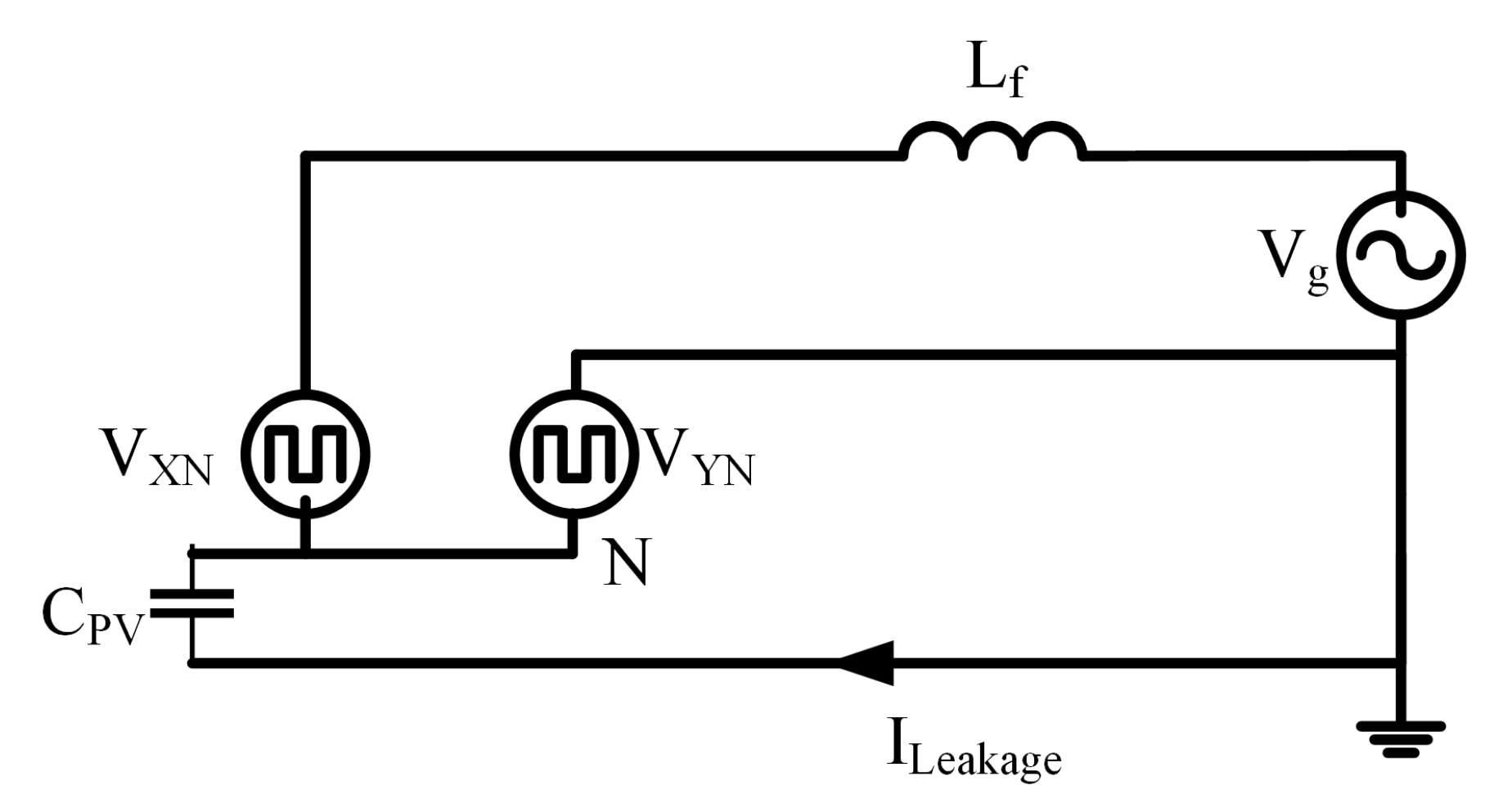

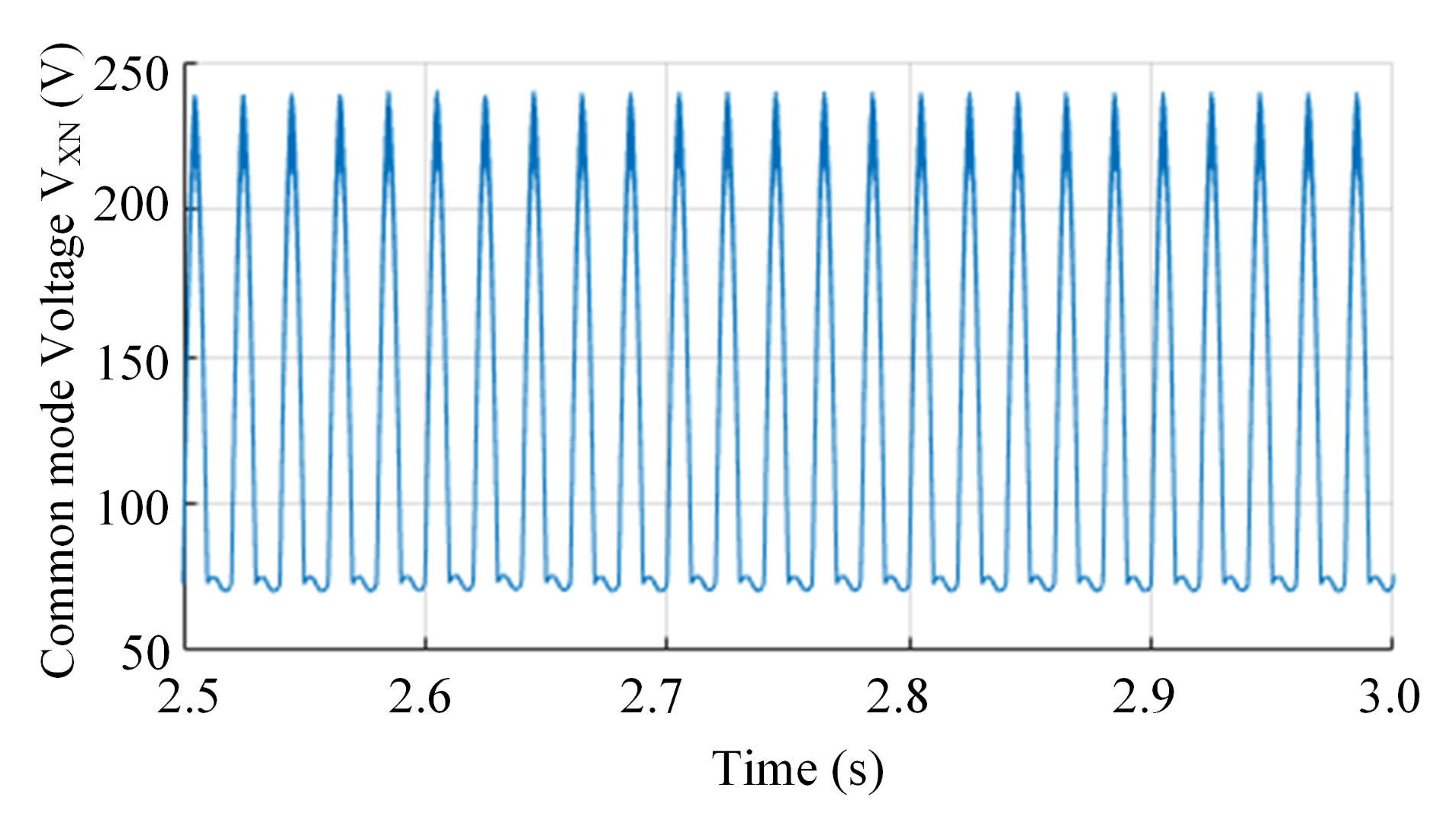

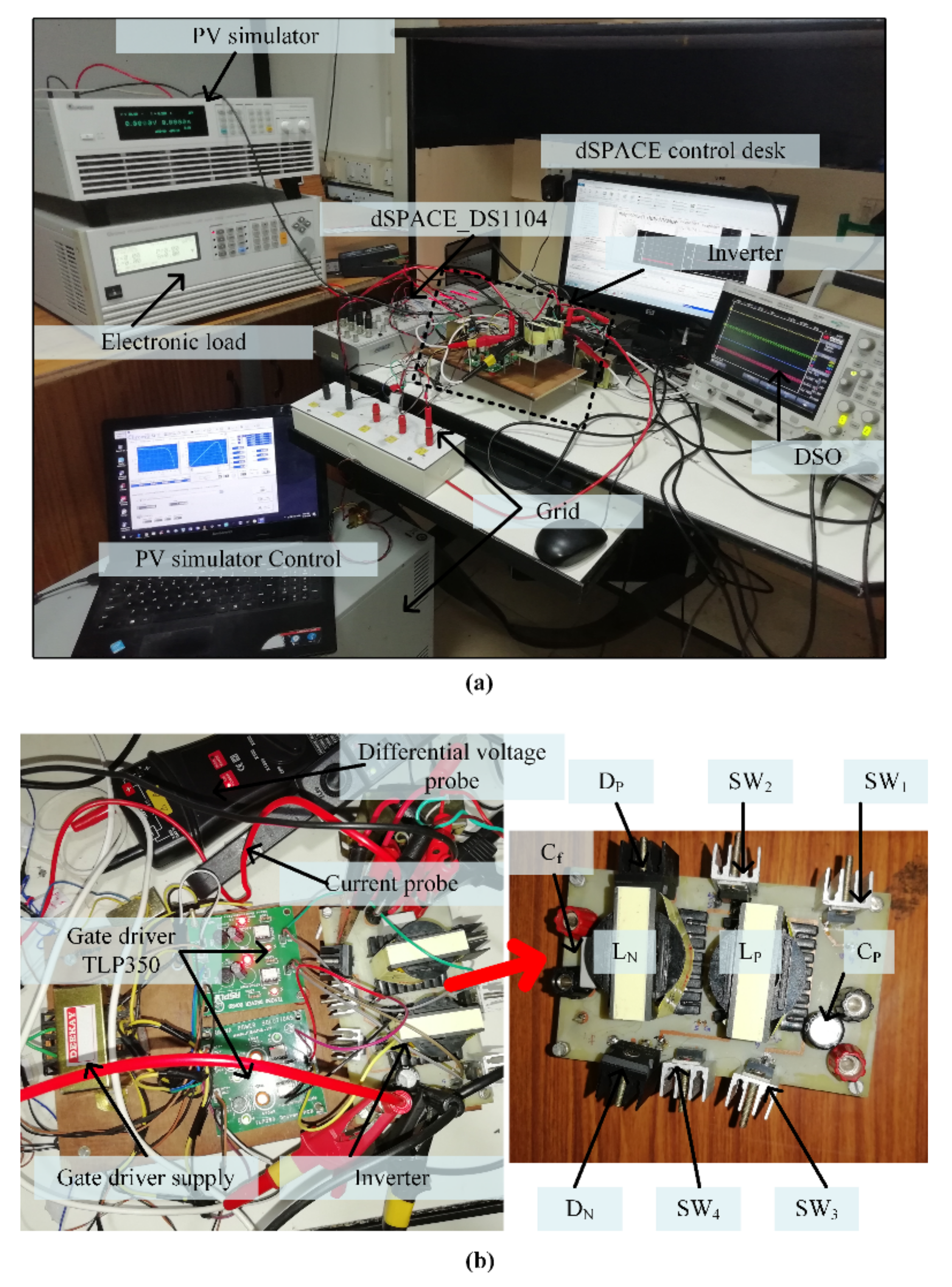

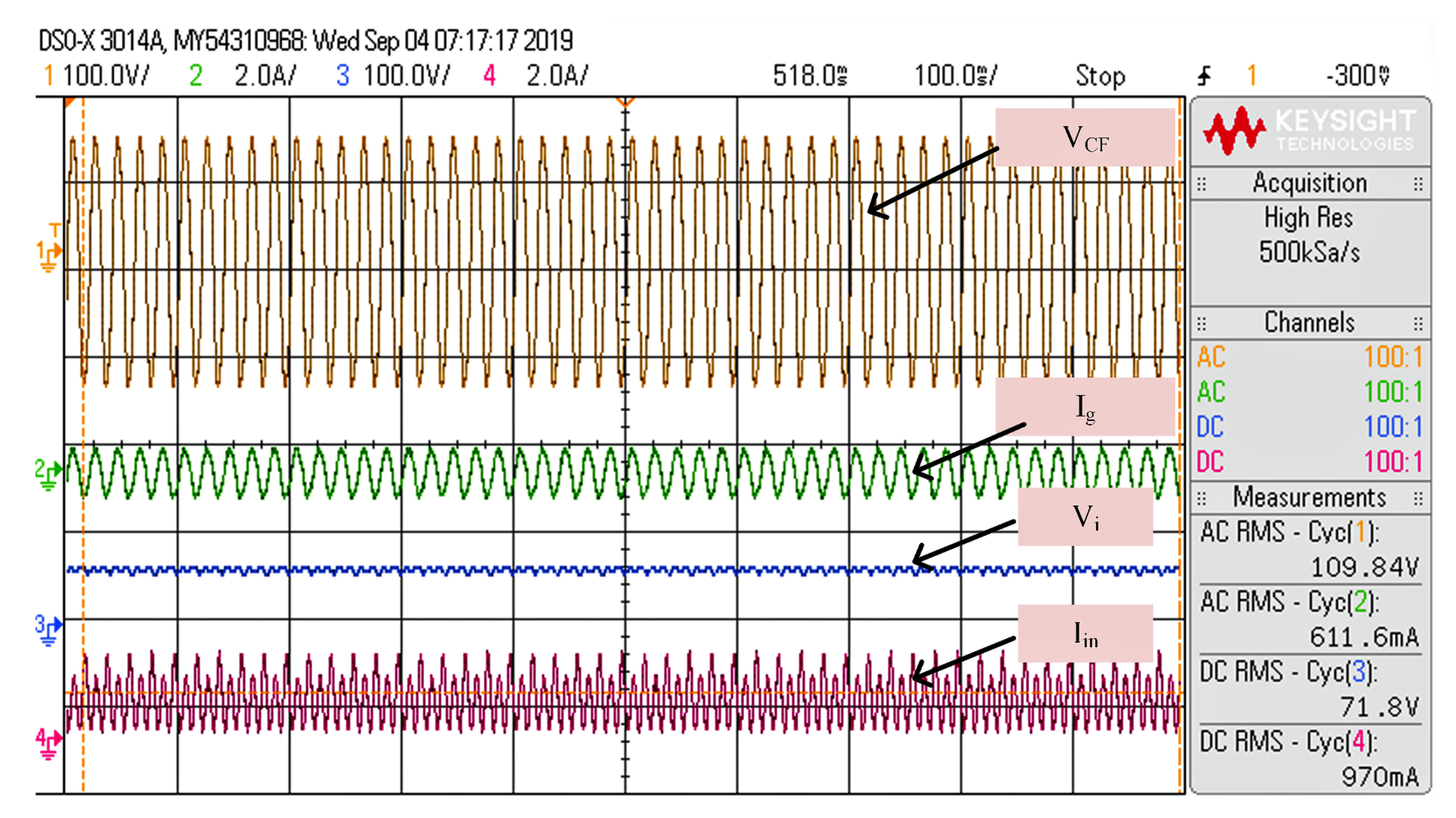

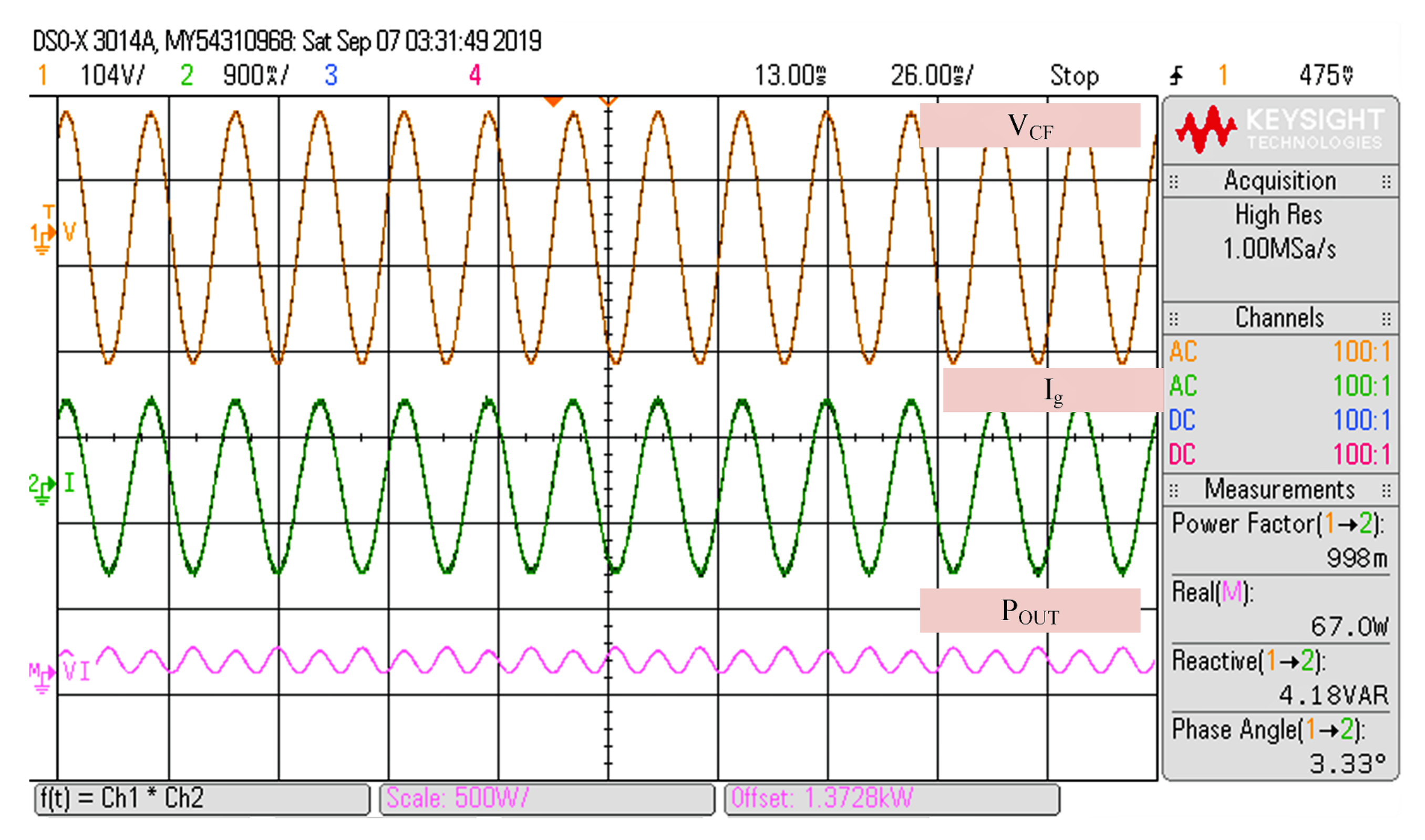

The BBSM topology is shown in

Figure 1 it encompasses four semiconductor switches controlled devices, two uncontrolled devices (diodes), and a C-type filter. At the Point of Common Coupling, the proposed inverter intersects the grid (PCC). were employed for buck-boost operation and grid injection of PV energy. They also prevent inverter shoot-through issues. This increases system reliability while also making switching processes easier. During both half cycles of the reference,

and

are activated to energize the inductors

and

, respectively. The

, as well as

plays a crucial role in inductors’ discharge and energy injection into the grid. The load is assumed as pure resistive load

.

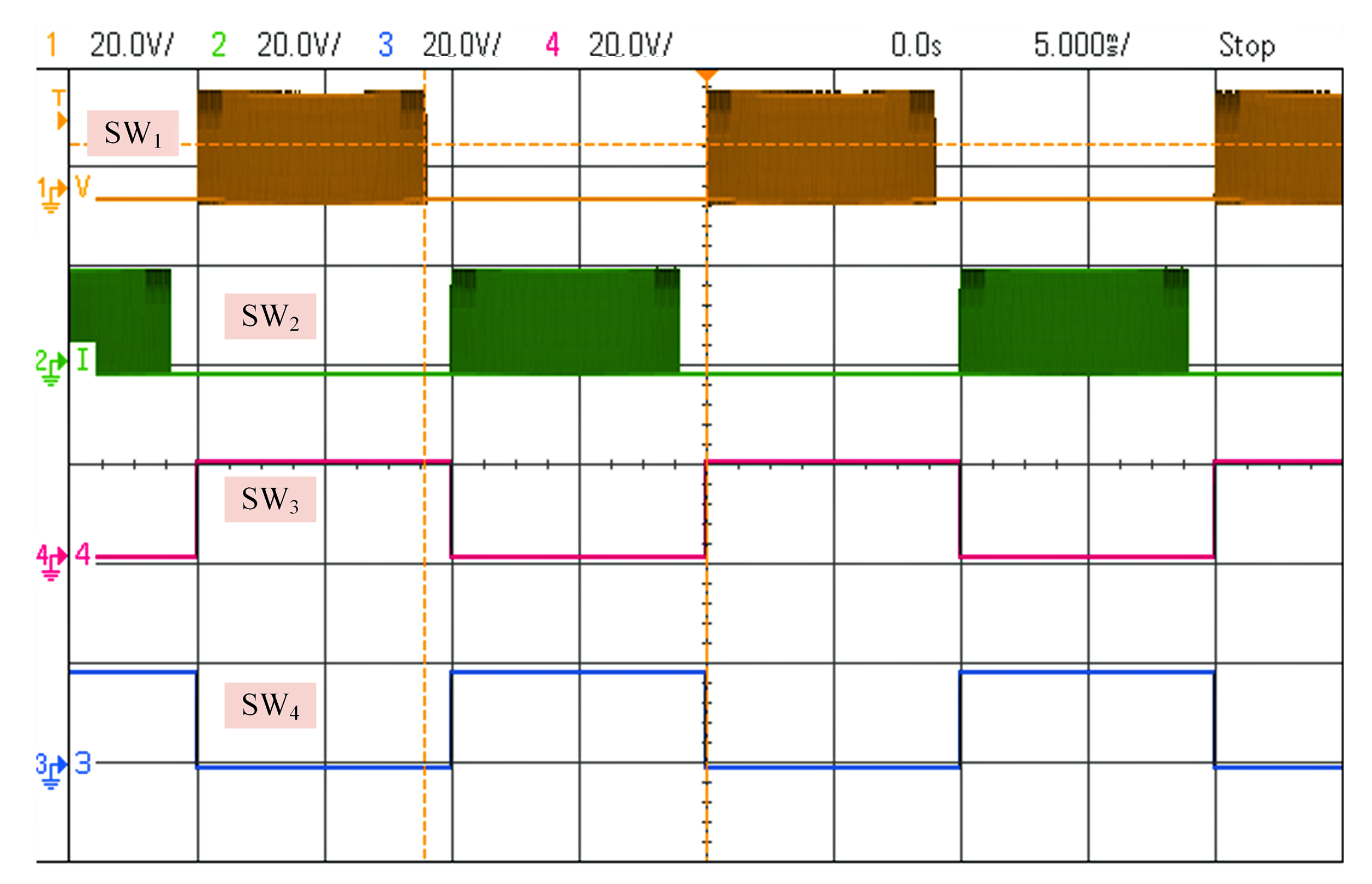

The and switches have a high operating frequency. The and switches operates at low frequency. All of the switches have a built-in safety diode. The inverter can be operated in six distinct modes, three of these modes occurred during each half cycle of the common reference or control signal. These occurred in a row, i.e., one after the other. In both reference cycles, the BBSM topology operates similarly to a typical DC-DC buck-boost converter, except that the suggested inverter topology modulates on a quasi-sinusoidal duty-cycle.

The control strategy is essentially accomplished through a two-steps scheme: the first is achieved via the control of the PV array’s voltage by the inductors’ current imposition, the second is achieved via the control of the grid current via the output capacitor’s voltage imposition. The principle of operations is described with the aid of the control variables are as follows:

Parameter O indicates the status of the output voltage half-cycle, during the positive part of the reference, O == 1, and switches and are in the ON state. During the negative part of the reference O == 0, and and are in the ON state. The reference cycle is obtained when is compared to 0.

Parameter U indicated when the output voltage has to be increased U == 1, this is achieved through triggering switches or or to be stepped-down (decreased) then U == 0 and achieved when triggering switches or this is accomplished by comparing and .

Parameter and indicates the charging / discharging process of and , respectively, as follows: = 1 & = 1, turn on / = 0 & = 1, turn on )/ this is generated by comparing the and inductor current .

Table 2 summarises the state of passive and active components in each mode of operation.

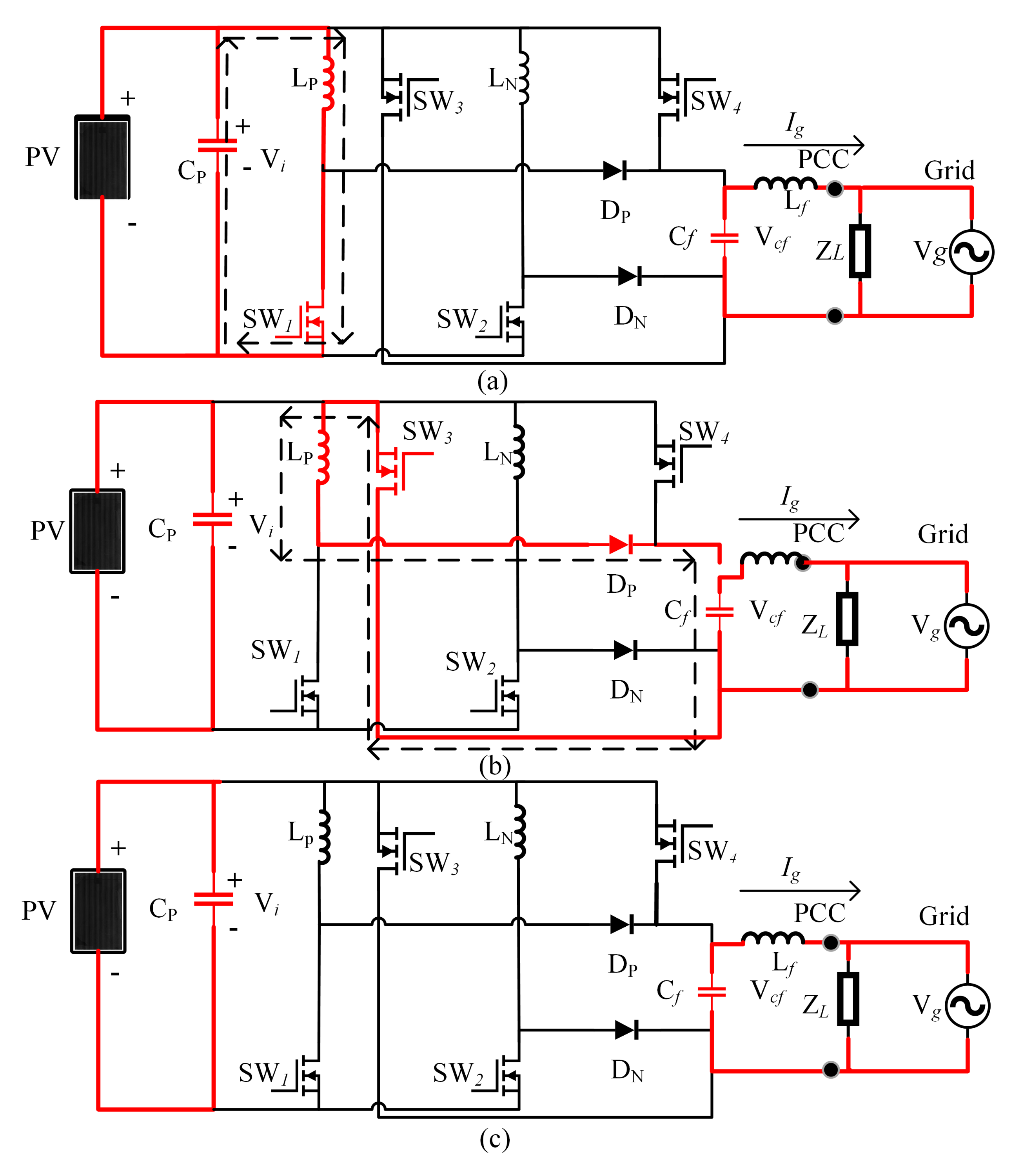

Figure 2 and

Figure 3 depicts the three modes of functioning of the topology in the positive and negative half-cycles, respectively. In different modes, the highlighted components are active. It’s vital to remember that during each operation, only one switch is in the conduction path, even if another switch is on. This may help to lower the total power loss of the system.

The operating mode

is carried out for the current assessment of the inductor

as shown in

Figure 2a, and switch

is activated due to this reason. Differential equations for control variables are derived from

Figure 2a. Here

is the input voltage and

is the grid voltage,

is the output filter capacitor, and

is the load.

After storing the energy in

during

mode to provide the required voltage gain, the

working mode is initiated. The stored energy is transferred through the output filter capacitor–load combination, while the positive half cycle diode

becomes forward biased in addition to creating a closed-loop via

as well as the inductor

, meanwhile,

is turned into its off status. The operating operation can be expressed using the differential equations from

Figure 2b as follows;

When the energy stored in inductor (

) is transmitted to capacitor load combination (

), the

mode is then initiated. As shown in

Figure 2c, the output energy of the filter capacitor is delivered under this mode.

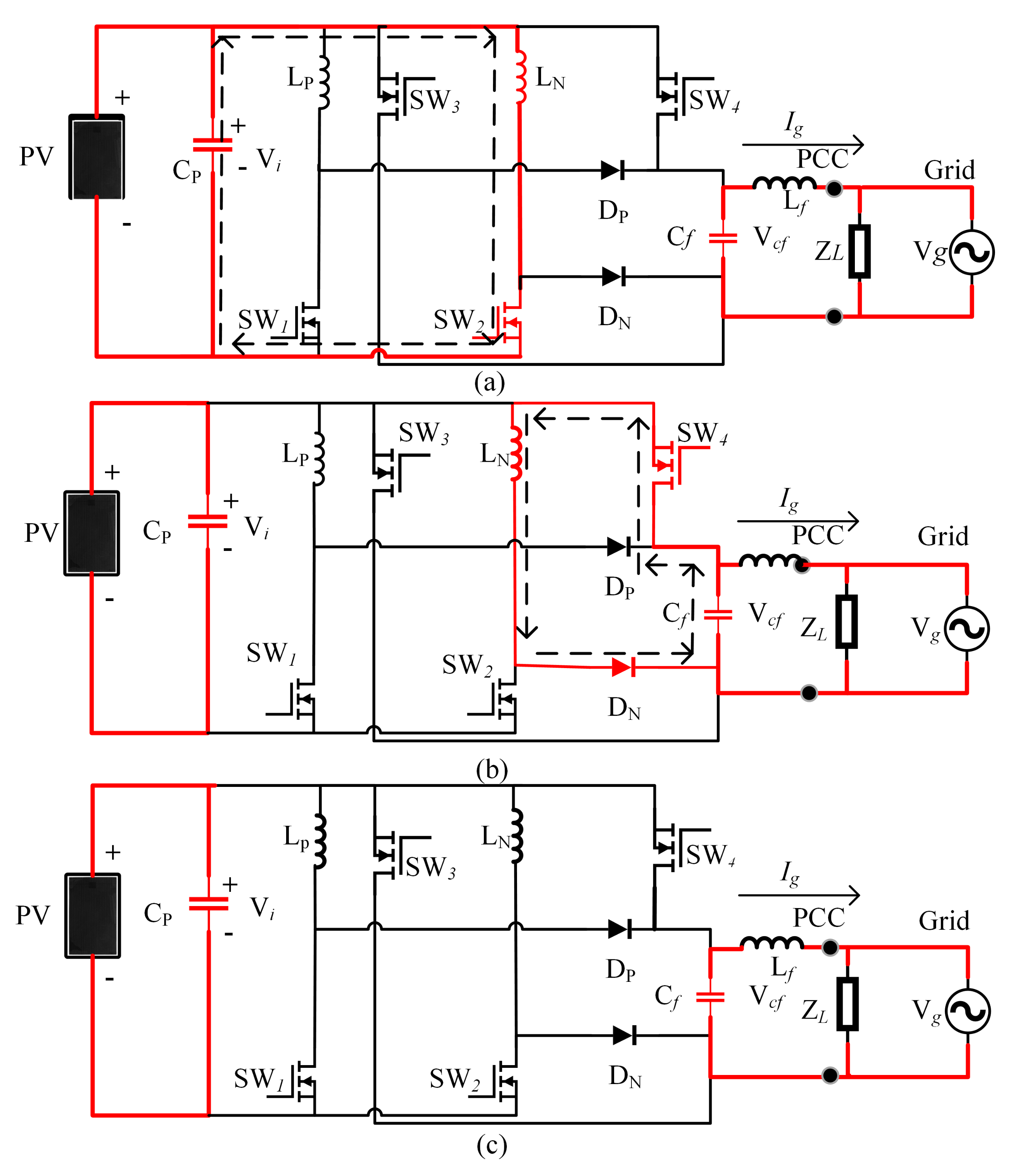

The

operation mode is employed to apply current to inductor

, as shown in

Figure 3a, and switch

is enabled for this reason. The following differential equations for control variables are derived from

Figure 3a.

After storing sufficient energy in the negative half cycle inductor (

) to provide the required voltage gain, the

working mode is activated. The stored energy is delivered to the filter capacitor-load combination, while the diode

becomes forward biased in addition, establishes a path of conduction via

as well as the inductor

,

is triggered off mean. From

Figure 3b, the following differential equations are found.

mode is activated, when all of the energy from the inductor (

) is shifted to the capacitor (

). As shown in

Figure 3c, the filter capacitor energy can be delivered to the output load in this mode.

The current flow direction is represented as dashed lines in

Figure 2 and

Figure 3.

To evaluate the proposed topology, the following assumptions are made.

Equation (

11) shows the relationship between

(Grid frequency) and

(Switching frequency of switches

and

).

The semiconductor devices device possesses ideal characteristics.

Throughout each switching time-period , the grid voltage is considered constant.

MOSFETs and diodes have zero forward resistance and infinite reverse resistance.

The duty cycle remains constant during each switching period.

The inverter’s operation is maintained DCM.

The load is resistive

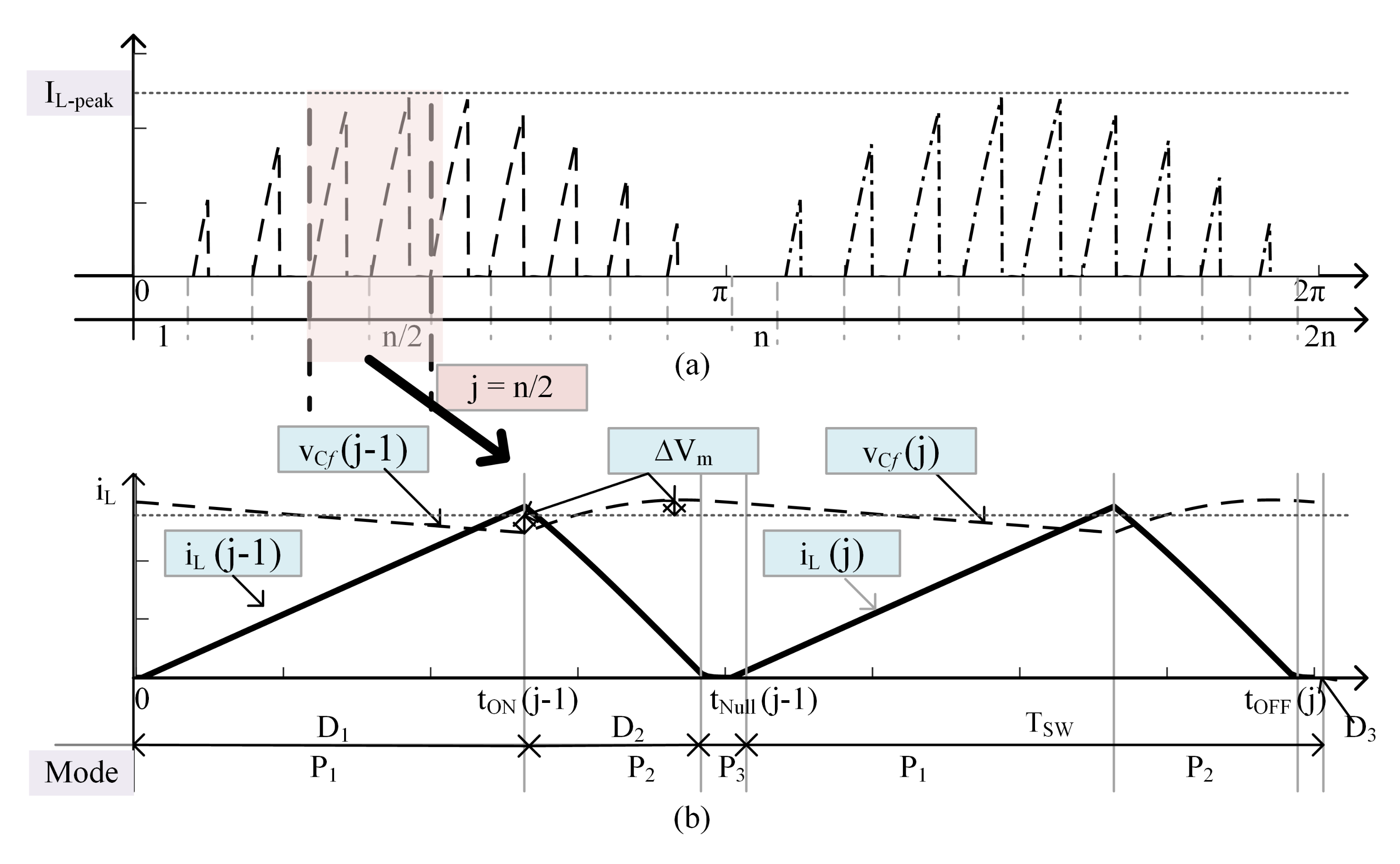

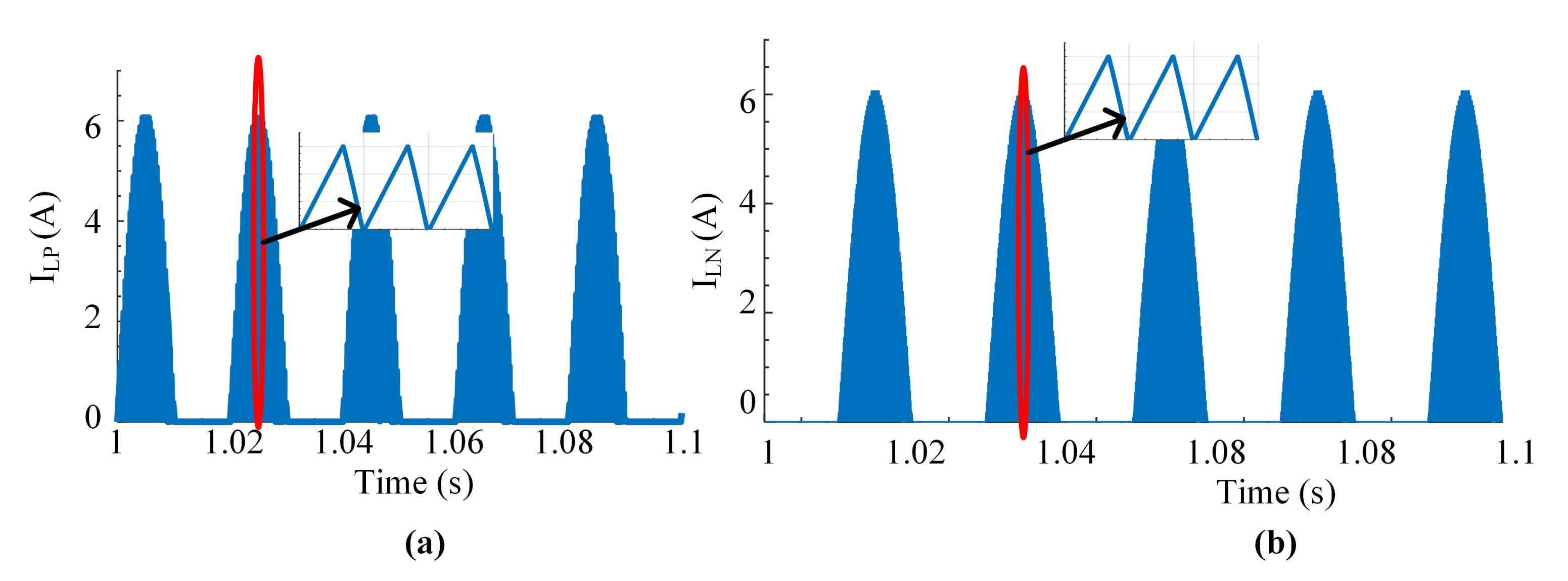

The

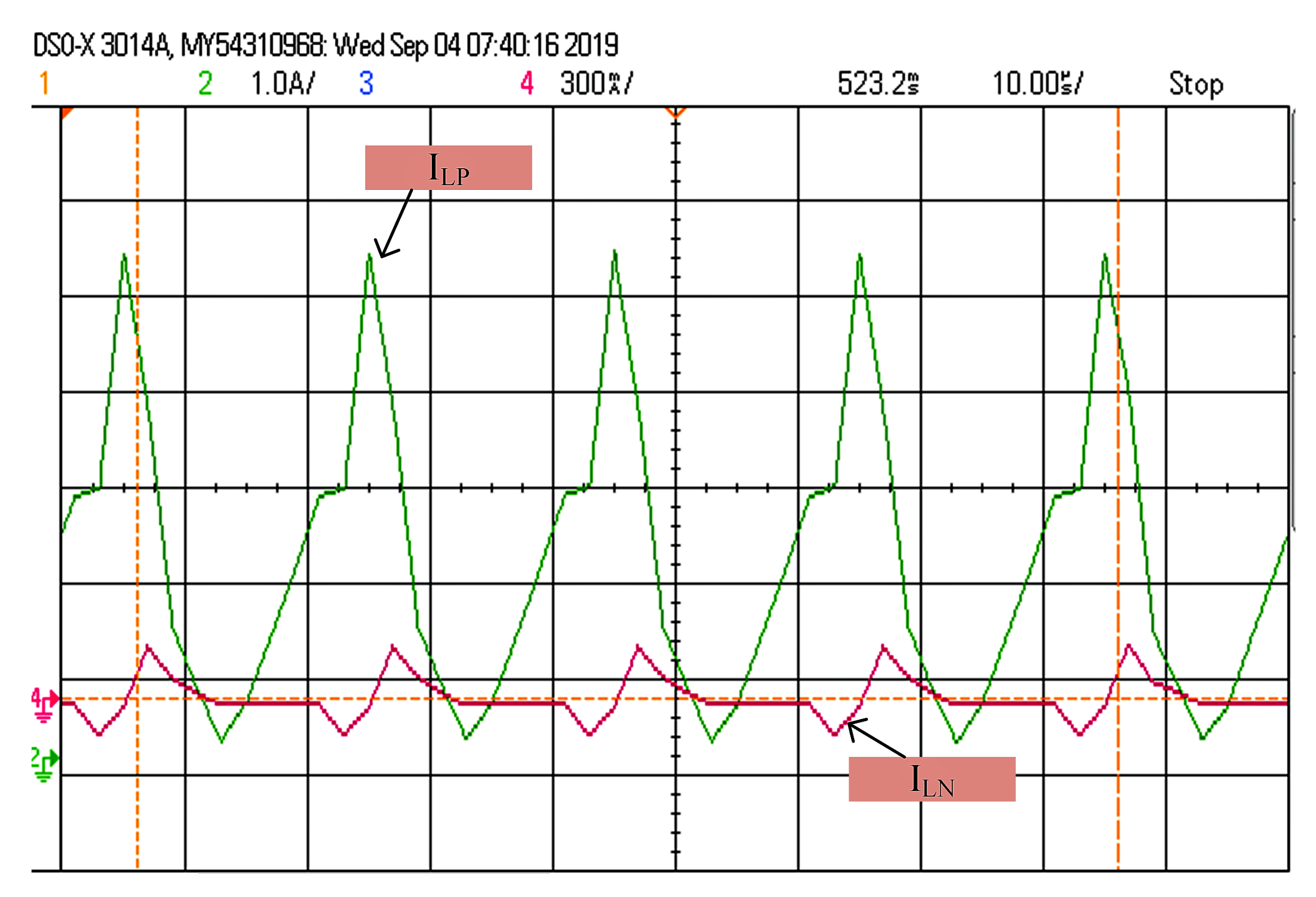

and

behave similarly during both reference cycles, they are referred to as

L in the analytical section. Inductor current at the peak interval in zoomed in

Figure 4b. In

mode, the inductor current increases. For the

jth switching period, the inductor charging current

achieves its maximum value at

. As the quantity of energy transferred to the output is determined by the magnetizing current of the inductor, the peak value of the current (

) is provided in (

12) and depends on the output power. (

13) can be used to express the energy stored in the inductor (

).

Using Equation (

13), the average value of current in inductor

throughout a swapping period expressed in Equation (

14). As noted in (

15), the current at output A is a sinusoidal changing current and that can be expressed as

, as illustrated in the expression (

14). As a result, the energy required on the output side

can be written as (

16). The peak output voltage is

in this case. By equating the Formulas (

13) and (

16), the charging duty ratio may be stated as (

17).

The discharging duty ratio can be determined as (

19).

The inverter modulation index is thus indicated by (

20) and static gain is given in (

21).

2.1. DCM Operational Requirement

The inductor current discharge completely in time

, if the average value of the current is lesser than the maximum ripple. Until the next switching cycle, the current will stay zero. When this pattern occurs, the inverter is in DCM mode. If the suggested inverter topology meets DCM condition for the time duration

, it operates in DCM mode throughout the grid cycle. The essential requirement for sampling duration

of the grid voltage is applied as described in (

22) for calculating the peak modulation index M limit for maintaining DCM functioning. In accordance with the conditions, the peak modulation index limit is calculated based on (

23).

The peak output voltage, , is used here.

2.2. Elements for Energy Storage Design

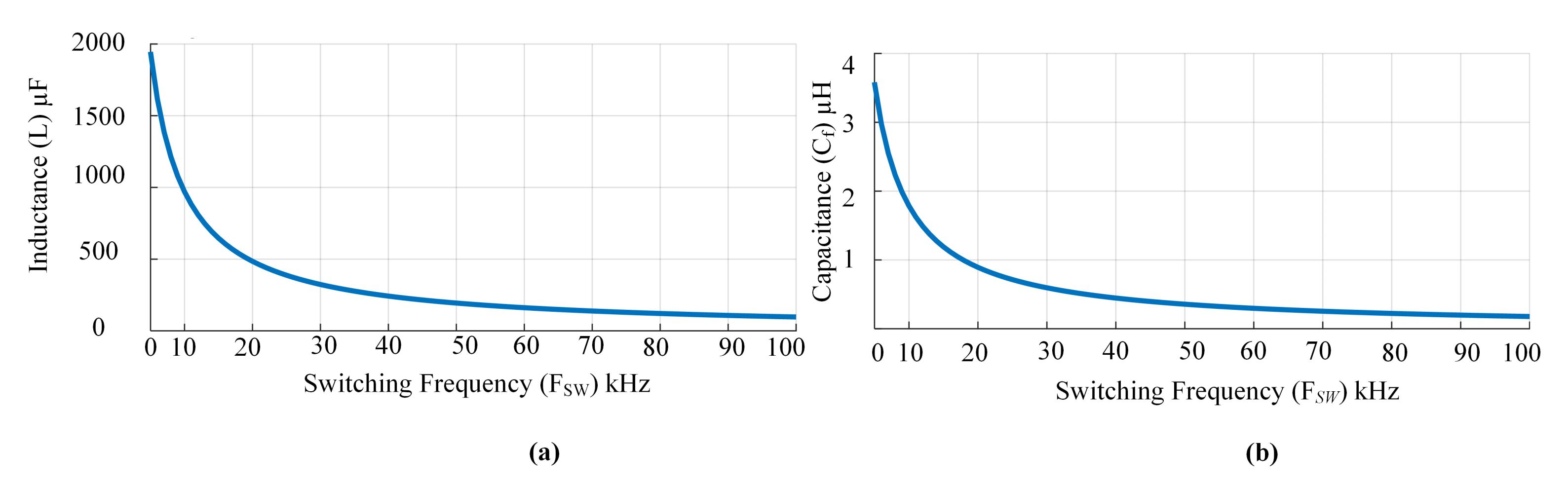

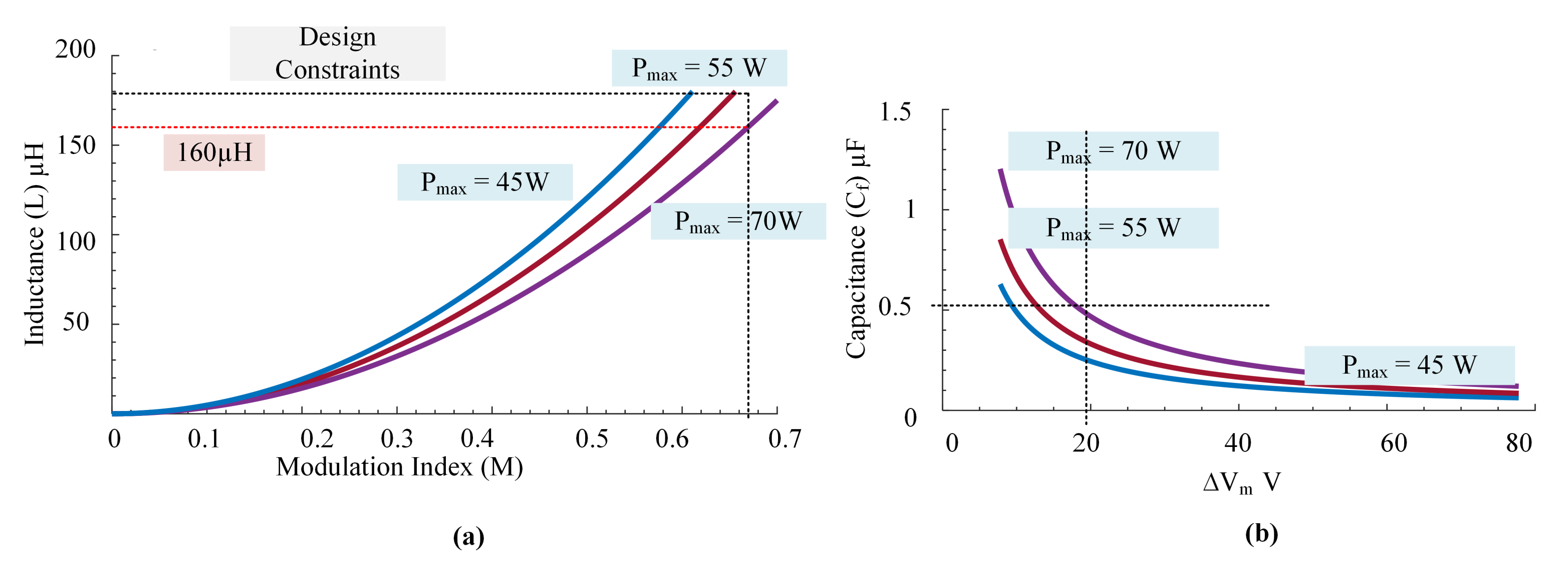

As the physical size of the inverter is determined by the size of its energy storage devices, the design of these elements is critical.

Figure 4 depicts the inductor current

. Energy is delivered in a discrete form since the inverter works in DCM. During each switching interval (

) Inductor L will store and transmits energy. Thus, a

capacitor is used in the inverter topology. The inductor’s energy has been completely transferred to the capacitor Cf. During the peak phase (

), it transfers most of the energy from L to

. The inductor should be able to handle (

), where

is the maximum input power. This situation assures when the grid receives (

) during each grid cycle, hence (

24) is derived from (

13). Equation (

25) may be used to calculate the inductor value by replacing (

12) into (

24). The relationship between L and

is seen in

Figure 5a from (

25). The maximum power output of a Photo-Voltaic module determines the design value of L. This condition ensures that DCM will work at any power level.

The total energy accumulated within the inductor (L) during

is totally released to the capacitor during

, as shown in

Figure 4. The variations in the energy over

can be represented in (

26). The

is designed based on the expression (

27). The relationship between

and

is depicted in

Figure 5b from (

27)

2.3. Power Device Selection

The whole cost and performance of a system are affected by the rating of the power devices in an inverter, which includes storage duration, current gain, and switching frequency. the calculation of voltage, as well as current load on power equipment, can be calculated. Switches maximum voltage is the same as the capacitor’s maximum voltage. Similarly, the peak current of the switches matches the maximum inductor current. The total active switch stress SS must be computed if the inverter has k switching devices as stated in (

28) using the RMS current

and the voltage

.

Table 3 lists all of the switches RMS current as well as the peak voltage expressions.