Opposite Triangle Carrier with SVPWM for Common-Mode Voltage Reduction in Dual Three Phase Motor Drives

Abstract

1. Introduction

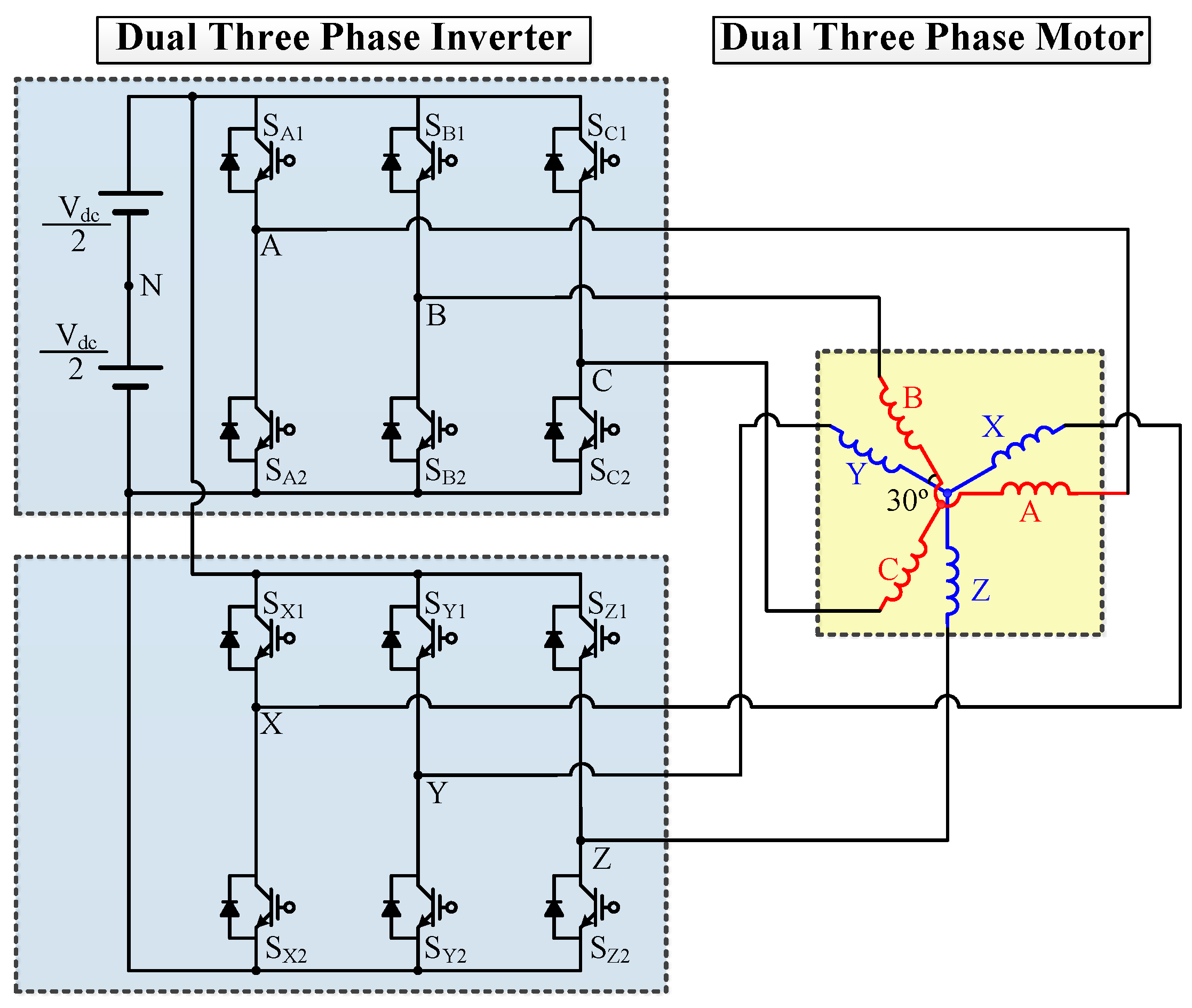

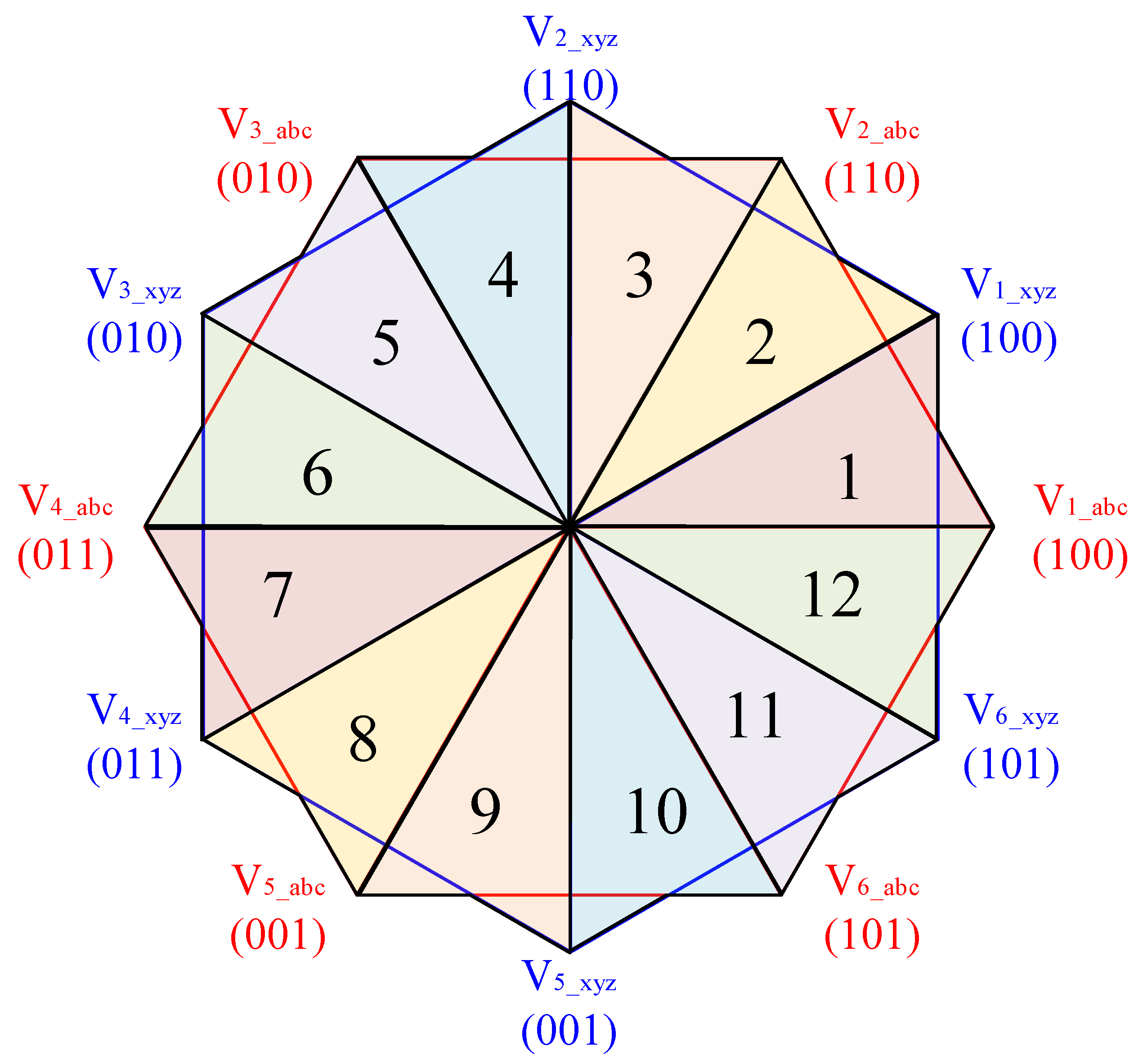

2. CMV in Dual Three Phase Motor

2.1. CMV in Dual Three Phase Motor

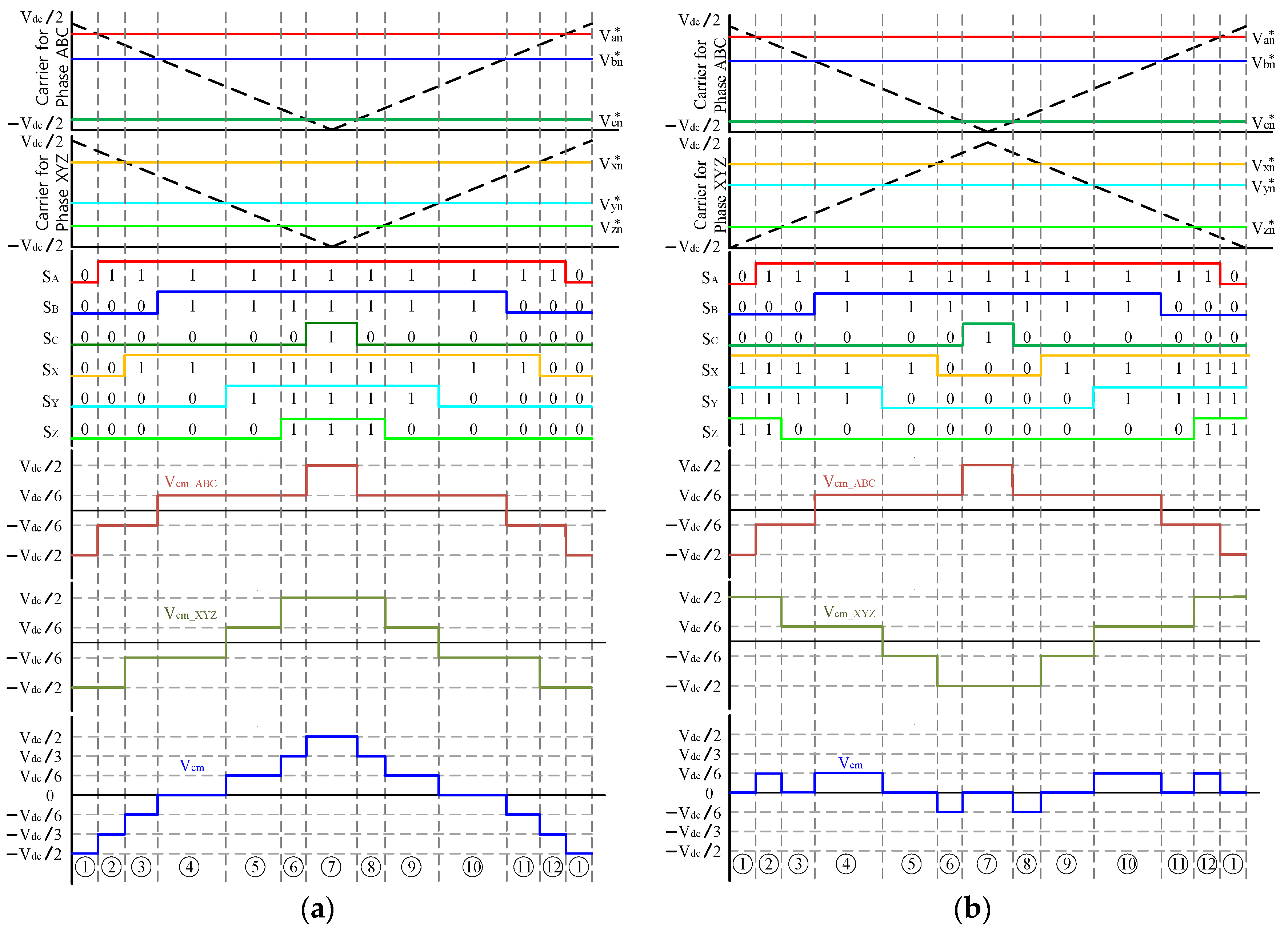

2.2. CMV According to the Carrier Method

2.3. Relationship between Change Frequency of CMV and Dwell Time in Zero Voltage Vector

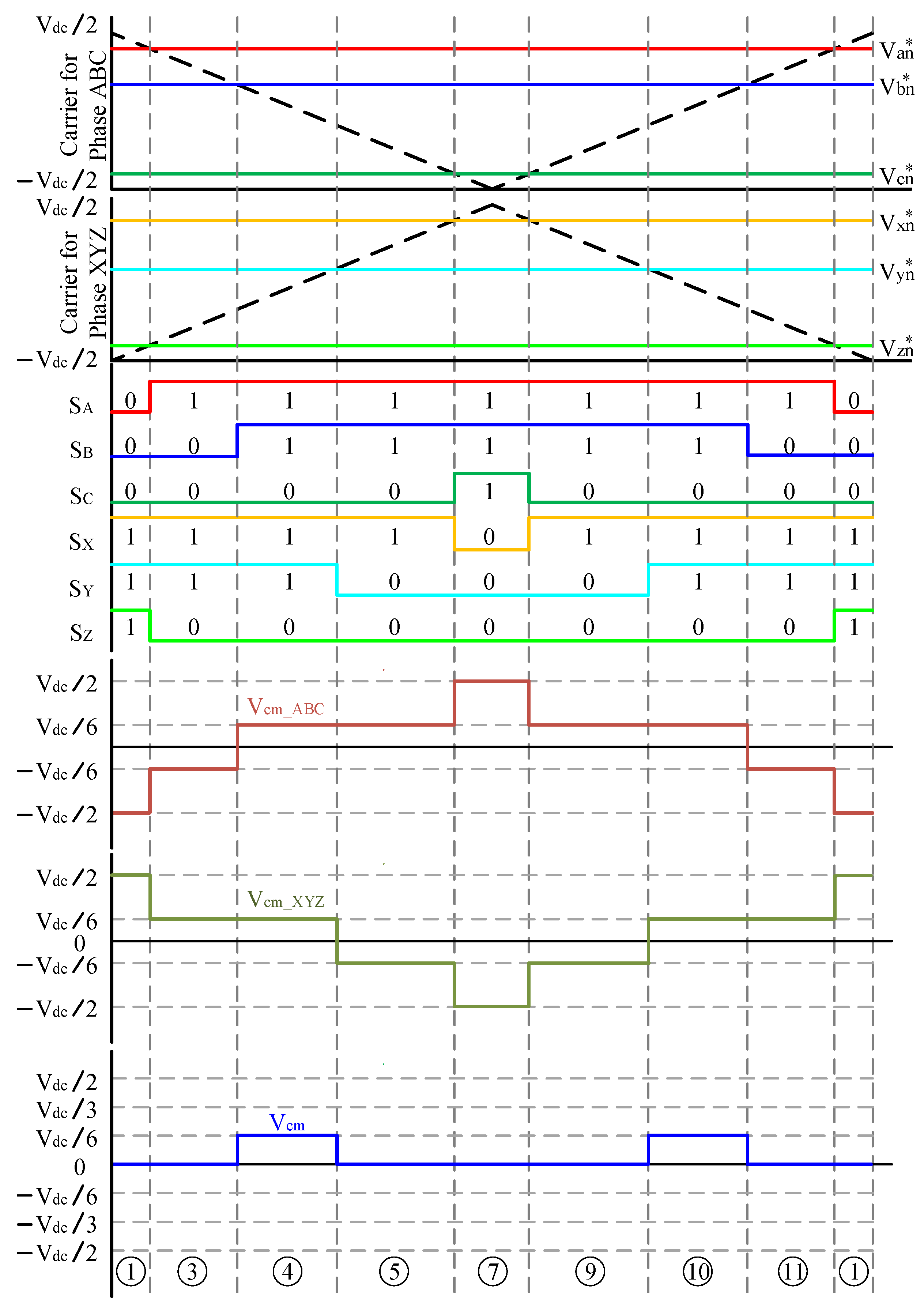

3. Reduction of Change Frequency of CMV by Synchronization of Dwell Time in Zero Voltage Vector

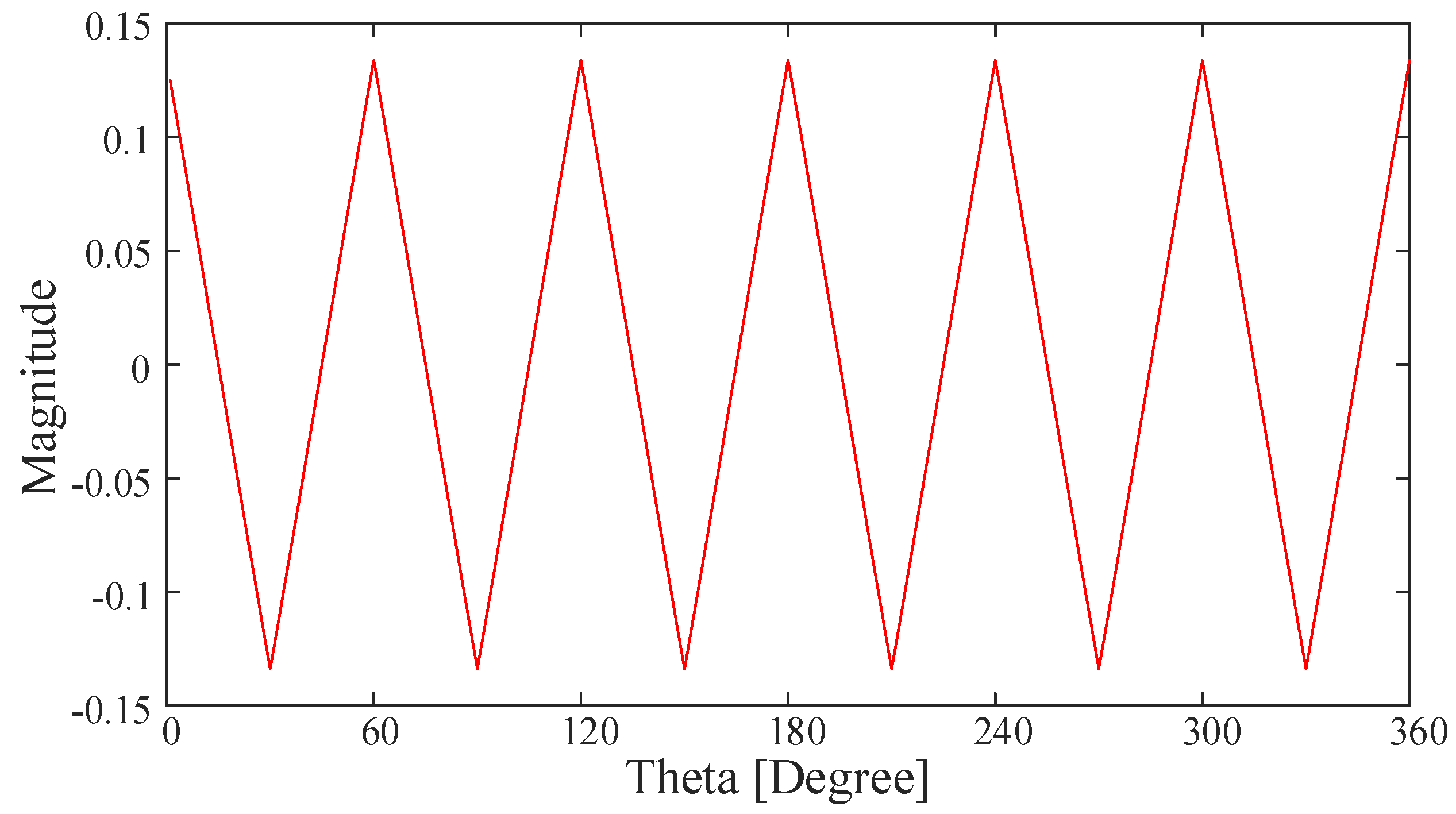

3.1. Analsis of the Dwell Time of Zero Voltage Vector

3.2. The Compensation Time in Zero Voltage Vector for CMV Reduction

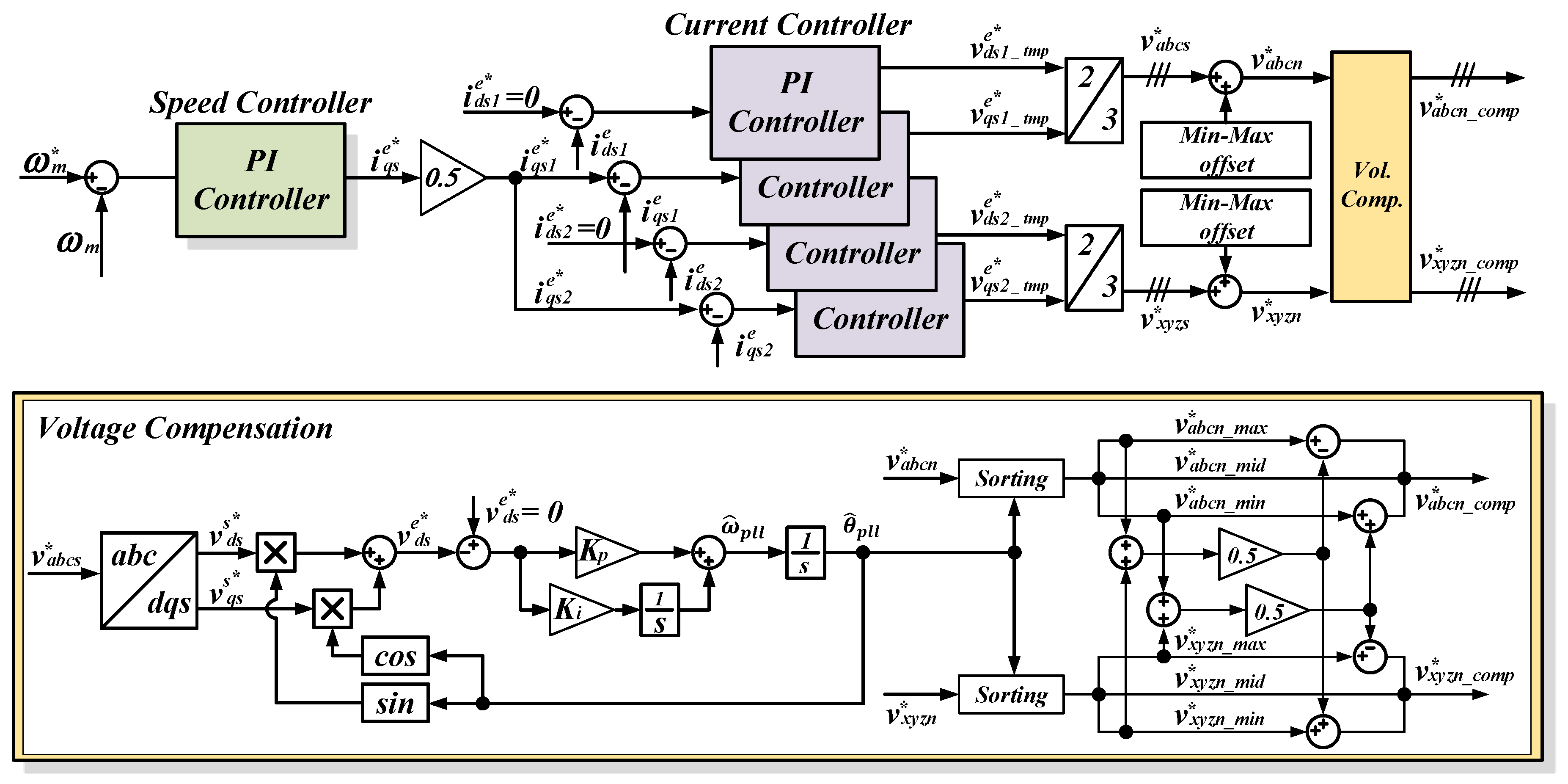

3.3. Overall Configuration of the Proposed Method

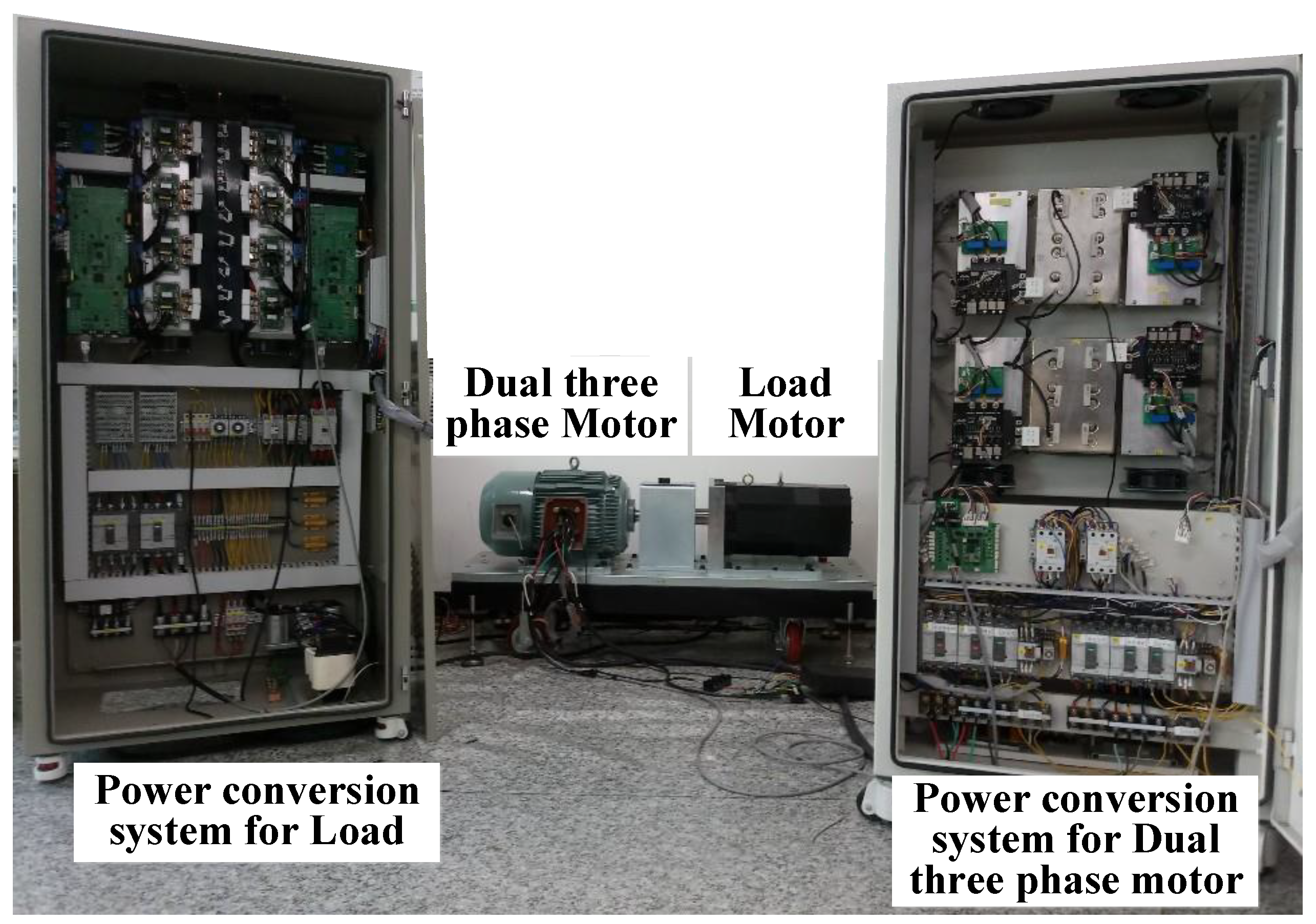

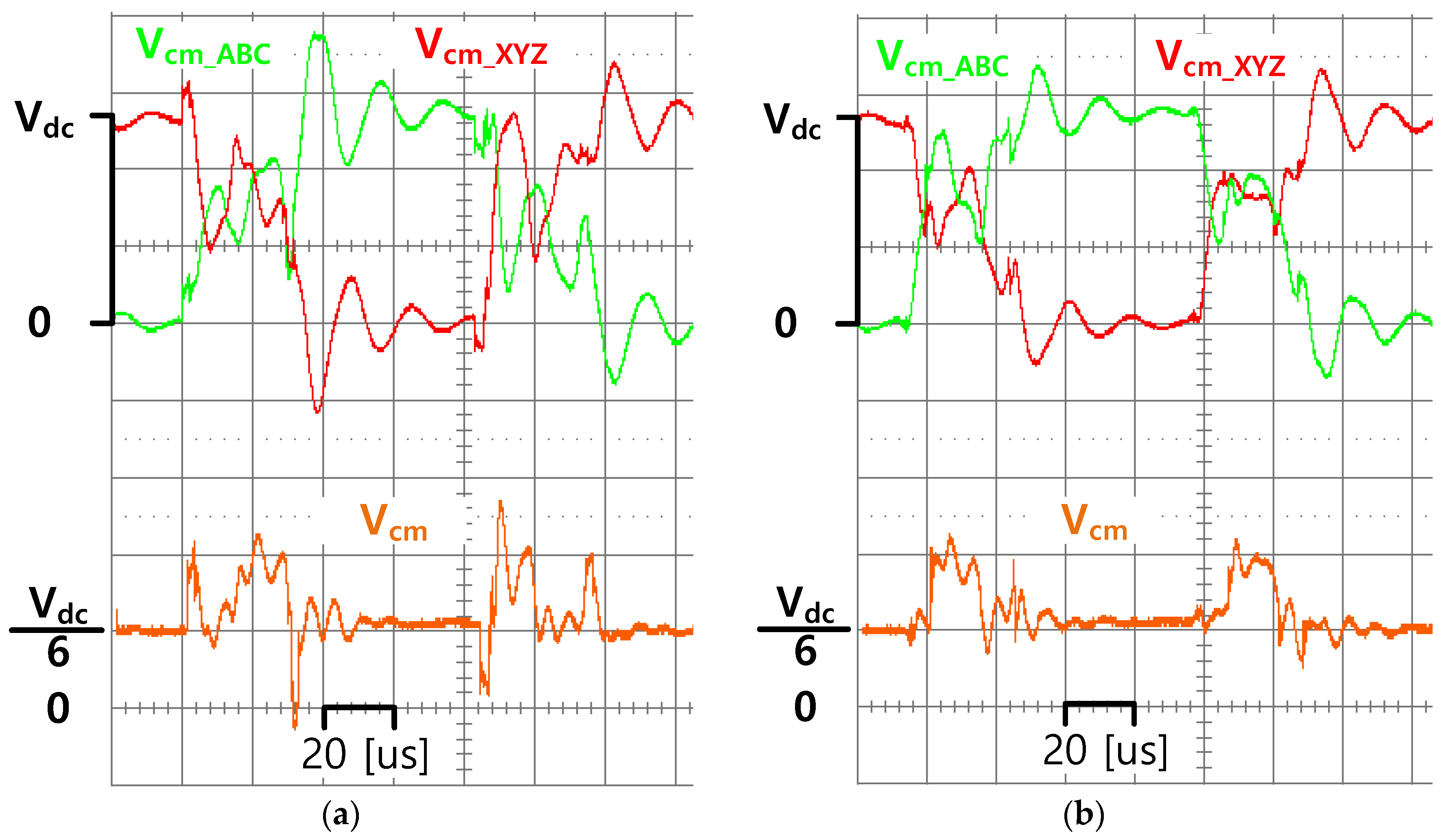

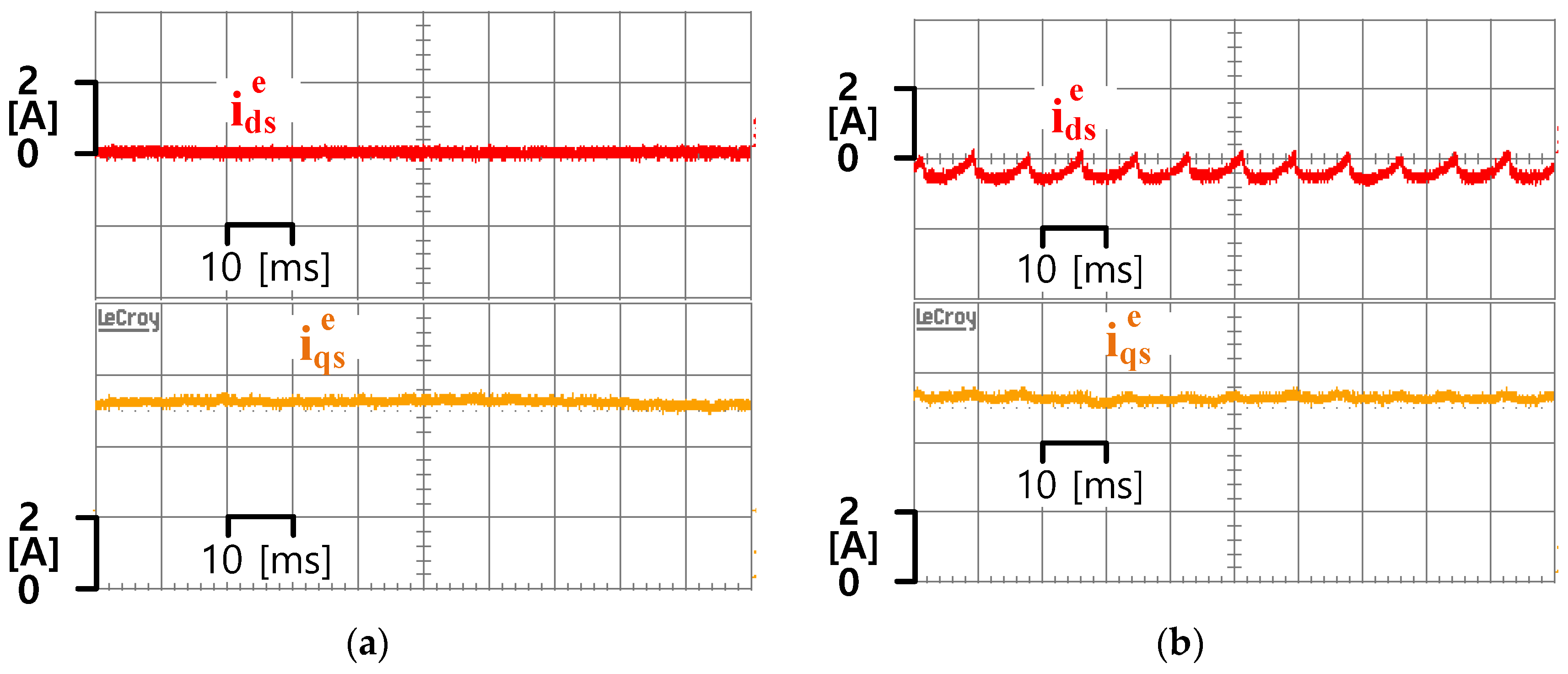

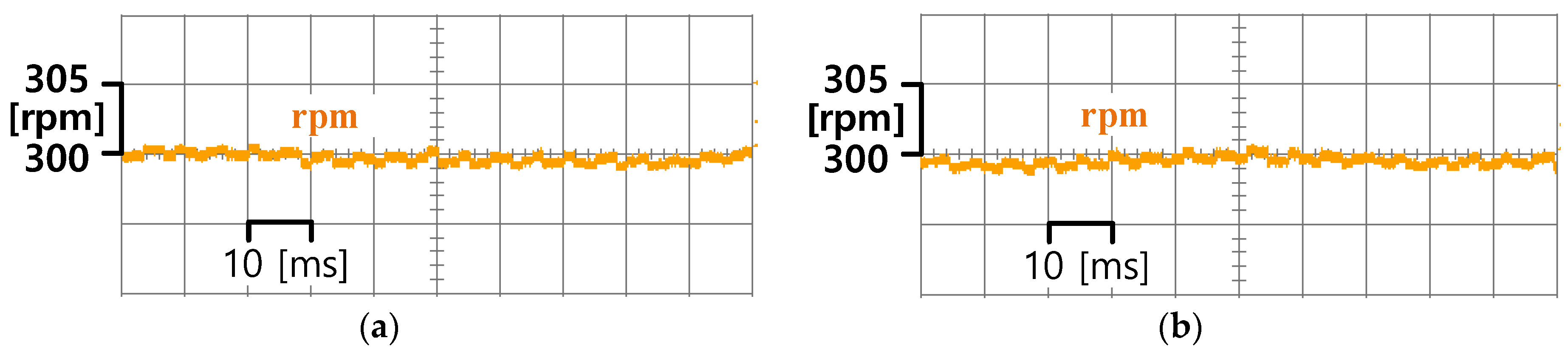

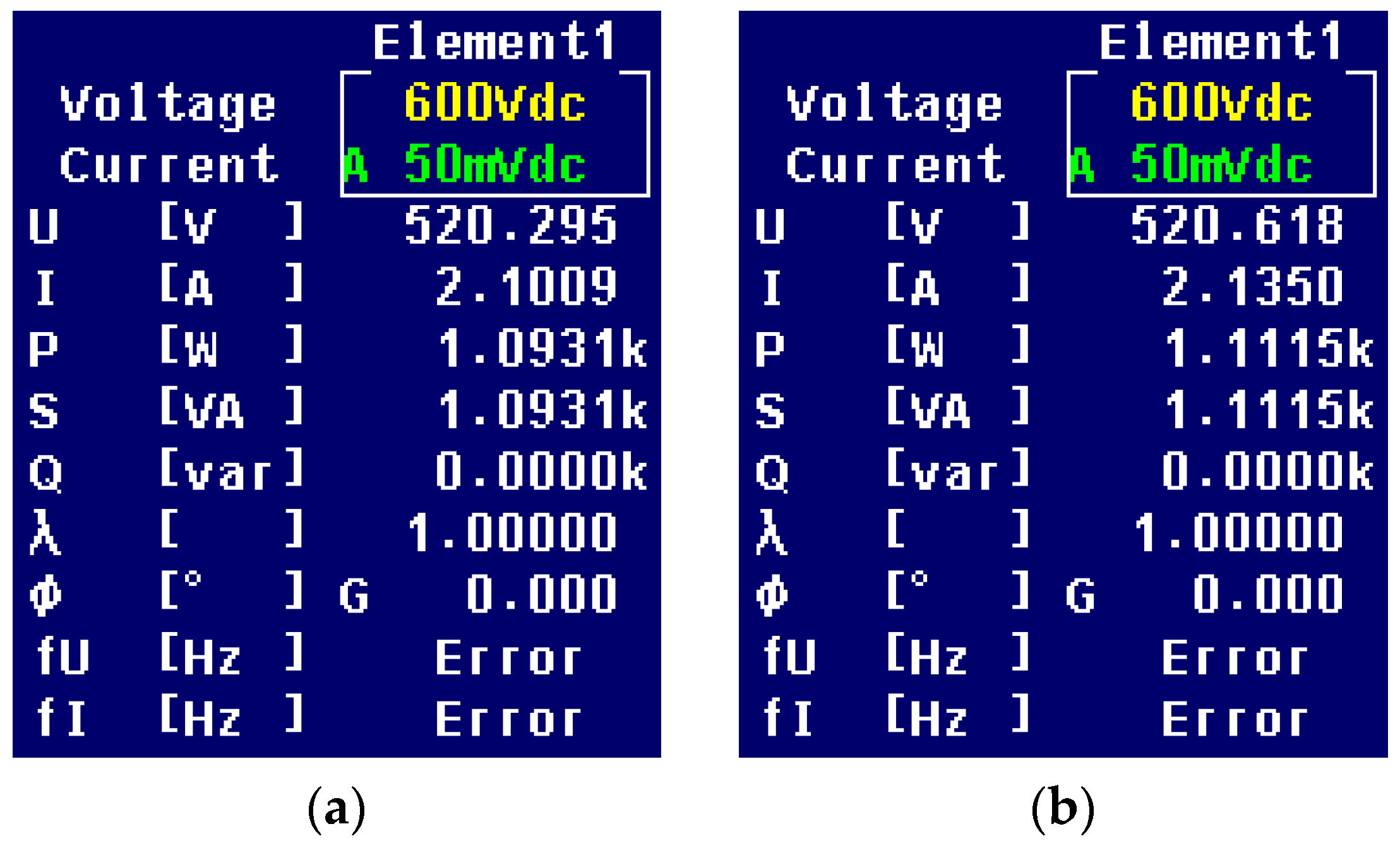

4. Experimental Set-Up and Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Barrero, F.; Duran, M.J. Recent Advances in the Design, Modeling, and Control of Multiphase Machines-Part I. IEEE Trans. Ind. Electron. 2016, 63, 449–458. [Google Scholar] [CrossRef]

- Bojoi, R.; Cavagnino, A.; Tenconi, A.; Tessarolo, A.; Vaschetto, S. Multiphase Electrical Machines and Drives in the Transportation Electrification. In Proceedings of the 2016 International Conference and Exposition on Electrical and Power Engineering (EPE), Lasi, Romania, 20–22 October 2016. [Google Scholar]

- Wang, X.; Wang, Z.; Xu, Z.; He, J.; Zhao, W. Diagnosis and Tolerance of Common Electrical Faults T-Type Three-Level Inverters Fed Dual Three-Phase Drives. IEEE Trans. Power Electron. 2020, 35, 1753–1769. [Google Scholar] [CrossRef]

- Hu, Y.; Zhu, Z.; Liu, K. Current Control for Dual Three-Phase Permanent Magnet Synchronous Motors Accounting for Current Unbalance and Harmonics. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 272–284. [Google Scholar]

- Karttunen, J.; Kallio, S.; Peltoniemi, P.; Silventoinen, P.; Pyrhonen, O. Decoupled Vector Control Scheme for Dual Three-Phase Permanent Magnet Synchronous Machines. IEEE Trans. Ind. Electron. 2014, 61, 2185–2196. [Google Scholar] [CrossRef]

- Zheng, J.; Huang, S.; Rong, F.; Lye, M. Six-Phase Space Vector PWM under Stator One-Phase Open-Circuit Fault Condition. Energies 2018, 11, 1796. [Google Scholar] [CrossRef]

- Liu, Z.; Zheng, Z.; Peng, Z.; Li, Y.; Hao, L. A Sawtooth Carrier-Based PWM for Asymmetrical Six-Phase Inverters with Improved Common-Mode Voltage Performance. IEEE Trans. Power Electon. 2018, 33, 9444–9458. [Google Scholar] [CrossRef]

- Shen, Z.; Jiang, D.; Liu, Z.; Ye, D.; Li, J. Common-Mode Voltage Elimination for Dual Two-Level Inverter-Fed Asymmetrical Six-Phase PMSM. IEEE Trans. Power Electron. 2020, 35, 3828–3840. [Google Scholar] [CrossRef]

- Gopakumar, K.; Ranganthan, V.T.; Bhat, S.R. Split-phase Induction Motor Operation from PWM Voltage Source Inverter. IEEE Trans. Ind. Appl. 1993, 29, 927–932. [Google Scholar] [CrossRef]

- Ahmet, M.H.; Un, E. A High-Performance PWM Algorithm for Common-Mode Voltage Reduction in Three-Phase Voltage Source Inverters. IEEE Trans. Power Electron. 2011, 26, 1998–2008. [Google Scholar]

- Lee, S.; Jung, J.; Hwang, S.; Kim, J.; Cho, H. Common-mode Voltage Reduction Method for H7 Inverter Using DPWM Offset Based Modulation Technique. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018. [Google Scholar]

- Jung, J.; Park, J.; Kim, J.; Son, Y. DC-Link Voltage Balance Control Using Fourth-Phase for 3-Phase 3-Level NPC PWM Converters with Common-Mode Voltage Reduction Technique. J. Power Electron. 2019, 19, 108–118. [Google Scholar]

- Son, Y.; Sul, S. Generalization of Active Filters for EMI Reduction and Harmonics Compensation. IEEE Trans. Ind. Appl. 2006, 42, 545–551. [Google Scholar] [CrossRef]

- Akagi, H.; Hasegawa, H.; Doumoto, T. Design and Performance of a Passive EMI Filter for Use with a Voltage-source PWM Inverter. IEEE Trans. Power Electron. 2004, 19, 1069–1076. [Google Scholar] [CrossRef]

- Cacciato, M.; Consoli, A.; Scarcella, G.; Testa, A. Reduction of Common-Mode Currents in PWM Inverter Motor Drives. IEEE Trans. Ind. Appl. 1999, 35, 545–551. [Google Scholar] [CrossRef]

- Un, E.; Ahmet, M.H. A Near-State PWM Method with Reduced Switching Losses and Reduced Common-Mode Voltage for Three-Phase Voltage Source Inverters. IEEE Trans. Ind. Appl. 2009, 45, 782–793. [Google Scholar] [CrossRef]

- Oriti, G.; Julian, A.L.; Lipo, T.A. A new space vector modulation strategy for common mode voltage reduction. In Proceedings of the PESC97. Record 28th Annual IEEE Power Electronics Specialists Conference. Formerly Power Conditioning Specialists Conference 1970-71, Power Processing and Electronic Specialists Conference 1972, Saint Louis, MO, USA, 27 June 1997. [Google Scholar]

- Huang, J.; Shi, H. Reducing the Common-Mode Voltage through Carrier Peak Position Modulation in an SPWM Three-Phase Inverter. IEEE Trans. Power Electron. 2014, 29, 4490–4495. [Google Scholar] [CrossRef]

- Nguyen, T.T.; Nguyen, N. An Efficient Four-state Zero Common-Mode Voltage PWM Scheme with Reduced Current Distortion for a Three-Level Inverter. IEEE Trans. Ind. Electron. 2018, 65, 1021–1030. [Google Scholar] [CrossRef]

- Le, Q.A.; Lee, D.-C. Elimination of Common-Mode Voltages Based on Modified SVPWM in Five-Level ANPC Inverters. IEEE Trans. Power Electron. 2019, 34, 173–183. [Google Scholar] [CrossRef]

- Seo, I.; Belaynehn, N.B.; Park, C.; Kim, J. A Study of Common Mode Voltage Generation According to Modulation Methods and Reduction Strategies on MMC System. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018. [Google Scholar]

- Xiong, W.; Sun, Y.; Su, M.; Zhang, J.; Liu, Y.; Yang, J. Carrier-Based Modulation Strategies with Reduced Common-Mode Voltage for Five-Phase Voltage Source Inverters. IEEE Trans. Power Electron. 2018, 33, 2381–2394. [Google Scholar] [CrossRef]

- Payami, S.; Behera, R.K.; Iqbal, A.; Al-Ammari, R. Common-Mode Voltage and Vibration Mitigation of a Five-Phase Three-Level NPC Inverter-Fed Induction Motor Drive System. IEEE J. Emerg. Sel. Top. Power Electron. 2015, 3, 349–361. [Google Scholar] [CrossRef]

- Kim, D.; Ma, J.; Kim, J. Phase to Phase Interleaved Method to Reduce the Common Mode Voltage for Seven Phase BLDCM Drive. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019-ECCE Asia), Busan, Korea, 27–30 May 2019. [Google Scholar]

- Liu, Z.; Wang, P.; Sun, W.; Shen, Z.; Jiang, D. Sawtooth Carrier-Based PWM Methods with Common-Mode Voltage Reduction for Symmetrical Multiphase Two-Level Inverters with Odd Phase Number. IEEE Trans. Power Electron. 2021, 36, 1171–1183. [Google Scholar] [CrossRef]

- Zhang, Z.; Jin, S.; Zhang, Z.; Zhang, F.; Li, B. Novel space vector PWM technology with lower common-mode voltage for dual three-phase PMSM. IET Power Electron. 2020, 7, 1426–1433. [Google Scholar] [CrossRef]

- Van der Broeck, H.W.; Skudelny, H.C. Analysis and realization of a pulse width modulator based on voltage space vectors. IEEE Trans. Ind. Appl. 1988, 24, 142–150. [Google Scholar] [CrossRef]

- Feng, G.; Lai, C.; Kelly, M.; Narayan, C.K. Dual Three-Phase PMSM Torque Modeling and Maximum Torque per Peak Current Control Through Optimized Harmonic Current Injection. IEEE Trans. Ind. Electron. 2019, 66, 3356–3368. [Google Scholar] [CrossRef]

| Region | ABC Winding Group | XYZ Winding Group |

|---|---|---|

| 1 | cos(θ − 30°) | cosθ |

| 2 | cos(θ − 60°) | |

| 3 | cos(θ − 90°) | |

| 4 | cos(θ − 120°) | |

| 5 | cos(θ − 150°) | |

| 6 | cos(θ − 180°) | |

| 7 | cos(θ − 210°) | |

| 8 | cos(θ − 240°) | |

| 9 | cos(θ − 270°) | |

| 10 | cos(θ − 300°) | |

| 11 | cos(θ − 330°) | |

| 12 | cosθ |

| Region | T0_err | Region | T0_err |

|---|---|---|---|

| 1 | (1 − /2)cosθ − sinθ/2 | 7 | (−1 + /2)cosθ + sinθ/2 |

| 2 | (1 − /2)(cosθ − sinθ) | 8 | (1/2 + /2)(cosθ − sinθ) |

| 3 | cosθ/2 − (1 − /2)sinθ | 9 | −cosθ/2 + (1 − /2)sinθ |

| 4 | −cosθ/2 − (1 − /2)sinθ | 10 | cosθ/2 + (1 − /2)sinθ |

| 5 | (−1/2 − /2)(cosθ − sinθ) | 11 | (1/2 − /2)(cosθ + sinθ) |

| 6 | (1 + /2)cosθ − sinθ/2 | 12 | (1 − /2)cosθ + sinθ/2 |

| Rated speed | 300 rpm | Stator resistance | 0.434 Ω |

| Switching frequency | 6 kHz | Stator inductance | 0.0141 mH |

| DC link voltage | 540 Vdc | Back-emf constant | 0.393 V/rpm |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hwang, S.-I.; Kim, J.-M. Opposite Triangle Carrier with SVPWM for Common-Mode Voltage Reduction in Dual Three Phase Motor Drives. Energies 2021, 14, 282. https://doi.org/10.3390/en14020282

Hwang S-I, Kim J-M. Opposite Triangle Carrier with SVPWM for Common-Mode Voltage Reduction in Dual Three Phase Motor Drives. Energies. 2021; 14(2):282. https://doi.org/10.3390/en14020282

Chicago/Turabian StyleHwang, Seon-Ik, and Jang-Mok Kim. 2021. "Opposite Triangle Carrier with SVPWM for Common-Mode Voltage Reduction in Dual Three Phase Motor Drives" Energies 14, no. 2: 282. https://doi.org/10.3390/en14020282

APA StyleHwang, S.-I., & Kim, J.-M. (2021). Opposite Triangle Carrier with SVPWM for Common-Mode Voltage Reduction in Dual Three Phase Motor Drives. Energies, 14(2), 282. https://doi.org/10.3390/en14020282