High Power Normally-OFF GaN/AlGaN HEMT with Regrown p Type GaN

Abstract

:1. Introduction

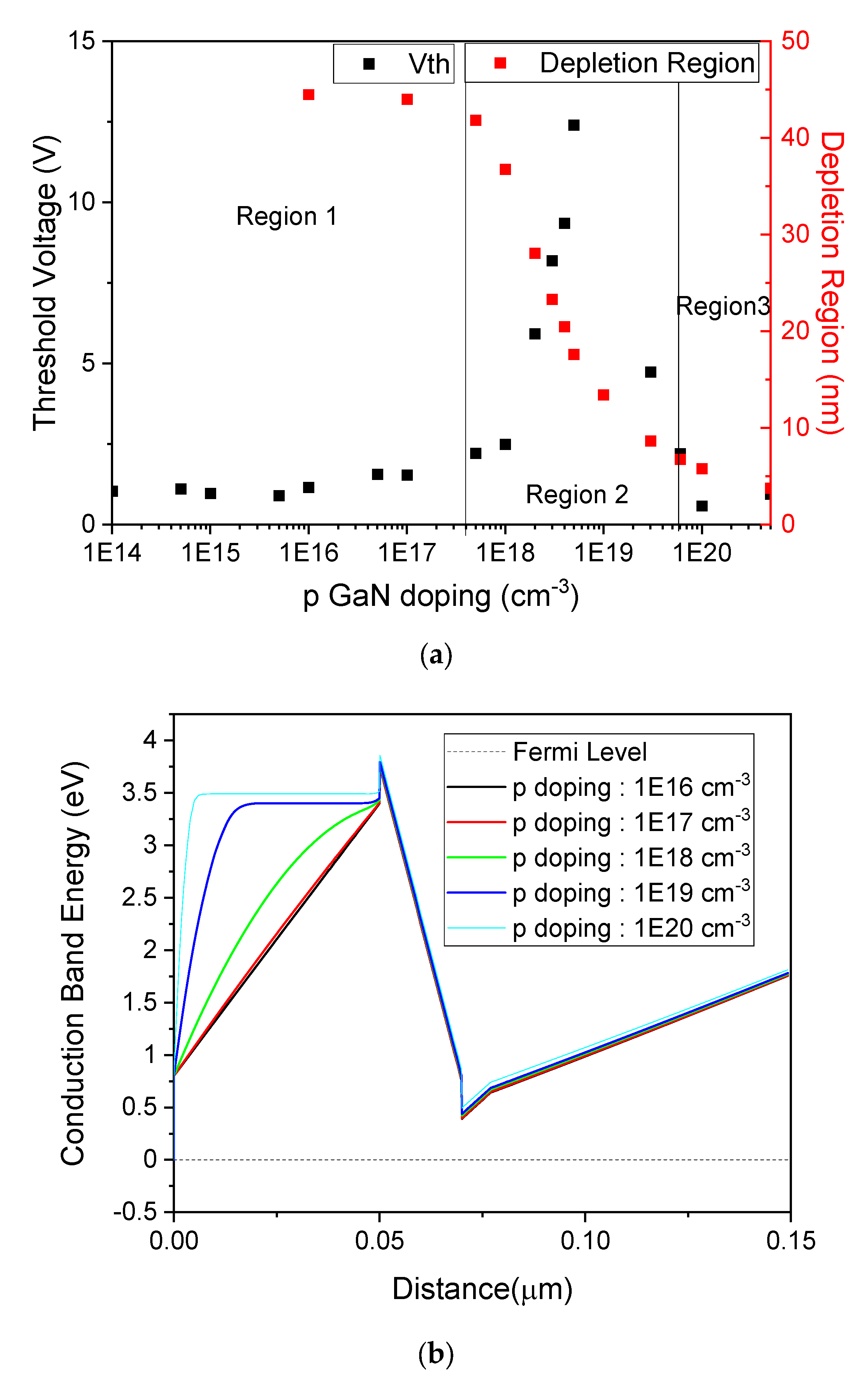

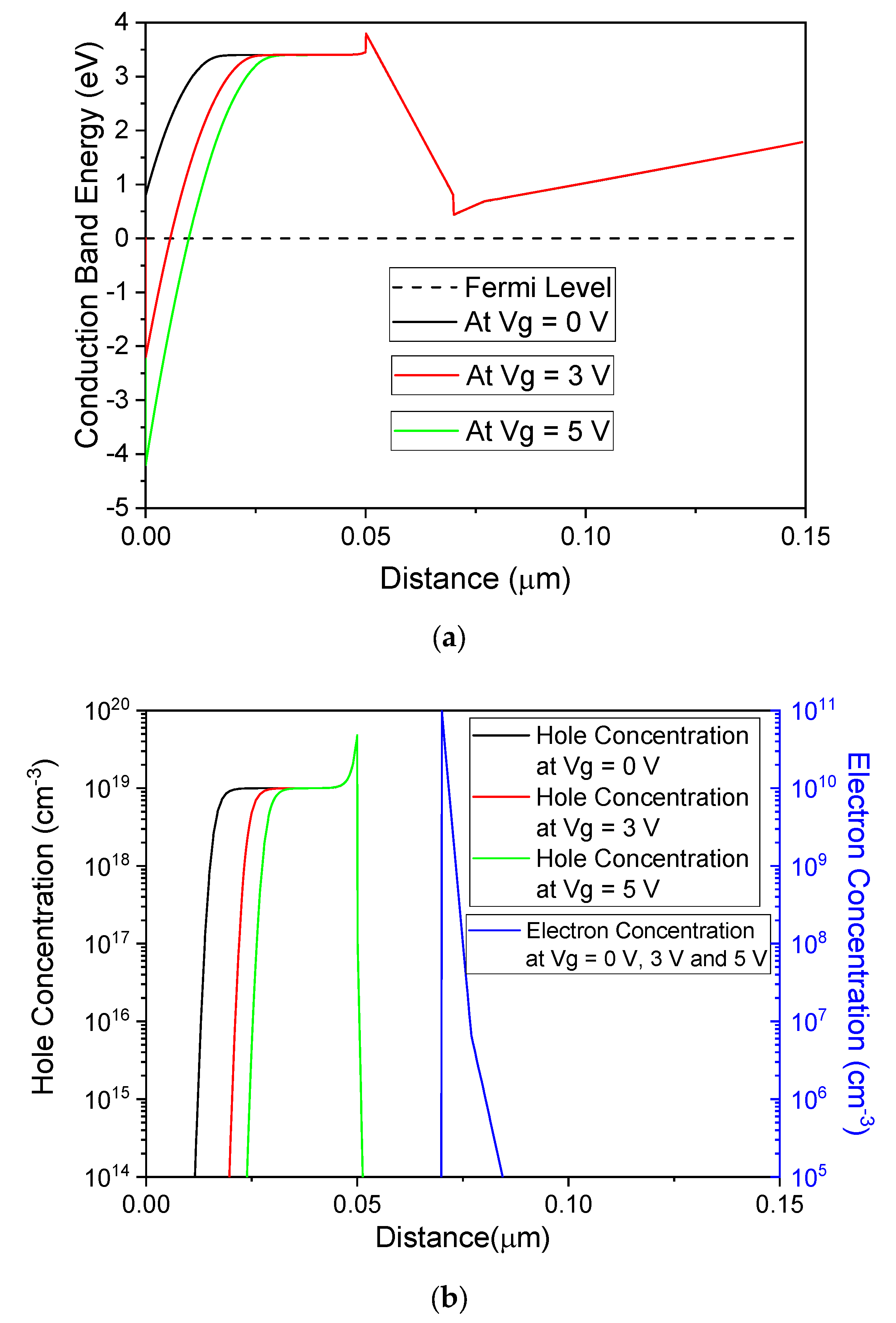

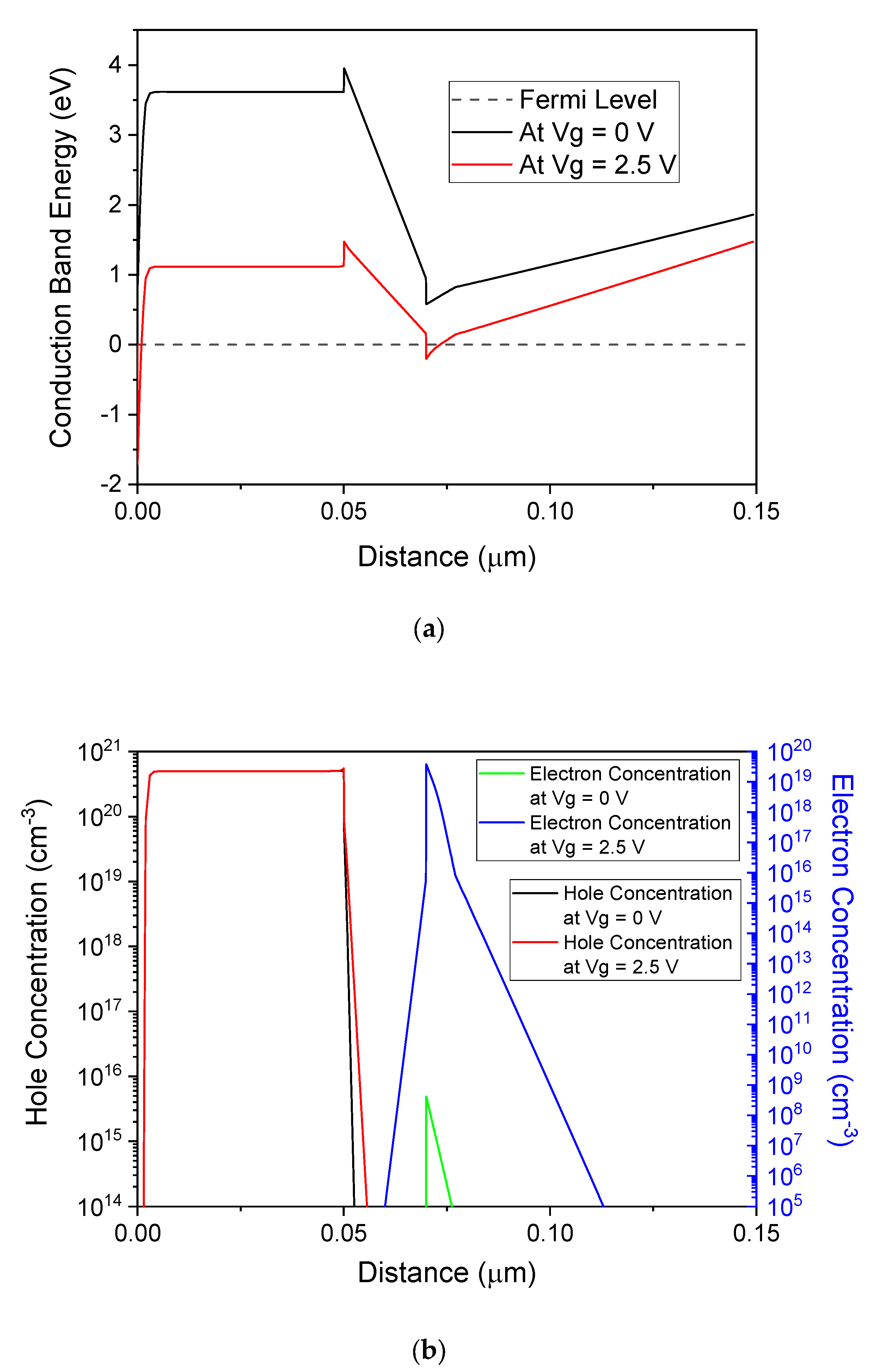

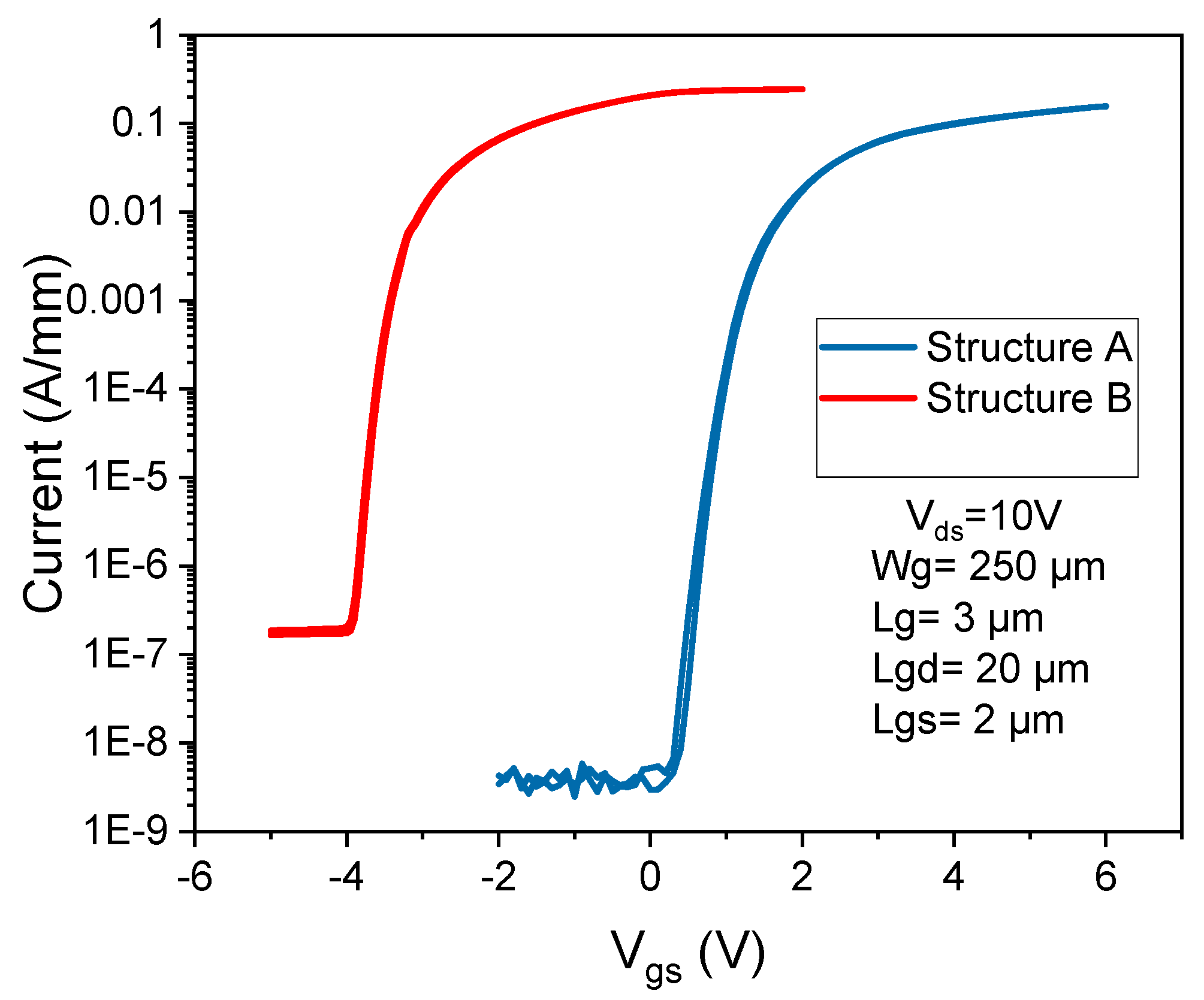

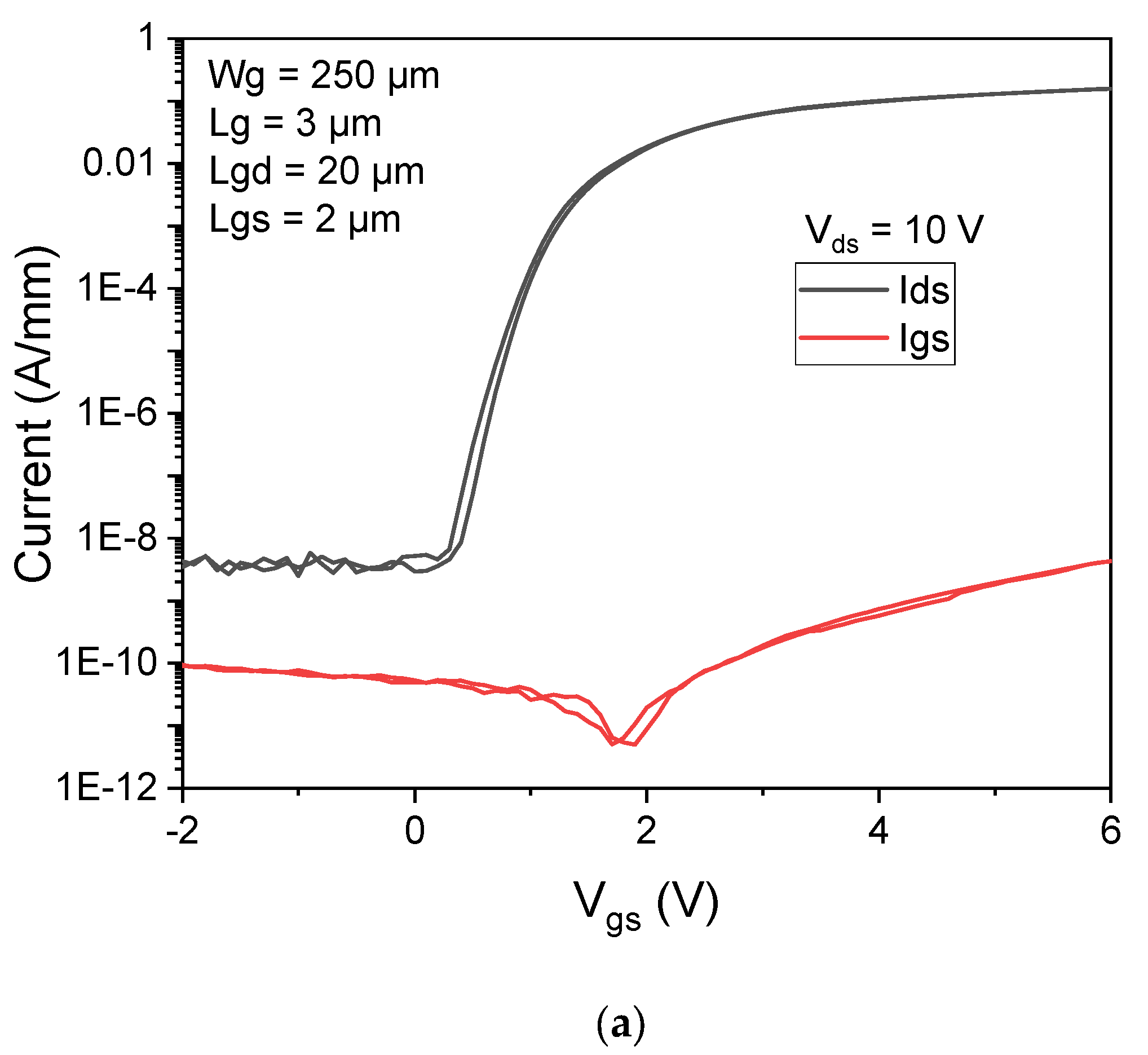

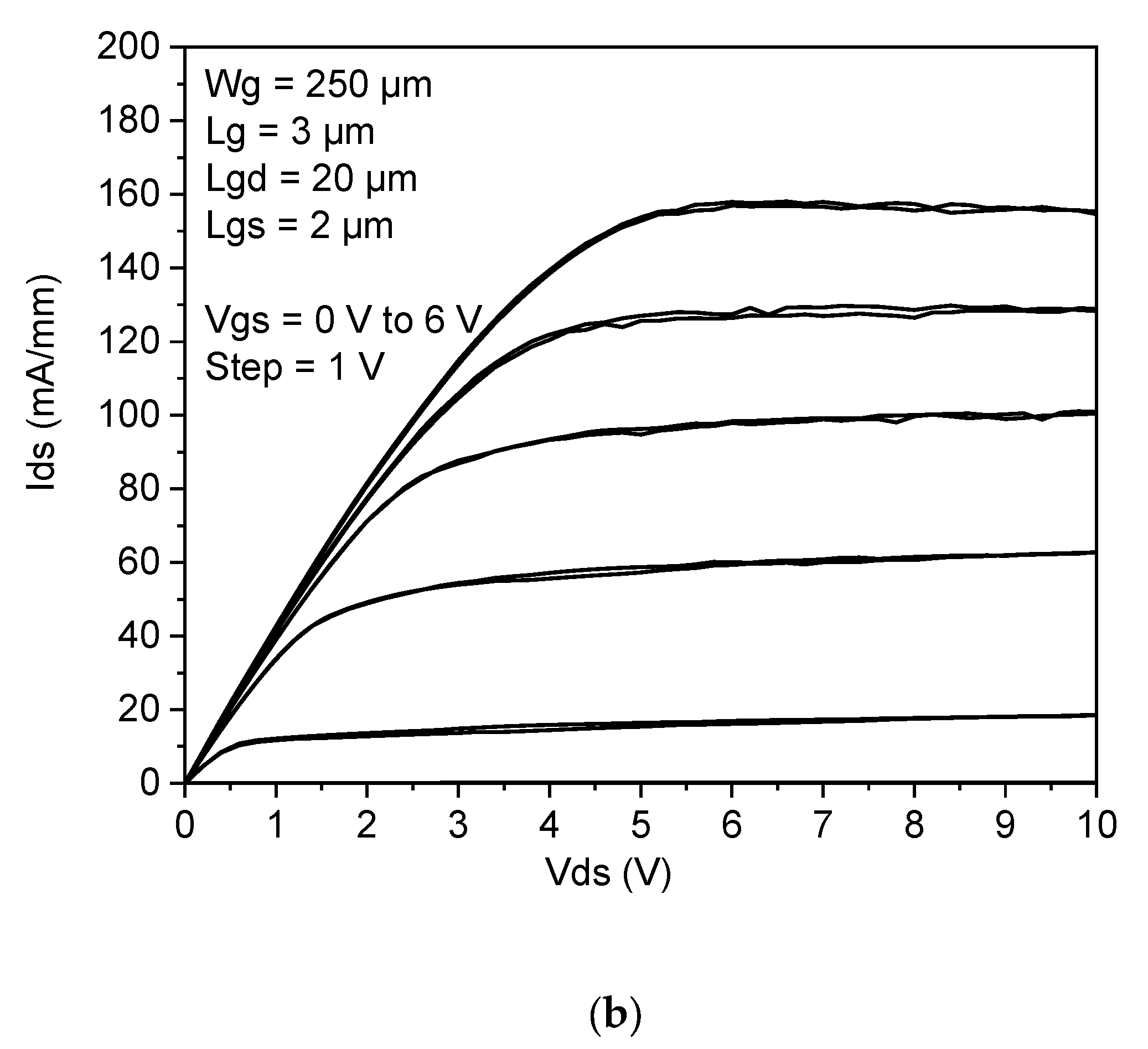

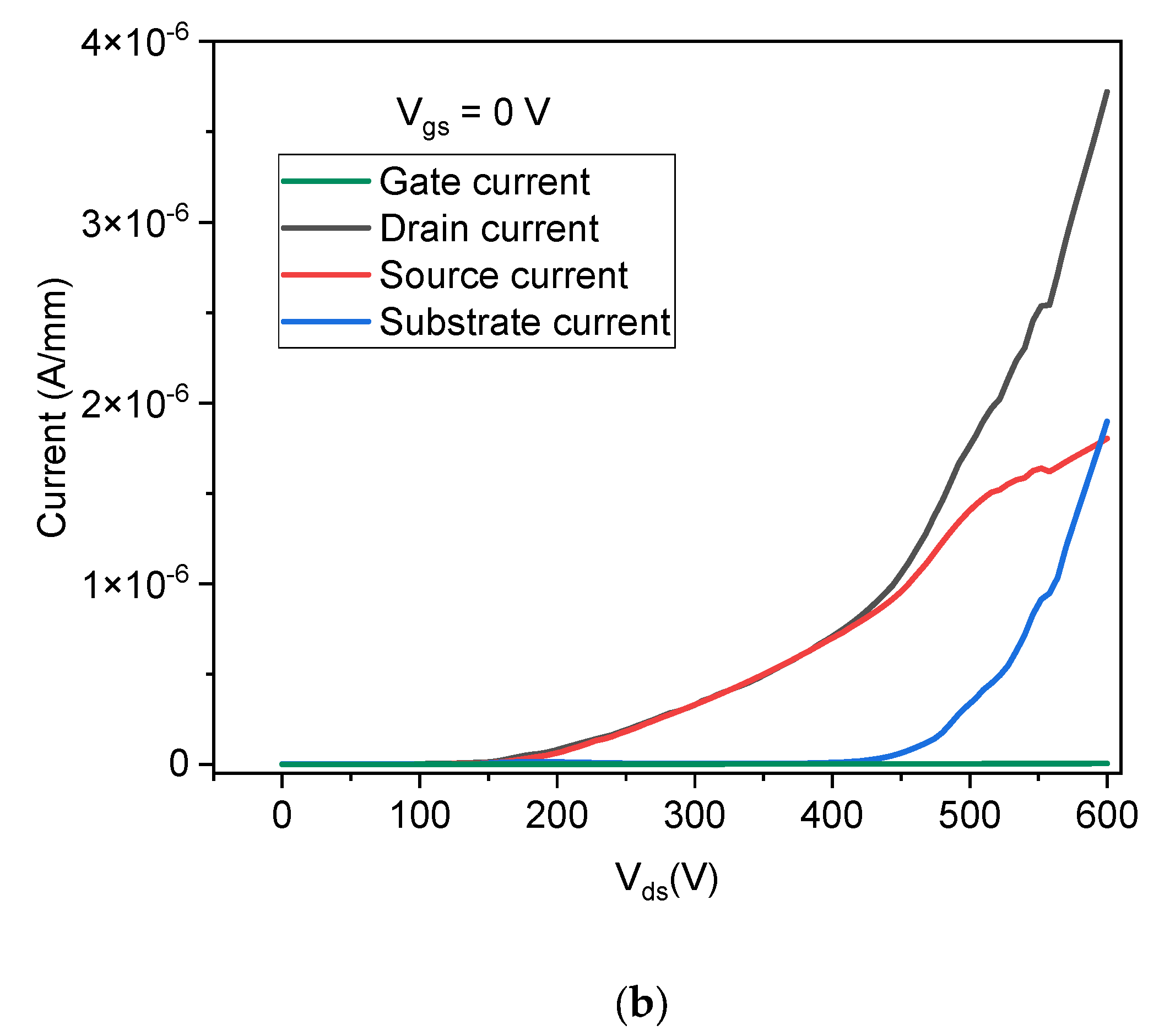

2. Simulation Results

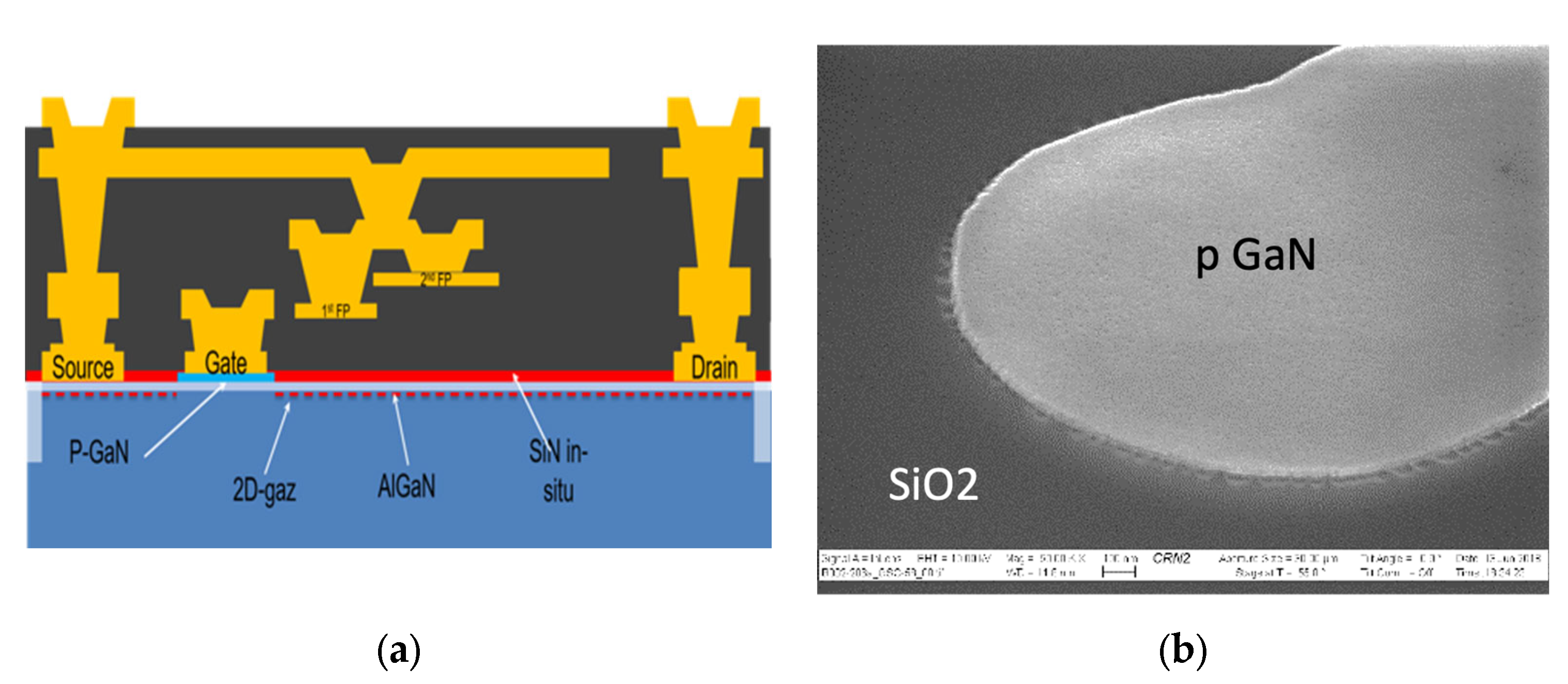

3. Devices Fabrication and Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Wong, J.; Shinohara, K.; Corrion, A.L.; Brown, D.F.; Carlos, Z.; Williams, A.; Tang, Y.; Robinson, J.F.; Khalaf, I.; Fung, H.; et al. Novel Asymmetric Slant Field Plate Technology for High-Speed Low-Dynamic R on E/D-mode GaN HEMTs. IEEE Electron Device Lett. 2017, 38, 95–98. [Google Scholar] [CrossRef]

- Shur, M.S. Physics of electron transport in nitride-based material. In Proceedings of the 2002 Conference on Optoelectronic and Microelectronic Materials and Devices, COMMAD 2002, Proceedings (Cat. No.02EX601), Sydney, Australia, 11–13 December 2002; pp. 7–12. [Google Scholar]

- Yang, L.; Hou, B.; Mi, M.; Zhang, P.; Zhu, J.; Zhu, Q.; Cao, Y.; Lv, L.; Zhou, X.; Ma, X.; et al. Normally-Off Fluoride-Based Plasma Treatment AlGaN/GaN HEMTs with Maximum fT and fmax of 61GHz/130GHz Using TiN-Based Source Ledge. In Proceedings of the 2018 15th China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China (SSLChina: IFWS), Shenzhen, China, 23–25 October 2018; pp. 1–4. [Google Scholar]

- Chakroun, A.; Jaouad, A.; Bouchilaoun, M.; Arenas, O.; Soltani, A.; Maher, H. Normally-off AlGaN/GaN MOS-HEMT using ultra-thin Al0.45Ga0.55N barrier layer. Phys. Status Solidi A 2017, 214, 1600836. [Google Scholar] [CrossRef]

- Lu, B.; Sun, M.; Palacios, T. An Etch-Stop Barrier Structure for GaN High-Electron-Mobility Transistors. IEEE Electron Device Lett. 2013, 34, 369–371. [Google Scholar] [CrossRef]

- Meneghini, M.; Hilt, O.; Wuerfl, J.; Meneghesso, G. Technology and Reliability of Normally-Off GaN HEMTs with p-Type Gate. Energies 2017, 10, 153. [Google Scholar] [CrossRef] [Green Version]

- Chiu, H.-C.; Chang, Y.-S.; Li, B.-H.; Wang, H.-C.; Kao, H.-L.; Hu, C.-W.; Xuan, R. High-Performance Normally Off p-GaN Gate HEMT With Composite AlN/Al0.17Ga0.83N/Al0.3Ga0.7N Barrier Layers Design. IEEE J. Electron Devices Soc. 2018, 6, 201–206. [Google Scholar] [CrossRef]

- Roccaforte, F.; Greco, G.; Fiorenza, P.; Iucolano, F. An Overview of Normally-Off GaN-Based High Electron Mobility Transistors. Materials 2019, 12, 1599. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Efthymiou, L.; Longobardi, G.; Camuso, G.; Chien, T.; Chen, M.; Udrea, F. On the physical operation and optimization of the p-GaN gate in normally-off GaN HEMT devices. Appl. Phys. Lett. 2017, 110, 123502. [Google Scholar] [CrossRef]

- Li, Z.; Li, J.; Jiang, H.; Han, Y.; Xia, Y.; Huang, Y.; Yin, J.; Hu, S. High Conductivity of Mg-Doped Al0.3Ga0.7N with Al0.4Ga0.6N/AlN Superlattice Structure. Adv. Condens. Matter Phys. 2014, 2014, 784918. [Google Scholar] [CrossRef] [Green Version]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rolland, G.; Rodriguez, C.; Gommé, G.; Boucherif, A.; Chakroun, A.; Bouchilaoun, M.; Pepin, M.C.; El Hamidi, F.; Maher, S.; Arès, R.; et al. High Power Normally-OFF GaN/AlGaN HEMT with Regrown p Type GaN. Energies 2021, 14, 6098. https://doi.org/10.3390/en14196098

Rolland G, Rodriguez C, Gommé G, Boucherif A, Chakroun A, Bouchilaoun M, Pepin MC, El Hamidi F, Maher S, Arès R, et al. High Power Normally-OFF GaN/AlGaN HEMT with Regrown p Type GaN. Energies. 2021; 14(19):6098. https://doi.org/10.3390/en14196098

Chicago/Turabian StyleRolland, Gwen, Christophe Rodriguez, Guillaume Gommé, Abderrahim Boucherif, Ahmed Chakroun, Meriem Bouchilaoun, Marie Clara Pepin, Faissal El Hamidi, Soundos Maher, Richard Arès, and et al. 2021. "High Power Normally-OFF GaN/AlGaN HEMT with Regrown p Type GaN" Energies 14, no. 19: 6098. https://doi.org/10.3390/en14196098

APA StyleRolland, G., Rodriguez, C., Gommé, G., Boucherif, A., Chakroun, A., Bouchilaoun, M., Pepin, M. C., El Hamidi, F., Maher, S., Arès, R., MacElwee, T., & Maher, H. (2021). High Power Normally-OFF GaN/AlGaN HEMT with Regrown p Type GaN. Energies, 14(19), 6098. https://doi.org/10.3390/en14196098