Modular Multilevel Converter for Low-Voltage Ride-Through Support in AC Networks

Abstract

:1. Introduction

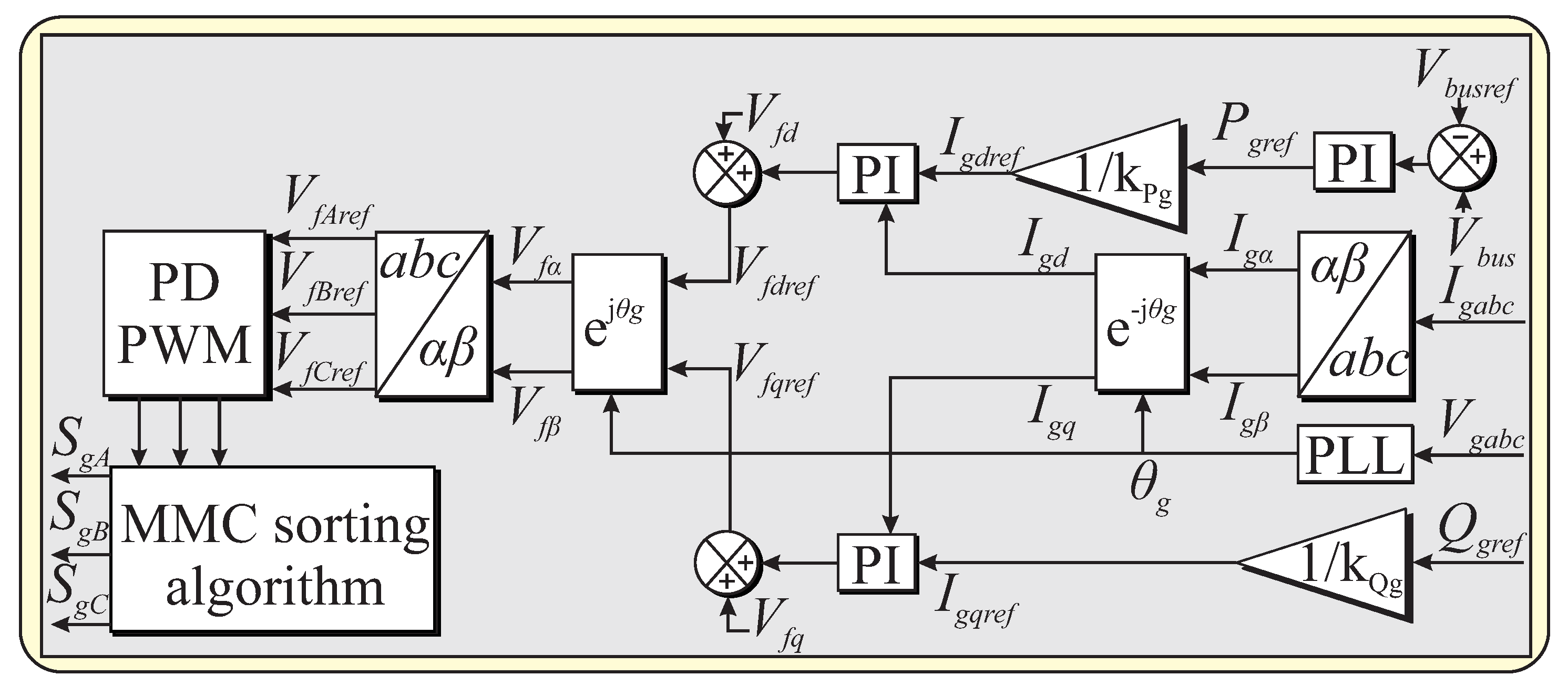

2. Description of Converter Topologies

- If = 1 and = 0, = ;

- If = 0 and = 1, = 0;

- Else = 0.

3. The Proposed Application

4. Performance Assessment

4.1. 2L-VSC in the LVRT Scenario

- SLG fault: The control maintained within the reference values during the fault period. However, when the PCC voltage returned to the prefault values, an overvoltage occurred: reached approximately 637 V, which was an increase of 6.16% compared to the steady-state value, while the DC current () reached approximately 15 A, representing about four-times the steady-state current;

- DLG fault: reached a maximum of approximately 641 V, representing an increase of 6.83%, while presented a similar behavior to the LG fault scenario;

- LL fault: reached a maximum of approximately 635 V, which was an increase of 5.83% compared to the steady-state value, while reached approximately 9.5 A, representing about 2.53-times the steady-state current;

- LLL fault: For the worst-case scenario, reached a maximum of 720 V, representing an overvoltage level of 20%, while reached 30 A, being more than nine-times the steady-state. The obtained results demonstrated that the 2L-VSC has a lower LVRT support, resulting in a higher possibility of damaging several system components during a severe grid fault.

- SLG fault: Around the fault’s initiation, the control maintained at the reference value. When reestablished its prefault voltage, an overvoltage 5% lower than without the DC chopper occurred. Conversely, reached a maximum value of approximately 12 A with a reduction of 20% compared to the 2L-VSC without the chopper;

- DLG fault: reached a maximum value of 635 V, while reached a peak of 10.2 A, representing a reduction of 9.36% and 7.27% compared to the case without the DC chopper, respectively;

- LL fault: reached a maximum value of 637 V, while reached a peak of 10.5 A, representing a increase of 0.31%, while increased 10.52% compared to the previous case;

- LLL fault: reached a maximum of 700 V, while reached a maximum of 30.5 A. There was a reduction of compared to the previous case of 2.83%. Conversely, obtained an increase of 3.33%.

4.2. 3L-NPC in the LVRT Scenario

- SLG fault: Similar to the previous cases, the control maintained within the reference value, reaching a maximum of 633 V when started to recover to the prefault condition, while reached a peak of 11 A. The 3L-NPC obtained a performance similar to the 2L-VSC without the DC chopper;

- DLG fault: The 3L-NPC achieved similar performance to 2L-VSC with the chopper, with reaching a maximum value of 632 V, while reached a peak of 11 A;

- LL fault: reached a maximum value of 615 V, while reached a peak of 9 A;

- LLL fault: The 3L-NPC obtained superior performance compared to 2L-VSC with and without the chopper, with reaching a maximum of approximately 675 V and reaching a peak of 28.7 A, representing a reduction of 6.25% and 3.33% compared to the 2L-VSC without the chopper, respectively, as well as 3.57% and 1.03% compared to the 2L-VSC with the chopper, respectively.

4.3. 3L-MMC in LVRT Scenario

- SLG fault: The control maintained within the reference value at the fault occurrence. When recovered to the prefault voltage levels, reached a maximum value of 615 V, while reached a peak of 5 A. Compared to the steady-state value, and increased 2.5% and approximately 1.5-times, respectively. However, the 3L-MMC presented the best performance, reducing by approximately 42.85% the overvoltage level and 50% the overcurrent level compared to the 2L-VSC with and without the DC chopper and the 3L-NPC;

- DLG fault: reached a maximum of 617 V, while reached a maximum of 8 A, representing an increase of 2.83- and 2.28-times the steady-state value, respectively;

- LL fault: reached a maximum of 612 V, while reached a maximum of 5.2 A, representing a decrease of 0.48%, while decreased 41.11% compared to the 3L-NPC topology;

- LLL fault: The 3L-MMC obtained for a maximum of 625 V and for a peak of 10 A, representing an increase of 4.16% and 2.85-times the steady-state value, respectively. However, the 3L-MMC provided a reduction of the overvoltage and overcurrent level of 4.8-times and 3-times, respectively, compared to the 2L-VSC without the chopper. Regarding the 2L-VSC with the chopper, there was a reduction of four- and three-times and , respectively, besides three-times for 3L-NPC in both cases.

4.4. Comparison of the 2L-VSC, 3L-NPC, and 3L-MMC under LVRT Scenarios

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Bollen, M.H.; Hassan, F. Integration of Distributed Generation in the Power System; John Wiley & Sons: Hoboken, NJ, USA, 2011; Volume 80. [Google Scholar]

- Infield, D.; Freris, L. Renewable Energy in Power Systems; John Wiley & Sons: Hoboken, NJ, USA, 2020. [Google Scholar]

- Abad, G. Power Electronics and Electric Drives for Traction Applications; John Wiley & Sons: Hoboken, NJ, USA, 2016. [Google Scholar]

- Abu-Rub, H.; Malinowski, M.; Al-Haddad, K. Power Electronics for Renewable Energy Systems, Transportation and Industrial Applications; John Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Tabatabaei, N.M.; Kabalci, E.; Bizon, N. Microgrid Architectures, Control and Protection Methods; Springer: Berlin/Heidelberg, Germany, 2019. [Google Scholar]

- Zhong, Q.C.; Hornik, T. Control of Power Inverters in Renewable Energy and Smart Grid Integration; John Wiley & Sons: Hoboken, NJ, USA, 2012; Volume 97. [Google Scholar]

- Sharkh, S.M.; Abu-Sara, M.A.; Orfanoudakis, G.I.; Hussain, B. Power Electronic Converters for Microgrids; John Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, 17, 518–523. [Google Scholar] [CrossRef]

- Meynard, T.; Foch, H. Multi-level choppers for high voltage applications. EPE J. 1992, 2, 45–50. [Google Scholar] [CrossRef]

- Mcmurray, W. Fast Response Stepped-Wave Switching Power Converter Circuit, 1971. U.S. Patent 3,581,212, 25 May 1971. [Google Scholar]

- Du, S.; Dekka, A.; Wu, B.; Zargari, N. Modular Multilevel Converters: Analysis, Control, and Applications; John Wiley & Sons: Hoboken, NJ, USA, 2017. [Google Scholar]

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the 2003 IEEE Bologna Power Tech Conference Proceedings, Bologna, Italy, 23–26 June 2003; Volume 3. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Robles, E.; Gabiola, I.; Zaragoza, J.; Villate, J.L.; Boroyevich, D. Three-Level Converter Topologies with Switch Breakdown Fault-Tolerance Capability. IEEE Trans. Ind. Electron. 2008, 55, 982–995. [Google Scholar] [CrossRef]

- Ghazanfari, A.; Mohamed, Y.A.I. A Resilient Framework for Fault-Tolerant Operation of Modular Multilevel Converters. IEEE Trans. Ind. Electron. 2016, 63, 2669–2678. [Google Scholar] [CrossRef]

- Zhao, X.; Guerrero, J.M.; Savaghebi, M.; Vasquez, J.C.; Wu, X.; Sun, K. Low-Voltage Ride-Through Operation of Power Converters in Grid-Interactive Microgrids by Using Negative-Sequence Droop Control. IEEE Trans. Power Electron. 2017, 32, 3128–3142. [Google Scholar] [CrossRef] [Green Version]

- Lee, C.; Hsu, C.; Cheng, P. A Low-Voltage Ride-Through Technique for Grid-Connected Converters of Distributed Energy Resources. IEEE Trans. Ind. Appl. 2011, 47, 1821–1832. [Google Scholar] [CrossRef]

- Alepuz, S.; Calle, A.; Busquets-Monge, S.; Kouro, S.; Wu, B. Use of Stored Energy in PMSG Rotor Inertia for Low-Voltage Ride-Through in Back-to-Back NPC Converter-Based Wind Power Systems. IEEE Trans. Ind. Electron. 2013, 60, 1787–1796. [Google Scholar] [CrossRef]

- Ding, G.; Gao, F.; Tian, H.; Ma, C.; Chen, M.; He, G.; Liu, Y. Adaptive DC-Link Voltage Control of Two-Stage Photovoltaic Inverter During Low Voltage Ride-Through Operation. IEEE Trans. Power Electron. 2016, 31, 4182–4194. [Google Scholar] [CrossRef]

- Yazdani, A.; Iravani, R. Voltage-Sourced Converters in Power Systems: Modeling, Control, and Applications; John Wiley & Sons: Hoboken, NJ, USA, 2010. [Google Scholar]

- Vijeh, M.; Rezanejad, M.; Samadaei, E.; Bertilsson, K. A General Review of Multilevel Inverters Based on Main Submodules: Structural Point of View. IEEE Trans. Power Electron. 2019, 34, 9479–9502. [Google Scholar] [CrossRef]

- Holmes, D.; Lipo, T.; Lipo, T. Pulse Width Modulation for Power Converters: Principles and Practice; IEEE Press Series on Power Engineering; IEEE Press: Piscataway Township, NJ, USA, 2003. [Google Scholar]

- Peddapelli, S. Pulse Width Modulation: Analysis and Performance in Multilevel Inverters; De Gruyter: Berlin, Germany, 2016. [Google Scholar]

- Jamshidifar, A.; Jovcic, D. Small-Signal Dynamic DQ Model of Modular Multilevel Converter for System Studies. IEEE Trans. Power Deliv. 2016, 31, 191–199. [Google Scholar] [CrossRef] [Green Version]

- Zygmanowski, M.; Grzesik, B.; Nalepa, R. Capacitance and inductance selection of the modular multilevel converter. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–10. [Google Scholar] [CrossRef]

- Kang, J.; Kang, D.W.; Lee, J.P.; Yoo, D.W.; Shim, J.W. Design Procedure of MMC-HVDC System: Comprehensive Consideration of Internal and External Dynamics. IEEE Access 2020, 8, 157437–157450. [Google Scholar] [CrossRef]

| Reference | Technique | Advantages | Drawbacks |

|---|---|---|---|

| [13] | Fourth leg addition to 3L-NPC-based flying capacitor. | Fixed neutral voltage under normal operation and phase replacement under LVRT. | Hardware addition; complex PWM and control loops. |

| [14] | Multilevel modular capacitor-clamped DC/DC converter (MMCCC); supervisory algorithm. | Postfault restoration scheme. | Hardware addition; complex control algorithm implementation; high implementation costs. |

| [15,16] | Positive/negative sequence droop control/ current injection. | Grid voltage support. | Complex two-layer hierarchical control implementation; control loop modification. |

| [17] | Surplus active power energy storage; DC chopper. | Avoids DC bus overvoltages under LVRT. | Hardware addition; control coordination requirement. |

| [18] | Adaptive DC bus voltage control. | High-frequency harmonics reduction; avoids DC bus overvoltages under LVRT. | Reference control loop modification; strongly dependent on the system parameters. |

| Proposed Application | Advantages | Contributions |

|---|---|---|

| MMC for LVRT support. | No additional hardware; no complex control loops; avoids DC bus overvoltages under LVRT; avoids overcurrents under LVRT; easily expandable modular structure. | ✓ MMC arm impedance for overcurrent and overvoltage suppression under LVRT; ✓ avoids the protection activation; ✓ supports the grid connection under LVRT; ✓ maintains the controllability of the power converter. |

| Criterion | VSC | NPC | MMC |

|---|---|---|---|

| Clamping diodes | 0 | ()() | 0 |

| Number of switches | 6 | 6() | 12() |

| Capacitors | DC bus | () | 6()+1 |

| Switch blocking voltage | |||

| Modularity | No | No | Yes |

| Voltage balancing | No | DC bus | Per submodule |

| Redundancy | No | No | Yes |

| Parameter | Value |

|---|---|

| Grid voltage | 380 V |

| Grid frequency | 60 Hz |

| DC bus voltage | 600 V |

| DC capacitor | 2000 uF |

| Switching frequency | 5 kHz |

| MMC arm resistance () | 0.5 |

| MMC arm inductance () | 5 mH |

| MMC submodule capacitance () | 1000 uF |

| Grid line resistance () | 0.487 |

| Grid line inductance () | 4.2 mH |

| Capacitor bank filter () | 380 uF |

| Converter filter resistance () | 0.4 |

| Converter filter inductance () | 15 mH |

| Fault resistance () | 1 m |

| Fault inductance () | 0.1 mH |

| Peak (V) | Peak (A) | |||||||

|---|---|---|---|---|---|---|---|---|

| Topology | SLG | DLG | LL | LLL | SLG | DLG | LL | LLL |

| 2L-VSC | 637 | 641 | 635 | 720 | 15 | 15.1 | 9.5 | 30 |

| 2L-VSC+DC chopper | 615 | 635 | 637 | 700 | 12 | 10.2 | 10.5 | 30.5 |

| 3L-NPC | 633 | 632 | 615 | 675 | 11 | 11 | 9 | 28.7 |

| 3L-MMC | 615 | 617 | 612 | 625 | 5 | 8 | 5.2 | 10 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

de Souza, V.R.F.B.; Barros, L.S.; Costa, F.B. Modular Multilevel Converter for Low-Voltage Ride-Through Support in AC Networks. Energies 2021, 14, 5314. https://doi.org/10.3390/en14175314

de Souza VRFB, Barros LS, Costa FB. Modular Multilevel Converter for Low-Voltage Ride-Through Support in AC Networks. Energies. 2021; 14(17):5314. https://doi.org/10.3390/en14175314

Chicago/Turabian Stylede Souza, Victor Ramon França Bezerra, Luciano Sales Barros, and Flavio Bezerra Costa. 2021. "Modular Multilevel Converter for Low-Voltage Ride-Through Support in AC Networks" Energies 14, no. 17: 5314. https://doi.org/10.3390/en14175314

APA Stylede Souza, V. R. F. B., Barros, L. S., & Costa, F. B. (2021). Modular Multilevel Converter for Low-Voltage Ride-Through Support in AC Networks. Energies, 14(17), 5314. https://doi.org/10.3390/en14175314