1. Introduction

Pulse-width modulated (PWM) active rectification is a fundamental requirement for the supply of modern high-power electrical systems, as it ensures lower distortion, higher performance and wider regulation capability with respect to passive and/or hybrid rectification solutions [

1,

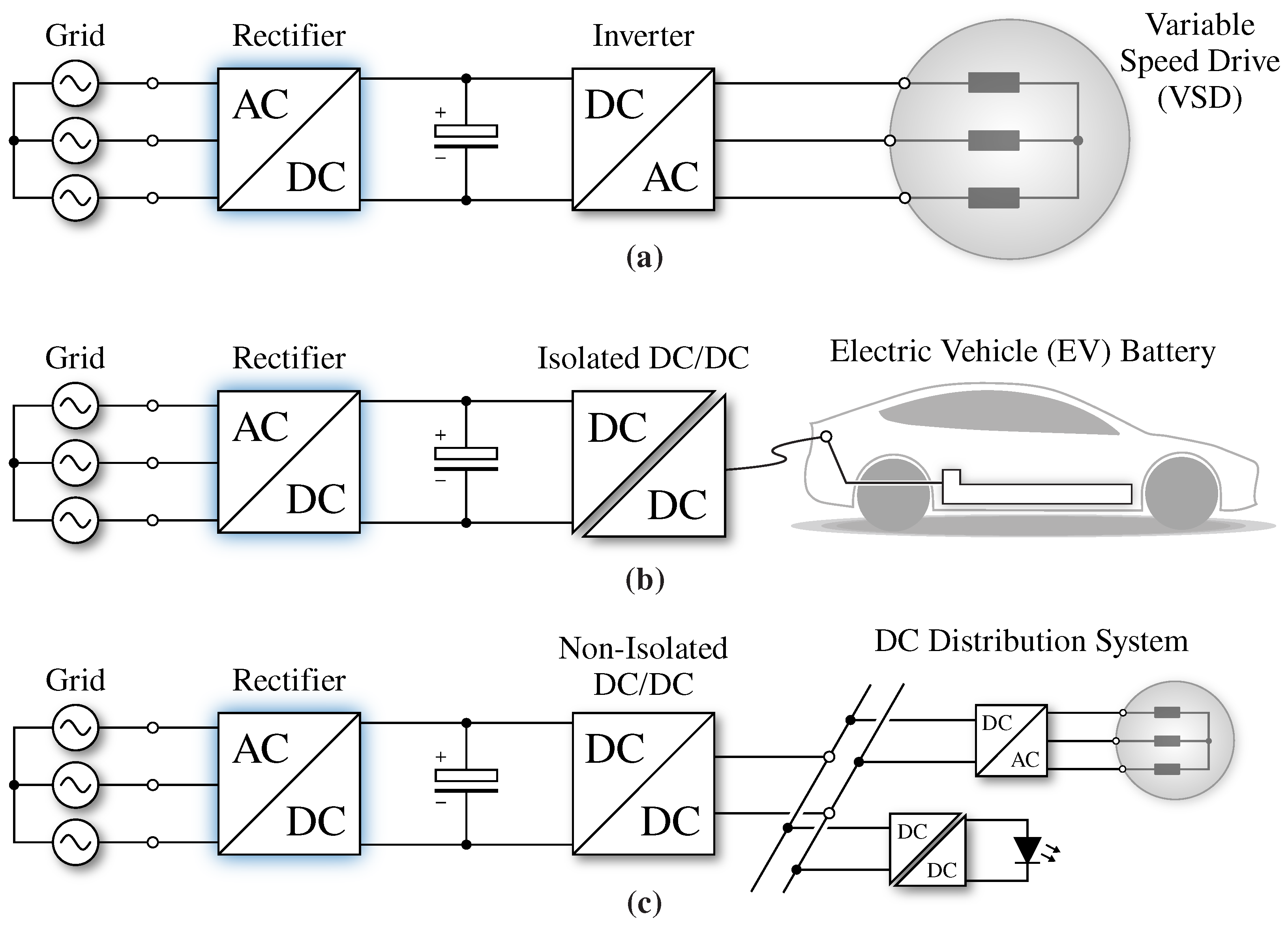

2]. Typically, the supply of high-power loads from the three-phase grid is performed in two stages, as illustrated in

Figure 1, the first being the rectifier or active front-end (AFE). The second conversion stage depends on the electrical system being supplied, such as three-phase DC/AC inverters for variable-speed drives (VSDs) or uninterruptible power supplies (UPSs) (

Figure 1a), isolated DC/DC converters for electric vehicle DC fast charging, telecommunication and data center power supplies, lighting systems or induction heating (

Figure 1b), and non-isolated DC/DC converters for DC distribution systems, high-power DC loads or DC microgrids (

Figure 1c).

General active rectification is typically performed by means of a conventional two-level inverter, due to its simplicity, robustness and intrinsic bidirectional capabilities. However, this topology has two major drawbacks, as it features a two-level output voltage waveform and requires semiconductor devices with relatively high voltage rating, both negatively affecting the converter losses and the grid-side filter size. Even though modern semiconductor technologies (e.g., high-voltage SiC MOSFETs) can substantially improve the two-level inverter performance by reducing losses and allowing for higher operating frequencies, multi-level converter solutions have demonstrated higher achievable performance, both in terms of efficiency and power density [

3,

4,

5]. In fact, these topologies simultaneously reduce the stress on the AC-side filter components and allow the employment of semiconductor devices with lower voltage rating and thus better figures of merit [

6].

When the power is only required to flow from the grid to the load, three-level unidirectional rectifiers represent perfect candidates for general active rectification [

7,

8,

9]. In particular, these converter topologies trade higher efficiency and power density for a slight complexity increase, thus achieving improved performance with respect to conventional two-level inverters [

3,

4,

5].

Besides high efficiency and high power density, the key requirements of a three-level rectifier can be summarized in (1) sinusoidal input current shaping, featuring low distortion and harmonics; (2) DC-link voltage regulation according to the desired reference value; and (3) control of the DC-link mid-point voltage deviation under normal operating conditions (i.e., balanced split DC-link loading). Other desired features include, but are not limited to, (4) minimization of the DC-link mid-point third-harmonic voltage oscillation [

8,

10], which directly affects the size of the DC-link capacitors and may be hard to reject by the subsequent conversion stage [

11]; (5) full control of the DC-link mid-point voltage deviation under unbalanced split DC-link loading [

7], which may occur when separate DC/DC units are connected to the two DC-link halves (e.g., in DC fast chargers [

12]); and (6) operation under non-unity power factor, to support the reactive energy flows in distribution grids [

13]. All the aforementioned required and desired features can be addressed either with a proper converter control strategy (1)–(6) [

14,

15,

16], with an accurate AC-side filter design (1) [

17,

18], or with an appropriate selection of the converter modulation strategy (4) [

8,

19]. In particular, (6) has not been explored in the literature and is increasingly becoming a desired feature of modern rectifiers, as distribution system operators (DSOs) are starting to charge end consumers for the injection/withdrawal of reactive energy into/from the grid [

20]. If properly controlled, existing unidirectional rectifiers could in fact actively compensate this reactive power excess and/or substitute traditional power factor correction capacitor banks, benefiting the DSO and improving the system power quality.

The main challenges in achieving (1)–(6) are strictly related to the unidirectional nature of three-level rectifiers. One major issue is the discontinuous conduction mode (DCM) operation of the converter around the current zero-crossings, which, if not correctly addressed, can lead to unacceptable phase current distortion in light load conditions [

21]. Moreover, unidirectional rectifiers are characterized by narrower operating limits with respect to their two-level and three-level bidirectional counterparts, mainly affecting the operation under non-unity power factor, the maximum DC-link mid-point current capability and the converter ability to compensate the low-frequency DC-link mid-point voltage oscillation. In particular, the rectifier operation under non-unity power factor and/or under constant zero-sequence voltage injection (i.e., when unbalanced split DC-link loading occurs) typically yields large and uncontrolled input current distortion, as reported in several previous works [

22,

23,

24,

25,

26,

27], practically limiting the acceptable operating region of the converter. Although high current control loop bandwidth and enhanced phase current sampling strategies may improve the rectifier input current distortion [

16], especially in light load conditions, these approaches lose effectiveness when significant voltage-to-current phase-shift and/or zero-sequence voltage injection are required.

Mainly because of the aforementioned reason, several papers dealing with the analysis and the control of three-level unidirectional rectifiers under diverse operating conditions have been published in the literature [

7,

8,

9,

14,

15,

22,

23,

24,

25,

26,

27,

28,

29].

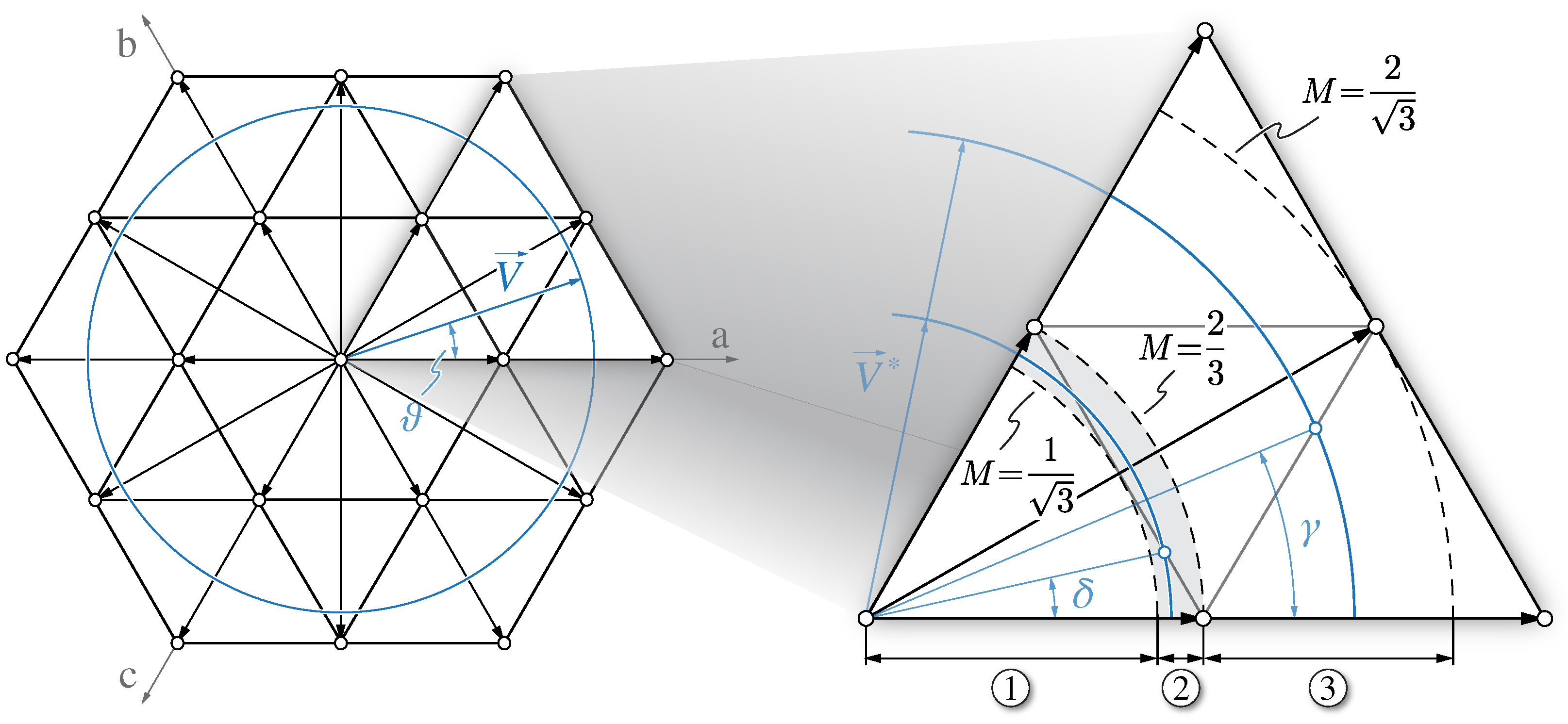

In particular, [

7,

8,

9] are the first papers analyzing the operational limits and the DC-link mid-point current capability of unidirectional three-level rectifiers, identifying a direct relation between the allocation of the converter redundant switching states (i.e., strictly related to the zero-sequence voltage injection) and the mid-point current generation process. Moreover, a preliminary attempt to control the DC-link mid-point voltage deviation is proposed in [

9], acting on the zero-sequence current reference of a hysteresis current controller. However, no details on the operation of the rectifier with non-unity power factor are provided.

A detailed small-signal analysis of unidirectional three-level rectifiers is described in [

14] and a complete multi-loop control strategy is proposed, enabling the accurate regulation of the DC-link mid-point voltage deviation. The same authors develop in [

28] a carrier-based modulation strategy for three-level rectifiers based on the translation of conventional space vector dwell times into an equivalent zero-sequence duty-cycle injection. With this approach, the zero-sequence voltage limits of the converter are correctly taken into account, resulting in undistorted input currents under non-unity power factor operation and when a constant zero-sequence voltage is injected (i.e., to regulate the mid-point current). Nevertheless, the proposed implementation is quite complex, and no current distortion assessment is performed.

A direct carrier-based approach for undistorted operation under non-unity power factor is first proposed in [

22]. This method is based on the addition of a zero-sequence voltage component to all bridge-leg voltage references, to make sure that the sign of the reference voltages is always equal to their respective phase currents. In fact, the unidirectional nature of the rectifier does not allow for the generation of a bridge-leg voltage with different sign as the current flowing in it. This approach, however, only solves the distortion issue for non-unity power factor operation (i.e., it has no general validity) and does not ensure sinusoidal operation when a constant zero-sequence voltage is injected.

In a similar way, [

23,

24,

25,

26,

27,

29] try to address the input phase current distortion deriving from non-unity power factor operation either by injecting a suitable zero-sequence voltage component for carrier-based approaches, or by correctly allocating the redundant switching states in space vector-based implementations. Nevertheless, none of these papers proposes a general and/or unified approach to ensure undistorted operation also under constant zero-sequence voltage injection.

Finally, a general methodology ensuring that the sign of the rectifier bridge-leg voltages remains equal to their respective phase currents in every operating condition is identified in [

15]. This approach is based on the saturation of the reference zero-sequence voltage according to straightforward analytical relations and is theoretically able to ensure undistorted input current for both non-unity power factor operation and constant zero-sequence voltage injection. However, the converter distortion performances are not assessed and the effects of the zero-sequence voltage saturation on the DC-link mid-point current are not investigated.

As a further note, several considerations and analysis methods that have been specifically developed for three-level bidirectional inverters (e.g., to estimate and/or minimize the DC-link mid-point current and voltage oscillation [

10,

30,

31,

32,

33,

34], to control the DC-link mid-point voltage deviation with/without load unbalance [

33,

34], etc.) or the addition of an independent neutral module in four wire systems (i.e., to independently control the DC-link mid-point current in every operating condition [

35,

36]) have general validity and could thus be as well applied to three-level unidirectional rectifiers with minor modifications. Nevertheless, no additional and/or relevant elements with respect to the presented literature survey on unidirectional topologies has been identified.

Even though the operation and the control of three-level rectifiers have been thoroughly analyzed in the literature, according to the authors’ best knowledge, a clear and complete analysis of the effects of non-unity power factor operation and constant zero-sequence voltage injection (i.e., operation under unbalanced split DC-link loading), has yet to be provided. In particular, no simple and unified carrier-based PWM approach ensuring undistorted operation of unidirectional rectifiers across their entire operating region has been proposed and verified experimentally. Moreover, no analytical expressions for the converter maximum DC-link mid-point current capability and minimum DC-link mid-point charge ripple for variable modulation index and power factor angle have been identified, forcing converter designers to make use of numerical and/or circuit simulations.

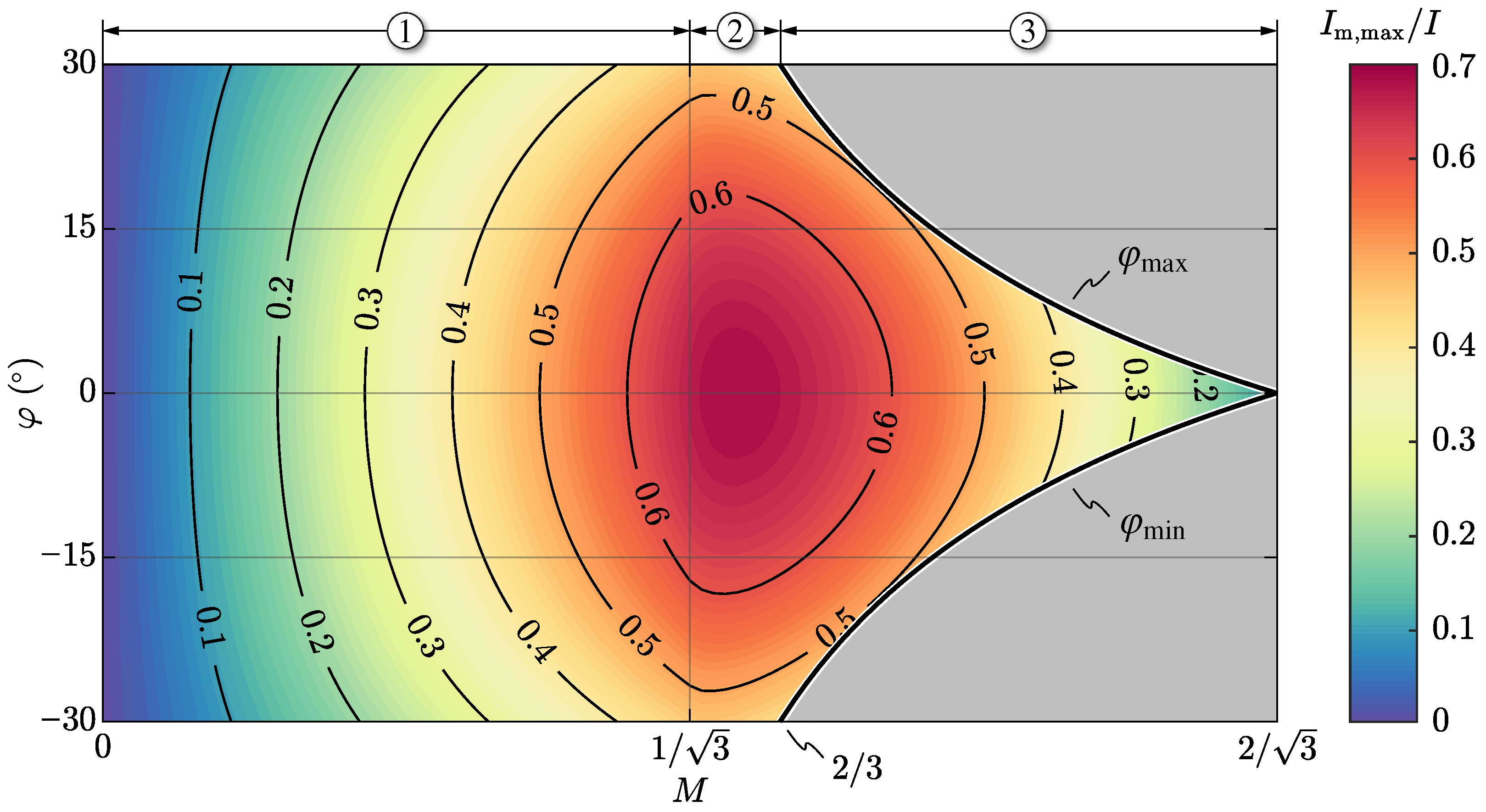

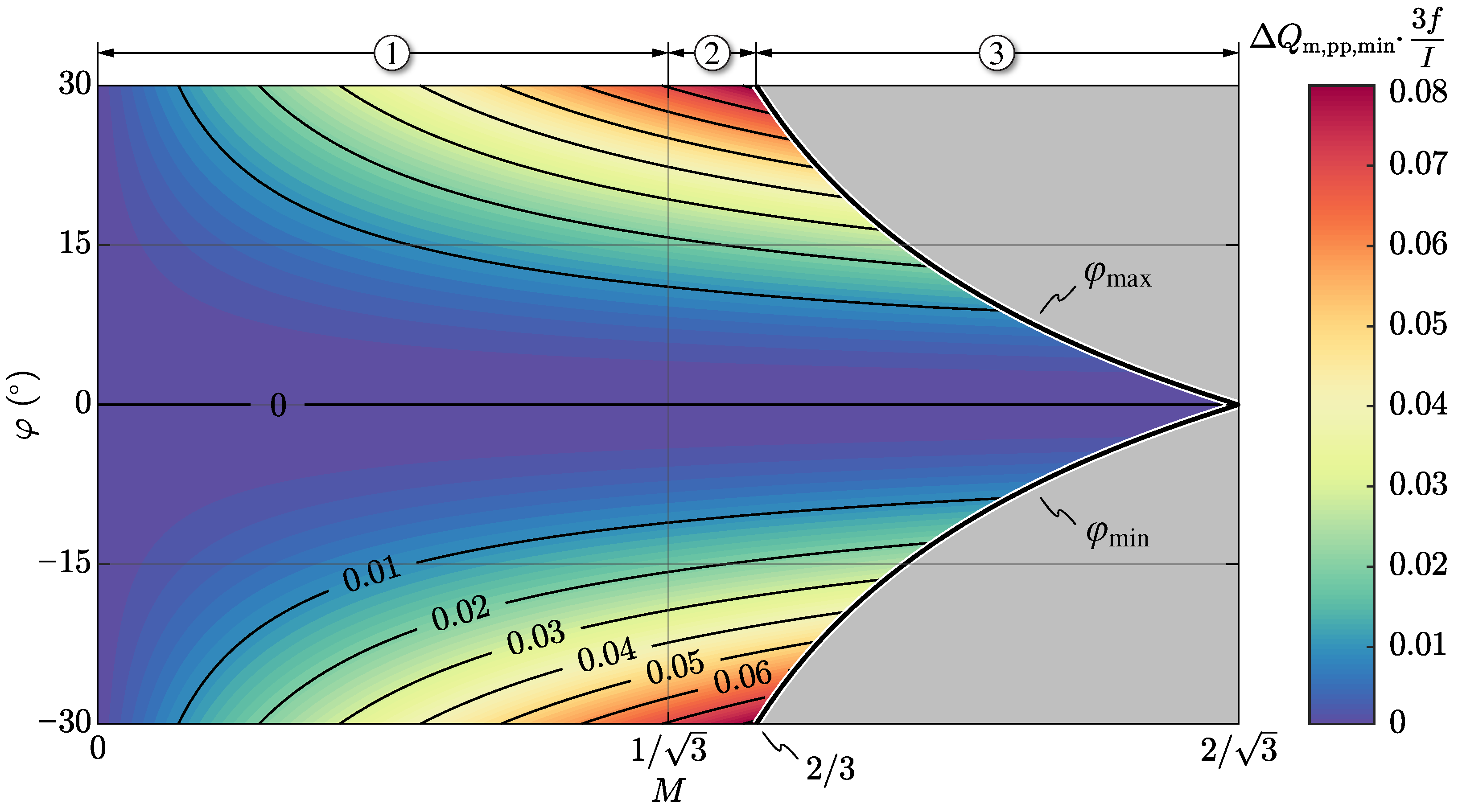

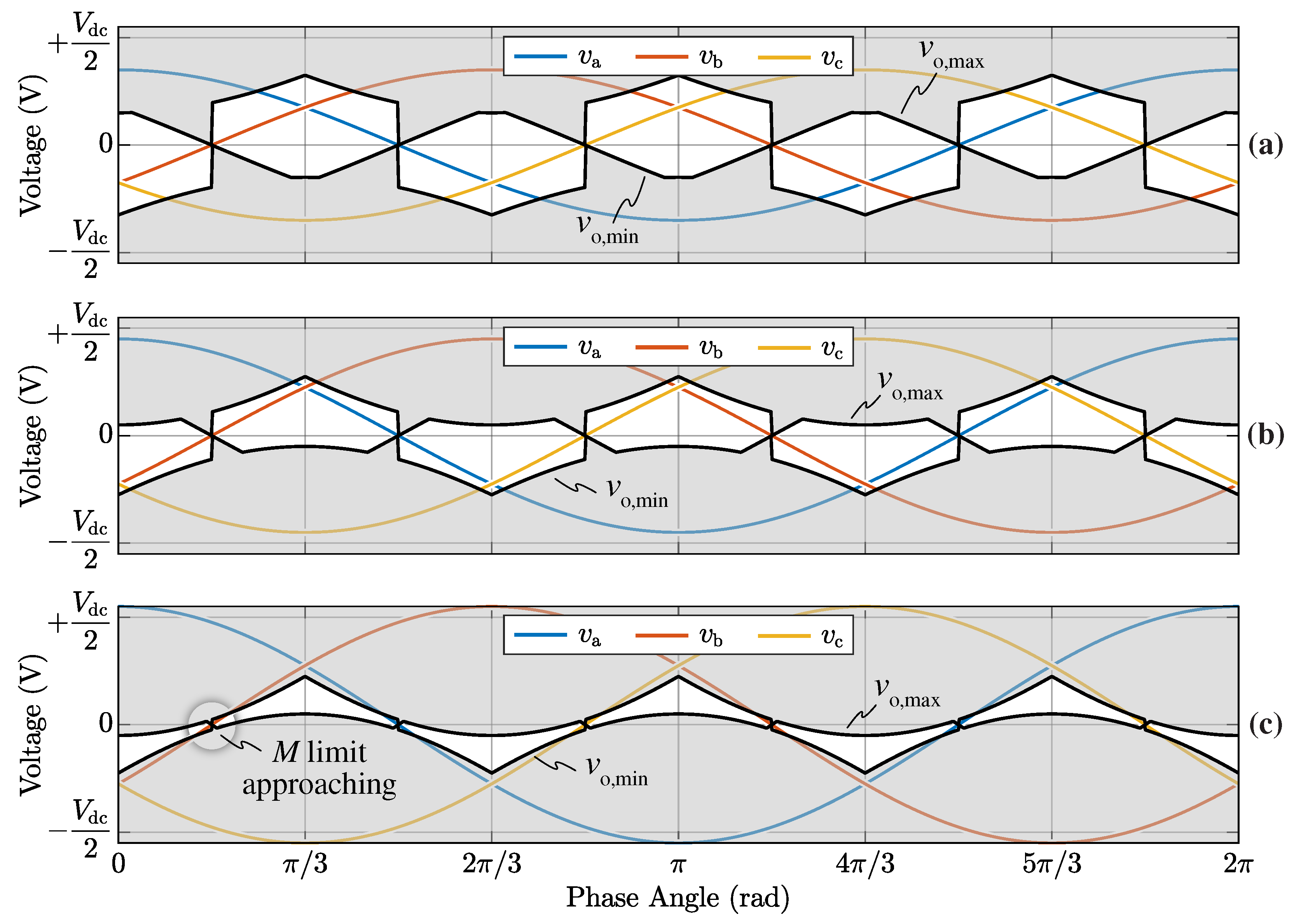

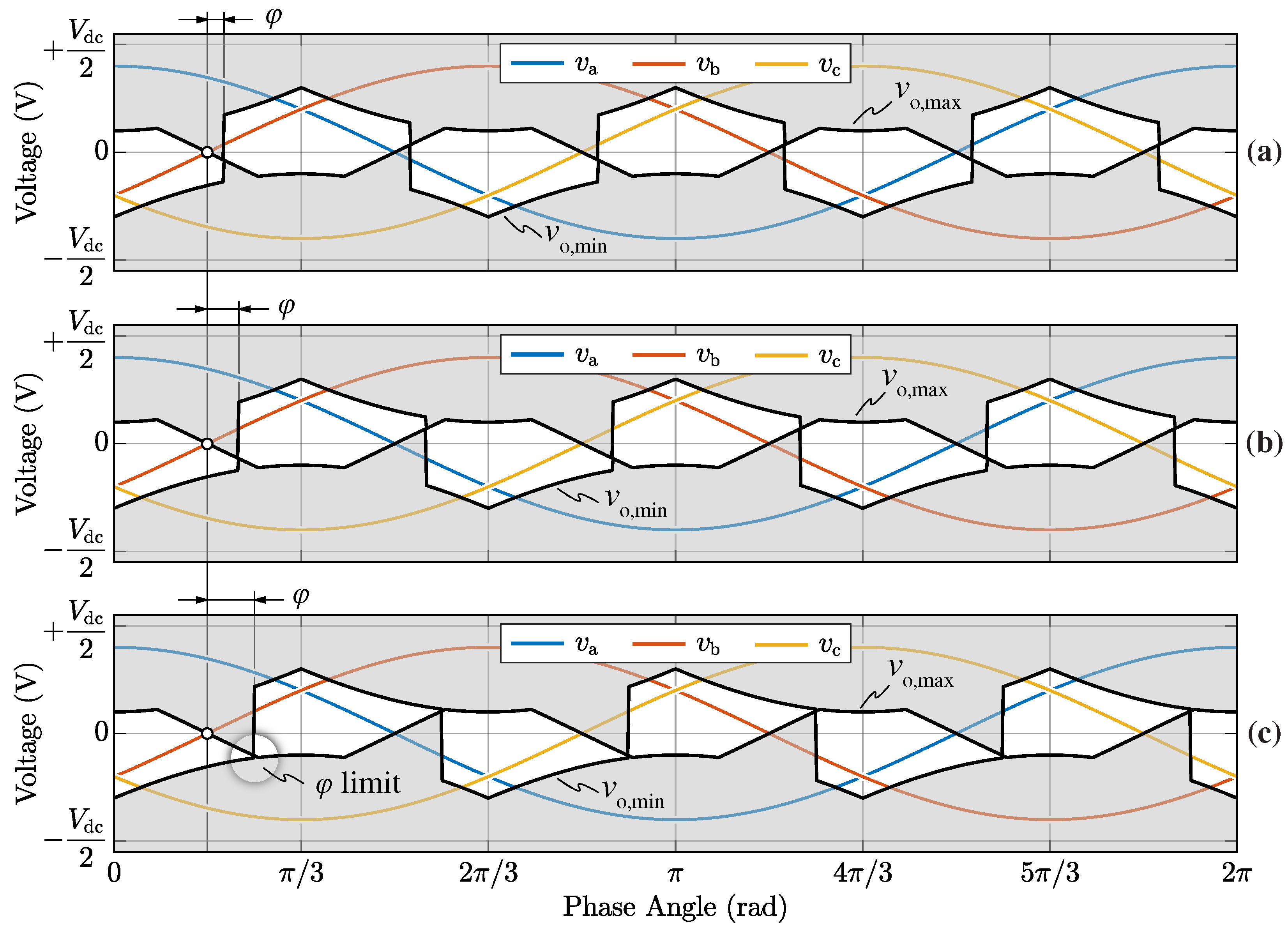

Therefore, this paper proposes a complete analysis of three-level unidirectional rectifiers under non-unity power factor operation and zero-sequence voltage injection, with the main goal of providing a simple and comprehensive overview of the rectifier limits and performance. The major contributions of this work are: (1) the adoption of a unified carrier-based PWM approach ensuring undistorted operation of the rectifier in every feasible operating condition (i.e., for variable power factor and variable zero-sequence voltage injection), based on the saturation of the zero-sequence voltage reference; (2) the analytical derivation of the DC-link mid-point current limits over the complete operating range of the rectifier; and (3) the analytical derivation of the minimum low-frequency (i.e., third-harmonic) mid-point peak-to-peak charge ripple for all feasible modulation index and power factor angle values. In particular, (3) allows the sizing of the split DC-link capacitors of three-level rectifiers with a straightforward analytical formula.

This paper is structured as follows. In

Section 2 the operational basics of three-level unidirectional rectifiers are described and the converter limits in terms of zero-sequence voltage, modulation index, power factor angle, maximum DC-link mid-point current and minimum mid-point charge ripple are derived, leveraging the analytical approaches reported in Appendices

Appendix A and

Appendix B. In

Section 3 the proposed analysis is verified experimentally on a digitally controlled 30

T-type converter prototype, assessing the input phase current distortion, the maximum mid-point current capability and the minimum mid-point charge ripple across all rectifier operating points. Finally,

Section 4 summarizes and concludes this work.

3. Experimental Results

In this section, the rectifier limits and performance in terms of displacement power factor (DPF), current total harmonic distortion (THD), maximum mid-point current capability and minimum mid-point charge ripple are experimentally assessed on a digitally controlled T-type converter prototype, supporting the theoretical analysis provided in

Section 2,

Appendix A and

Appendix B. For reasons of conciseness, the converter performances are here evaluated only in steady-state conditions, nevertheless a complete assessment of the dynamical behavior of the considered rectifier prototype is provided in [

16].

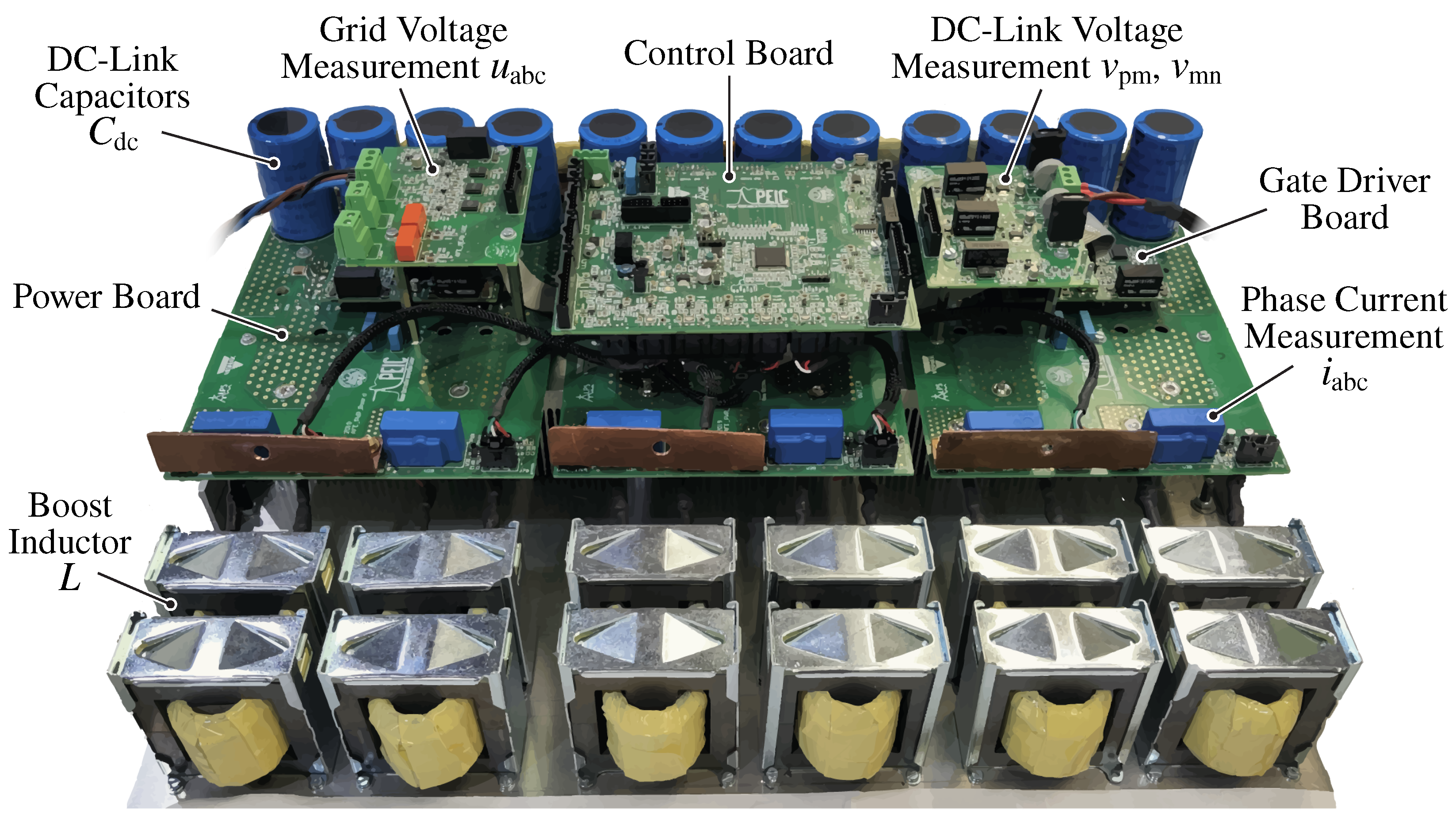

The specifications and the nominal operating conditions of the three-level T-type unidirectional rectifier exploited for the experimental validation are reported in

Table 1. It is worth noting that this converter has been designed as the active front-end stage of an electric vehicle ultra-fast battery charger [

16,

39]. The rectifier prototype is illustrated in

Figure 11 and consists of two paralleled three-phase 30

units, realized for modularity reasons. Nevertheless, only one converter unit is used in the experimental tests, due to the maximum power limitation of the available equipment.

Each converter bridge-leg employs two 650

Si MOSFETs connected in anti-series (i.e., as 4Q switch) operating at 20

and two 1200

Si fast-recovery diodes. Furthermore, the converter boost inductors employ XFlux 60

powder cores from Magnetics [

40], which are characterized by a soft-saturating B–H characteristic. This feature leads to a current-dependent variable inductance value (see

Table 1), which must be taken into account in the control tuning [

16]. The detailed characteristics of the inductor design are reported in [

39], obtained as a result of the optimization procedure described in [

41].

Figure 12 shows a schematic diagram of the adopted experimental setup. The T-type rectifier is connected to a grid emulator (i.e., emulating the 50

, 400

European low-voltage grid) by means of an

filter, consisting of the converter boost inductors (

L), filter capacitors (

) equipped with series damping resistors (

), and grid-side inductors (

). The main scope of the

filter is to eliminate the switching-frequency harmonic content from the grid currents

[

17,

42], so that a lower current total harmonic distortion (THD) is achieved and the converter may comply with grid-code standards [

43,

44]. Furthermore, the presence of the

filter allows isolation of the low-frequency component of the distortion, which depends on the control strategy, from the switching-frequency one, which only depends on the selected modulation scheme, allowing for a proper assessment of the converter closed-loop control performance. In the present case, the values of

and

are selected according to [

39], and the value of

is representative of an equivalent inner grid impedance of ≈0.02 pu. On the DC-side, the converter is connected to two independent electronic loads, which emulate the rectifier split DC-link loads. The measurements are performed both with a Teledyne LeCroy 500 MHz, 12-bit, 10 GS/s, 8-channel oscilloscope (i.e., employing isolated high-voltage differential probes for voltage measurements and standard current probes for current measurements), and with an HBM GEN4tB 2 MS/s data acquisition system, leveraging current and voltage sensors with high rated accuracy (i.e., <

). In particular, the latter approach has been exploited to automatically map the rectifier performance over its complete operating region.

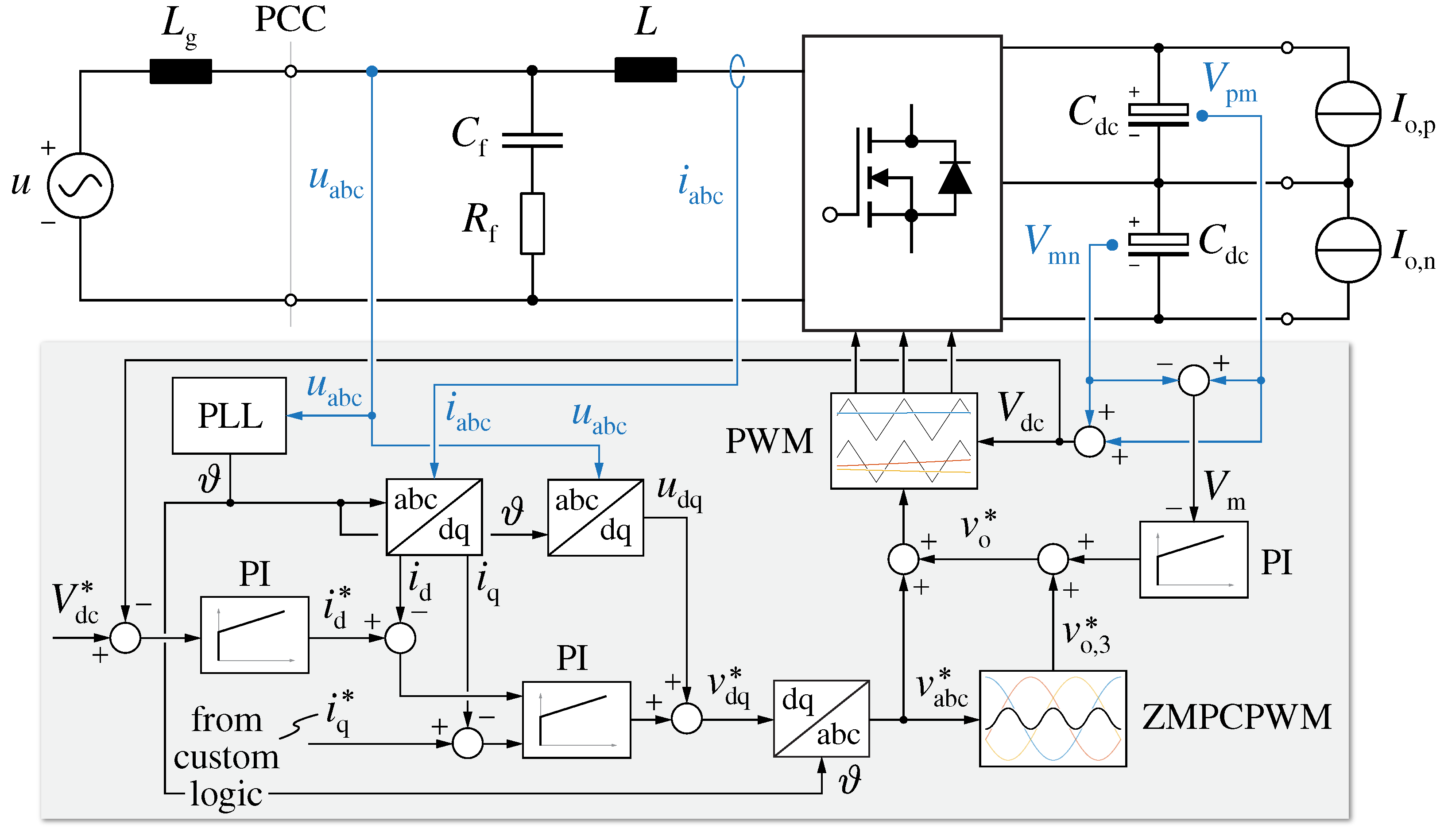

3.1. Multi-Loop Control Scheme

The rectifier is controlled with the full-digital multi-loop control strategy reported in [

16], where the detailed description and tuning of all loops is provided. A conventional voltage-oriented dq current control scheme is adopted [

17,

45,

46,

47], complemented by a DC-link voltage loop, tracking the desired DC-link voltage value

, and a DC-link mid-point voltage balancing loop, ensuring limited steady-state and dynamical

voltage deviation. A simplified block diagram of the complete system and the adopted control strategy is provided in

Figure 13.

The voltages at the point of common coupling (PCC) are measured to achieve the reference frame synchronization with the grid by means of a phase locked loop (PLL) [

48,

49]. The measured grid voltages are then fed forward in the current control loop, to unburden the integral part of the PI regulator. Even though the digital sampling and update process is performed once per switching/control period, the

current feedback values are obtained by means of oversampling (32 samples per control period) and averaging, to enhance the measurement quality around the current zero-crossings. In fact, traditional synchronous/asynchronous sampling approaches do not provide the correct average current value when discontinuous conduction mode (DCM) takes place [

21,

50], thus affecting the current control accuracy and leading to increased low-frequency distortion. The DC-link voltage loop controls the active power transfer of the rectifier and therefore provides the reference to the d-axis current control loop. The q-axis current

, instead, is typically controlled to compensate the reactive power injected by the filter capacitors

(i.e., to ensure unity power factor operation at the PCC), nevertheless it can be set to any value that complies with the converter-side power factor angle limitations of the rectifier (see

Section 2.4), being

. Finally, the DC-link mid-point voltage balancing loop ensures

at all times, acting on the zero-sequence voltage

injection [

9,

14,

15,

16,

51]. In particular, this control loop theoretically does not interfere with the others, as

affects neither the active power transfer nor the phase current formation process (see

Section 2.1.1). Furthermore, the measured

is passed through a moving average filter operated at

, so that the control loop does not react to the possibly occurring low-frequency mid-point voltage oscillation.

In practice, the complete converter multi-loop control strategy is implemented on a STM32G474VE MCU from ST Microelectronics [

52] with an interrupt service routine running at

.

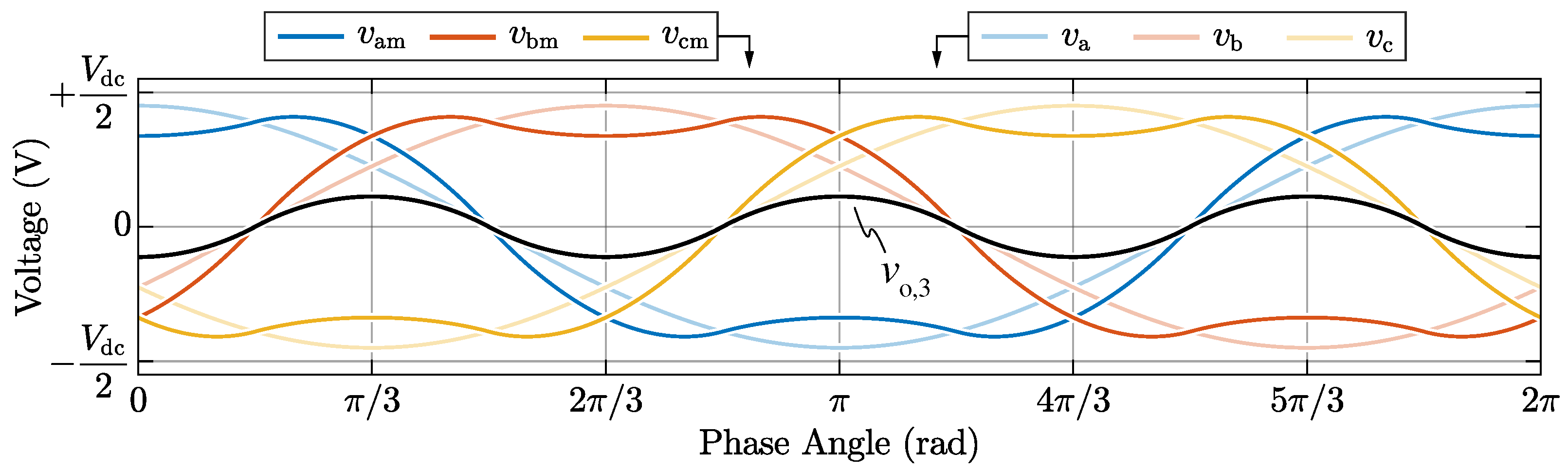

3.2. Steady-State Performance Evaluation

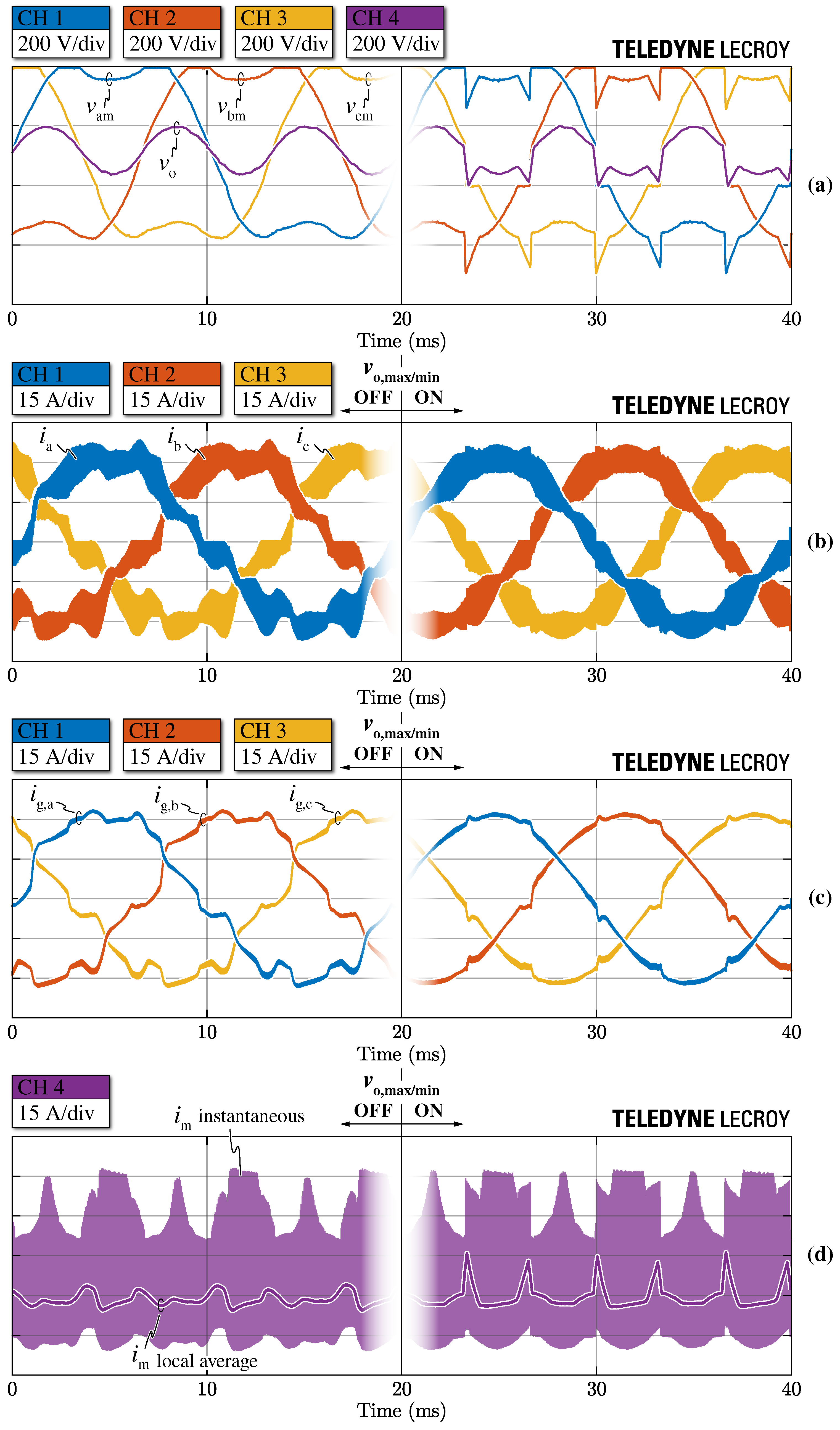

The most significant rectifier waveforms in steady-state operation are illustrated in

Figure 14, where the grid voltages

, the converter-side currents

and the grid-side (i.e., filtered) currents

are shown for

,

and different values of transferred power. It is observed that the grid-side current quality improves with the rectifier loading. For instance, at 10% of the rated power (see

Figure 14b) the converter-side current ripple amplitude becomes comparable to the current peak value, therefore leading to marked low-frequency zero-crossing distortion that bypasses the filter capacitor and appears in the grid-side currents. Even though the distortion at light load may seem large, the pronounced DCM operation of unidirectional rectifiers typically leads to much higher distortion levels [

21]. In the present case, the pseudo-sinusoidal shape of the currents is maintained thanks to the adopted current oversampling and averaging strategy, the high current control loop bandwidth and the feed-forward contributions reported in

Figure 13 [

16]. At 50% and 100% of the rated power (see

Figure 14c,d the quality of both converter-side and grid-side currents improves substantially, as the relative amplitude of the current ripple decreases and the zero-crossing distortion related to DCM operation is mostly eliminated by the current control loop [

16].

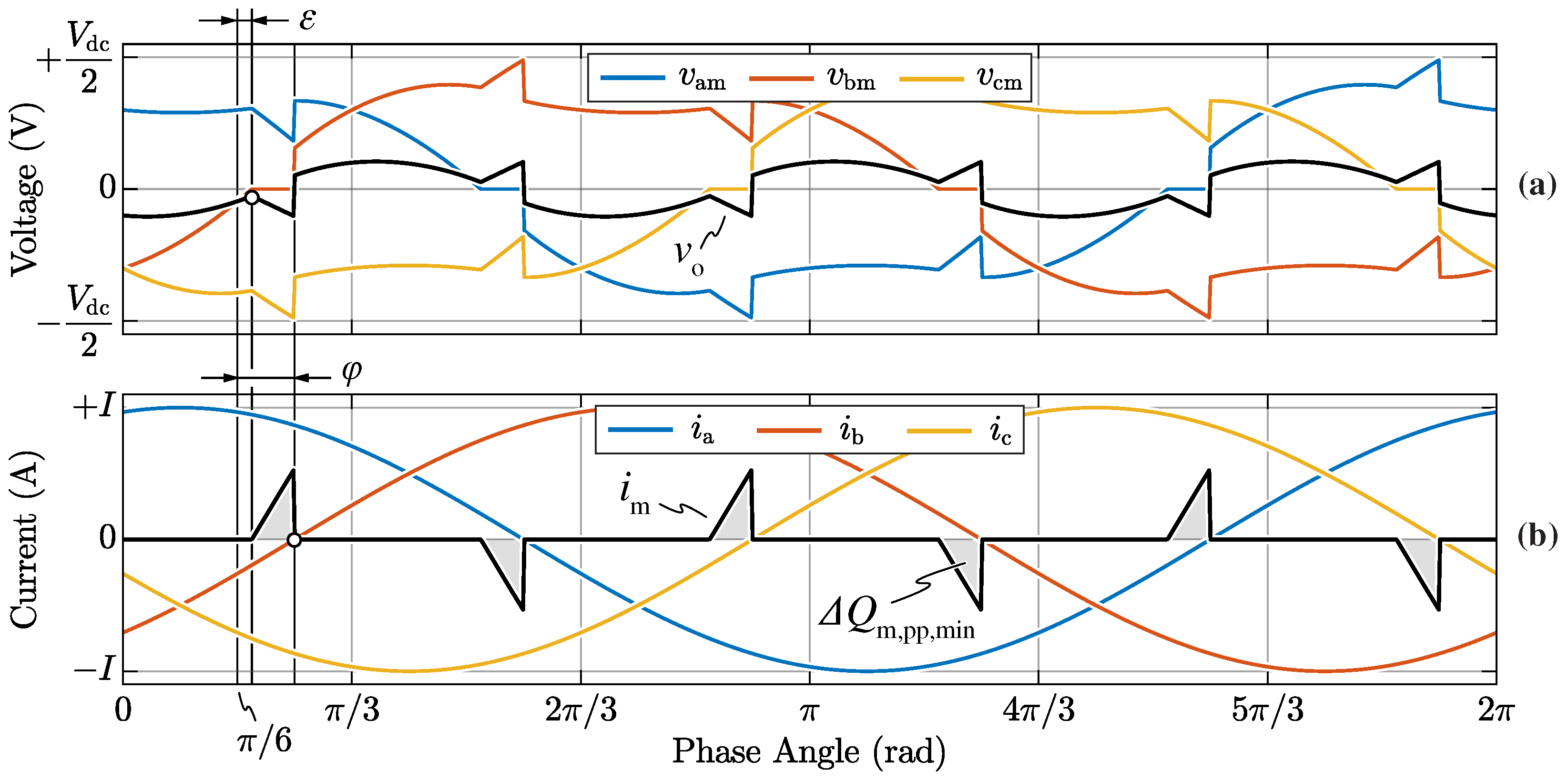

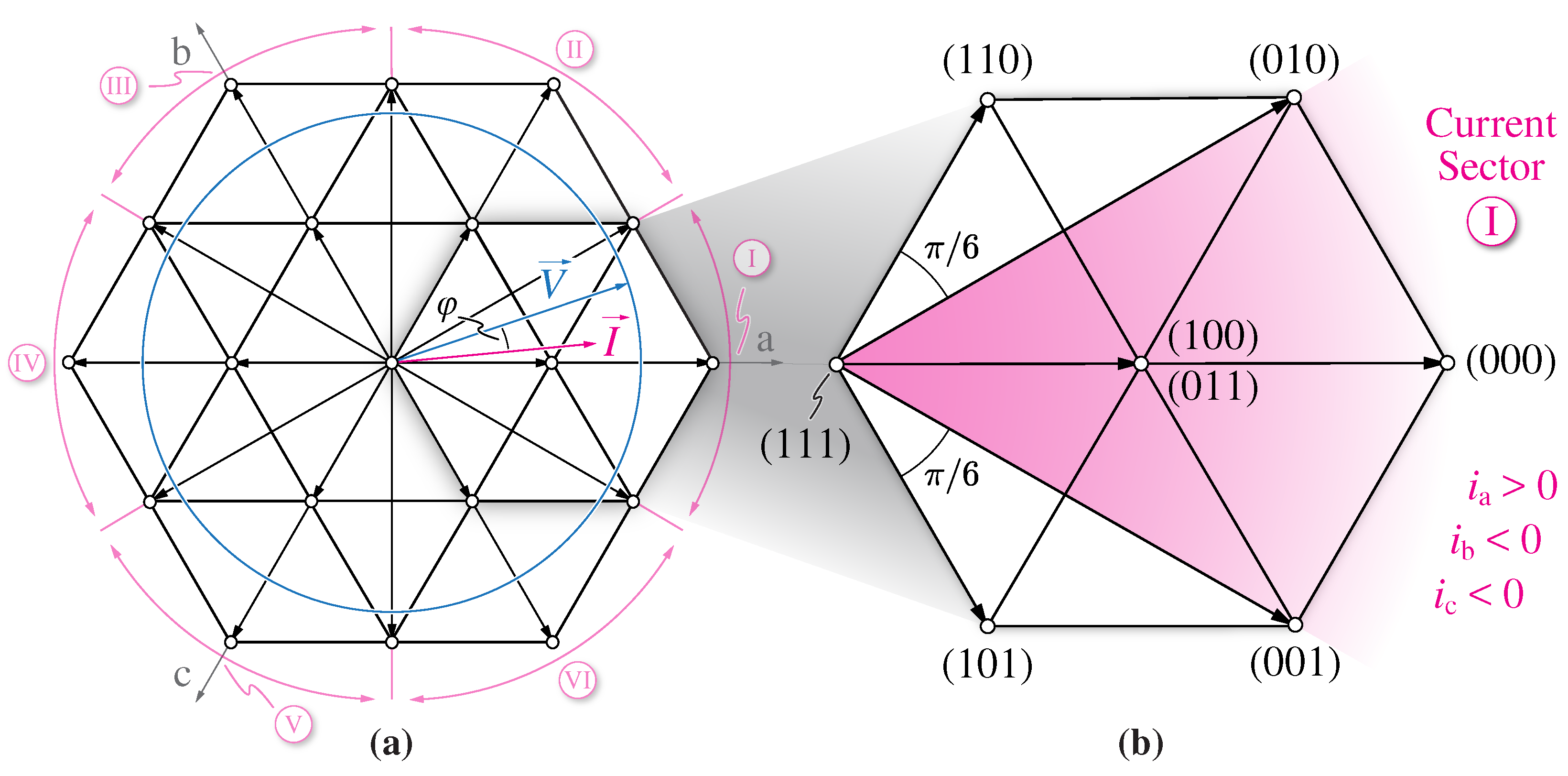

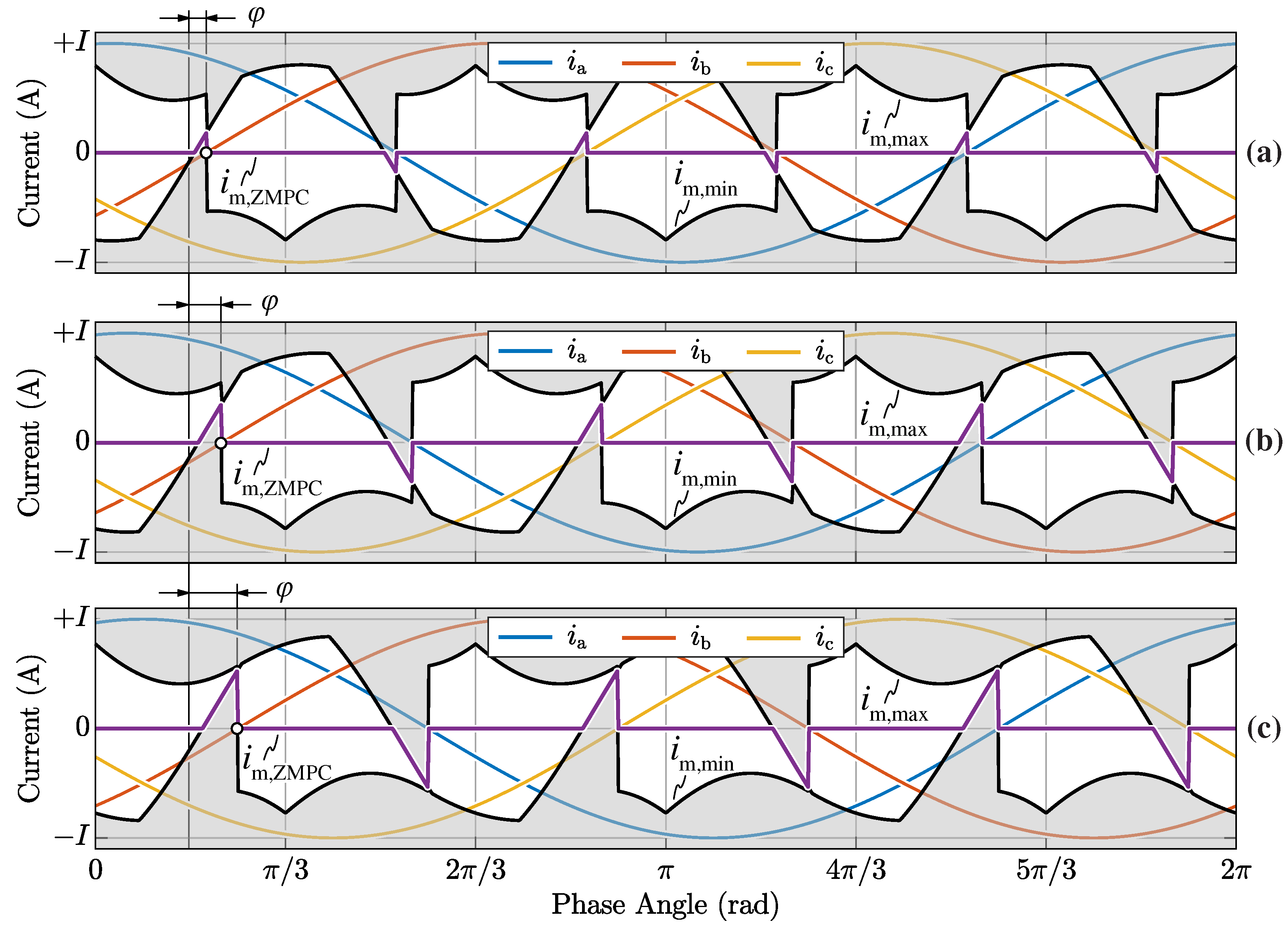

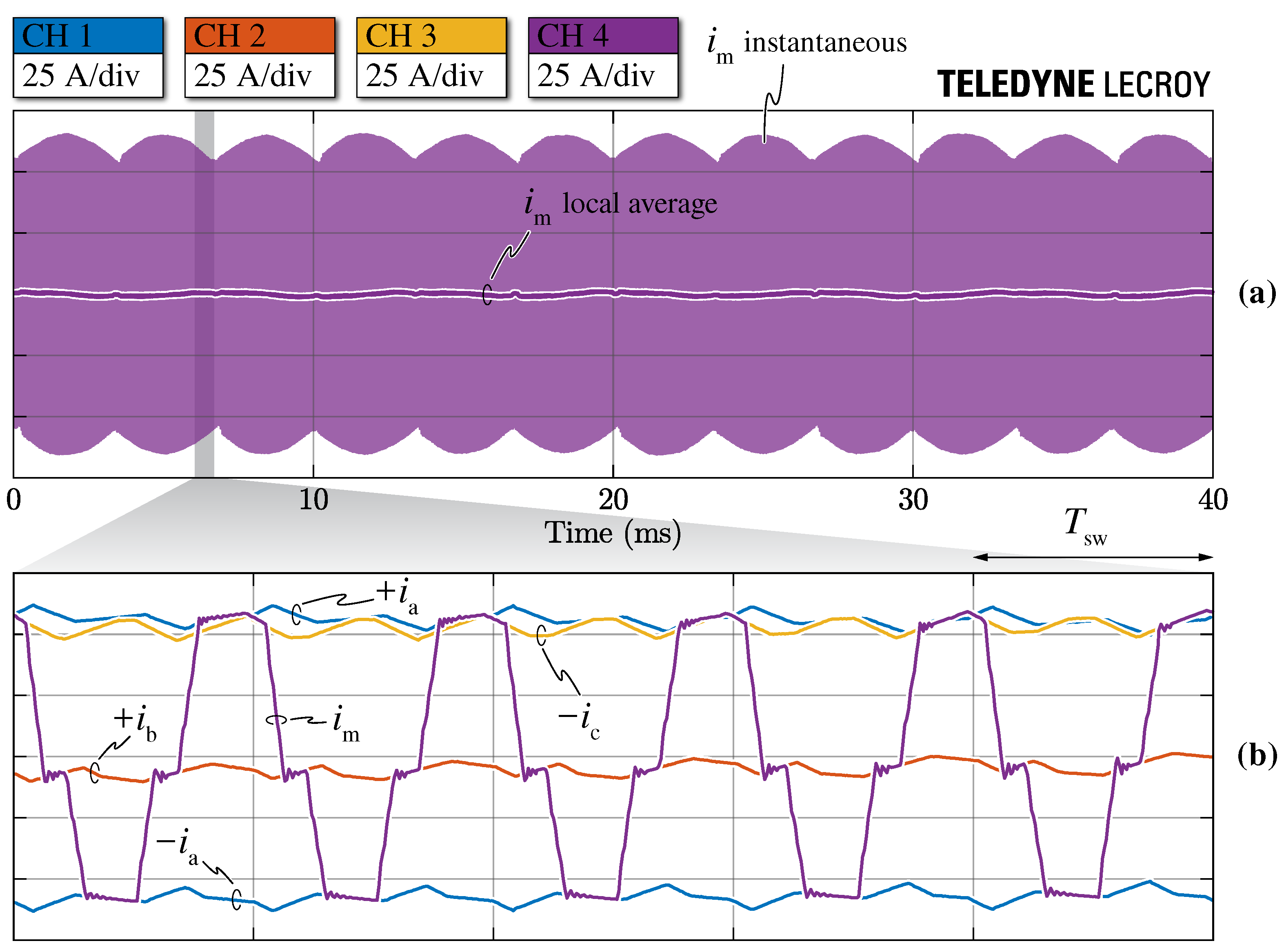

Both instantaneous and local average values of the DC-link mid-point current

for

(

),

and

are illustrated in

Figure 15, where a focus is also provided in (b). Although the instantaneous value of

jumps between the converter-side phase current values

,

,

and 0 (i.e., visible from the current envelopes), the local average value of

remains approximately 0 along the complete grid period, due to the adopted zero-mid-point current modulation (ZMPCPWM) strategy. A focus of the instantaneous values of

,

,

and

towards the end of current sector Ⓘ is provided in

Figure 15b, where the mid-point current is shown to jump between

(state 100),

(state 011),

(state 010) and

(state 110), as expected from space vector theory (see

Figure 3b).

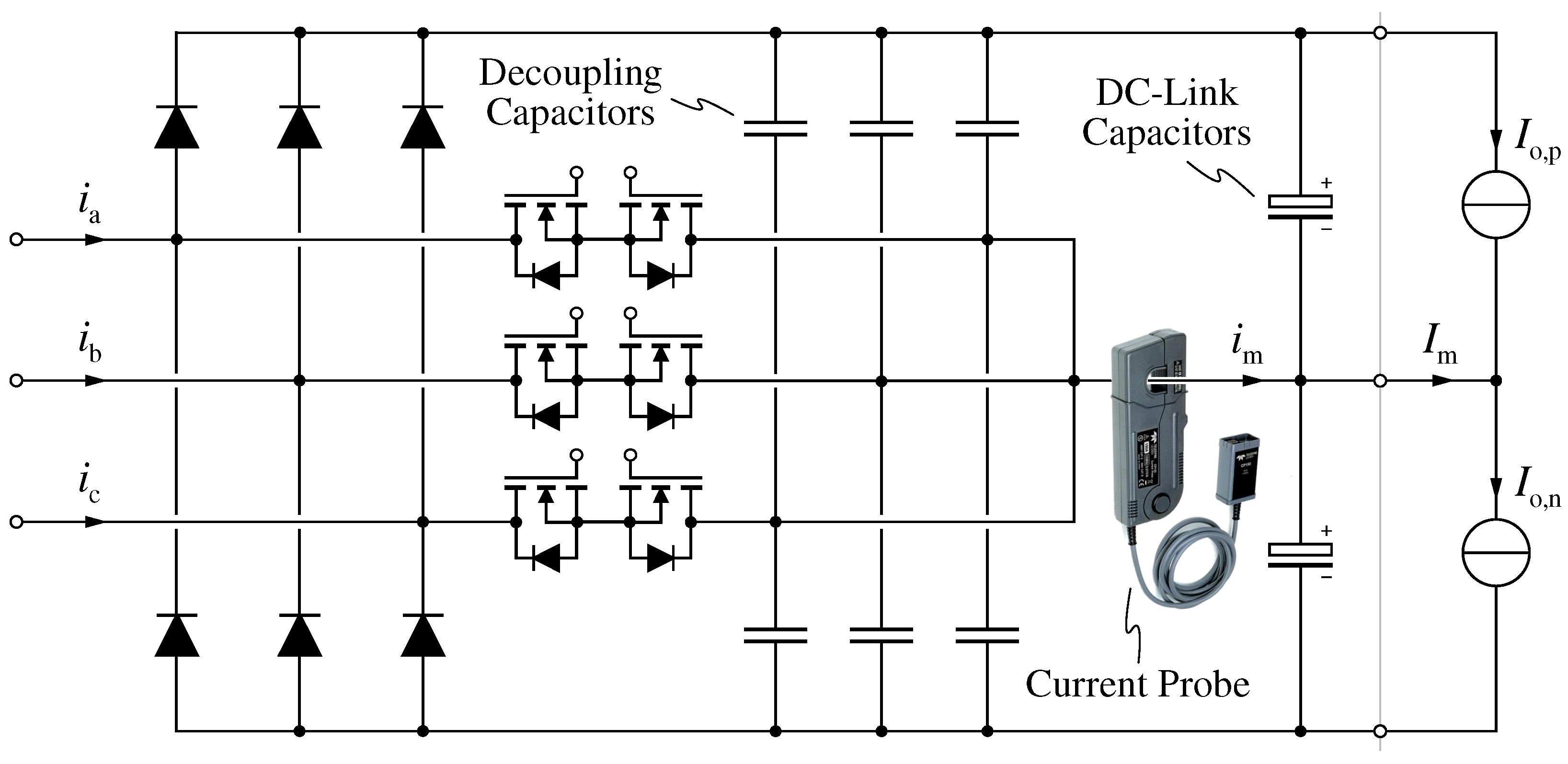

It is worth noting that the measurement of the instantaneous mid-point current value is not common in the literature (i.e., the only case known to the authors is [

53]), as it represents a challenging task to achieve. In practice, the current measurement must be placed within the commutation loop of all bridge-legs, thus negatively affecting the switching performance of the rectifier. In the present case, the measurement of

has been achieved by placing the current probe between the bridge-leg decoupling capacitors (i.e., 220

ceramic capacitors) and the DC-link capacitors (i.e., 4080

electrolytic capacitors), as schematically illustrated in

Figure 16. Even though the decoupling capacitors are placed in parallel to the DC-link capacitors, their small capacitance value does not substantially affect the mid-point current, especially considering the relatively low switching frequency of the rectifier.

Figure 17 and

Figure 18 show the most relevant rectifier waveforms under non-unity power factor operation and constant zero-sequence voltage injection, respectively. In particular, the reference bridge-leg voltages

,

,

, the reference zero-sequence voltage

, the converter-side currents

, the grid-side currents

and the DC-link mid-point current

are shown for

and

. Furthermore, the effect of the zero-sequence voltage saturation

on all measured quantities is highlighted by comparing the results with a conventional control implementation (i.e., with no saturation acting on

). It is worth noting that

,

,

and

are obtained from separate digital-to-analog converters (DACs) of the MCU (i.e., with a 0–

scale) and are thus rescaled in

Figure 17a and

Figure 18a.

Figure 17 shows the operation of the rectifier with

. In particular,

Figure 17c highlights that non-unity power factor operation generates a large zero-crossing distortion if no zero-sequence voltage saturation is implemented. The enforcement of

, in fact, allows the rectifier to correctly apply the desired bridge-leg voltage values even when the phase currents are phase-shifted with respect to the reference voltages, as described in

Section 2. Consequently, undistorted operation under non-unity power factor is achieved. Furthermore,

Figure 17d shows that by saturating the zero-sequence voltage, a larger mid-point current local average

and thus a higher DC-link mid-point peak-to-peak charge ripple

are obtained. This is because, to ensure the undistorted operation of the rectifier, the applied zero-sequence voltage

departs from the ideal

value introduced by the ZMPCPWM (see

Figure 17a). It is also worth observing that the local average of

obtained experimentally is in good agreement with the simulated waveforms reported in

Figure 7 and

Figure A4b.

The rectifier waveforms with a constant zero-sequence voltage

added to

(i.e., ZMPCPWM injection) are shown in

Figure 18. This injection emulates the converter performance under unbalanced split DC-link loading, i.e., when a constant mid-point current periodical average

is required. This is highlighted in

Figure 18d, where the injection of a positive zero-sequence voltage is shown to generate a negative value of mid-point periodical average

, as expected from theoretical considerations. Additionally in this case larger

and

ripple values are obtained when the

saturation is enabled.

Figure 18c shows that the zero-sequence voltage saturation

allows substantial improvement of the phase current waveforms. Nevertheless, in this case the zero-crossing distortion cannot be completely avoided, since the injection of the constant zero-sequence voltage contribution increases the amplitude of the converter-side current ripple (see

Figure 14c for comparison), which widens the DCM window around the current zero-crossings and leads to higher distortion. It is worth noting that this issue can be greatly reduced in practice by independently controlling the two anti-series mid-point switches, such that the free-wheeling of the current through the mid-point is always possible [

26]. In fact, even though in the present case the two anti-series switches are supplied by independent gate drivers, they receive equal PWM signals, greatly simplifying the modulation and the control of the rectifier. It should be pointed out that the low-frequency distortion would mostly disappear at full load (i.e.,

), due to the lower ratio between the current ripple and the current peak. However, this condition could not be tested, due to the power limitations of the adopted electronic loads.

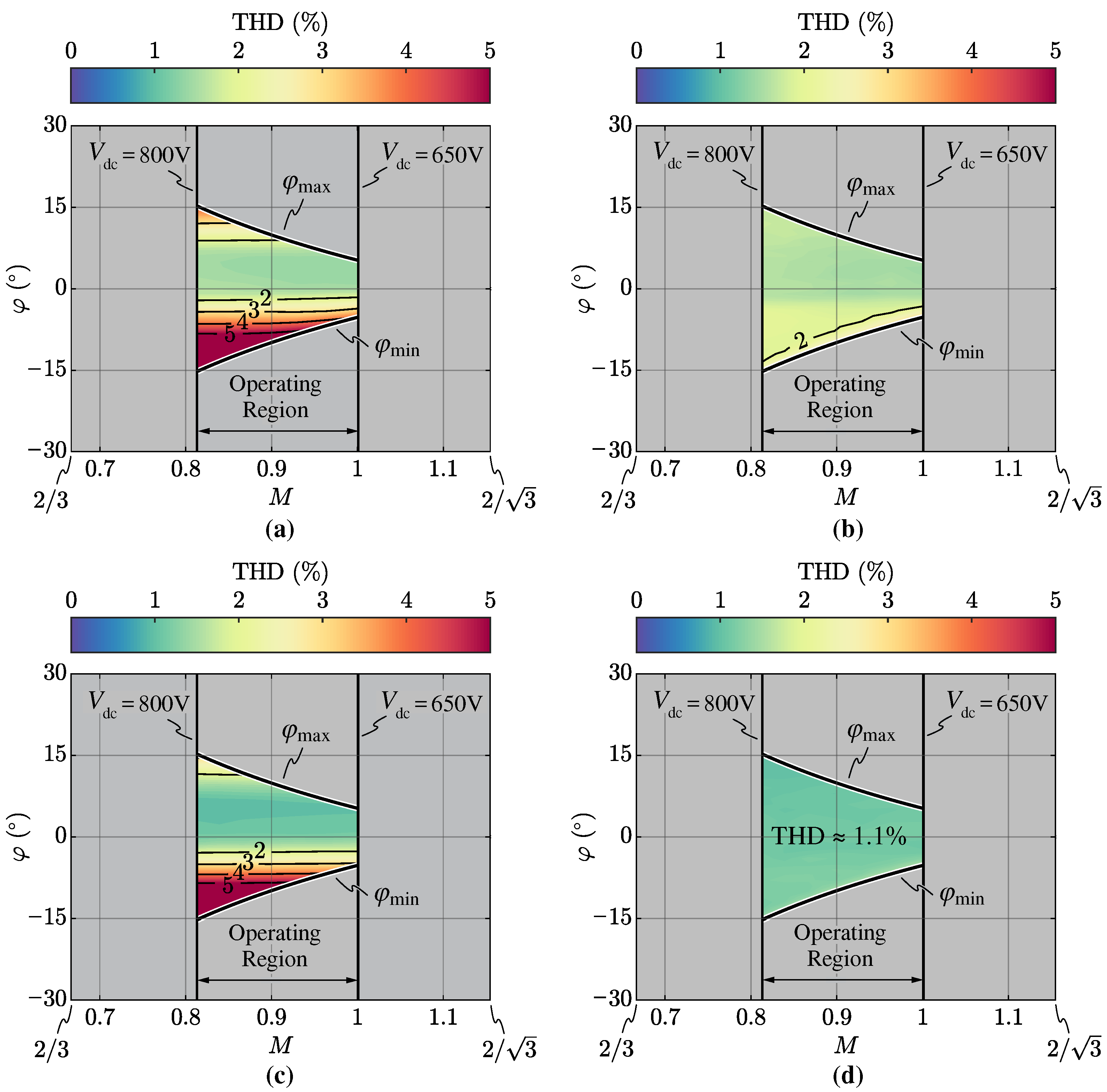

3.2.1. Total Harmonic Distortion (THD)

The grid-side current total harmonic distortion (THD) is defined as

where

is the total RMS value of the grid-side current and

is the RMS value of the grid current first harmonic.

The rectifier performance is mapped over the complete modulation index

M and converter-side power factor angle

operating region, both at 50% and 100% of the nominal apparent power (i.e.,

). The results are shown in

Figure 19, where the THD performance obtained with and without

saturation are compared. As expected from

Figure 14, the quality of the grid-side current improves at higher load levels, as the zero-crossing distortion is reduced. Moreover, by enforcing the zero-sequence voltage saturation, the THD lies below the conventional 5% limit (i.e., required by grid standards [

44]) for all operating points, which is not the case when

is disabled. Finally, it is observed that the THD values are not symmetrical with respect to

, resulting in worse distortion for

(i.e., capacitive operation). The main explanation resides in the fact that the zero-sequence voltage saturation modifies the current ripple shape and amplitude, leading to a wider DCM operation around the zero-crossings for negative values of

.

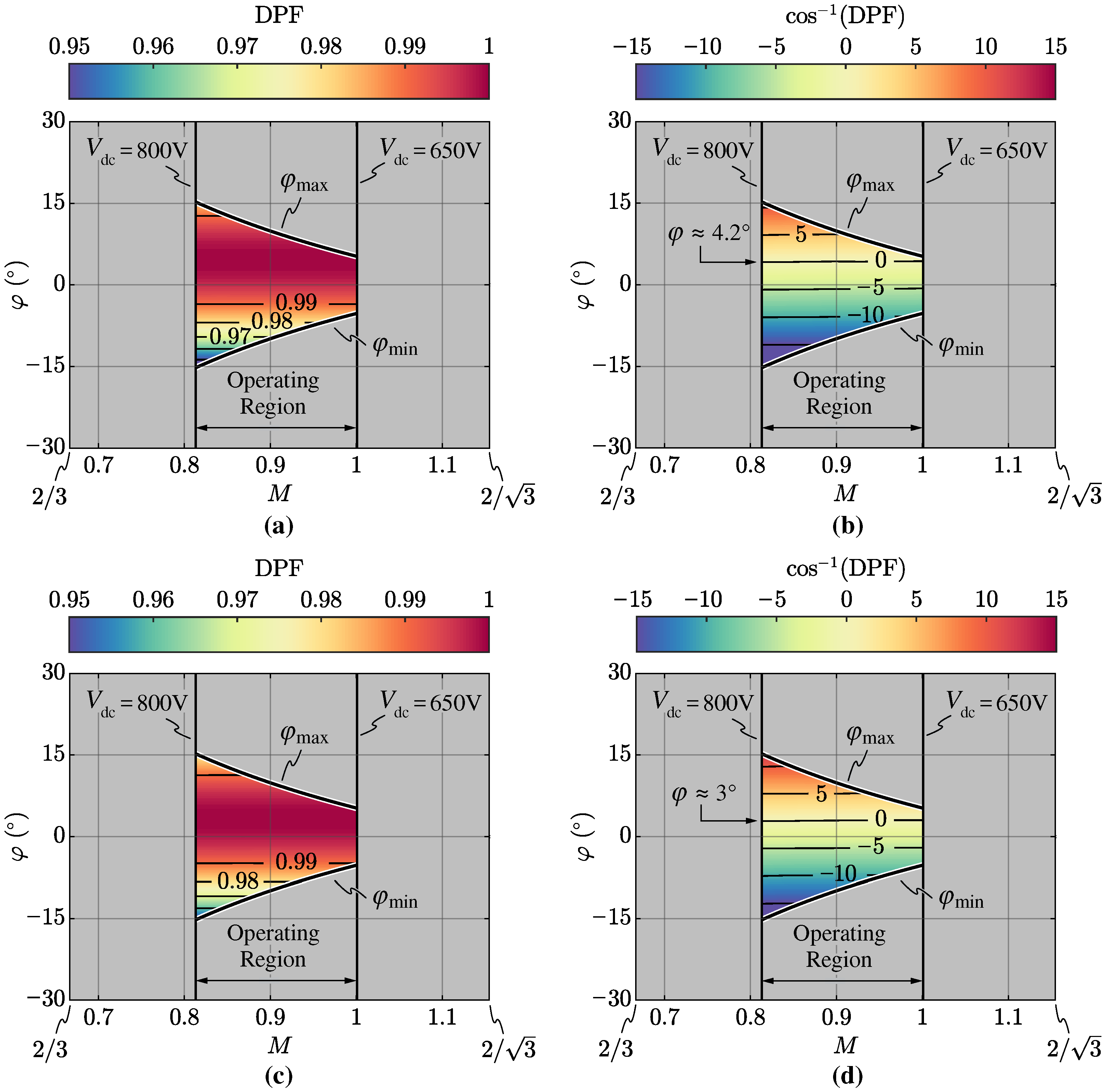

3.2.2. Displacement Power Factor (DPF)

The displacement power factor (DPF) of the rectifier is defined as

where

and

are the phase angles of the grid voltage vector (i.e., measured at the PCC) and the grid current vector, respectively. It is worth noting that

, as the grid-side converter current also includes the filter capacitor current contribution. The experimental DPF is illustrated in

Figure 20a,c for 50% and 100% of the nominal apparent power (i.e.,

). In both cases, the zero-sequence voltage saturation is enabled.

For a better understanding of the phase-shift between

and

, the DPF angle (i.e.,

) is shown in

Figure 20b,d, where a positive value indicates a lagging power factor (i.e., inductive behavior) and a negative value indicates a leading power factor (i.e., capacitive behavior). It can be observed that the current flowing into the filter capacitor

is completely compensated for

at 50% of the rated power and

at 100% of the rated power, as expected from basic theoretical considerations.

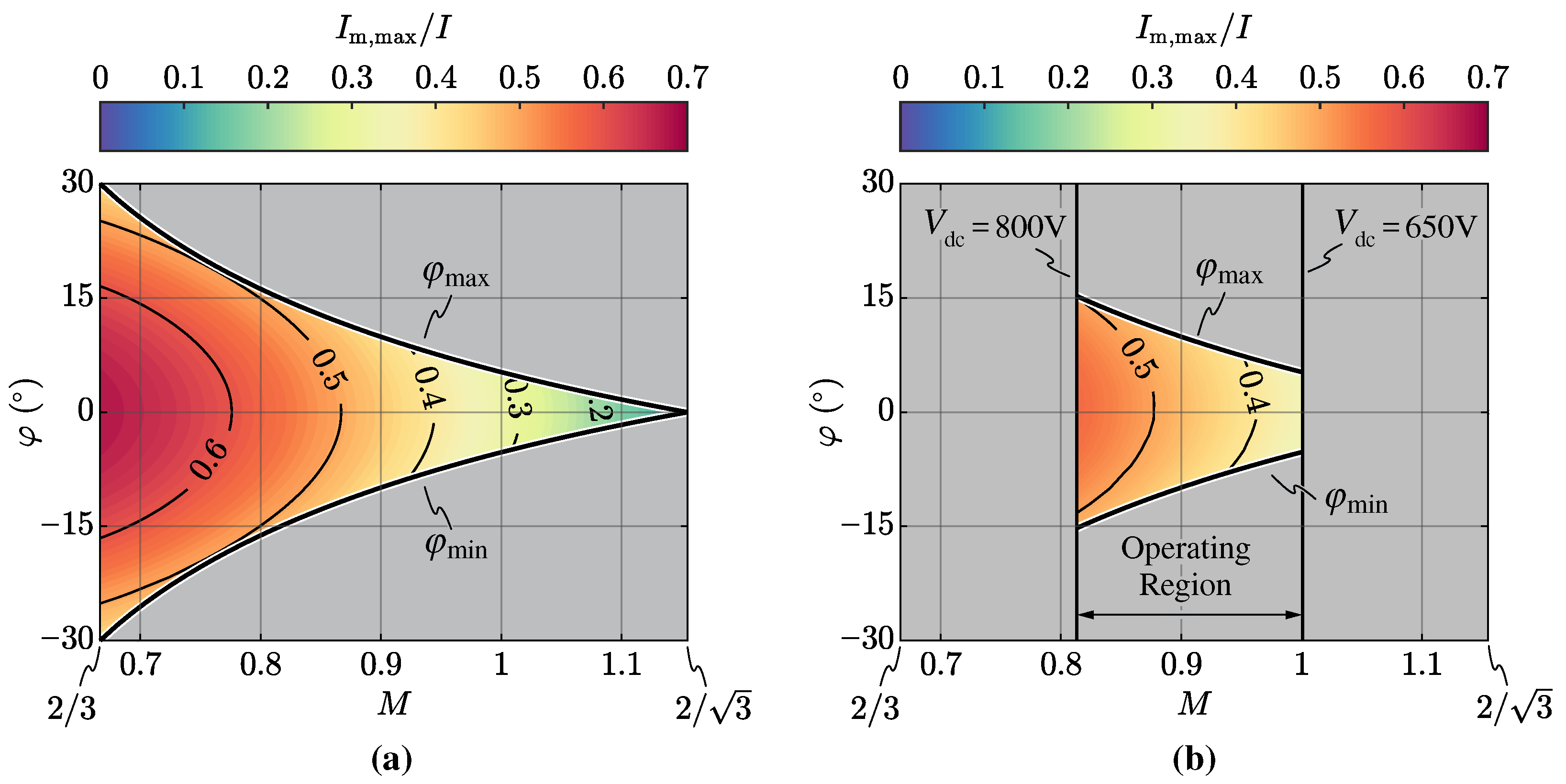

3.2.3. Maximum Mid-Point Current ()

The maximum DC-link mid-point current capability of the rectifier (

) is assessed experimentally by operating the converter at 50% of the rated apparent power (i.e.,

) and injecting a zero-sequence voltage equal to

. The results are illustrated in

Figure 8b in

Section 2.5, where they are normalized with respect to the converter-side peak current value

I. It is observed that the theoretical and the experimental results are in close agreement, achieving a maximum deviation of 5% over the complete operating range of the rectifier. Therefore, the analytical

formulas derived in

Appendix A can be considered successfully verified.

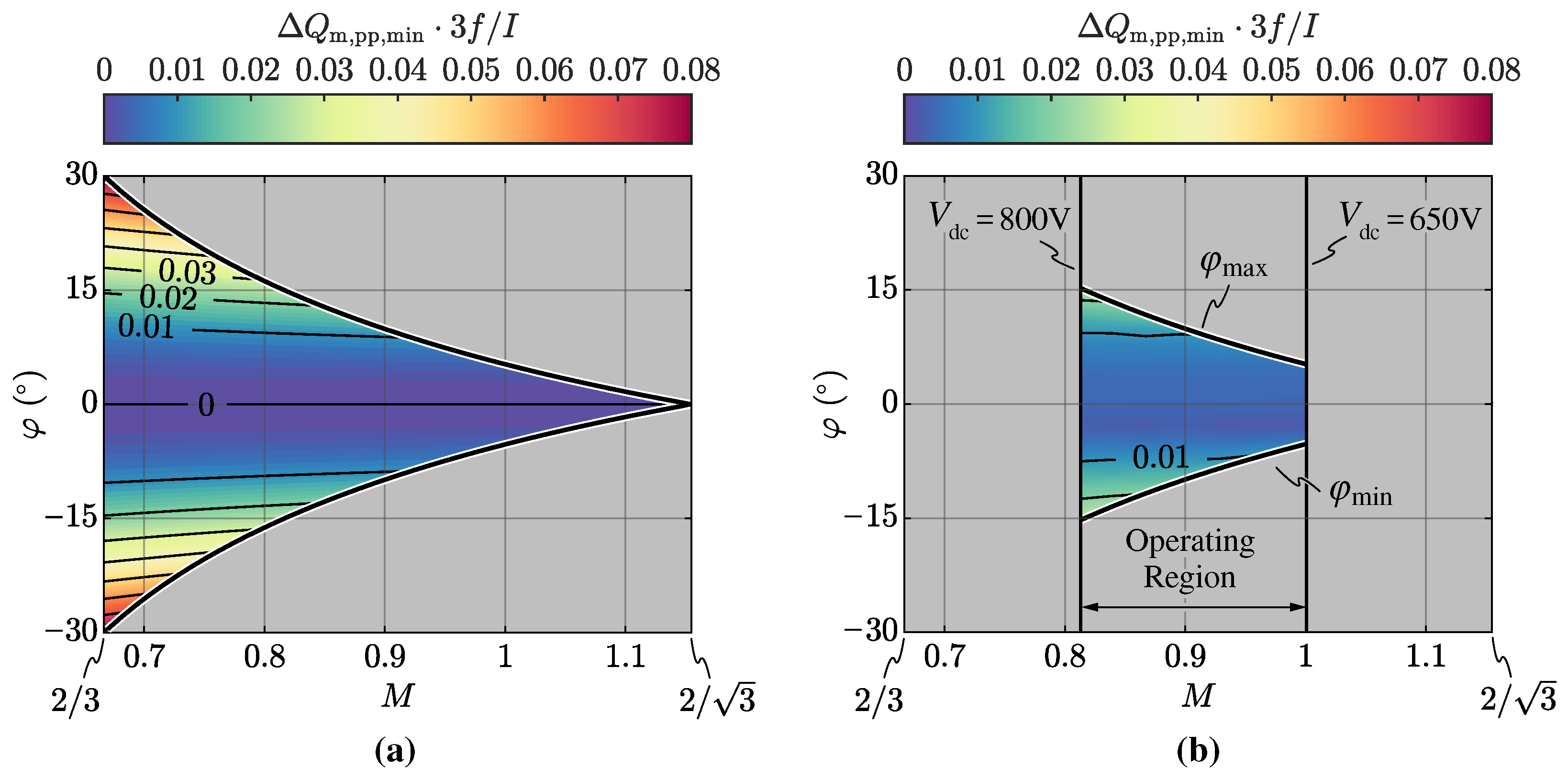

3.2.4. Minimum Mid-Point Charge Ripple ()

The minimum DC-link mid-point peak-to-peak charge ripple

is assessed experimentally by operating the converter at 100% of the rated apparent power (i.e.,

), injecting the zero-sequence voltage component

defined by ZMPCPWM and saturating it according to the

limits. In particular, the mid-point charge is obtained in post-processing as the integral of the measured mid-point current

. The results are illustrated in

Figure 10b in

Section 2.6, where they are normalized with respect to the converter-side peak phase current

I and three-times the grid frequency

. Additionally in this case, the theoretical and the experimental results are in close agreement; however, the value

obtained experimentally does not reach 0 for

. This is mainly due to the converter-side current not being perfectly sinusoidal, as it features a slight zero-crossing distortion that yields a non-zero mid-point current local average (see

Figure 15). Nevertheless,

can never be achieved in practice, as the switching-frequency mid-point current ripple (i.e., neglected in the theoretical model) yields a non-zero charge ripple: theoretical and experimental results at

would only coincide for

. Overall, the analytical

formula derived in

Appendix B can be considered successfully verified, achieving best estimation accuracy for systems with

(i.e., with high pulse ratios).

4. Conclusions

This paper has presented a comprehensive analysis and performance assessment of three-phase three-level unidirectional rectifiers under non-unity power factor operation and unbalanced split DC-link loading.

The complete analysis applies to all three-level unidirectional rectifiers and thus features a wide range of applications, e.g., active front ends for the supply of variable-speed drives, uninterruptible power supply systems, battery chargers, data centers and high-power DC loads. In particular, the ability to operate under non-unity power factor is becoming a desired feature of modern rectifiers, as distribution system operators worldwide are starting to charge end consumers for the excess reactive energy injected/withdrawn into/from the grid. In this scenario, properly controlled unidirectional rectifiers could support the reactive energy flows and potentially substitute traditional power factor correction capacitor banks, without requiring new or additional hardware. Furthermore, the ability to operate under unbalanced split DC-link loading is necessary when separate loads are connected to the rectifier DC-link halves, which is typically the case for modular high-power converters (e.g., the DC/DC stage of electric vehicle DC fast chargers).

Therefore, this paper has focused on analyzing, improving and extending the operation of three-phase three-level unidirectional rectifiers. First, the operational basics of three-level rectifiers have been recalled and the theoretical operating limits of the converter in terms of zero-sequence voltage, modulation index, power factor angle, DC-link mid-point current and minimum DC-link mid-point charge ripple have been derived. A unified carrier-based pulse-width modulation (PWM) approach aiming for the undistorted operation of the rectifier across all feasible operating conditions has been proposed, de facto enabling the converter operation under non-unity power factor and unbalanced split-DC-link loading. This approach, uniquely based on restraining (i.e., saturating) the zero-sequence voltage within its feasible limits, has been described in detail and its effects on the DC-link mid-point current generation have been investigated. Furthermore, novel analytical expressions have been derived in the Appendix, defining the rectifier maximum mid-point current capability (i.e., directly linked to the converter DC-link load unbalance) and the minimum peak-to-peak DC-link mid-point charge ripple (i.e., allowing for the straightforward sizing of the DC-link capacitance value) over the complete converter operating region. Finally, the theoretical analysis has been successfully verified on a digitally controlled 30 T-type rectifier prototype operating at 20 . The input phase current total harmonic distortion (THD), the maximum mid-point current capability and the minimum mid-point peak-to-peak charge ripple have been experimentally assessed across all rectifier operating points, demonstrating excellent performance and a high-level of agreement with the analytical predictions.