PWM Strategy to Alleviate Common-Mode Voltage with Minimized Output Harmonic Distortion for Five-Level Cascaded H-Bridge Converters

Abstract

:1. Introduction

- (1)

- A PWM strategy featuring reduced CMV magnitudes, zero average CMV, and minimum output harmonic distortion is extended from a three-level NPC [33] to a five-level CHB converter;

- (2)

- A carrier-rotation technique [7] is combined with the proposed scheme for even power loss distribution in a five-level CHB converter, thereby enhancing the efficiency and reliability over the long term compared to a five-level NPC one;

- (3)

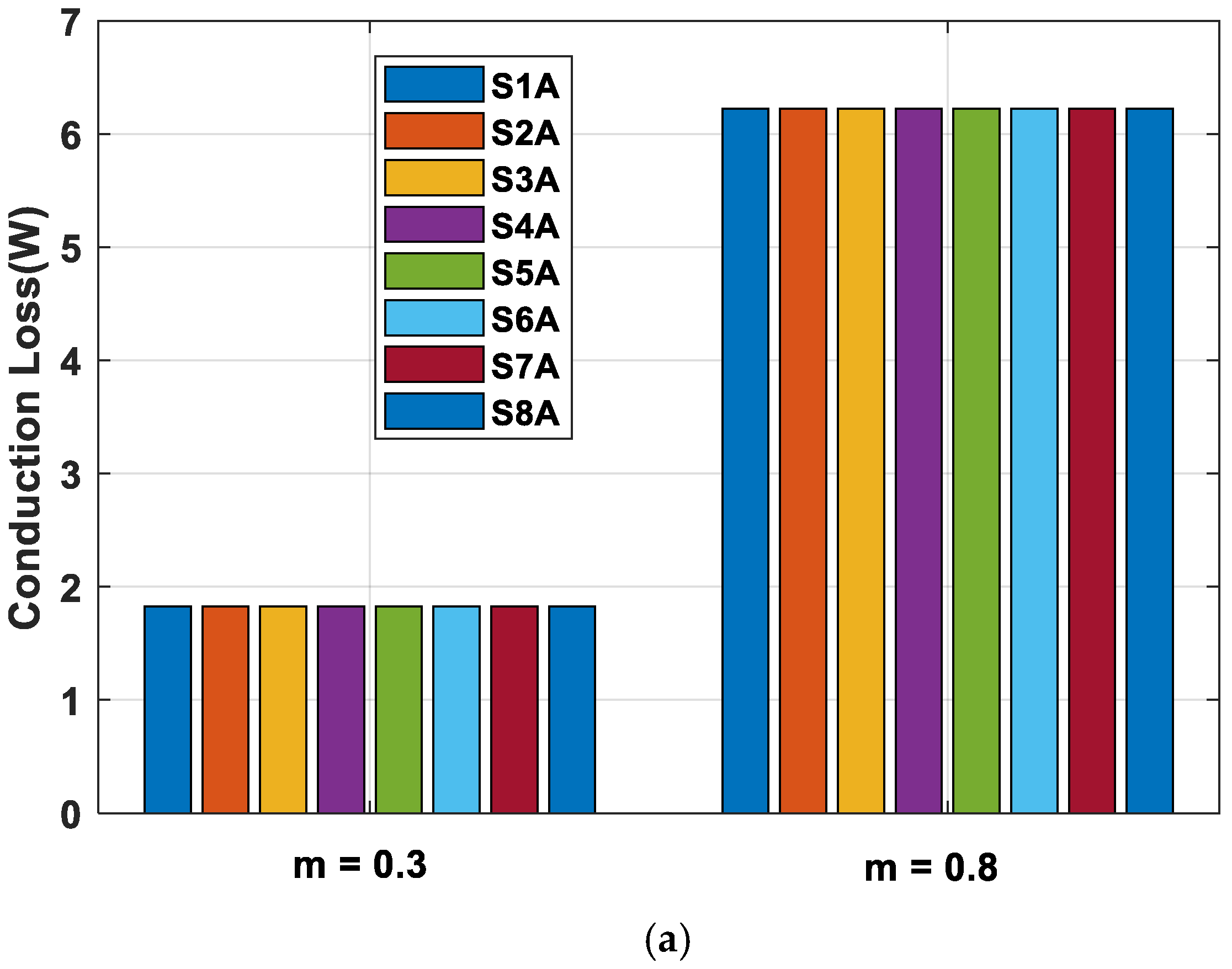

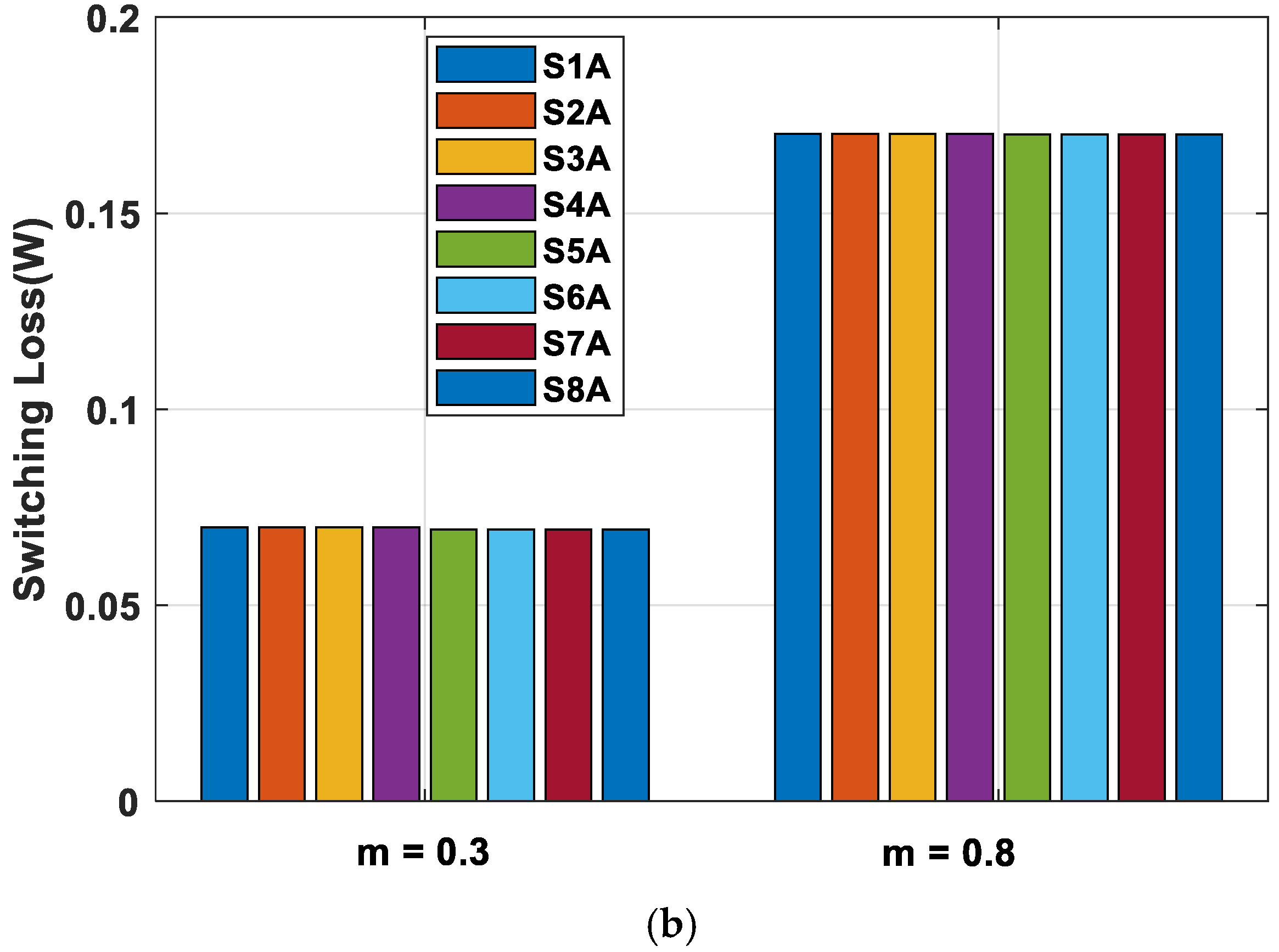

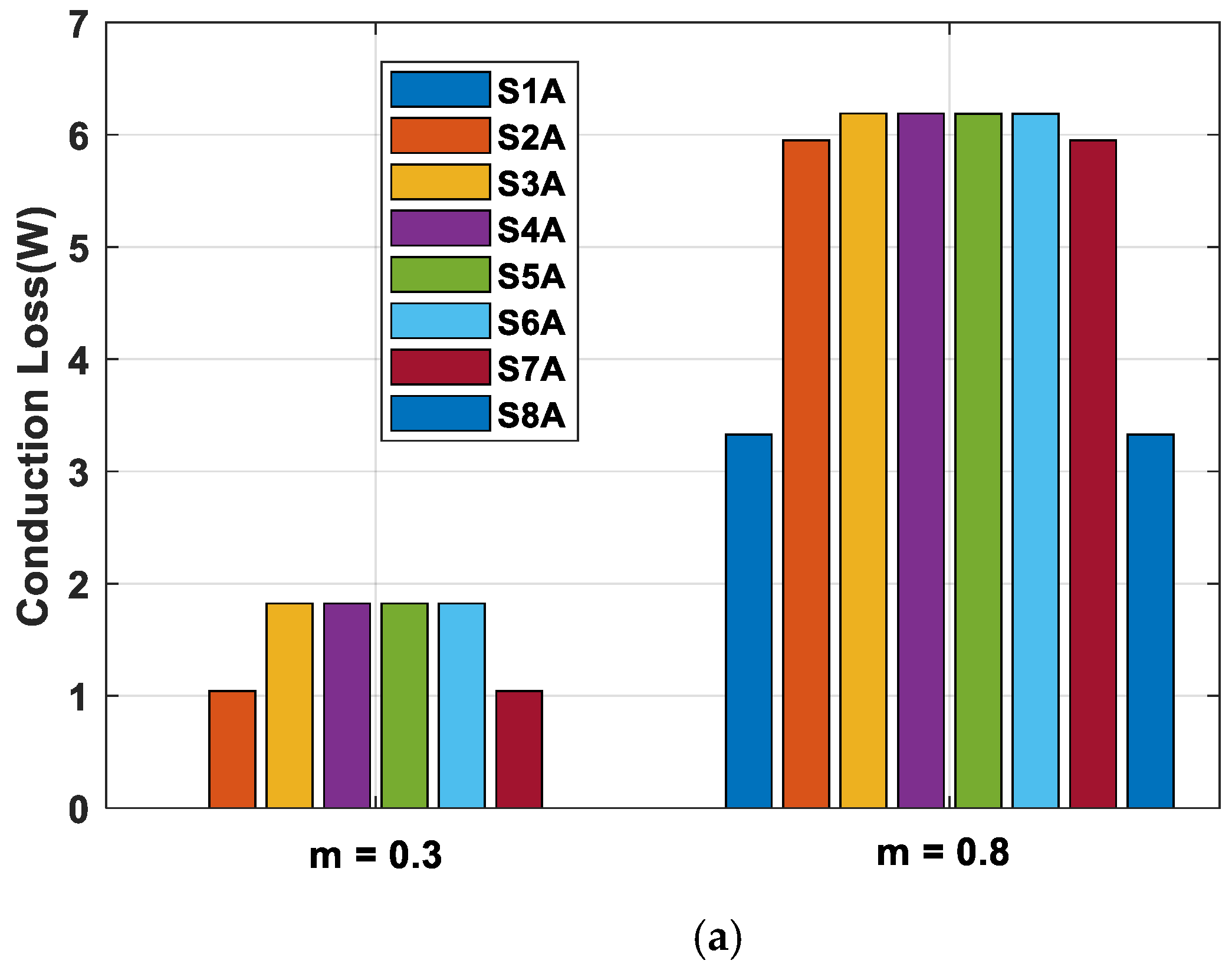

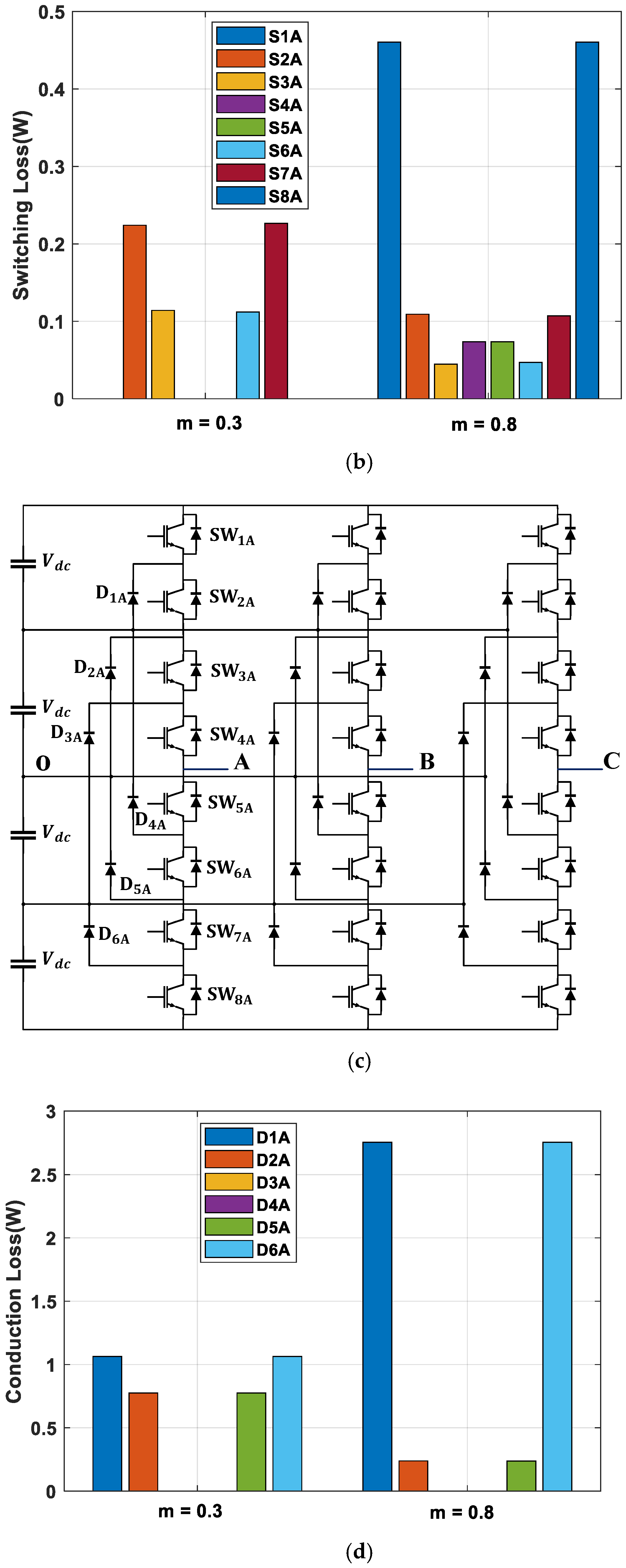

- A power loss analysis conducted in a PLECS thermal module is presented to confirm the even distribution of power loss, and to establish the condition of equivalent switching loss power under which the harmonic distortion of different PWM strategies is fairly compared against one another;

- (4)

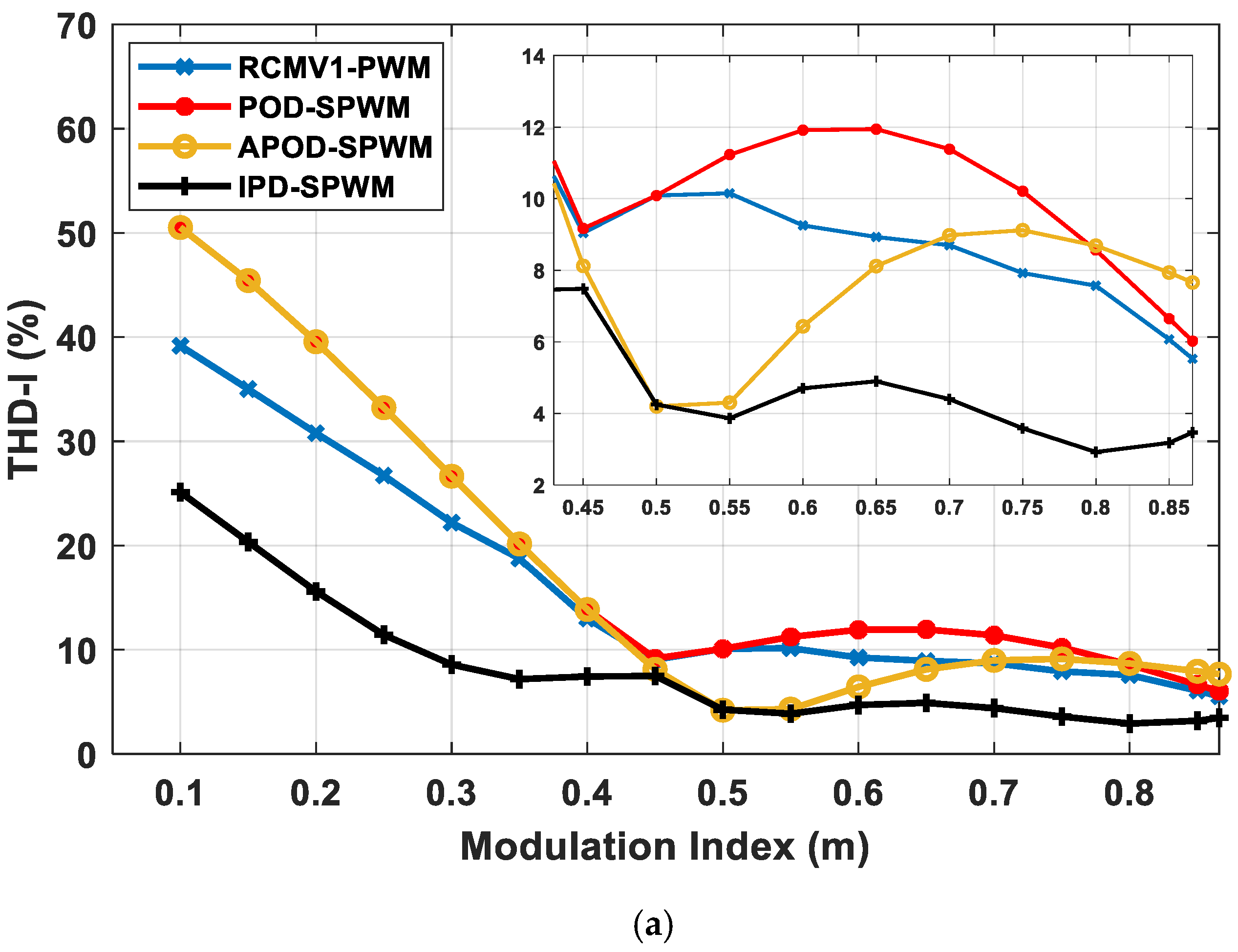

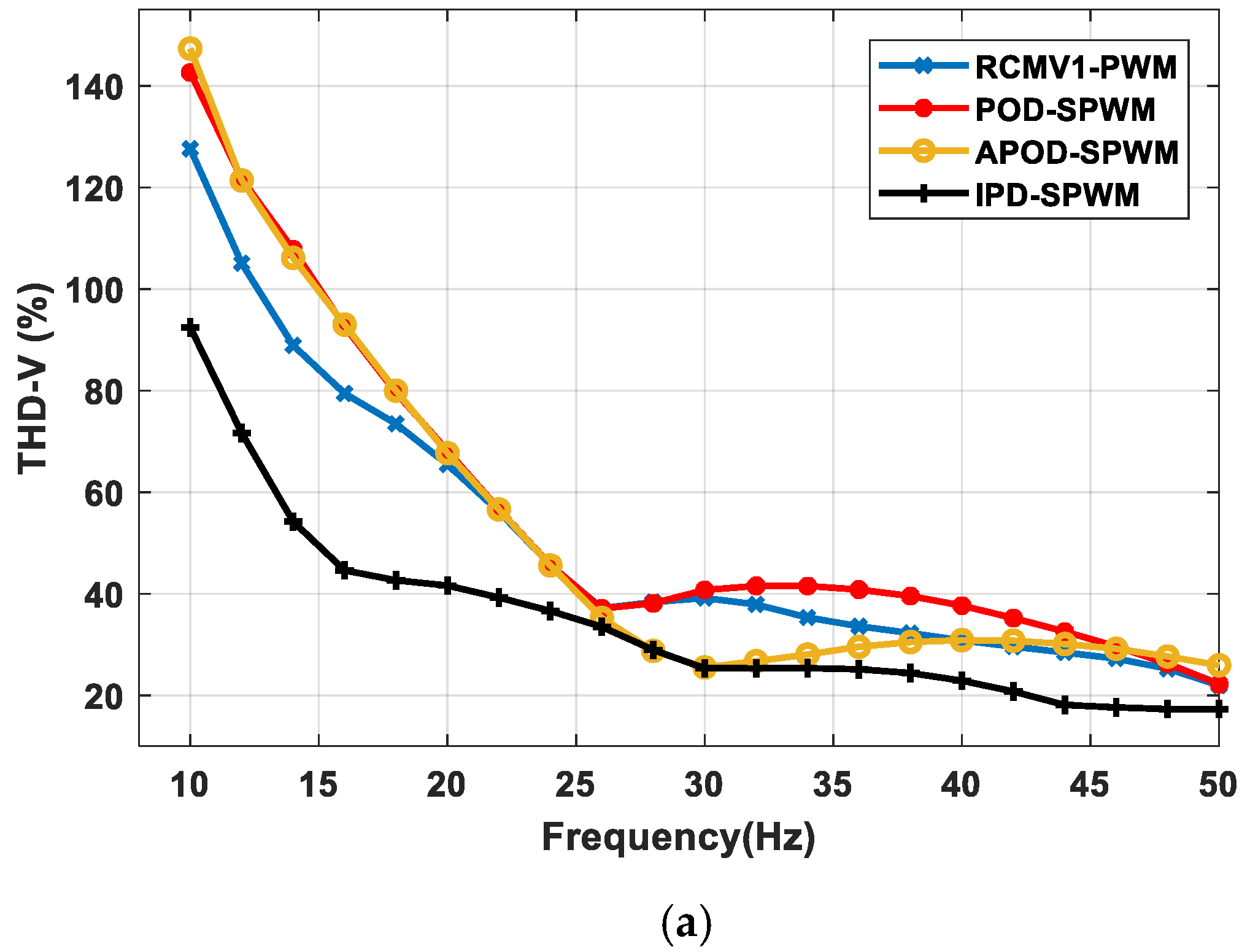

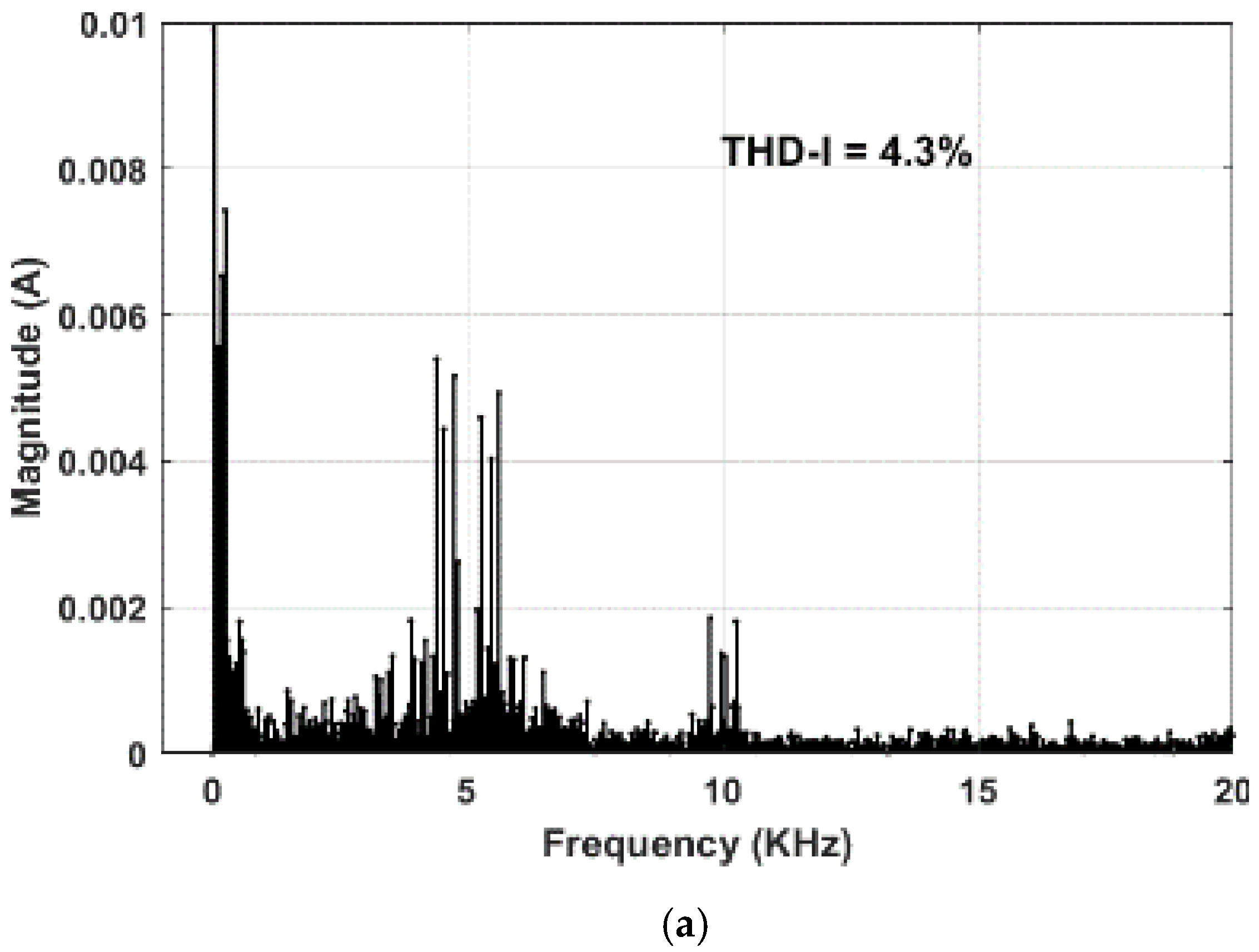

- A detailed comparative analysis of output harmonic distortion on the basis of comparable switching loss power is conducted in both simulation and experiment for the proposed strategy, POD-SPWM, APOD-SPWM, and IPD-SPWM.

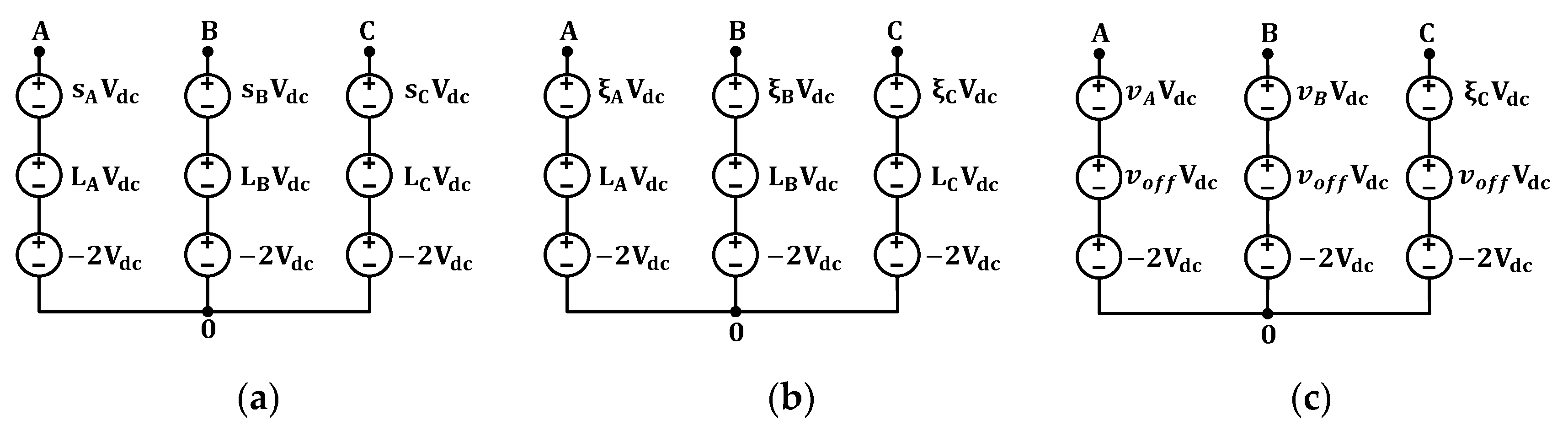

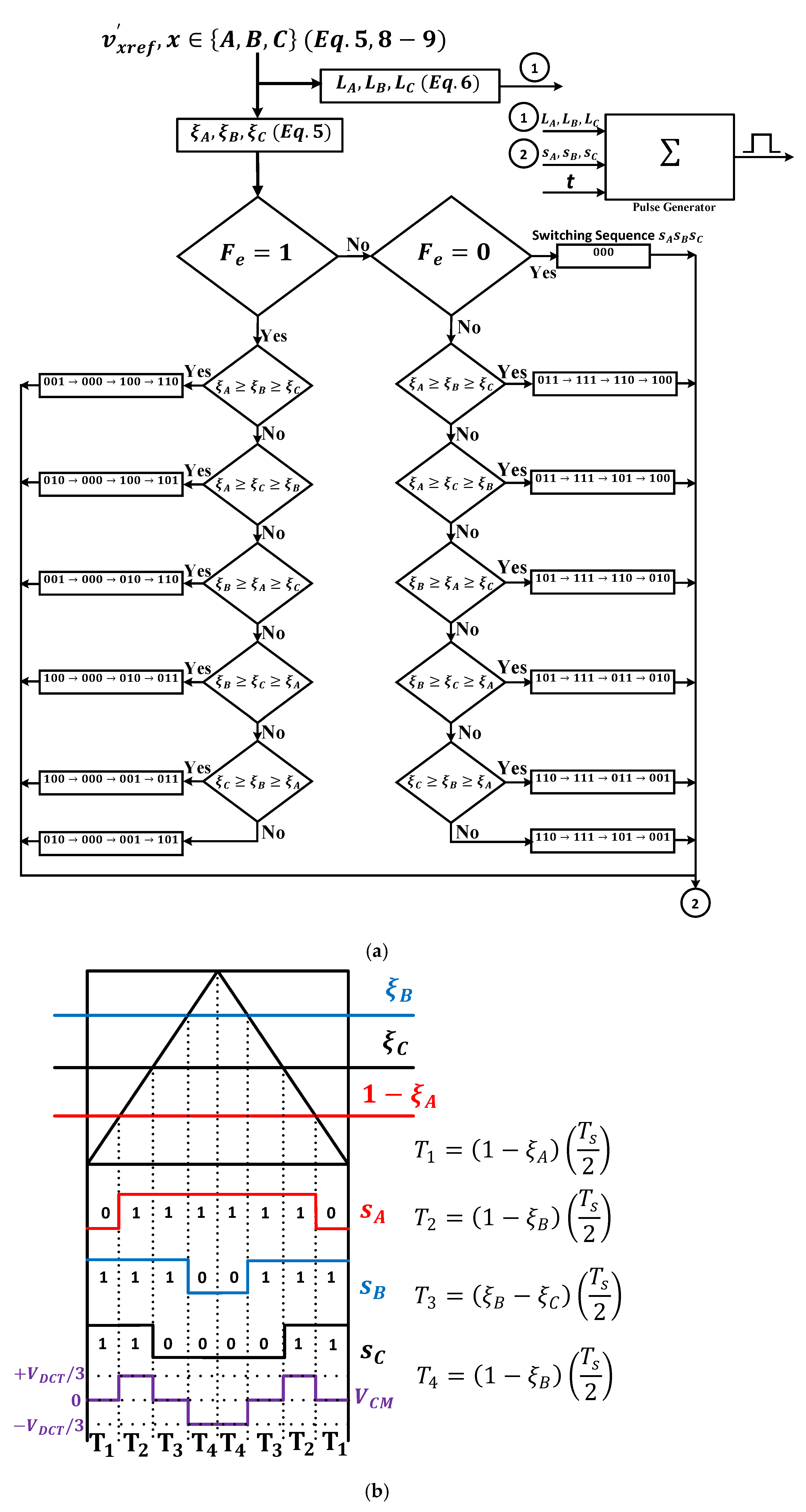

2. PWM Strategy to Alleviate CMV with Improved Output Harmonic Distortion and Equal Loss Distribution

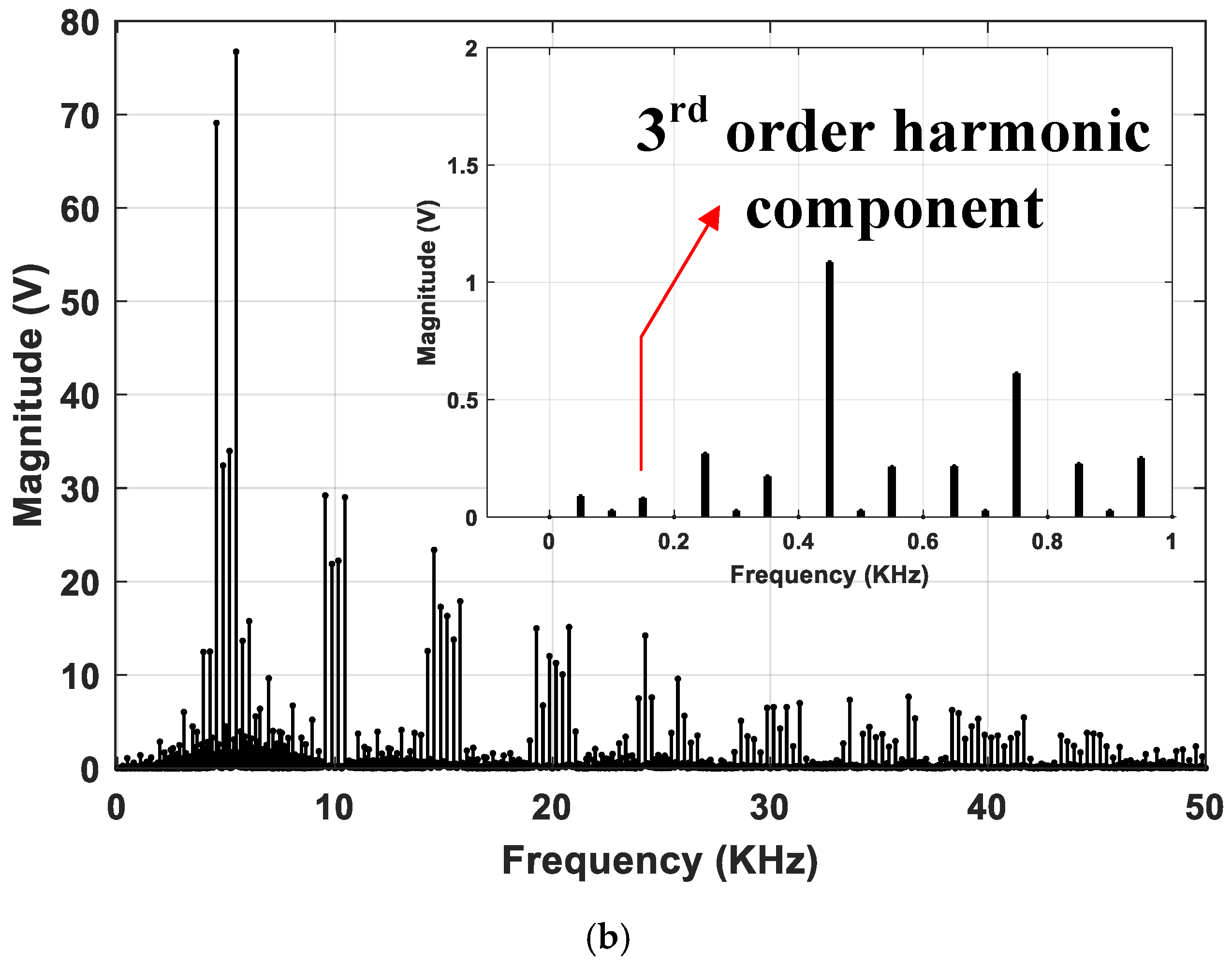

2.1. With CMV Alleviation and Improved Output Harmonic Distortion

2.2. With Equal Loss Distribution

3. Performance Criteria for Evaluation

3.1. Power Loss

3.2. Harmonic Distortion

4. Simulation Results

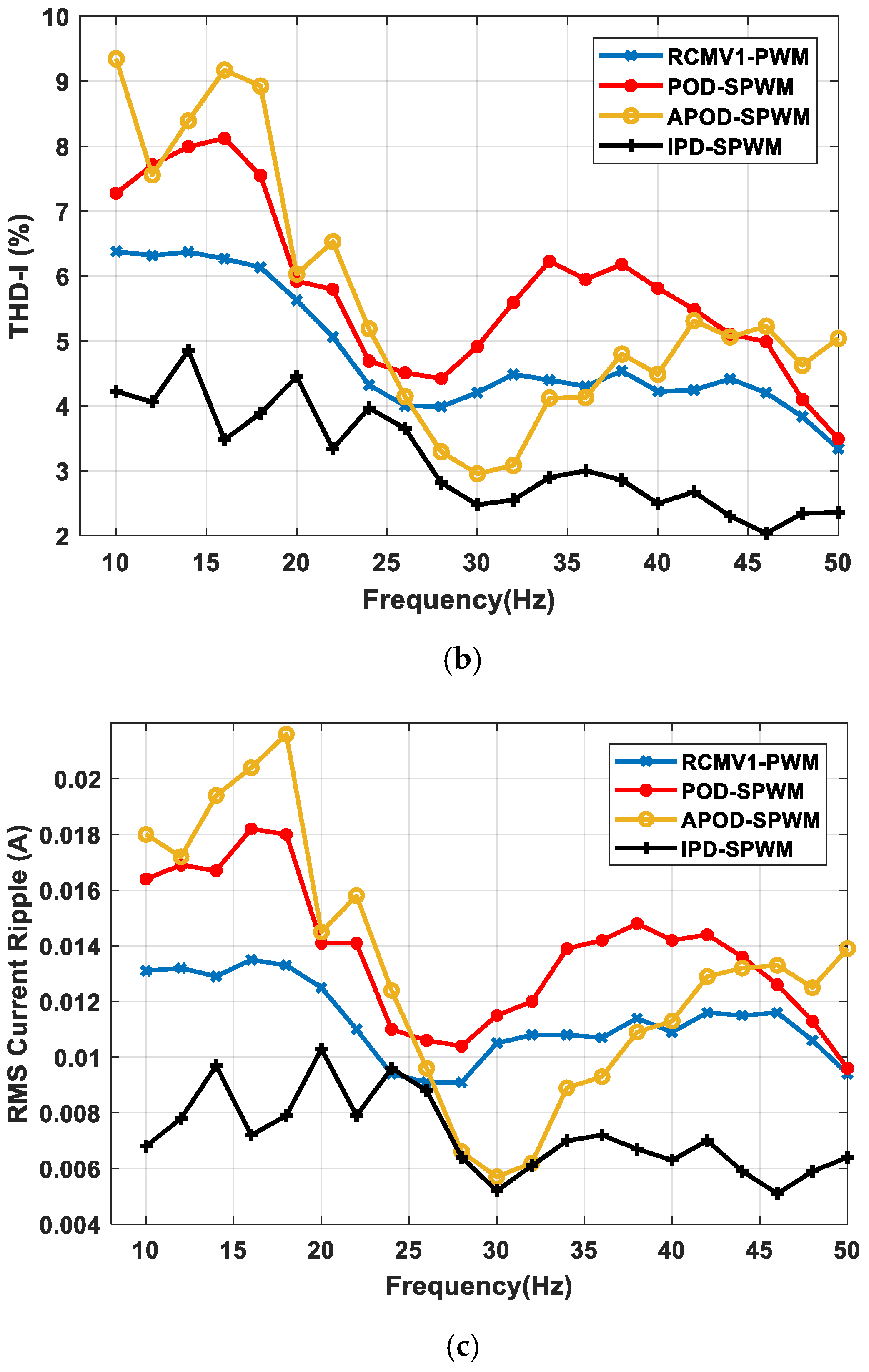

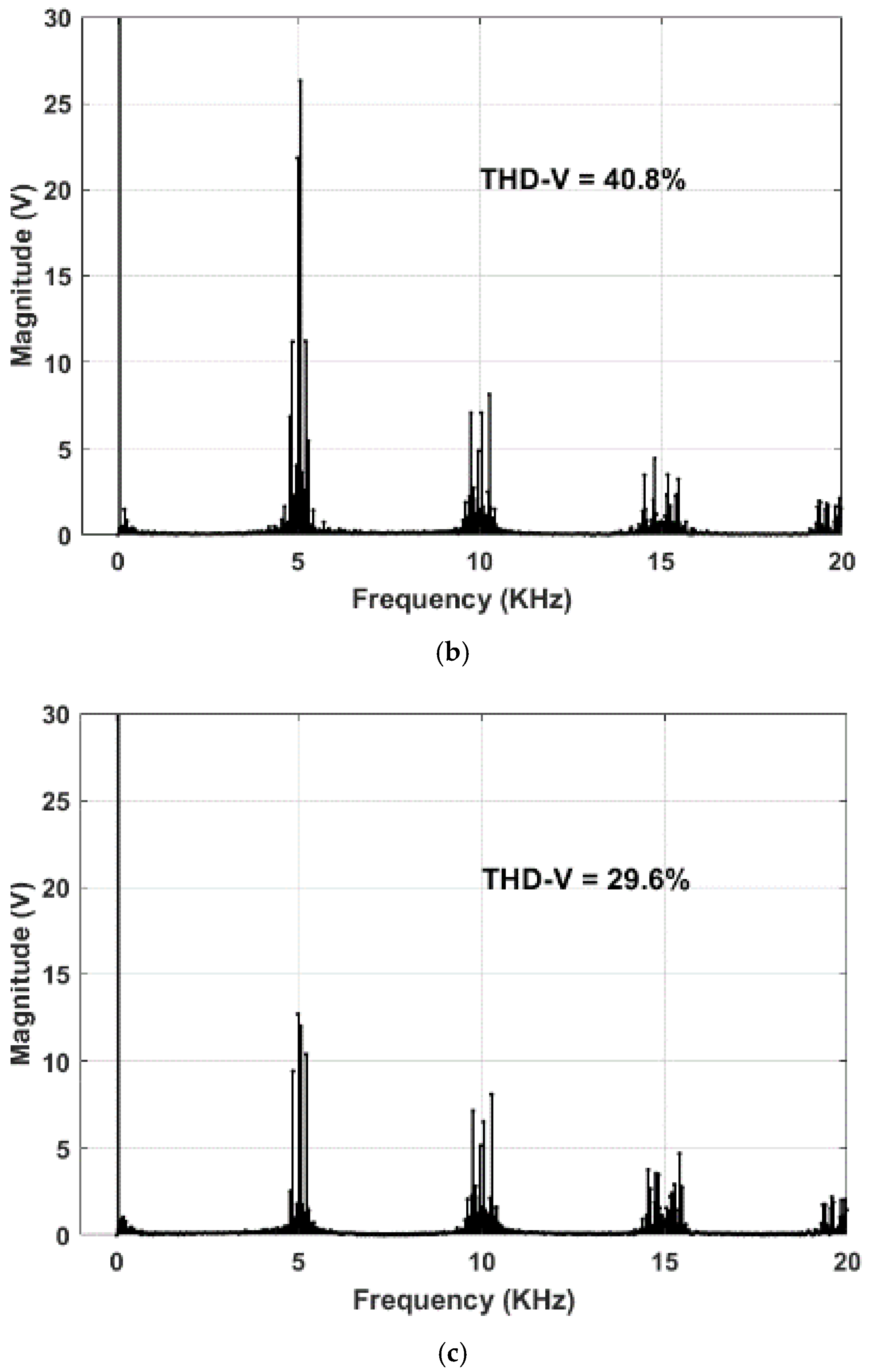

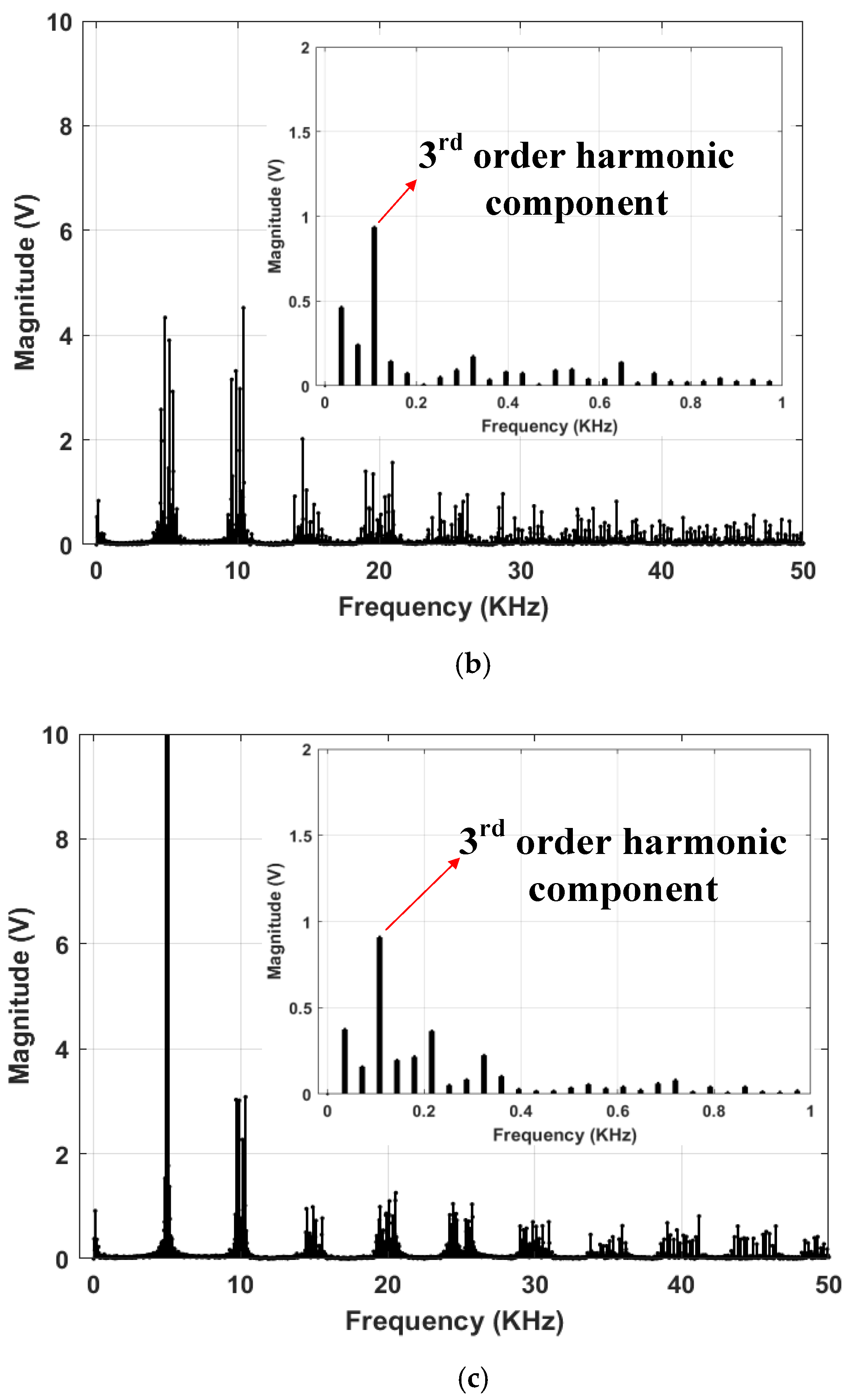

4.1. Harmonic Distortion Evaluation

4.2. Power Loss Comparison

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Wu, B.; Narimani, M. Cascaded H-Bridge Multilevel Inverters. In High-Power Converters and ac Drives; Wiley: Hoboken, NJ, USA, 2016; pp. 119–141. [Google Scholar]

- Elsanabary, A.I.; Konstantinou, G.; Mekhilef, S.; Townsend, C.D.; Seyedmahmoudian, M.; Stojcevski, A. Medium Voltage Large-Scale Grid-Connected Photovoltaic Systems Using Cascaded H-Bridge and Modular Multilevel Converters: A Review. IEEE Access 2020, 8, 223686–223699. [Google Scholar] [CrossRef]

- Jing, T.; Maklakov, A.S. A Review of Voltage Source Converters for Energy Applications. In Proceedings of the Ural Conference on Green Energy (UralCon) 2018 International, Chelyabinsk, Russia, 4–6 October 2018; pp. 275–281. [Google Scholar]

- Jiang, W.; Ren, K.; Xue, S.; Yang, C.; Xu, Z. Research on the Asymmetrical Multilevel Hybrid Energy Storage System Based on Hybrid Carrier Modulation. IEEE Trans. Ind. Electron. 2021, 68, 1241–1251. [Google Scholar] [CrossRef]

- Vasu, R.; Chattopadhyay, S.K.; Chakraborty, C. Asymmetric Cascaded H-Bridge Multilevel Inverter with Single DC Source per Phase. IEEE Trans. Ind. Electron. 2019, 67, 5398–5409. [Google Scholar] [CrossRef]

- Rajesh, V.; Chattopadhyay, S.K.; Chakraborty, C. Self-Balancing Trinary Asymmetric Three-Phase Multilevel Inverter. In Proceedings of the IECON 2018—44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018; pp. 4480–4485. [Google Scholar]

- Sreenivasarao, D.; Agarwal, P.; Das, B. Performance evaluation of carrier rotation strategy in level-shifted pulse-width modulation technique. IET Power Electron. 2014, 7, 667–680. [Google Scholar] [CrossRef]

- Gupta, K.K.; Bhatnagar, P.; Vahedi, H.; Al-Haddad, K. Carrier based PWM for even power distribution in cascaded H-bridge multilevel inverters within single power cycle. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 6470–6475. [Google Scholar]

- Ye, M.; Ren, W.; Le Chen, C.; Wei, Q.; Song, G.; Li, S. Research on Power-Balance Control Strategy of CHB Multilevel Inverter Based on TPWM. IEEE Access 2019, 7, 157226–157240. [Google Scholar] [CrossRef]

- Ye, M.; Zhang, J.; Chen, L.; Kang, L.; Wu, H.; Li, S.; Le Chen, C. Modified Modulation Strategy with Balanced Power and Switching Losses Distributed for Seven-Level Cascaded H-Bridge Inverters. IEEE Access 2019, 7, 134036–134046. [Google Scholar] [CrossRef]

- Bruckner, T.; Bernet, S.; Guldner, H. The Active NPC Converter and Its Loss-Balancing Control. IEEE Trans. Ind. Electron. 2005, 52, 855–868. [Google Scholar] [CrossRef]

- Kui, W.; Zedong, Z.; Lie, X.; Yongdong, L. Neutral-Point Voltage Balancing Method for Five-Level NPC Inverters Based on Carri-er-Overlapped PWM. IEEE Trans. Power Electron. 2021, 36, 1428–1440. [Google Scholar]

- Kui, W.; Zedong, Z.; Lie, X.; Yongdong, L. A Generalized Carrier-Overlapped PWM Method for Neutral-Point-Clamped Multi-level Converters. IEEE Trans. Power Electron. 2020, 35, 9095–9106. [Google Scholar]

- Fan, F.; See, K.Y.; Banda, J.K.; Liu, X.; Gupta, A.K. Investigation and mitigation of premature bearing degradation in motor drive system. IEEE Electromagn. Compat. Mag. 2019, 8, 75–81. [Google Scholar] [CrossRef]

- Wu, B.; Narimani, M. Transformerless MV Drives. In High-Power Converters and ac Drives; Wiley: Hoboken, NJ, USA, 2016; pp. 417–445. [Google Scholar]

- Kai, T.; Jiacheng, W.; Bin, W.; Dawei, X.; Zhongyuan, C.; Navid, R.Z. A virtual space vector modulation technique for the reduction com-mon-mode voltages in both magnitude and third-order component. IEEE Trans. Electron. 2016, 31, 839–848. [Google Scholar]

- Pengkang, X.; Jiazheng, L.; Henglin, C. Influence of motor cable on common-mode currents in an inverter-fed motor drive sys-tem. Front. Inf. Technol. Electron. Eng. 2018, 19, 273–284. [Google Scholar]

- Kumar, M.; Jayaraman, K. Common Mode Impedance Shaping Choke to Attenuate the Conducted EMI in Three Phase Drive. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020; pp. 1–5. [Google Scholar]

- Akagi, H.; Tamura, S. A Passive EMI Filter for Eliminating Both Bearing Current and Ground Leakage Current from an Inverter-Driven Motor. IEEE Trans. Power Electron. 2006, 27, 1152–1158. [Google Scholar] [CrossRef]

- Zhu, N.; Kang, J.; Xu, D.; Wu, B.; Xiao, Y. An Integrated AC Choke Design for Common-Mode Current Suppression in Neutral-Connected Power Converter Systems. IEEE Trans. Power Electron. 2011, 27, 1228–1236. [Google Scholar] [CrossRef]

- Wu, B.; Narimani, M. Two-Level Voltage Source Inverter. In High-Power Converters and ac Drives; Wiley: Hoboken, NJ, USA, 2016; pp. 93–117. [Google Scholar]

- Nguyen, N.-V.; Nguyen, T.-K.T.; Lee, H.-H. A Reduced Switching Loss PWM Strategy to Eliminate Com-mon Mode Voltage in Multilevel Inverters. IEEE Trans. Power Electron. 2015, 30, 5425–5438. [Google Scholar] [CrossRef]

- Nguyen, T.-K.T.; Nguyen, N.-V.; Prasad, N.R. Eliminated Common-Mode Voltage Pulsewidth Modu-lation to Reduce Output Current Ripple for Multilevel Inverters. IEEE Trans. Power Electron. 2016, 31, 5952–5966. [Google Scholar] [CrossRef]

- Nguyen, T.-K.T.; Nguyen, N.-V.; Prasad, N.R. Novel Eliminated Common-Mode Voltage PWM Sequences and an Online Al-gorithm to Reduce Current Ripple for a Three-Level Inverter. IEEE Trans. Power Electron. 2017, 32, 7482–7493. [Google Scholar] [CrossRef]

- Nguyen, T.-K.T.; Nguyen, N.-V. An Efficient Four-State Zero Common-Mode Voltage PWM Scheme with Reduced Current Distortion for a Three-Level Inverter. IEEE Trans. Ind. Electron. 2018, 65, 1021–1030. [Google Scholar] [CrossRef]

- Pham, K.D.; Nguyen, N.V. Pulse-Width Modulation Strategy for Common Mode Voltage Elimination with Reduced Common Mode Voltage Spikes in Multilevel Inverters with Extension to Over-Modulation Mode. J. Power Electron. 2019, 19, 727–743. [Google Scholar]

- Tsai, M.-J.; Chen, H.-C.; Tsai, M.-R.; Wang, Y.B.; Cheng, P.-T. Evaluation of Carrier-Based Modulation Techniques with Com-mon-Mode Voltage Reduction for Neutral Point Clamped Converter. IEEE Trans. Power Electron. 2018, 33, 3268–3275. [Google Scholar] [CrossRef]

- Cacciato, M.; Consoli, A.; Scarcella, G.; Testa, A. Reduction of common mode currents in PWM inverter motor drives. IEEE Trans. Ind. Appl. 2002, 35, 469–476. [Google Scholar] [CrossRef]

- Ali, S.M.; Reddy, V.V.; Kalavathi, M.S.; Ali, S.M. Simplified active zero state PWM algorithms for vector controlled induction motor drives for reduced common mode voltage. In Proceedings of the International Conference on Recent Advances and Innovations in Engineering (ICRAIE-2014), Jaipur, India, 9–11 May 2014; pp. 1–7. [Google Scholar]

- Un, E.; Hava, A.M. A Near-State PWM Method with Reduced Switching Losses and Reduced Common-Mode Voltage for Three-Phase Voltage Source Inverters. IEEE Trans. Ind. Appl. 2009, 45, 782–793. [Google Scholar] [CrossRef]

- Vazquez, G.; Hernandez-Avila, I.; Sosa, J.; Limones-Pozos, C.A.; Arau, J. A Comparative Analysis of Space-Vector PWM Techniques for Transformerless Three-Phase Voltage Source Inverters. In Proceedings of the 2018 14th International Conference on Power Electronics (CIEP), Cholula, Puebla, Mexico, 24–26 October 2018; pp. 183–187. [Google Scholar]

- Renge, M.M.; Suryawanshi, H.M. Multilevel Inverter to Reduce Common Mode Voltage in AC Motor Drives Using SPWM Technique. J. Power Electron. 2011, 11, 21–27. [Google Scholar] [CrossRef] [Green Version]

- Pham, K.D.; Nguyen, N.V. A Reduced Common-Mode-Voltage Pulsewidth Modulation Method with Output Harmon-ic Distortion Minimization for Three-Level Neutral-Point-Clamped Inverters. IEEE Trans. Power Electron. 2020, 35, 6944–6962. [Google Scholar] [CrossRef]

- PLECS. Available online: https://www.plexim.com/download (accessed on 28 June 2021).

- PLECS. Available online: https://www.plexim.com/sites/default/files/plecsmanual.pdf (accessed on 28 June 2021).

- Infineon. Available online: https://www.infineon.com/cms/en/product/power/igbt/igbt-discretes/ikw15n120h3/#!simulation (accessed on 28 June 2021).

- Infineon. Available online: https://www.infineon.com/cms/en/product/power/diodes-thyristors/silicon-diodes/idp30e120/ (accessed on 28 June 2021).

| sx + Lx | ||||

|---|---|---|---|---|

| 0 | ||||

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 | ||||

| Parameters | Symbols | Value |

|---|---|---|

| Maximum Collector-Emitter Voltage | Vce-max | 1200 V |

| Maximum Continuous Collector Current at Tj = 25 °C | Ic-max | 30 A |

| Maximum Continuous Collector Current at Tj = 100 °C | Ic-max | 15 A |

| Maximum Junction Temperature | Tj-max | 175 °C |

| Gate Emitter Voltage | VGE | ±20 V |

| Collector-Emitter Saturation Voltage at Tj = 25 °C | VCEsat | 2.05 V |

| Turn-On Delay Time at Tj = 25 °C | td(on) | 21 ns |

| Turn-Off Delay Time at Tj = 25 °C | td(off) | 260 ns |

| Turn-On Energy at Tj = 25 °C | Eon | 1.10 mJ |

| Turn-Off Energy at Tj = 25 °C | Eoff | 0.45 mJ |

| Diode Forward Voltage at Tj = 25 °C, IF = 15 A | VF | 2.4 V |

| Diode Forward Current at Tj = 25 °C | IF | 15 A |

| Diode Reverse Recovery Time at Tj = 25 °C | trr | 260 ns |

| Diode Reverse Recovery Charge at Tj = 25 °C | Qrr | 0.80 μC |

| Diode Peak Reverse Recovery Current at Tj = 25 °C | Irrm | 7.7 A |

| Parameters | Symbols | Value |

|---|---|---|

| Peak Reverse Voltage | VRRM | 1200 V |

| Maximum Continuous Collector Current at Tj = 25 °C | IF-max | 50 A |

| Maximum Continuous Collector Current at Tj = 90 °C | IF-max | 30 A |

| Maximum Junction Temperature | Tj-max | 150 °C |

| Forward Voltage Drop at IF = 30 A, Tj = 25 °C | VF | 1.65 V |

| Reverse Recovery Time at Tj = 25 °C | trr | 243 ns |

| Reverse Recovery Charge at Tj = 25 °C | Qrr | 2630 nC |

| Peak Reverse Recovery Current at Tj = 25 °C | Irrm | 23.7 A |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pham, K.D.; Nguyen, Q.V.; Nguyen, N.-V. PWM Strategy to Alleviate Common-Mode Voltage with Minimized Output Harmonic Distortion for Five-Level Cascaded H-Bridge Converters. Energies 2021, 14, 4476. https://doi.org/10.3390/en14154476

Pham KD, Nguyen QV, Nguyen N-V. PWM Strategy to Alleviate Common-Mode Voltage with Minimized Output Harmonic Distortion for Five-Level Cascaded H-Bridge Converters. Energies. 2021; 14(15):4476. https://doi.org/10.3390/en14154476

Chicago/Turabian StylePham, Khoa Dang, Quan Vinh Nguyen, and Nho-Van Nguyen. 2021. "PWM Strategy to Alleviate Common-Mode Voltage with Minimized Output Harmonic Distortion for Five-Level Cascaded H-Bridge Converters" Energies 14, no. 15: 4476. https://doi.org/10.3390/en14154476

APA StylePham, K. D., Nguyen, Q. V., & Nguyen, N.-V. (2021). PWM Strategy to Alleviate Common-Mode Voltage with Minimized Output Harmonic Distortion for Five-Level Cascaded H-Bridge Converters. Energies, 14(15), 4476. https://doi.org/10.3390/en14154476