Improvement of DC Fault Current Limiting and Interrupting Operation of Hybrid DC Circuit Breaker Using Double Quench

Abstract

:1. Introduction

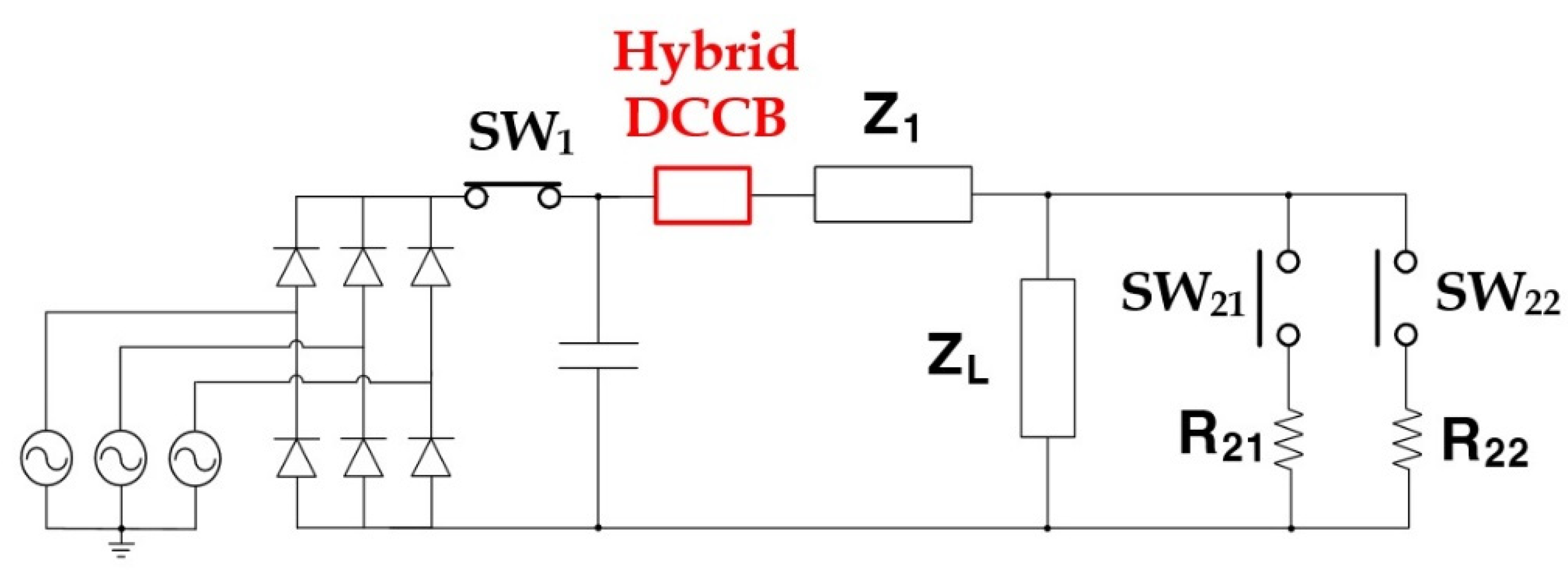

2. Structure and Modeling of Hybrid Direct Current Circuit Breaker (DCCB) Using Double Quench

2.1. Structure of Hybrid Direct Current Circuit Breaker (DCCB) Using Double Quench

2.2. Modeling of Hybrid Direct Current Circuit Breaker (DCCB) Using Double Quench

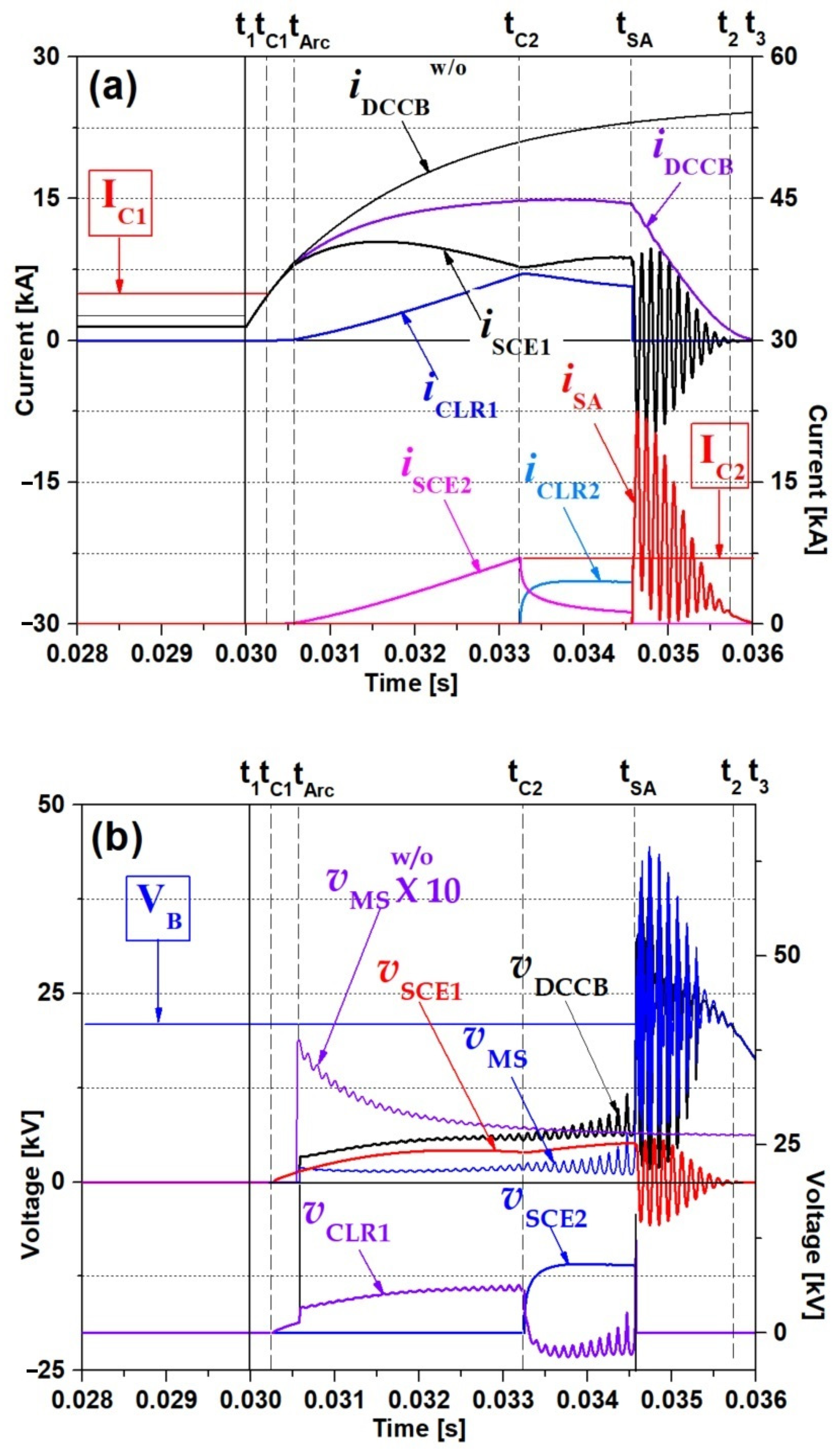

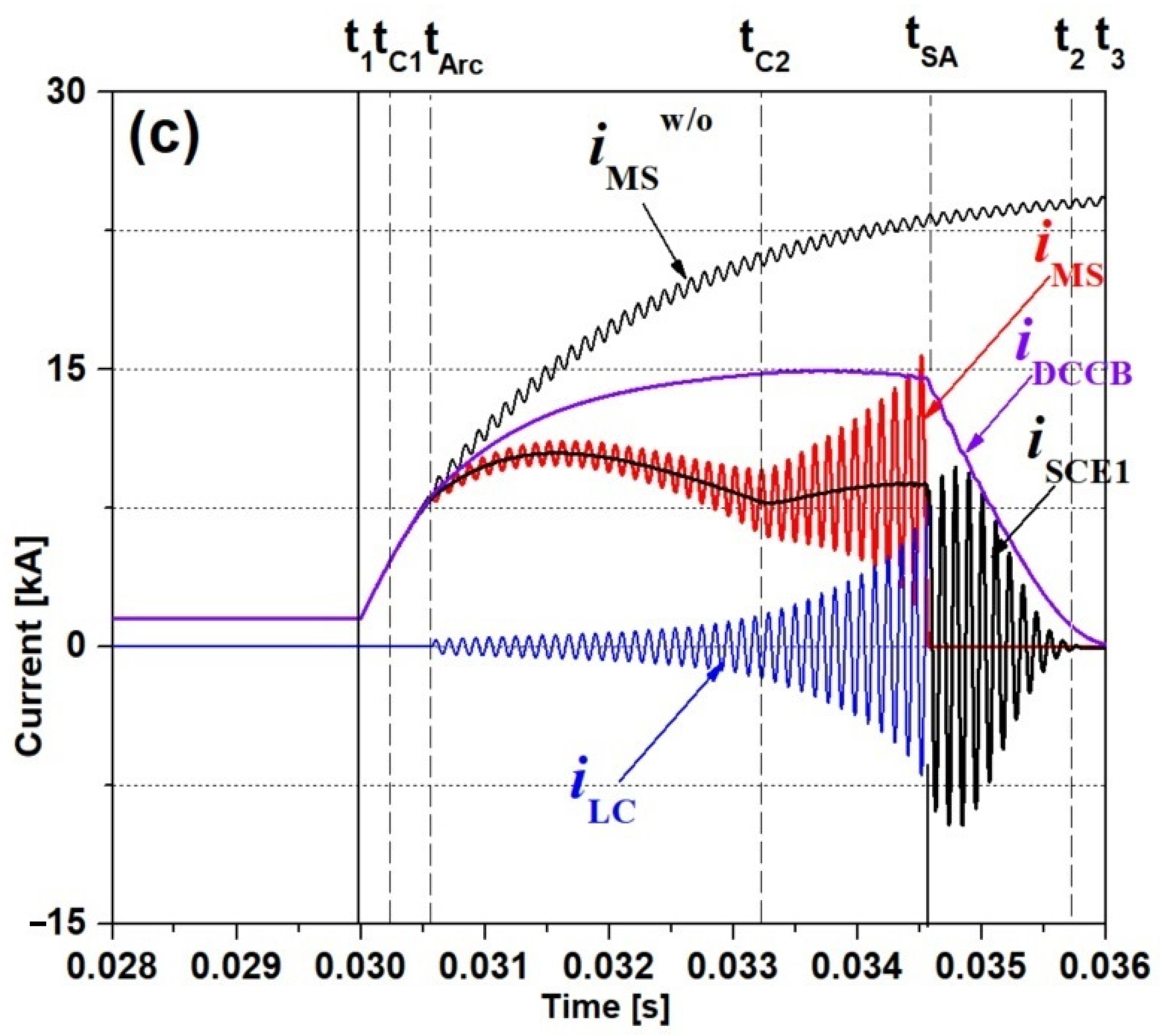

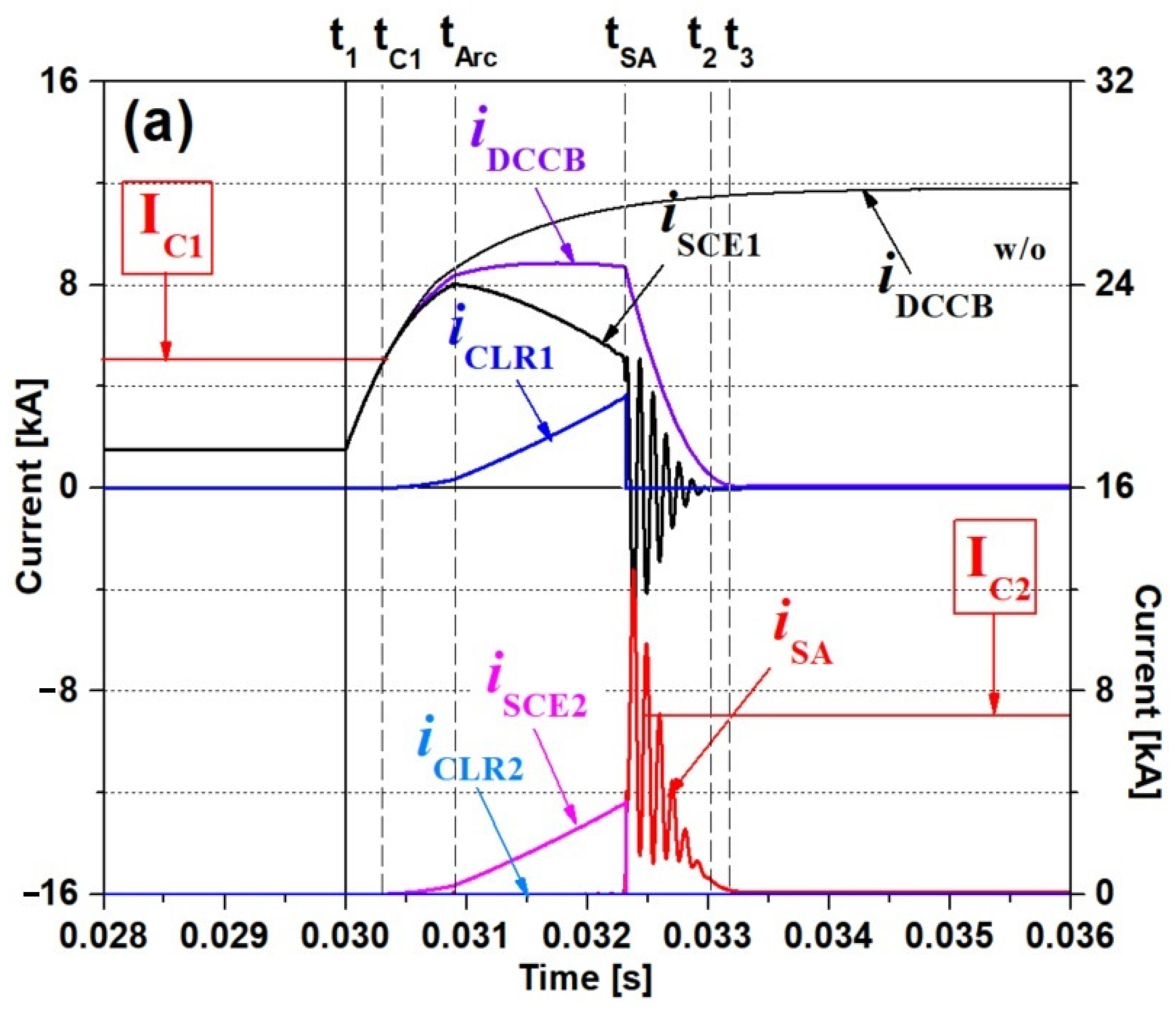

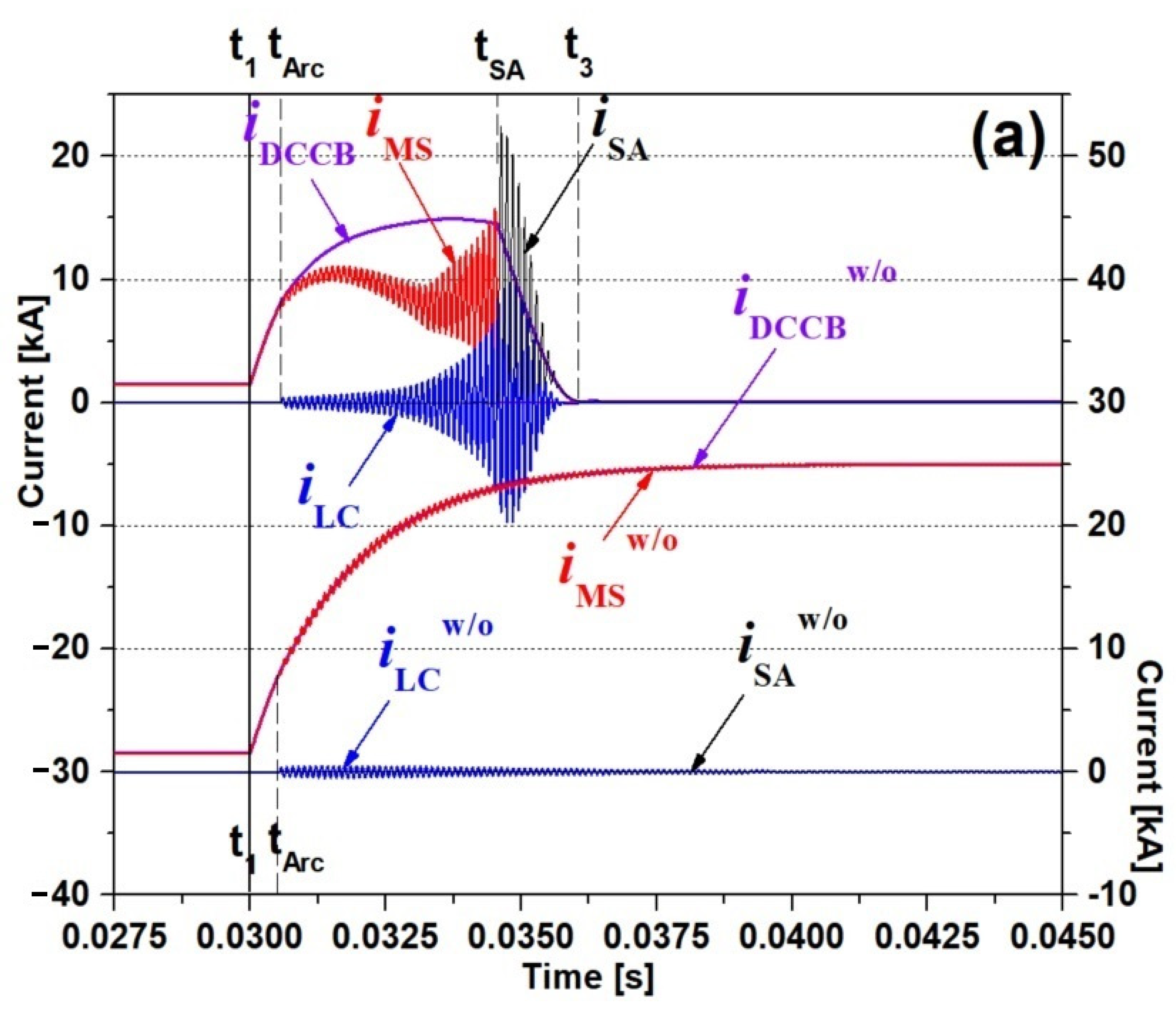

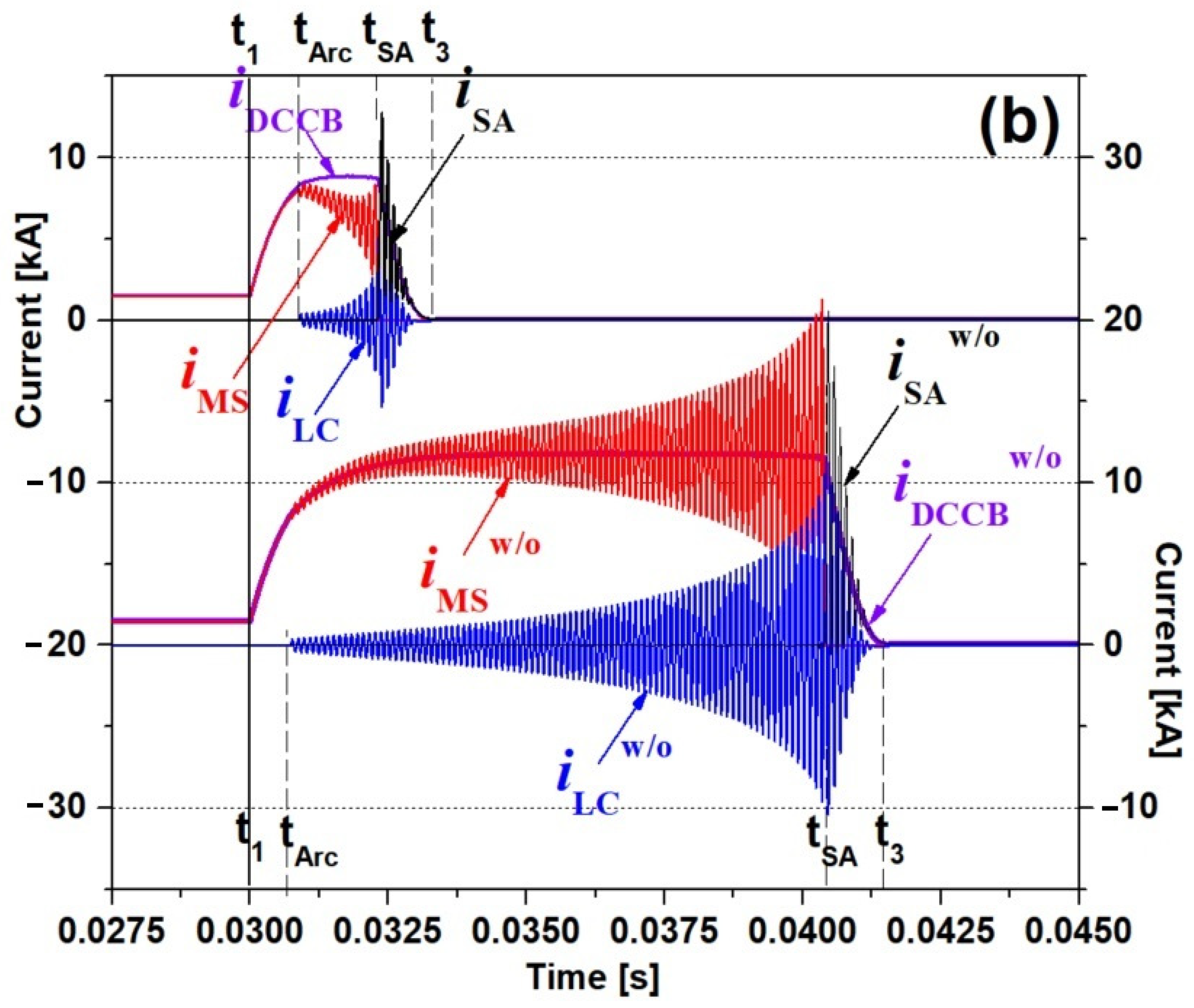

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Nakao, H.; Nakagoshi, Y.; Hatano, M.; Koshizuka, T.; Nishiwaki, S.; Kobayashi, A.; Murao, T.; Yanabu, S. DC Current Interruption in HVDC SF6 Gas MRTB by Means of Self-Excitation. IEEE Power Eng. Rev. 2001, 21, 62. [Google Scholar] [CrossRef]

- Callavik, M.; Blomberg, A.; Häfner, J.; Jacobson, B. Hybrid HVDC Breaker. ABB Grid Syst. Tech. Pap. 2012, 361, 143–152. [Google Scholar]

- Sneath, J.; Rajapakse, A.D. Fault Detection and Interruption in an Earthed HVDC Grid Using ROCOV and Hybrid DC Breakers. IEEE Trans. Power Deliv. 2016, 31, 973–981. [Google Scholar] [CrossRef]

- Meyer, C.; Kowal, M.; de Doncker, R.W. Circuit breaker concepts for future high-power DC-applications. In Conference Record of the 2005 Industry Applications Conference, Proceedings of the Fourtieth IAS Annual Meeting, Kowloon, Hong Kong, 2–6 October 2005; Institute of Electrical and Electronics Engineers: Piscataway, NJ, USA, 2005. [Google Scholar] [CrossRef]

- Thomas, D.W.P.; Pereira, E.T.; Christopoulos, C.; Howe, A.F. The simulation of circuit breaker switching using a composite Cassie-modified Mayr model. IEEE Trans. Power Deliv. 1955, 10, 1829–1835. [Google Scholar] [CrossRef]

- Lee, J.; Khan, U.A.; Lee, H.; Lee, B. Impact of SFCL on the Four Types of HVDC Circuit Breakers by Simulation. IEEE Trans. Appl. Supercond. 2016, 26, 1–6. [Google Scholar]

- Xiang, B.; Tan, Y.; Yang, K.; Liu, Z.; Geng, Y.; Wang, J.; Yanabu, S. Quenched Resistance Effects on a Superconducting Current-Limiting-Type DC Breaker. IEEE Trans. Appl. Supercond. 2016, 26, 1–5. [Google Scholar] [CrossRef]

- Zhoua, G.; Hana, M.; Filizadehb, S.; Caoa, X.; Huang, W. Studies on the combination of RSFCLs and DCCBs in MMC-MTDC system protection. Int. J. Electr. Power Energy Syst. 2021, 125, 106532. [Google Scholar] [CrossRef]

- Liang, S.; Tang, Y.; Ren, L.; Xu, Y.; Shi, J.; Li, Z.; Tan, X. Parameter Matching and Optimization of a Hybrid Type DC SFCL Considering the Transient Characteristics of VSC-Based DC Systems. Energies 2019, 12, 3522. [Google Scholar] [CrossRef] [Green Version]

- Lee, H.; Asif, M.; Park, K.; Lee, B. Feasible protection strategy for HVDC system by means of SFCL and passive resonance DC breaker. IET J. Eng. 2019, 2019, 767–770. [Google Scholar] [CrossRef]

- van der Sluis, L. Transients in Power Systems; John Wiley & Sons: Hoboken, NJ, USA, 2001. [Google Scholar]

- Walter, M.M. Switching Arcs in Passive Resonance HVDC Circuit Breakers. Ph.D. Thesis, ETH Zürich, Zürich, Switzerland, 2013. [Google Scholar]

- Yamaguchi, H.; Kataoka, T. Current Limiting Characteristics of Transformer Type Superconducting Fault Current Limiter with Shunt Impedance and Inductive Load. IEEE Trans. Appl. Supercond. 2008, 18, 668–671. [Google Scholar] [CrossRef]

- Babaei, M.; Abdelwahed, S.; Kluss, J.V.; Jafari-Marandi, R. A novel approach for optimal design of superconducting fault current limiter. In Proceedings of the 2018 IEEE Texas Power and Energy Conference (TPEC), College Station, TX, USA, 12 March 2018. [Google Scholar]

- Žitnik, B.; Babuder, M.; Muhr, M.; Žitnik, M.; Thottappillil, R. Numerical Modelling of Metal Oxide Varistors. In Proceedings of the XIVth International Symposium on High Voltage Engineering, Beijing, China, 25–29 August 2005. [Google Scholar]

| DC System Circuit | Parameters | Value | Unit |

|---|---|---|---|

| DC source voltage | VDC | 15 | kV |

| Line impedance (Z1) | R1 | 0.01 | Ω |

| X1 | 0.377 | Ω | |

| Load impedance (ZL) | RL | 0.6 | Ω |

| Small DC Fault Resistance | R21 | 0.6 | Ω |

| Large DC Fault Resistance | R22 | 1.2 | Ω |

| Components | Description | Parameters | Value | Unit |

|---|---|---|---|---|

| MS | Conductance of insulation material | G0 | 5.5 × 1015 | - |

| Heat energy | Q0 | 15 | - | |

| Time constant of arc | τa | 1 | - | |

| Series Resonance Circuit | Series inductance | L | 87 | μH |

| Series capacitance | C | 3.33 | μF | |

| SCE1 | Normal resistance of SCE1 | RN1 | 1 | Ω |

| Normal resistance of SCE2 | RN2 | 20 | Ω | |

| SCE2 | Time constant of SCE1 & SCE2 | τb | 0.1 | - |

| Critical current of SCE1 | IC1 | 5 | kA | |

| Critical current of SCE2 | IC2 | 7 | kA | |

| CLR1 | Current limiting reactance | LCLR | 2 | mH |

| CLR2 | Current limiting resistance | RCLR | 2 | Ω |

| SA | breakdown voltage | VB | 20 | kV |

| nonlinear index | γ | 8 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, S.-J.; Lee, J.-H.; Lee, J.-W.; Lim, S.-H. Improvement of DC Fault Current Limiting and Interrupting Operation of Hybrid DC Circuit Breaker Using Double Quench. Energies 2021, 14, 4157. https://doi.org/10.3390/en14144157

Choi S-J, Lee J-H, Lee J-W, Lim S-H. Improvement of DC Fault Current Limiting and Interrupting Operation of Hybrid DC Circuit Breaker Using Double Quench. Energies. 2021; 14(14):4157. https://doi.org/10.3390/en14144157

Chicago/Turabian StyleChoi, Sang-Jae, Jun-Hyup Lee, Jin-Wook Lee, and Sung-Hun Lim. 2021. "Improvement of DC Fault Current Limiting and Interrupting Operation of Hybrid DC Circuit Breaker Using Double Quench" Energies 14, no. 14: 4157. https://doi.org/10.3390/en14144157

APA StyleChoi, S.-J., Lee, J.-H., Lee, J.-W., & Lim, S.-H. (2021). Improvement of DC Fault Current Limiting and Interrupting Operation of Hybrid DC Circuit Breaker Using Double Quench. Energies, 14(14), 4157. https://doi.org/10.3390/en14144157