1. Introduction

Energy storage devices, including lithium-ion batteries (LIBs) and electric double-layer capacitors (EDLCs), are indispensable in various applications, from small portable electronic devices to utility-scale systems. EDLCs offer various key advantages over traditional rechargeable batteries in terms of power density, cycle life, and operation temperature range. However, EDLCs cannot simply be an alternative to secondary batteries because of their low energy density properties. EDLCs have chiefly been used as a high-power-density energy buffer that supports the main battery [

1,

2]. Lithium-ion capacitors (LICs), a hybrid energy storage device of EDLCs and LIBs, have also been developed to enhance energy density [

3,

4,

5,

6,

7,

8,

9]. Thanks to the long-life performance at a wide temperature range, EDLCs and LICs would expectedly replace traditional lead–acid batteries in infrastructure applications, where maintenance-free operation is strongly desirable. Another likely application is spacecraft energy storage systems, where traditional LIBs are cycled with shallow depth-of-discharge (DoD) to meet the requirement of 5 to 10 year operation. EDLCs and LICs can operate without significant degradation, even with deep DoD, hence dramatically bridging the energy density gap between LIBs and EDLCs/LICs [

9,

10].

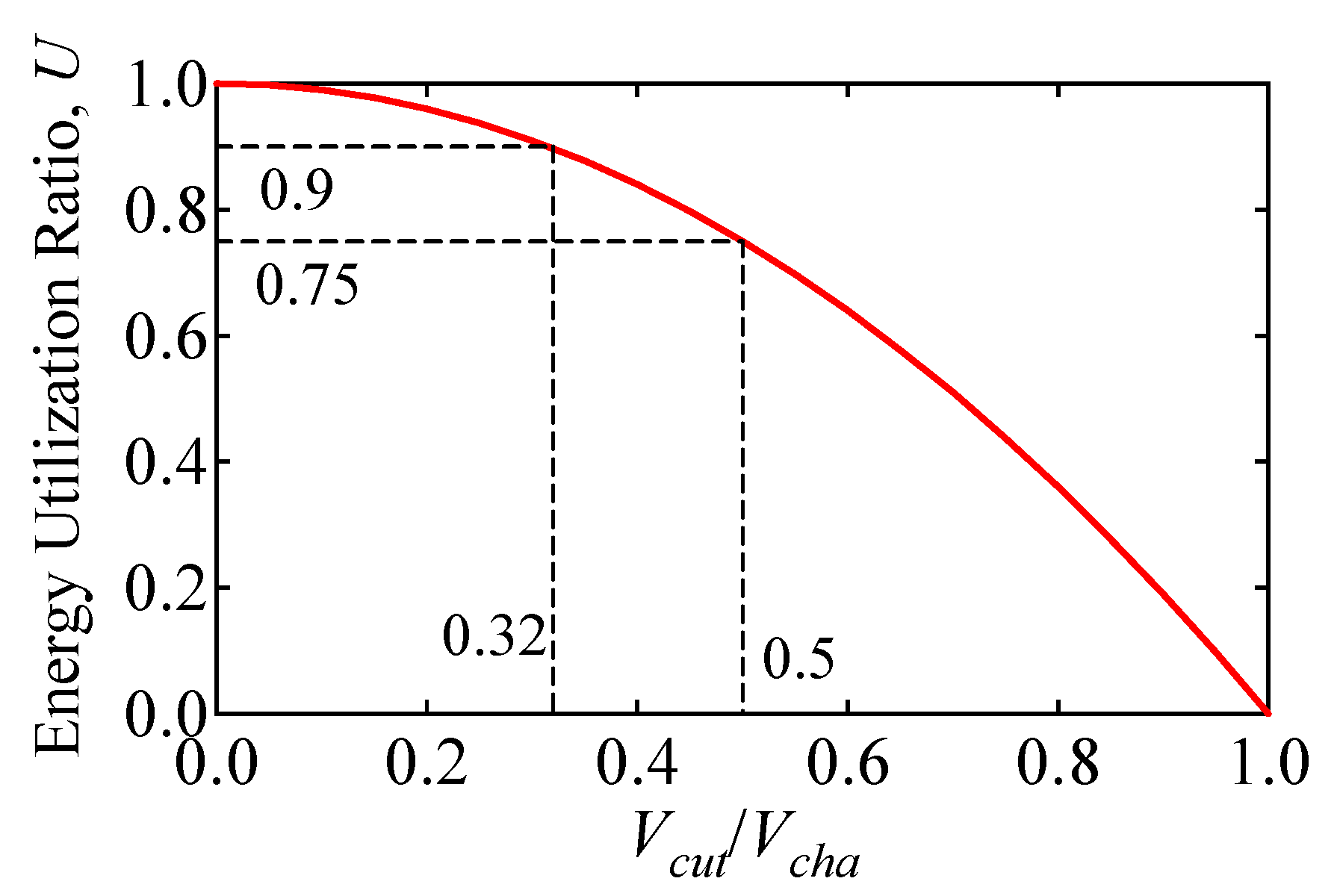

Aside from the lower energy density properties, wide voltage variations of EDLCs and LICs are cited as a major drawback. Single-cell voltages of an EDLC, LIC, and LIB as a function of ampere-hour DoD are shown in

Figure 1. The typical voltage variation ranges of LIB cells are 2.7–4.2 V, whereas those of EDLCs and LICs are 0–2.5 V and 2.2–3.8 V, respectively. This suggests that DC–DC converters for EDCLs and LICs need to operate with a wide input/output voltage range. However, such wide input/output voltage operation generally impairs converters’ performance, such as power conversion efficiencies and volume.

EDLCs and LICs can be charged and discharged only in an allowable input/output voltage range of DC–DC converters. If an operational voltage range of a DC–DC converter is 1.0–3.0 V, an EDLC cell can be charged and discharged only in the range of 1.0–2.5 V. This implies that the energy stored in the voltage range of 0–1.0 V is no longer usable. In general, an EDLC’s energy utilization ratio,

U, is given by:

where

Vcha is the charging voltage, and

Vcut is the cut-off voltage. A characteristic of

U as a function of

Vcut/

Vcha is graphed in

Figure 2. The lower the cut-off voltage

Vcut, the higher the energy utilization ratio

U will be. For example, 75% of the stored energy can be utilized by discharging an EDLC cell as low as

Vcut =

Vcha/2. Discharging as low as 0.32

Vcha achieves 90% energy utilization. Wide input/output voltage range DC–DC converters achieve high energy utilization, but their performance is unavoidably impaired, as discussed above.

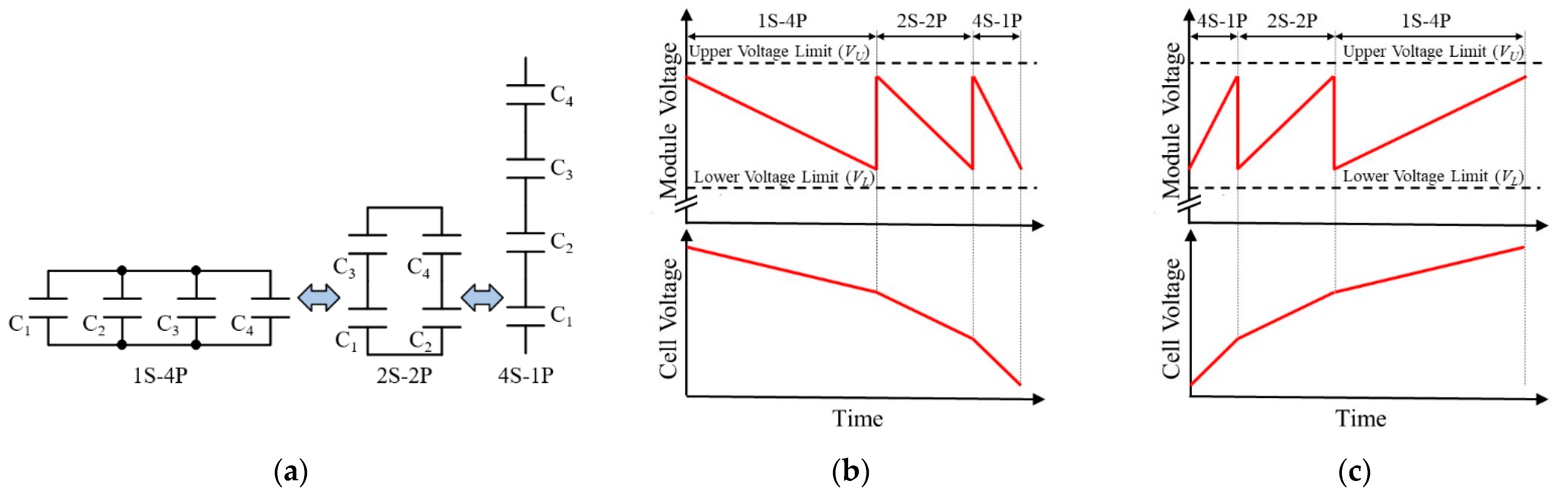

Series-parallel reconfiguration techniques, also known as changeover circuits, have been developed to cope with the above issues of EDLCs [

11,

12,

13,

14,

15,

16,

17,

18]. Literally, the series-parallel connections of EDLCs are reconfigured depending on cell voltages so that the module voltage stays within the desired voltage range.

Figure 3 illustrates images of reconfiguration sequence and voltage profiles of a four-cell module. In the discharging process (

Figure 3b), the module starts to operate as a 1-series 4-parallel (1S-4P) configuration, with which the module voltage

VM is equal to the cell voltage

VC. Before

VM decreases down to the predetermined lower voltage limit

VL, the module is reconfigured to be 2S-2P configuration to double the module voltage

VM (i.e.,

VM = 2

VC). Before

VM reaches

VL again, the module is reconfigured to be 4S-1P configuration so that

VM = 4

VC. This reconfiguration technique allows cells to discharge deeply while keeping

VM within a desired voltage range. In the charging process (

Figure 3c), the series-parallel configuration is reconfigured in the opposite order.

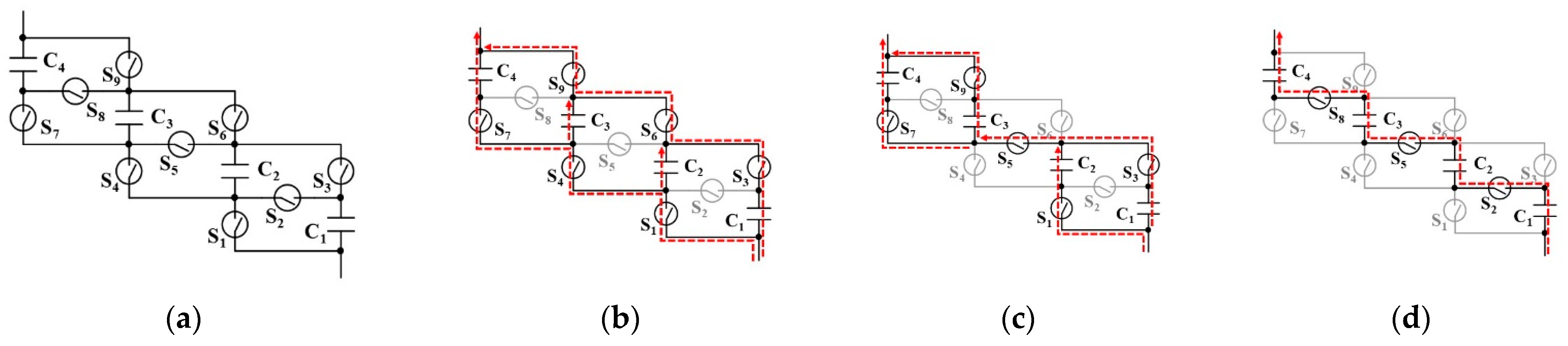

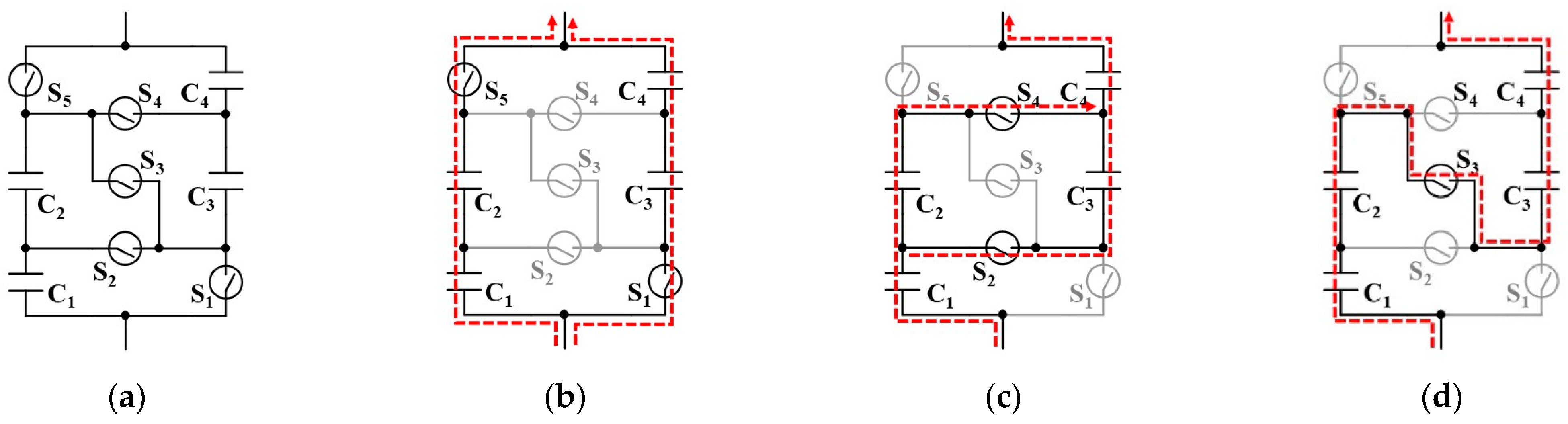

A variety of series-parallel reconfiguration modules have been proposed [

11,

12,

13,

14,

15,

16,

17,

18]. Depending on whether cell voltage imbalance occurs during series-parallel reconfiguration sequences, the conventional reconfiguration techniques can be categorized into two groups: balance- and unbalance-shift circuits. A typical balance-shift circuit consisting of four cells C

1–C

4 is shown in

Figure 4a that operates identically to the circuit in

Figure 3. This circuit operates either in the 1S-4P, 2S-2P, or 4S-1P configuration, and all cells can discharge and charge uniformly in all configurations. However, this technique cannot be used for modules comprising odd number cells (e.g., five and seven cells), and, therefore, its design flexibility and extendibility are poor. Employing cells with a larger/smaller capacitance is another way to tune the module capacitance, but the limited variety of products does not allow fine-tuning. For example, capacitances of DXE series from Nippon Chemi-Con corporation [

19] are 400, 800, 1200, and 1400 F. Changing from 800 F cells to 400 F or 1200 F ones only achieves a 0.5 or 1.5 times greater module capacitance.

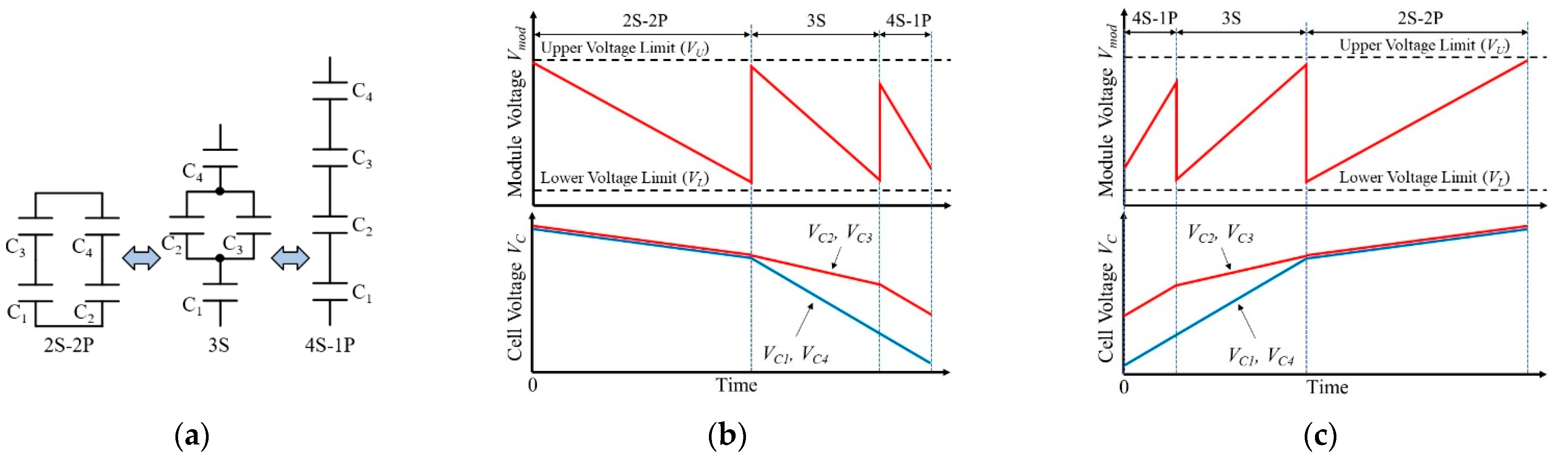

Representative reconfiguration steps and voltage profiles of the unbalanced-shift circuit for four cells C

1–C

4 are shown in

Figure 5.

VC1–

VC4 in

Figure 5b,c are the voltages of C

1–C

4. The number of series-connection changes one by one (i.e., 2S, 3S, and 4S), and voltage step changes can be finer than those of the balance-shift circuits. All cells can be equally discharged and charged in 2S-2P and 4S-1P configurations, but unequal currents flow in the 3S configuration, generating cell voltage imbalance. In the discharging process, for example, C

1 and C

4 discharge faster, and

VC1 and

VC4 decrease steeper than

VC2 and

VC3. The occurrence of voltage imbalance significantly lowers the energy utilization ratio of the module, because some cell voltages decrease down to 0 V or some cells might be over-discharged under subzero voltages in the worst case. A representative unbalanced-shift circuit for four cells and its operation modes are shown in

Figure 6 [

17].

Previous work proposed the unbalance-shift circuit with cell voltage equalization capability [

18]. All cells can charge and discharge uniformly, and the number of series-connection can be changed step-by-step. However, the minimum number of series-connection is limited to

n/2 for

n-cell modules—for example, the minimum number of series-connection of five- and six-cell modules is 3. The five-cell module can operate as either 3S, 4S, or 5S configurations, but 1S and 2S configurations are not feasible. This limited configuration results in a reduced energy utilization ratio.

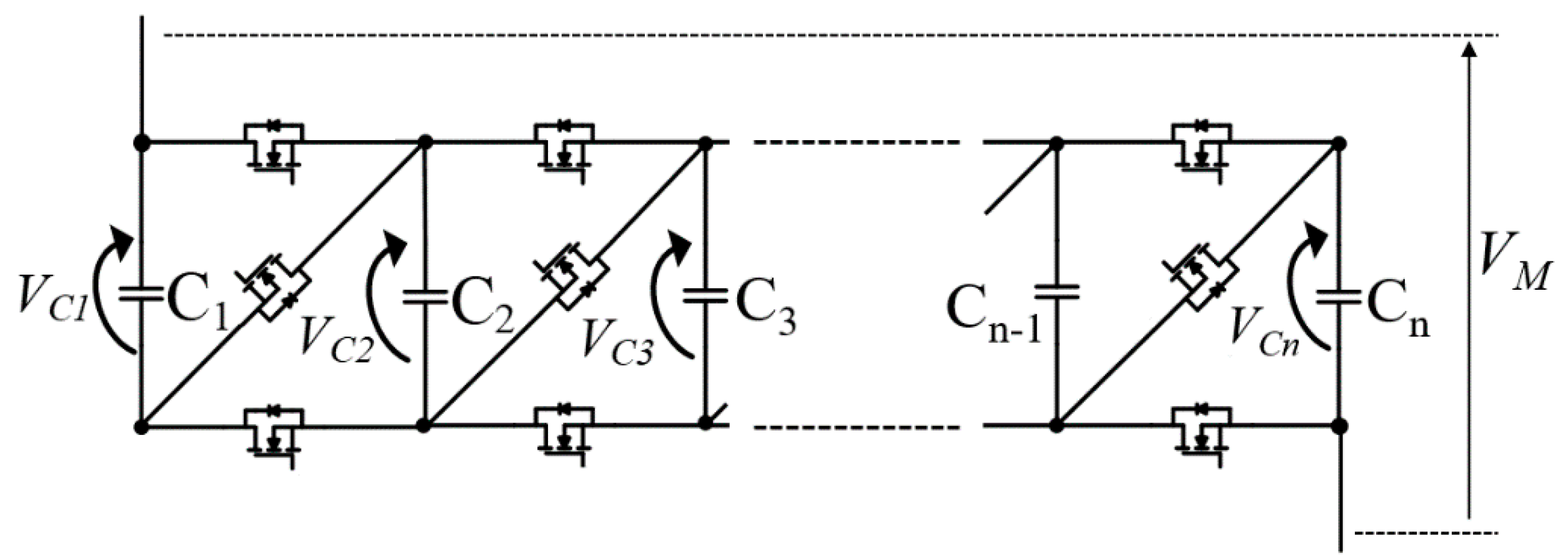

This paper presents a novel series-parallel reconfiguration circuit with voltage equalization capability. The number of cells connected in series can be changed one by one without causing cell voltage imbalance. Furthermore, the proposed circuit is applicable to any number of cells, realizing flexible design and good modularity. The proposed reconfiguration circuit for the

n-cell module can operate as a 1S …

n-S configuration, further improving the energy utilization ratio compared with [

18]. The remainder of this paper is organized as follows:

Section 2 introduces the proposed series-parallel reconfiguration circuit; the operation analysis will be performed in

Section 3; followed by experimental verification tests for the five-cell module in

Section 4.

3. Operation Analysis

3.1. Operation Principle

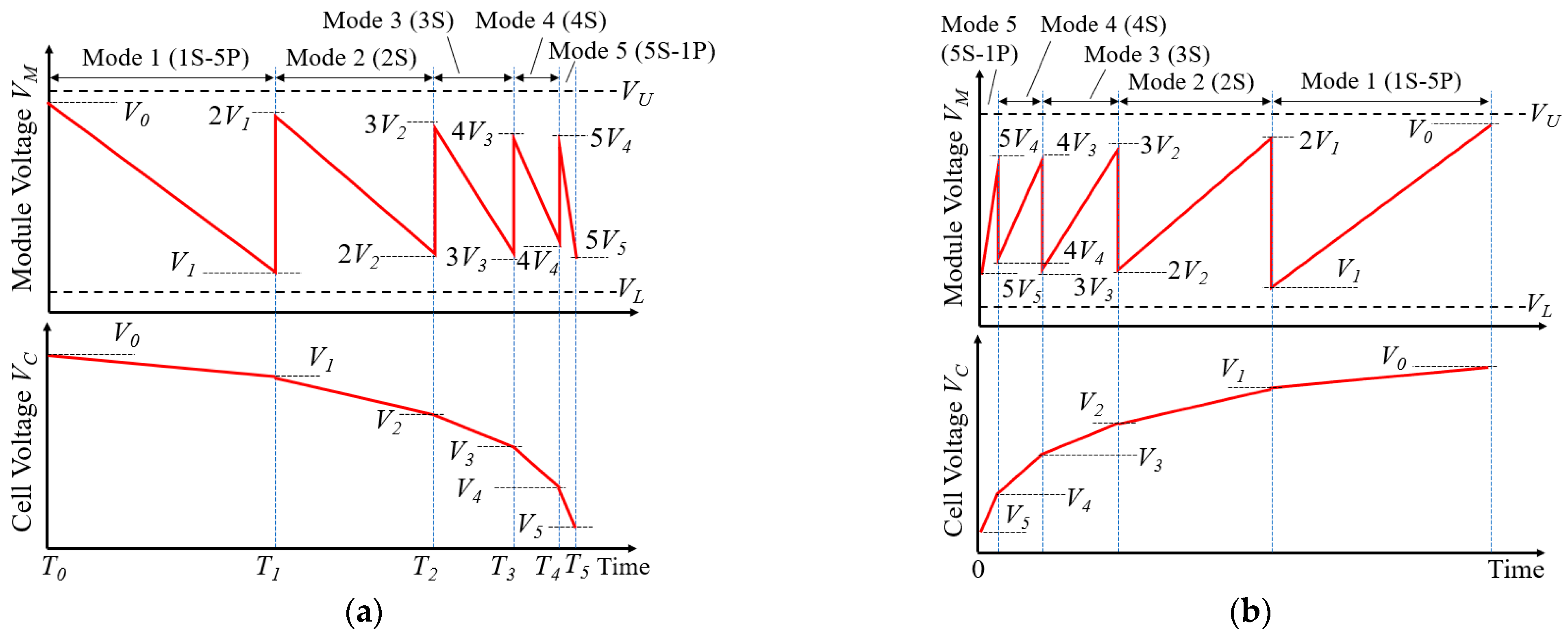

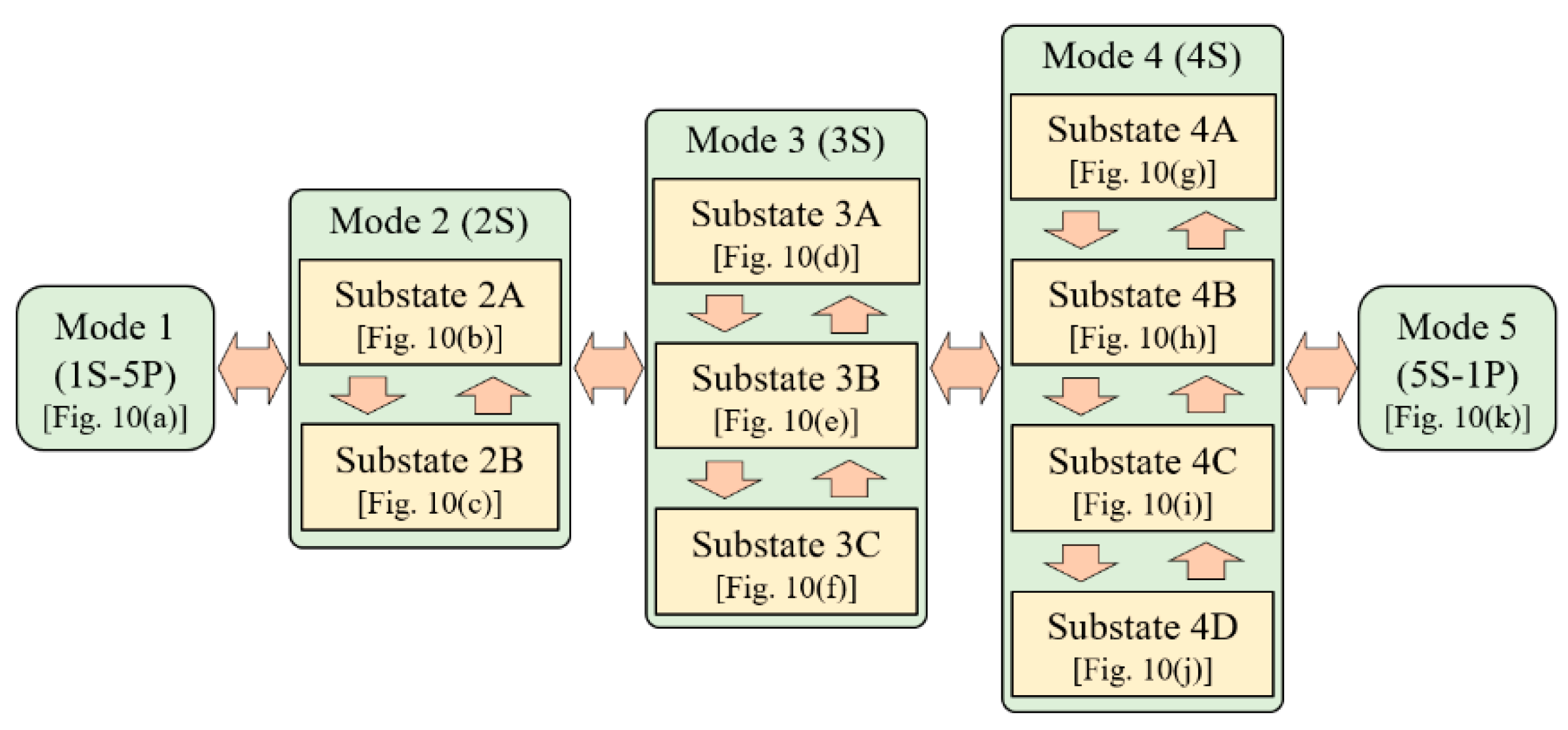

Cell and module voltage profiles of the proposed reconfiguration circuit are illustrated in

Figure 9. The series-parallel connection of cells in the discharging process (

Figure 9a) is sequentially reconfigured from 1-series 5-parallel (1S-5P) to 5S-1P configurations, so that the variation range of the module voltage

VM is between the upper and lower voltage limits of

VU and

VL. There are five configurations (i.e., 1S-5P, 2S, 3S, 4S, and 5S-1P), and 2S-, 3S-, and 4S-configurations have their own unique substates. The substates in 2S-, 3S-, and 4S-configurations are repetitively switched to achieve cell voltage equalization. Current flow paths in each configuration or substate in discharging process are shown in

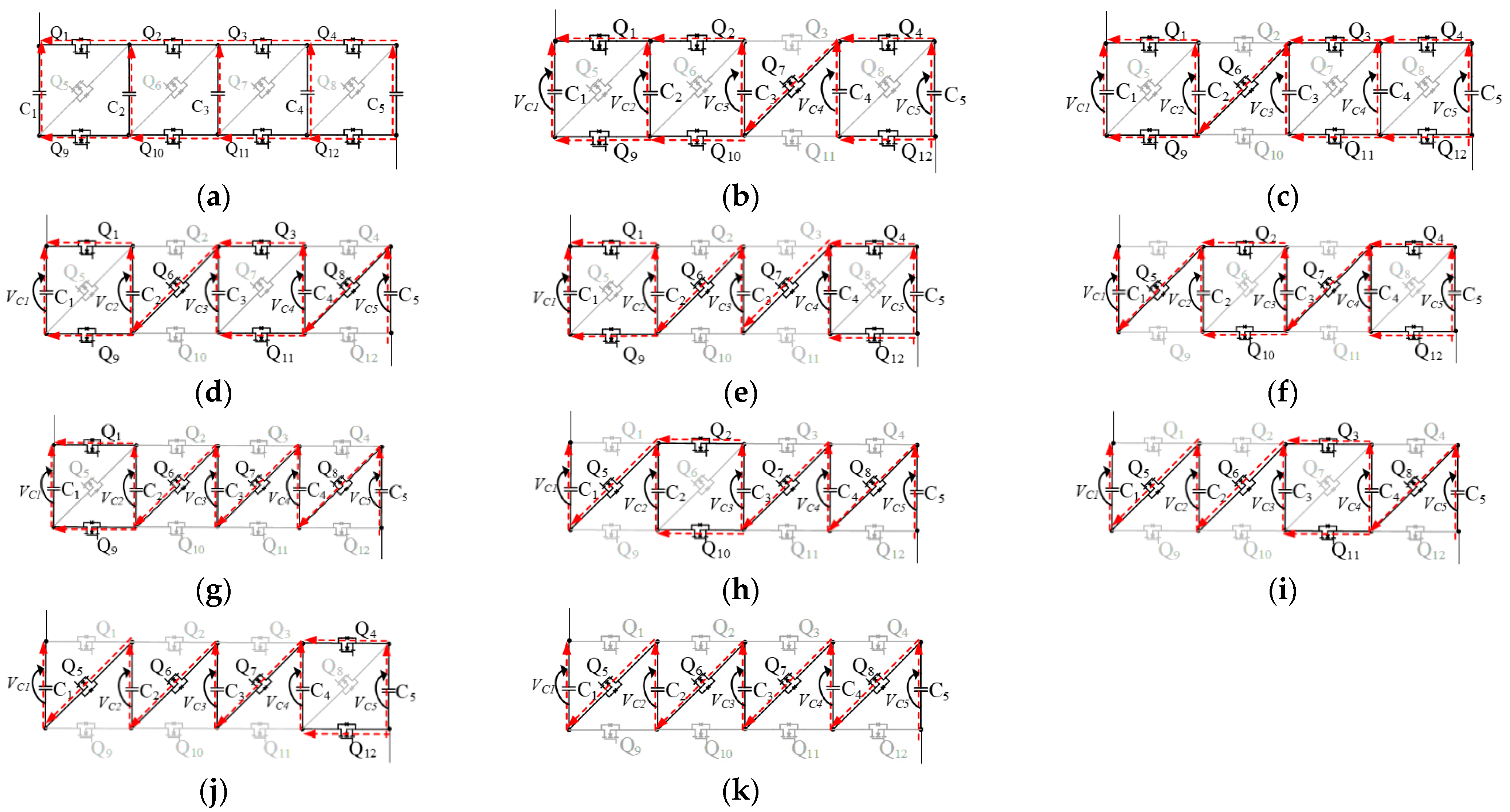

Figure 10.

Mode 1 (1S-5P) (

Figure 10a): The module starts discharging with 1S-5P configuration. All cells are connected in parallel through switches and, therefore, cell voltages are uniform. Before

VM reaches

VL, the operation mode moves to the 2S configuration.

Mode 2 (2S) (

Figure 10b,c): The module configuration alternates between two substates. In substate 2A (

Figure 10b), C

1–C

3 are connected in parallel, while the remaining cells of C

4 and C

5 are also connected in parallel in a different group. Their voltage relationships in substate 2A are expressed as:

where

VC1–

VC5 are the voltages of C

1–C

5. The combined capacitance of C

1–C

3 is 1.5 times larger than that of C

4–C

5, generating voltage imbalance. In substate 2B (

Figure 10c), on the other hand, C

3 is connected in parallel with C

4 and C

5, yielding the following voltage relationships:

Since the combined capacitances of C1–C2 and C3–C5 are different, their voltages tend to be mismatched. Although both substates contain unbalanced combined capacitances, all cells are virtually connected in parallel by switching substates 2A and 2B repetitively at a fixed frequency. Repetitive switching between substates 2A and 2B is equivalent to combining (2) and (3), yielding VC1 = VC2 = VC3 = VC4 = VC5. Thus, the virtual parallel connection equalizes all cell voltages in the module.

Mode 3 (3S) (

Figure 10d–f): The series-parallel configuration alternates among three substates. Either C

1, C

3, or C

5 is discharged alone, whereas the remaining cells are discharged in parallel with another cell. In substate 3A (

Figure 10d), for example, the discharging current of C

5 is twice that of other cells. Similarly, a larger current flows through C

3 and C

1 in substates 3B and 3C, respectively. Although cell voltages tend to be imbalanced in these substates in 3S configuration, repetitively alternating the configuration among substates 3A–3C realizes the virtual parallel connection for all cells. From

Figure 10d–f, the voltage relationships in substates 3A–3C are:

Combining (4)–(6) produces VC1 = VC2 = VC3 = VC4 = VC5, achieving the voltage equalization.

Mode 4 (4S) (

Figure 10g–j): There are four substates in 4S configuration. Two out of five cells are connected in parallel, while other cells are connected in series. In substate 4A (

Figure 10g), for example, C

1 and C

2 are connected in parallel, and other cells are connected in series. In other substates, the other two cells are connected in parallel. Cell voltage relationships in substates 4A–4D (

Figure 10g–j) are expressed as:

From (7)–(10), VC1 = VC2 = VC3 = VC4 = VC5. Similar to the 2S and 3S configurations, repetitive alternation among these four substates realizes cell voltage equalization.

Mode 5 (5S-1P) (

Figure 10k): All cells are connected in series and discharge uniformly without generating voltage imbalance.

The mode transition is illustrated in

Figure 11. The discharging process starts with Mode 1 (1S-5P configuration) and ends with Mode 5 (5S-1P configuration). Substates in each configuration are repetitively switched to prevent the occurrence of cell voltage imbalance. In the charging process, series-parallel configurations are shifted in the opposite order (i.e., from Mode 5 to Mode 1) so that the variation range of

VM is between

VU and

VL, as illustrated in

Figure 9b.

3.2. Operation Condition

The series-parallel connection of cells is reconfigured depending on cell voltages. The module voltage

VM must stay between the upper limit

VU and lower limit

VL, even when the circuit is reconfigured. The cell and module voltage profiles in

Figure 9a yield the following equations:

where

T0–

T5 are the time at the beginning or end of operation modes in the discharging process (see

Figure 9a). Rearrangement of (11) and (12) produces:

These equations can also be applied to the charging process (

Figure 9b).

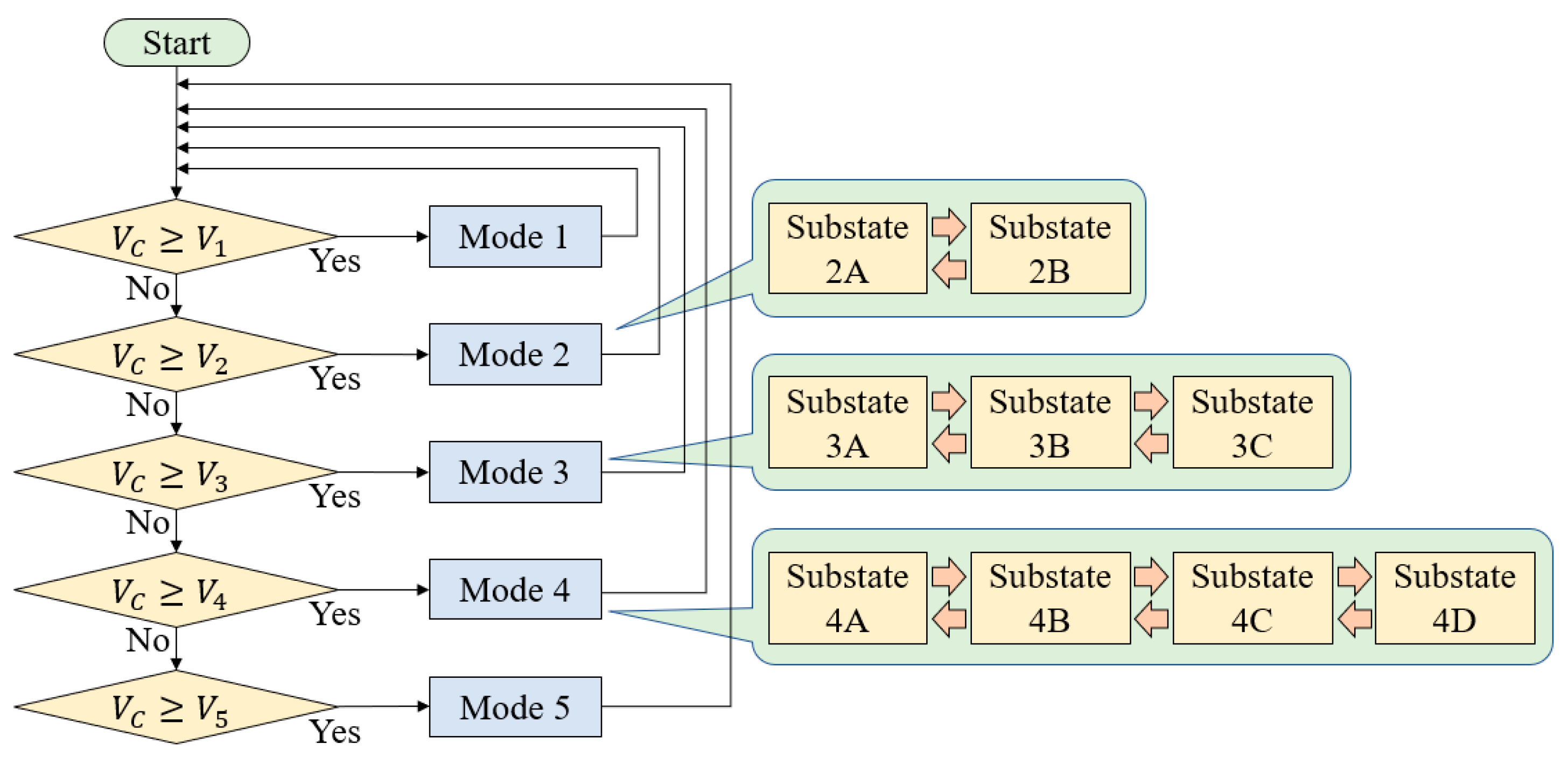

3.3. Reconfiguration Algorithm

Assuming all cell voltages are equalized to be

VC, the operation modes are determined, based on

VC, as:

The flowchart of the reconfiguration sequence for the five-cell module is shown in

Figure 12. Series-parallel configuration is simply determined based on the measured

VC. Substates in Modes 2–4 are switched at several hertz to preclude the occurrence of cell voltage imbalance.

3.4. Switching Frequency

Although substates in Modes 2–4 repetitively switch, cell voltage imbalance occurs to some extent in each substate due to unbalanced combined capacitances, as discussed in

Section 3.1. A huge cell voltage imbalance might trigger an excessively large current at switching moments. A switching frequency

f should be properly determined to prevent the occurrence of a large cell voltage imbalance. In the following, the voltage imbalance between C

4 and C

5 in Mode 3 is focused as an example.

In substate 3A (

Figure 10d), C

5 discharges alone, while C

4 shares the discharge current with C

3. Assuming all cell capacitances are

C, the current difference between C

4 and C

5 is

IM/2, where

IM is the module’s discharge current. The voltage imbalance generated in substate 3A, Δ

V, is expressed as:

where

f is the switching frequency. In the next substate (substate 3B in

Figure 10e), C

4 and C

5 are connected in parallel, and a balance current

Ieq flows between them. Cells’ internal resistances

r4 and

r5, and switches’ on-resistance

Ron limit

Ieq are expressed as:

where

Rtotal is the total resistance. In general,

Rtotal is in the range of several to a few ten milliohms and, therefore, Δ

V should be within a few ten millivolts. Equation (15) suggests that

f < 10 Hz would be high enough to achieve Δ

V < 10 mV for 400 F cells, even when

IM ranges several ten amperes.

Although Mode 3 was focused above, operations in Modes 2 and 4 can be analyzed similarly. Since the numbers of substates in each mode are different (i.e., two, three, and four substates in Modes 2, 3, and 4, respectively), f is individually set for each mode. In Mode 3, for example, it takes four steps before coming back to the original substates (i.e., ). Modes 2 and 4, on the other hand, require two steps () and six steps (), respectively. The switching frequency f was determined to be 2.5, 5, and 10 Hz for Modes 2, 3, and 4, respectively, so that whole steps in each operation mode are completed in a similar time range; whole steps in Mode 2, 3, and 4 are completed in 0.8 s (=2 steps/2.5 Hz), 0.8 s (=4 steps/5 Hz), and 0.6 s (=6 steps/10 Hz), respectively.

4. Experimental Results

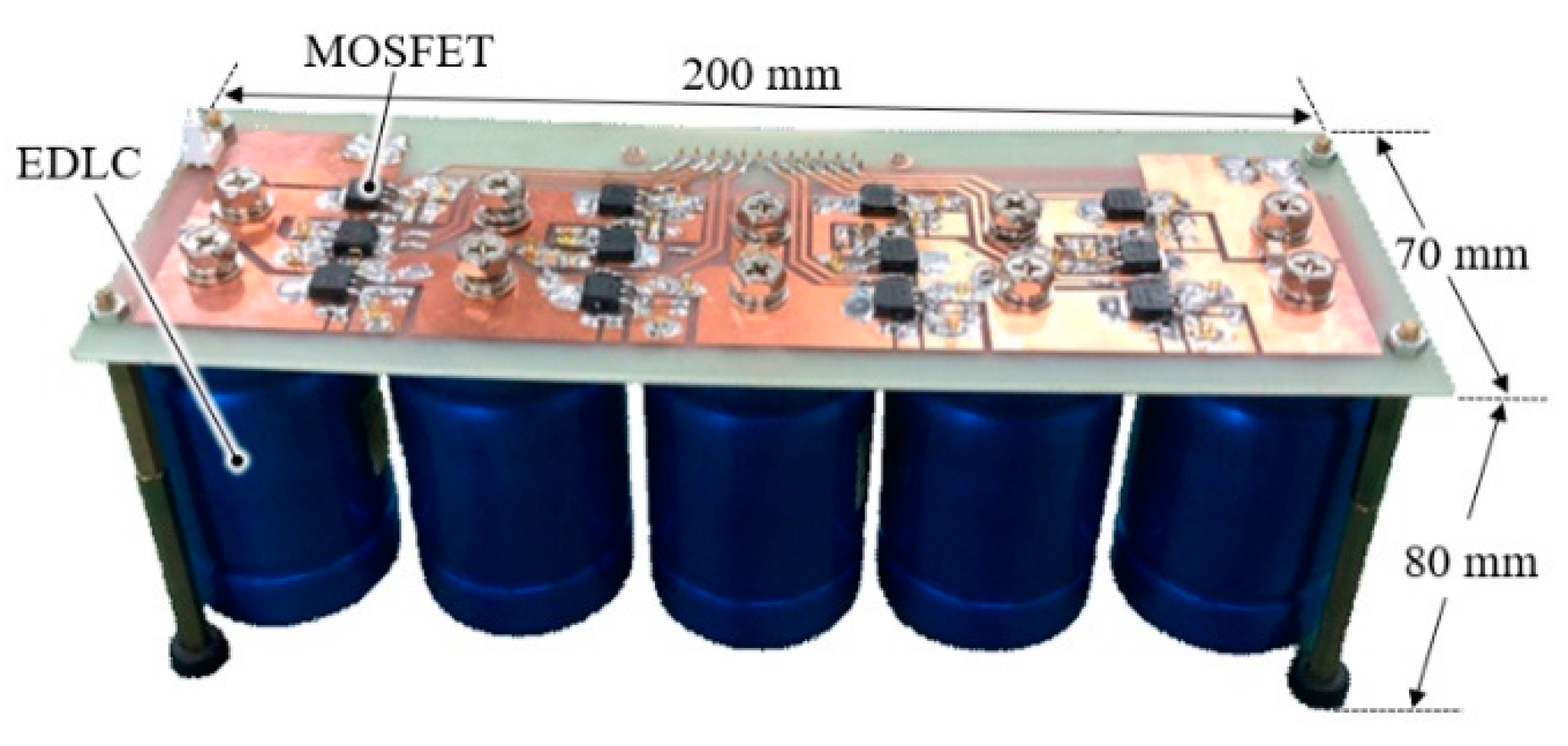

The proposed reconfiguration circuit for five cells was built, as shown in

Figure 13. 400 F EDLC cells with a rated charge voltage of 2.5 V were used. TMS320F28335 control card (Texas Instruments, Dallas, TX, USA) was used to measure cell voltages, implement the flowchart of the reconfiguration algorithm (

Figure 12), and generate driving signals for switches. N-channel MOSFETs (IRFR3410,

Ron = 39 mΩ) were used as switches. The gate-source voltage of 10 V was applied to turn on switches. Substates in 2S-, 3S-, and 4S-configurations were switched at 2.5, 5, and 10 Hz, respectively.

V1–

V4 were set to be 1.25, 0.83, 0.625, and 0.5 V, respectively. The EDLC module was cycled with a constant current of 2.0 A.

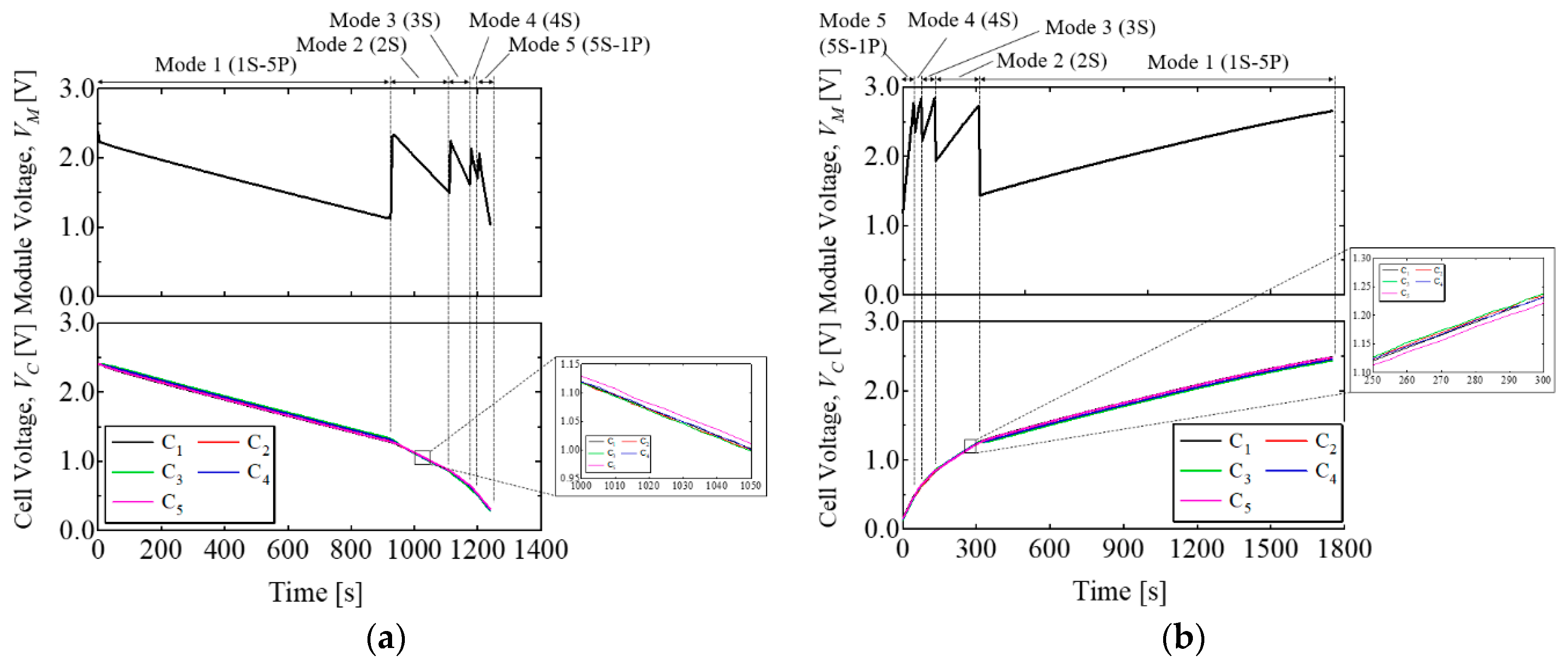

The measured discharging and charging voltage profiles are shown in

Figure 14a,b, respectively. The module started discharging in Mode 1 (1S-5P configuration) and was switched to Mode 2 (2S configuration) when

VC reached

V1 = 1.25 V. Cell voltage profiles in Mode 2 are magnified in the inset of

Figure 14a. The voltage of C

5 was slightly higher than others. This offset is attributable to a mismatch in cells’ internal resistances, and the internal resistance of C

5 would have been lower than others—the voltage of C

5 in Mode 2 was the highest and lowest in discharging and charging processes in

Figure 14a,b, respectively. However, the voltage imbalance was as low as 10 mV, and all cell voltages were satisfactorily balanced. All cells continued to uniformly discharge in Modes 3 and 4 (3S- and 4S-configurations) without causing cell voltage imbalance. All cells were discharged as low as 0.3 V at the end of the discharging experiment, which was equivalent to the energy utilization ratio of 98.6%.

The variation range of VM was limited within 1.04 V and 2.83 V, while all cells discharged from 2.5 V to 0.3 V. Both discharging and charging voltage profiles matched very well with the theoretical characteristics, demonstrating the proposed reconfiguration technique.