Numerical Study of 4H-SiC UMOSFETs with Split-Gate and P+ Shielding

Abstract

1. Introduction

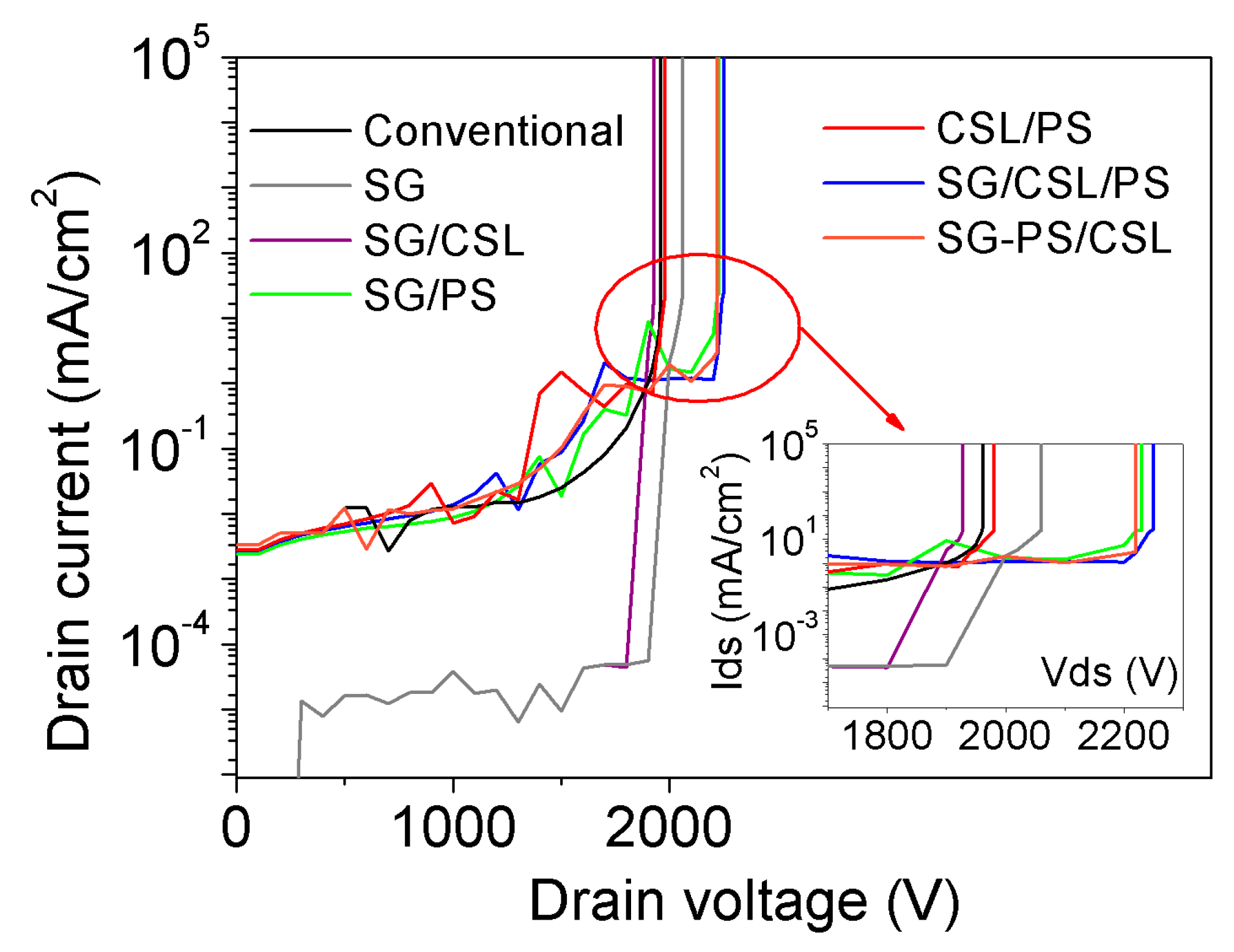

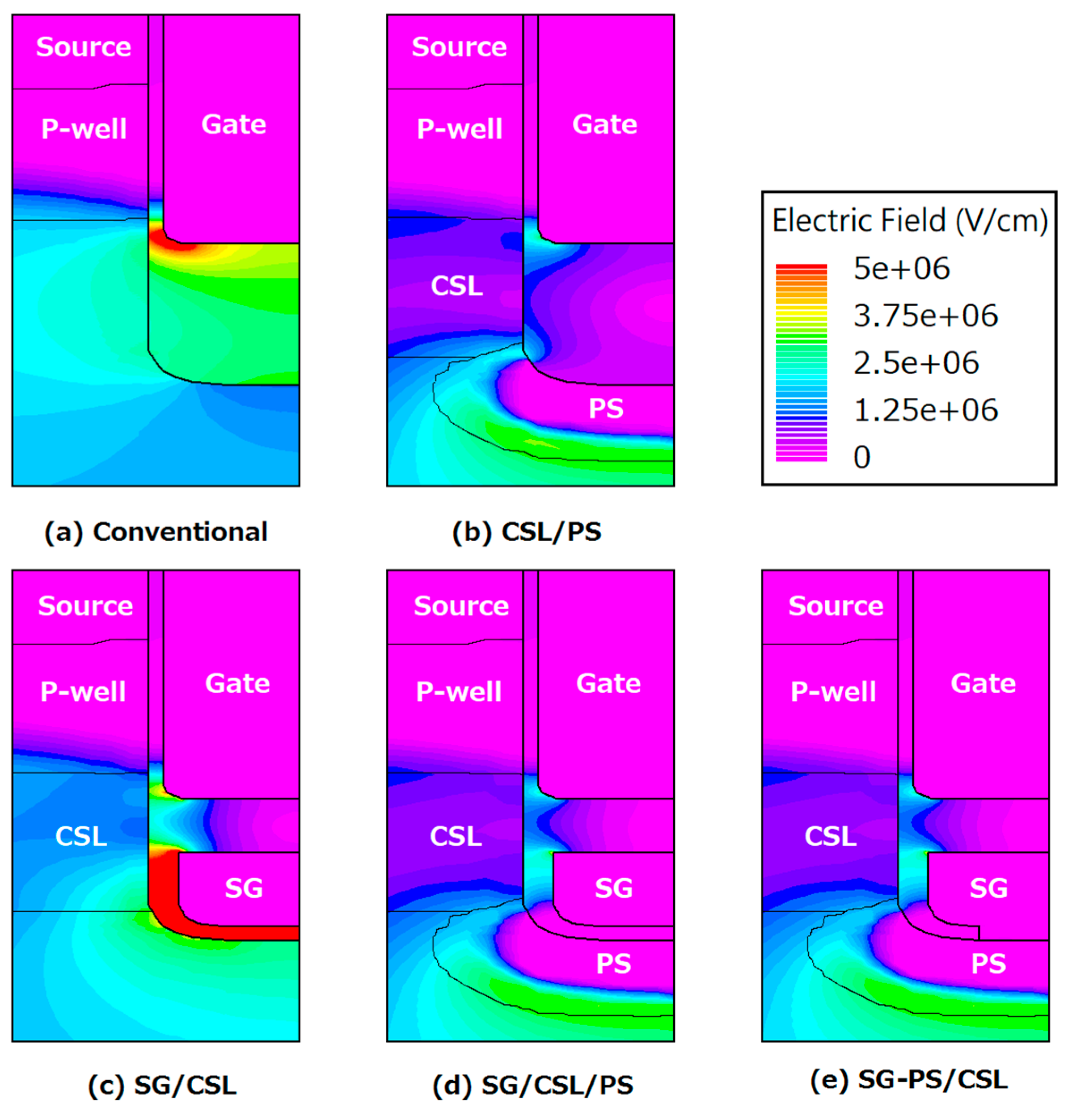

2. DC and Reverse Characteristics

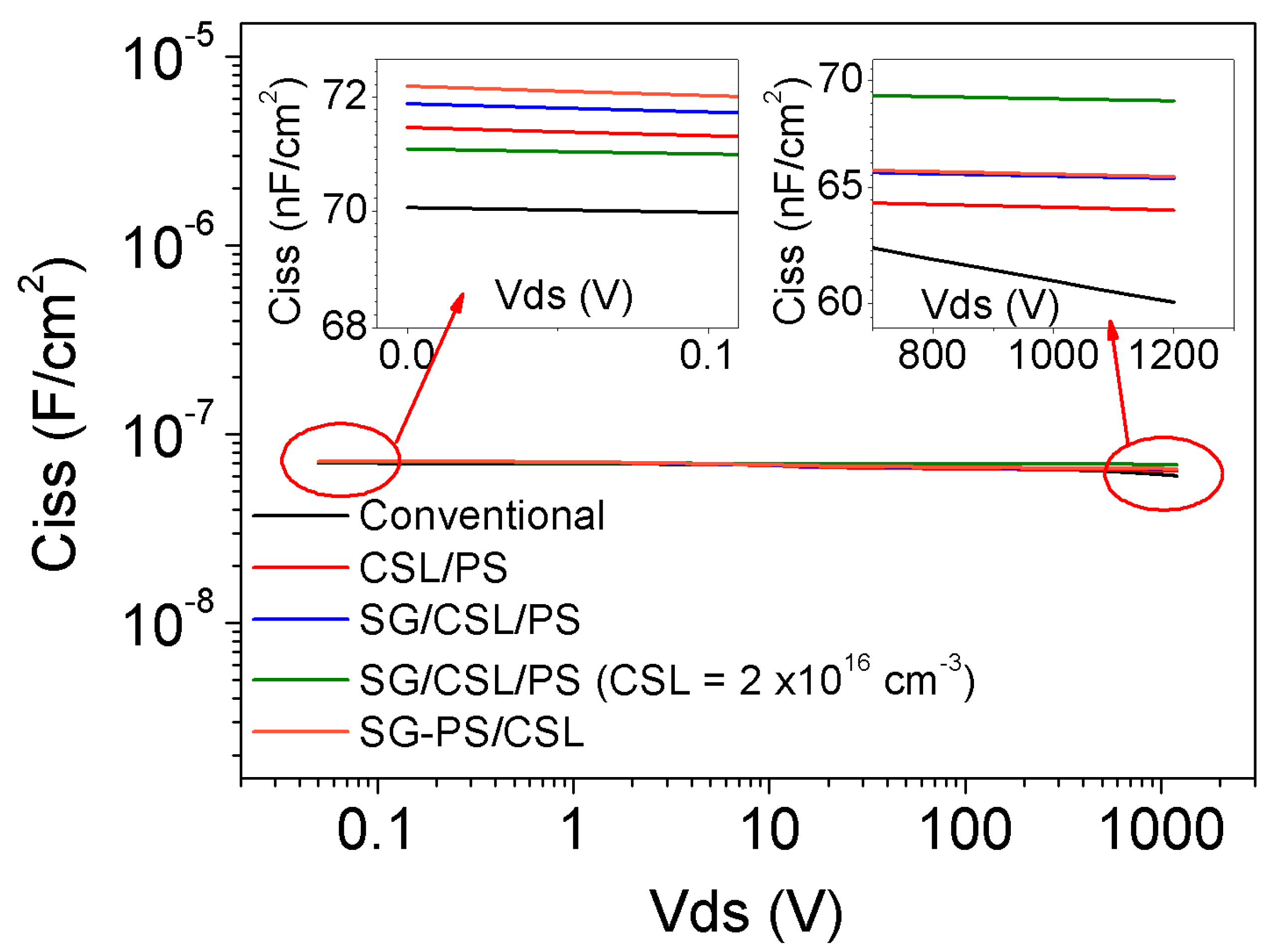

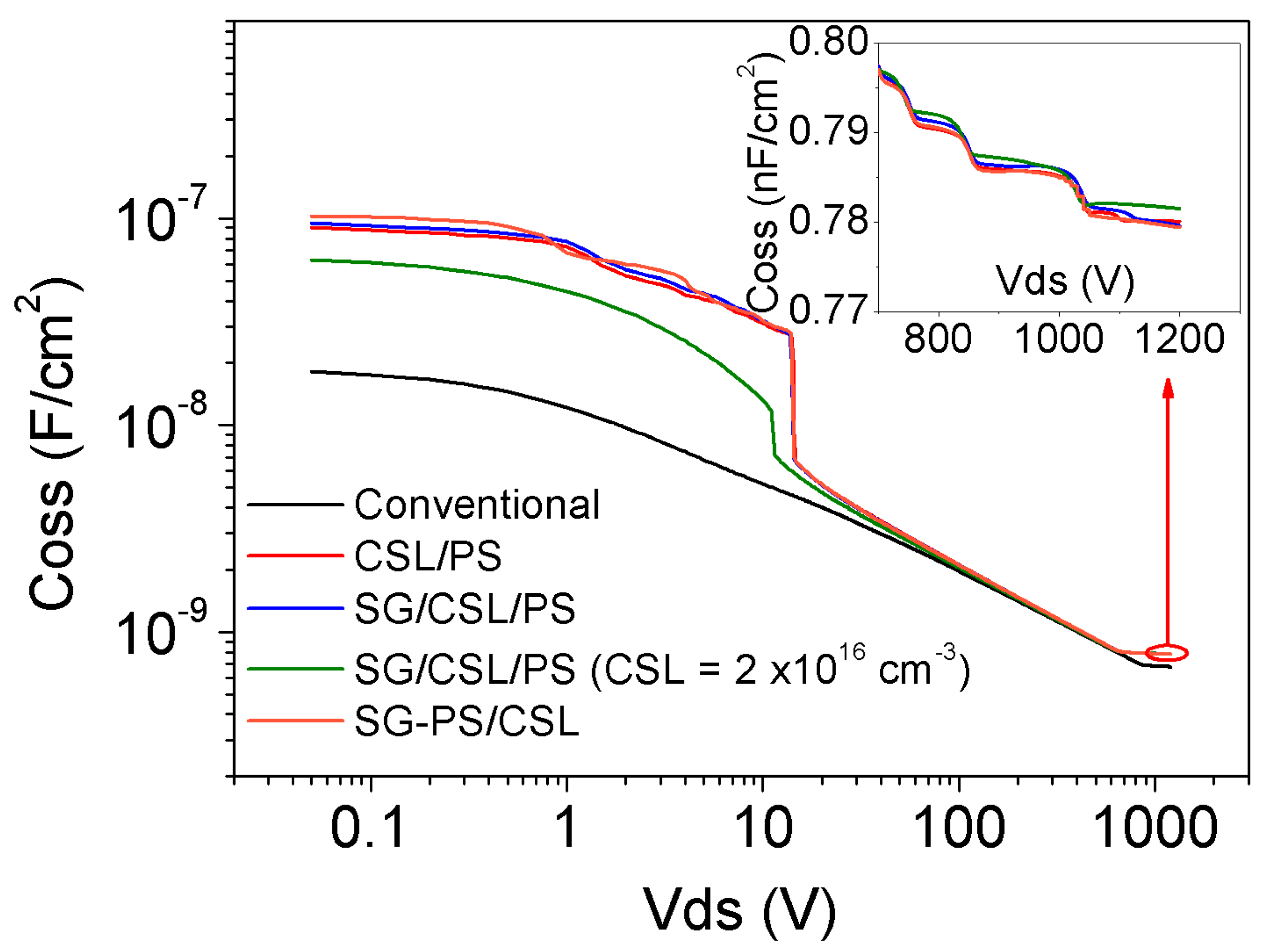

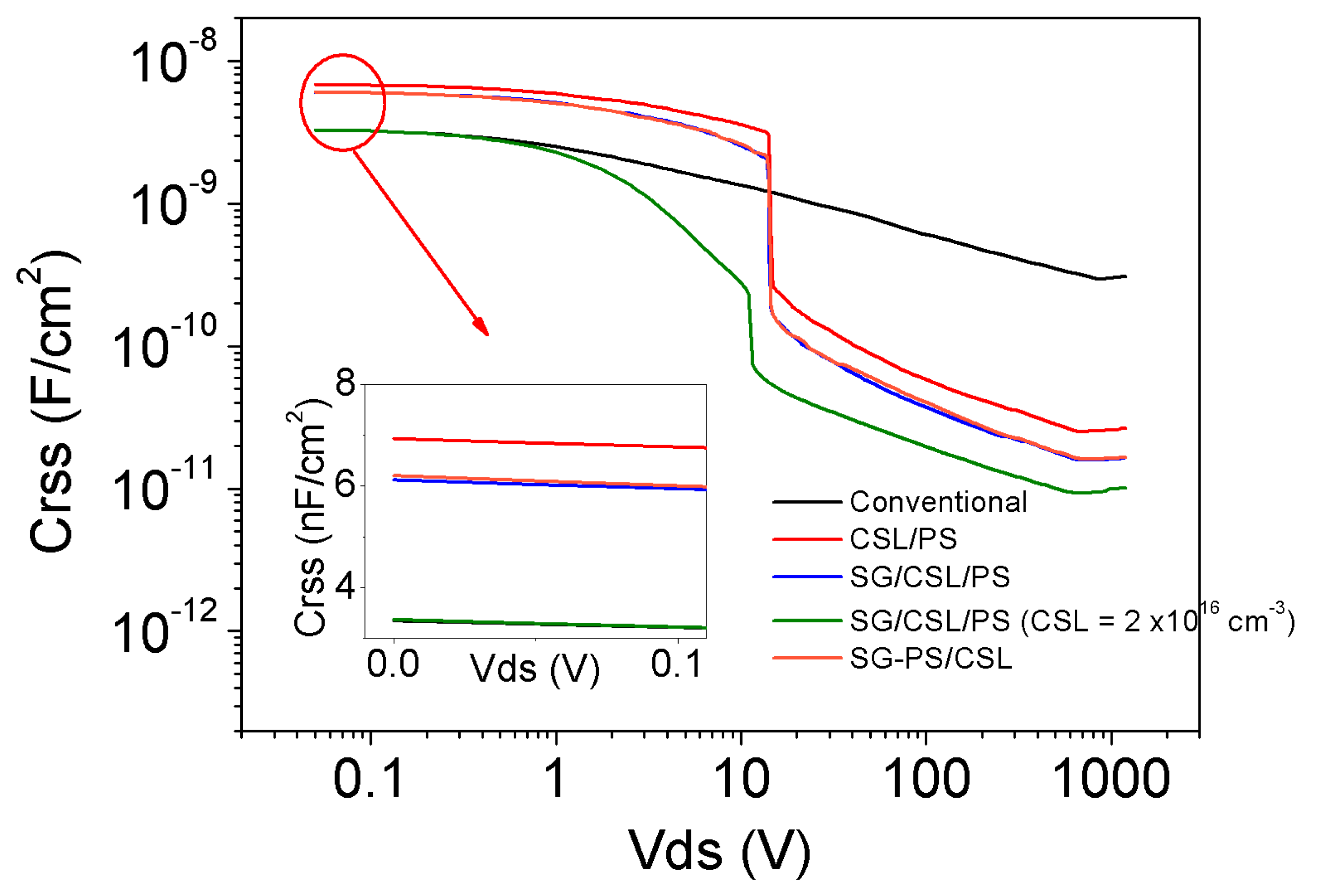

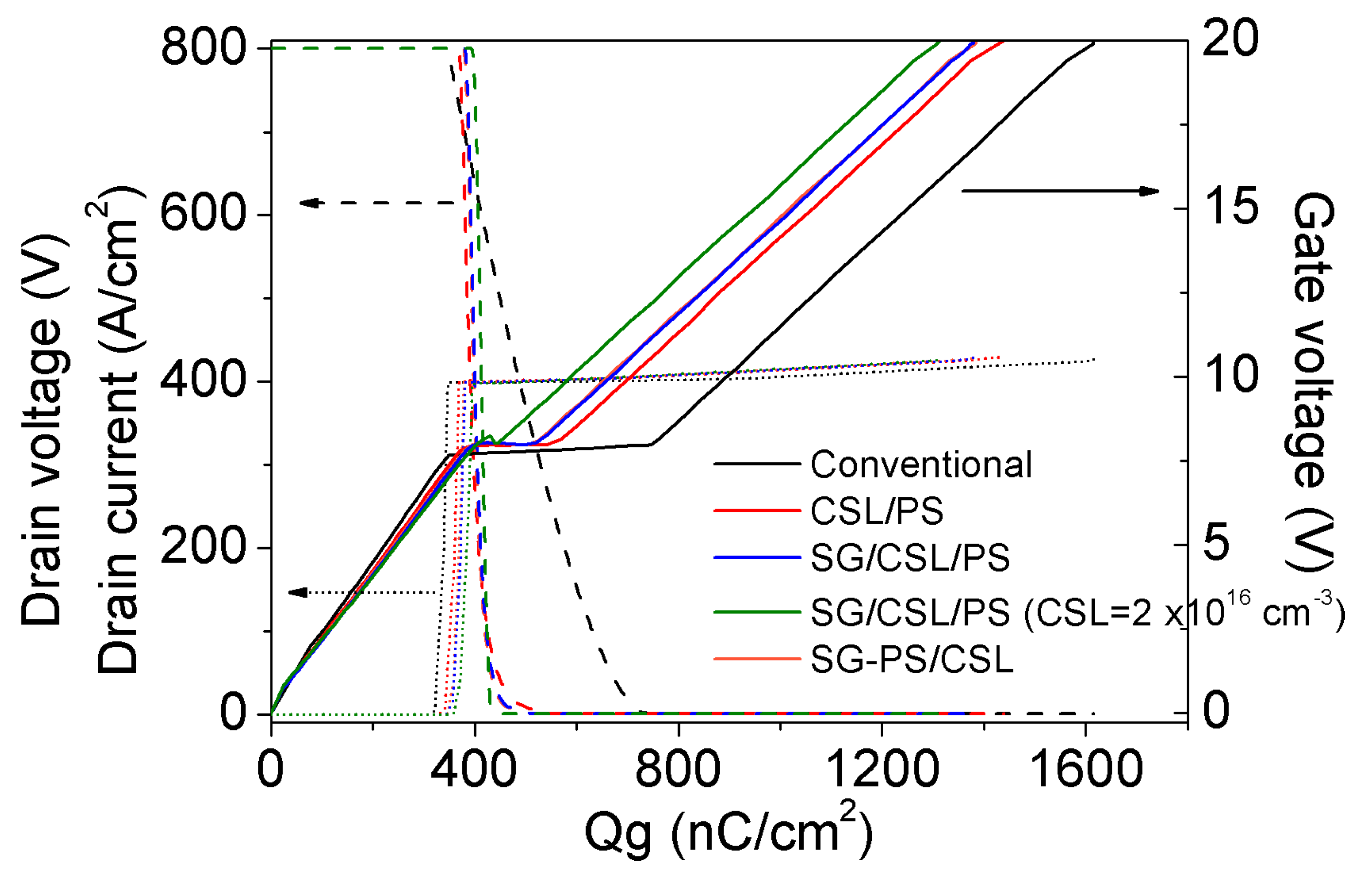

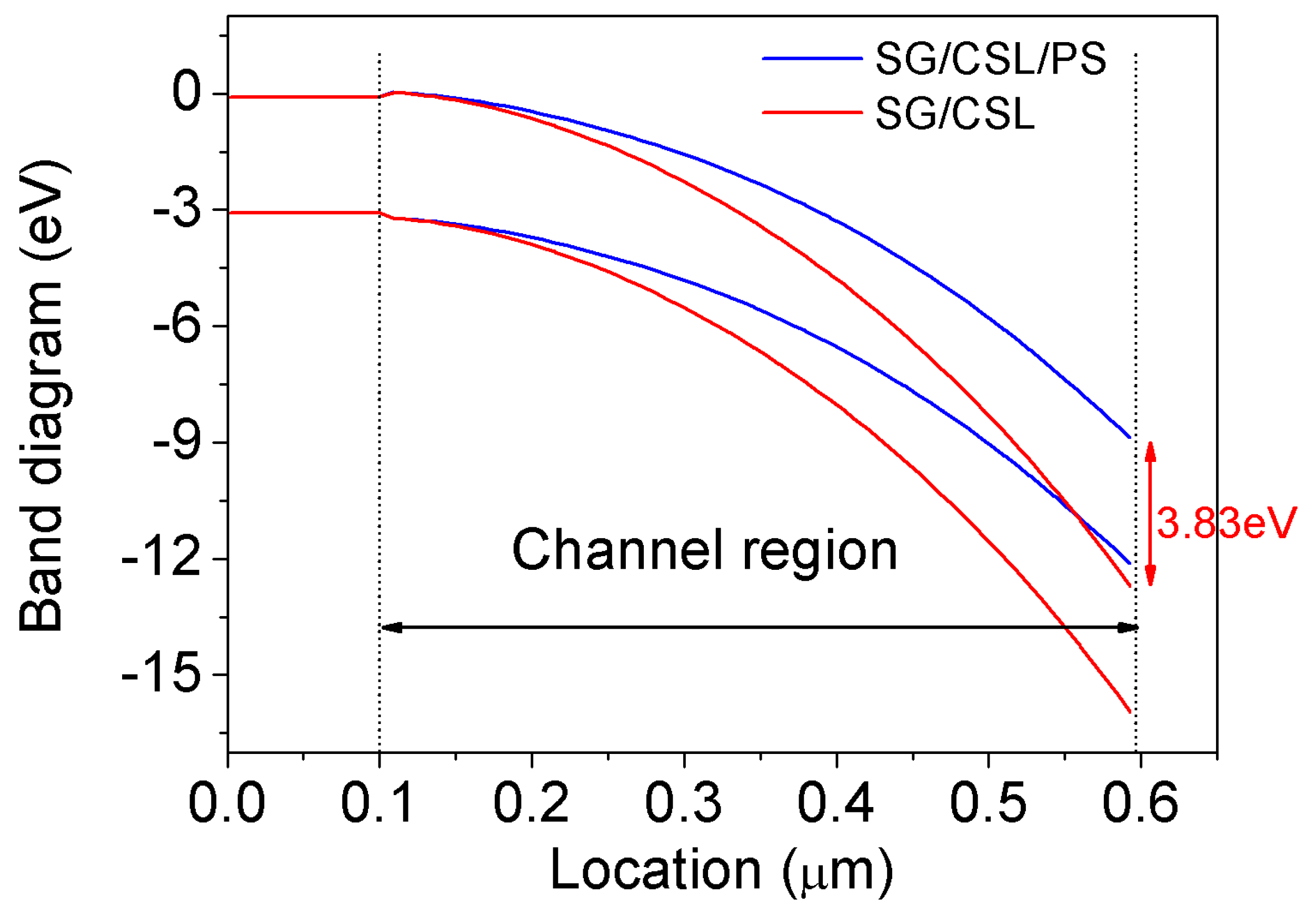

3. AC and Switching Characteristics

4. Short-Circuit Capability

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; John Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Cheng, L.; Agarwal, A.K.; Dhar, S.; Ryu, S.; Palmour, J.W. Static performance of 20 A, 1200 V 4H-SiC power MOSFETs at temperatures of −187 °C to 300 °C. J. Electron. Mater. 2012, 41, 910–914. [Google Scholar] [CrossRef]

- Yano, H.; Hatayama, T.; Fuyuki, T. POCl3 annealing as a new method for improving 4H-SiC MOS device performance. ECS Trans. 2013, 50, 257–265. [Google Scholar] [CrossRef]

- Nanen, Y.; Kato, M.; Suda, J.; Kimoto, T. Effects of nitridation on 4H-SiC MOSFETs fabricated on various crystal faces. IEEE Trans. Electron Devices 2013, 60, 1260–1262. [Google Scholar] [CrossRef]

- Ryu, S.; Krishnaswami, S.; O’Loughlin, M.; Richmond, J.; Agarwal, A.; Palmour, J.; Hefner, A.R. 10-kV, 123-mΩ∙cm2 4H-SiC Power DMOSFETs. IEEE Electron Device Lett. 2004, 25, 556–558. [Google Scholar] [CrossRef]

- Saha, A.; Cooper, J.A. A 1-kV 4H-SiC power DMOSFET optimized for low on-resistance. IEEE Trans. Electron Devices 2007, 54, 2786–2791. [Google Scholar] [CrossRef]

- Nakamura, T.; Nakano, Y.; Aketa, M.; Nakamura, R.; Mitani, S.; Sakairi, H.; Yokotsuji, Y. High performance SiC trench devices with ultra-low Ron. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011. [Google Scholar]

- Rashid, S.J.; Mihaila, A.; Udrea, F.; Amaratunga, G. Trench oxide protection for 10 kV 4H-SiC trench MOSFETs. In Proceedings of the Fifth International Conference on Power Electronics and Drive Systems, Singapore, 17–20 November 2003. [Google Scholar]

- Li, Y.; Cooper, J.A.; Capano, M.A. High-Voltage (3 kV) UMOSFETs in 4H-SiC. IEEE Trans. Electron Devices 2002, 49, 972–975. [Google Scholar] [CrossRef]

- Peters, D.; Siemieniec, R.; Aichinger, T.; Basler, T.; Esteve, R.; Bergner, W.; Kueck, D. Performance and ruggedness of 1200V SiC-Trench-MOSFET. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017. [Google Scholar]

- Barkhordarian, V. Application Note AN-1084, Infineon/IR. Available online: https://www.infineon.com/dgdl/an-1084.pdf?fileId=5546d462533600a401535595840d101e (accessed on 24 December 2019).

- Ebihara, Y.; Ichimura, A.; Mitani, S.; Noborio, M.; Takeuchi, Y.; Mizuno, S.; Yamamoto, T.; Tsuruta, K. Deep-P encapsulated 4H-SiC trench MOSFETs with ultra low RonQgd. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018. [Google Scholar]

- Wei, J.; Zhang, M.; Jiang, H.; Wang, H.; Chen, K.J. Dynamic degradation in SiC trench MOSFET with a floating p-shield revealed with numerical simulations. IEEE Trans. Electron. Devices 2017, 64, 2592–2598. [Google Scholar] [CrossRef]

- Jiang, J.-Y.; Huang, C.-F.; Wu, T.-L.; Zhao, F. Simulation Study of 4H-SiC Trench MOSFETs with Various Gate Structures. In Proceedings of the Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019. [Google Scholar]

- Agarwal, A.K.; Siergiej, R.R.; Seshadri, S.; White, M.H.; McMullin, P.G.; Burk, A.A.; Rowland, L.B.; Brandt, C.D.; Hopkins, R.H. A critical look at the performance advantages and limitations of 4H-SiC power UMOSFET structures. In Proceedings of the 8th International Symposium on Power Semiconductor Devices and ICs, Maui, HI, USA, 23 May 1996. [Google Scholar]

- Tanaka, R.; Kagawa, Y.; Fujiwara, N.; Sugawara, K.; Fukui, Y.; Miura, N.; Imaizumi, M.; Yamakawa, S. Impact of grounding the bottom oxide protection layer on the short-circuit ruggedness of 4H-SiC trench MOSFETs. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014. [Google Scholar]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: Berlin/Heidelberg, Germany, 2008. [Google Scholar]

- Idir, N.; Bausiere, R.; Franchaud, J.J. Active gate voltage control of turn-on di/dt and turn-off dv/dt in insulated gate transistors. IEEE Trans. Power Electron. 2006, 21, 849–855. [Google Scholar] [CrossRef]

- Matin, M.; Saha, A.; Cooper, J.A. A self-aligned process for high-voltage, short-channel vertical DMOSFETs in 4H-SiC. IEEE Trans. Electron Devices 2004, 51, 1721–1725. [Google Scholar] [CrossRef]

- Noborio, M.; Kanzaki, Y.; Suda, J.; Kimoto, T. Experimental and theoretical investigations on short-channel effects in 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2005, 52, 1954–1962. [Google Scholar] [CrossRef]

- Otsuki, M.; Onozawa, Y.; Kanemaru, H.; Seki, Y.; Matsumoto, T. A study on the short-circuit capability of field-stop IGBTs. IEEE Trans. Electron Devices 2003, 50, 1525–1531. [Google Scholar] [CrossRef]

- Knoll, L.; Mihaila, A.; Kranz, L.; Bellini, M.; Wirths, S.; Bianda, E.; Papadopoulos, C.; Rahimo, M. Dynamic switching and short circuit capability of 6.5kV silicon carbide MOSFETs. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018. [Google Scholar]

- Eikyu, K.; Sakai, A.; Matsuura, H.; Nakazawa, Y.; Akiyama, Y.; Yamaguchi, Y.; Inuishi, M. On the scaling limit of the Si-IGBTs with very narrow mesa structure. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech, 12–16 June 2016. [Google Scholar]

- Tanaka, M.; Nakagawa, A. Conductivity modulation in the channel inversion layer of very narrow mesa IGBT. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017. [Google Scholar]

| Characteristics | Unit | Conventional | CSL/PS CSL = 9 × 1016 cm−3 | SG/CSL/PS CSL = 9 × 1016 cm−3 | SG/CSL/PS CSL = 2 × 1016 cm−3 | SG–PS/CSL CSL = 9 × 1016 cm−3 |

|---|---|---|---|---|---|---|

| RON,SP | mΩcm2 | 2.38 | 2.32 | 2.33 | 2.60 | 2.33 |

| Maximum Eox at 1600 V | MV/cm | 7.5 | 2.1 | 2.2 | 1.2 | 2.2 |

| Qgs | nC/cm2 | 339 | 360 | 374 | 436 | 371 |

| Qgd | nC/cm2 | 408 | 209 | 149 | 29 | 149 |

| Ciss at 800 V | nF/cm2 | 61.86 | 64.26 | 65.63 | 69.21 | 65.72 |

| Coss at 800 V | pF/cm2 | 714 | 790 | 791 | 792 | 790 |

| Crss at 800 V | pF/cm2 | 299 | 25 | 16 | 9 | 16 |

| RON x QGD | mΩnC | 971 | 485 | 347 | 75 | 347 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, J.-Y.; Wu, T.-L.; Zhao, F.; Huang, C.-F. Numerical Study of 4H-SiC UMOSFETs with Split-Gate and P+ Shielding. Energies 2020, 13, 1122. https://doi.org/10.3390/en13051122

Jiang J-Y, Wu T-L, Zhao F, Huang C-F. Numerical Study of 4H-SiC UMOSFETs with Split-Gate and P+ Shielding. Energies. 2020; 13(5):1122. https://doi.org/10.3390/en13051122

Chicago/Turabian StyleJiang, Jheng-Yi, Tian-Li Wu, Feng Zhao, and Chih-Fang Huang. 2020. "Numerical Study of 4H-SiC UMOSFETs with Split-Gate and P+ Shielding" Energies 13, no. 5: 1122. https://doi.org/10.3390/en13051122

APA StyleJiang, J.-Y., Wu, T.-L., Zhao, F., & Huang, C.-F. (2020). Numerical Study of 4H-SiC UMOSFETs with Split-Gate and P+ Shielding. Energies, 13(5), 1122. https://doi.org/10.3390/en13051122