Analysis of the DC Fault Current Limiting Characteristics of a DC Superconducting Fault Current Limiter Using a Transformer

Abstract

:1. Introduction

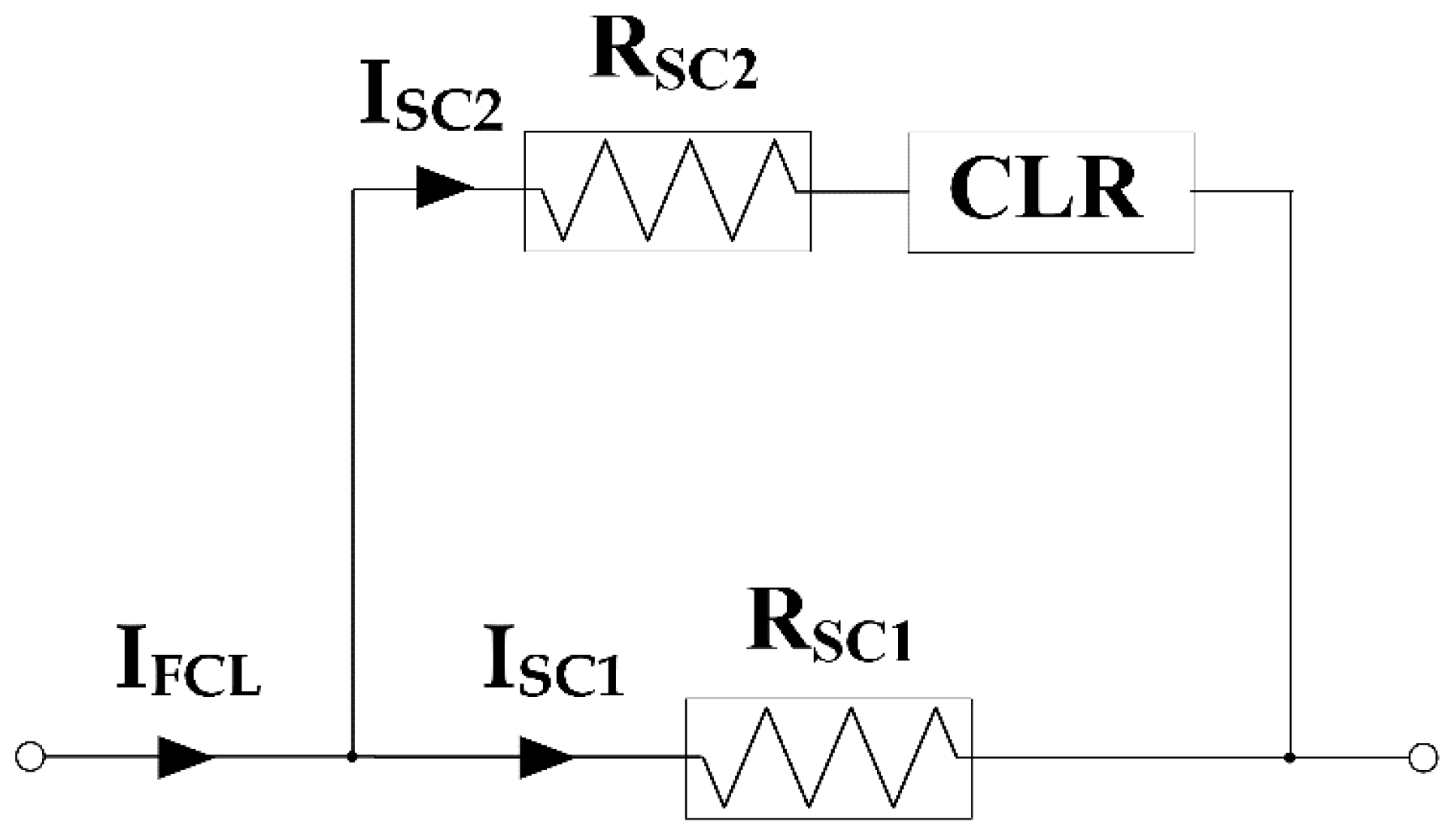

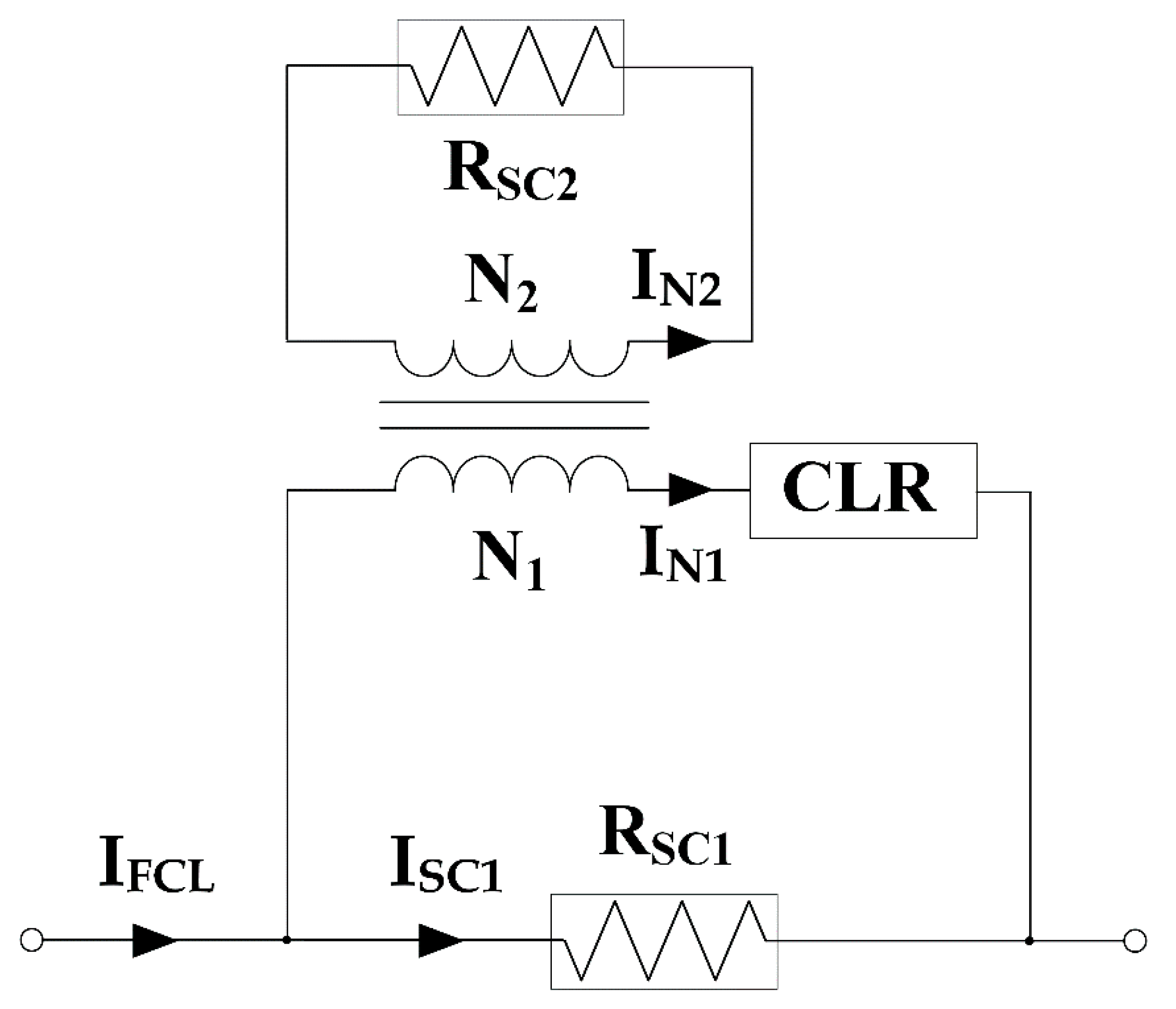

2. Principle of Operation and Experiment of the DC SFCL

2.1. Configuration and Principle of Operation

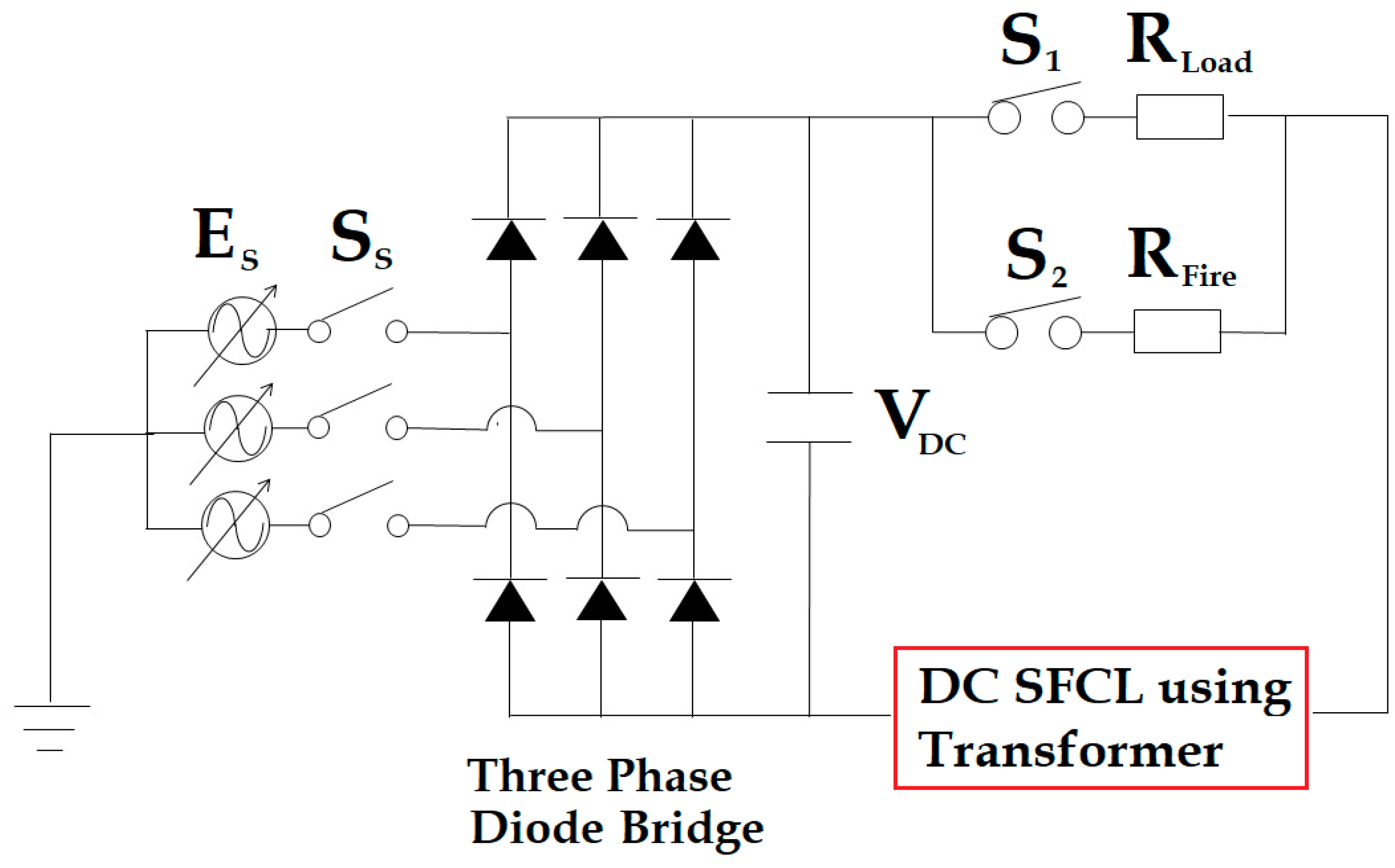

2.2. Experimental Structure and Method

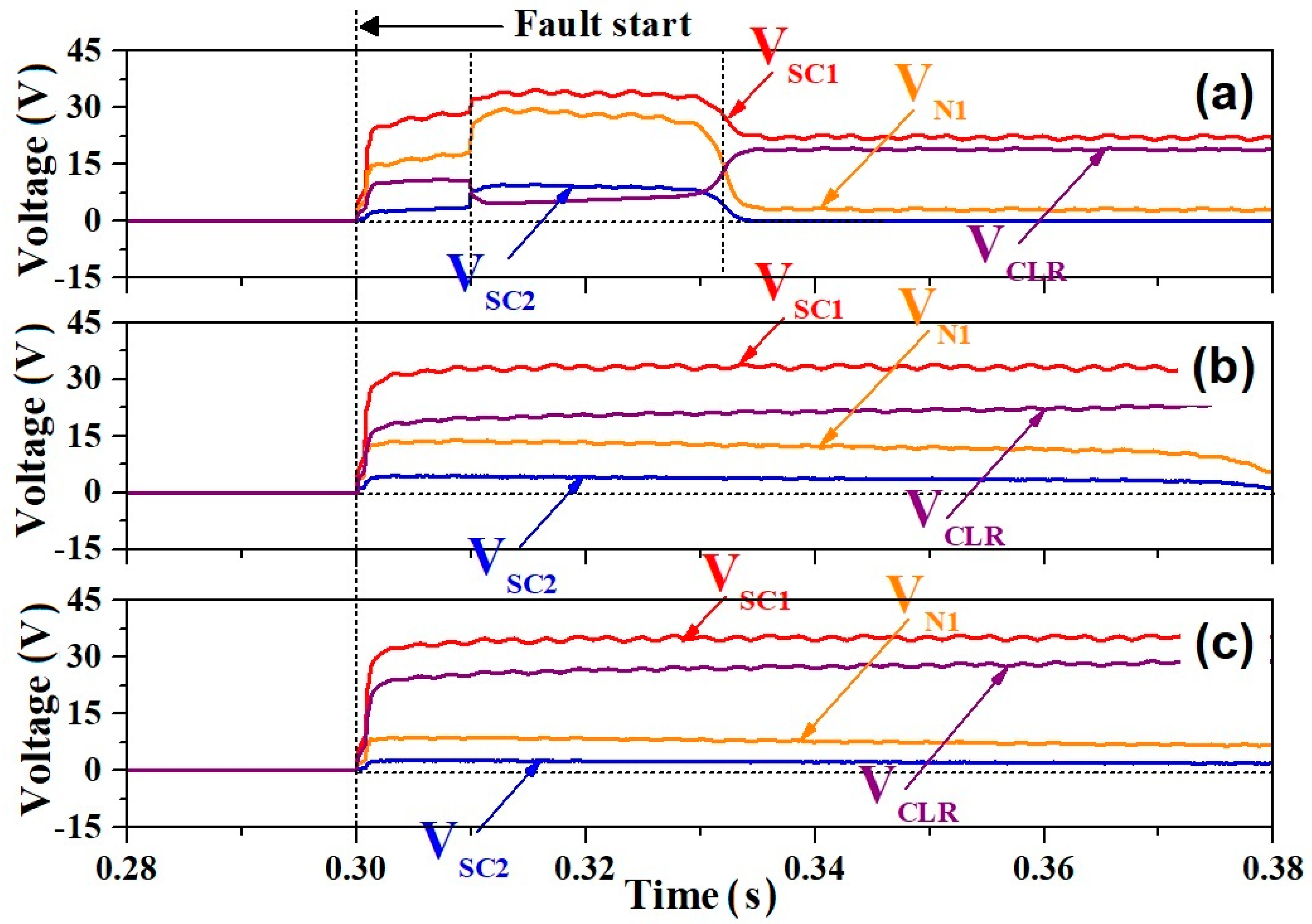

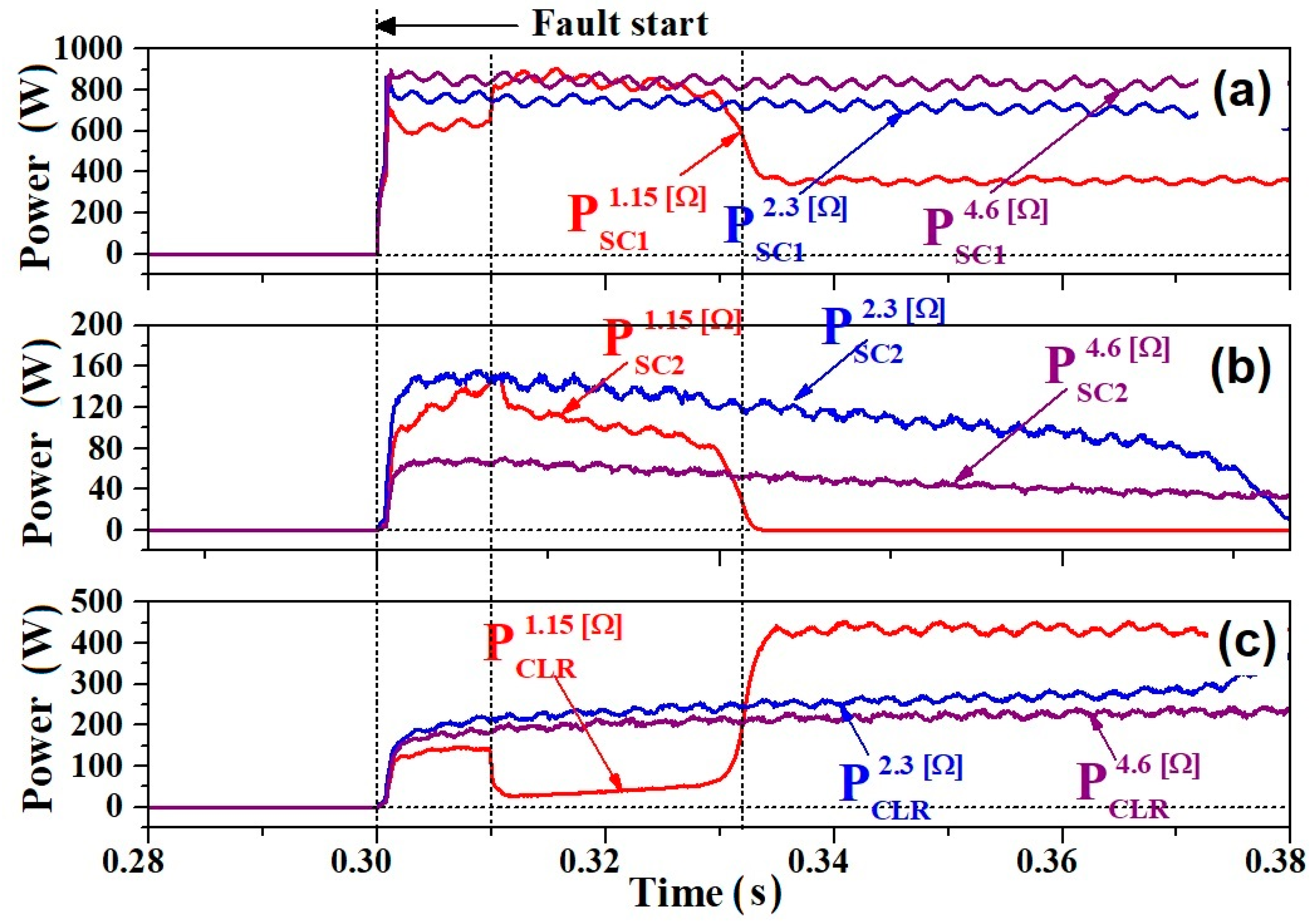

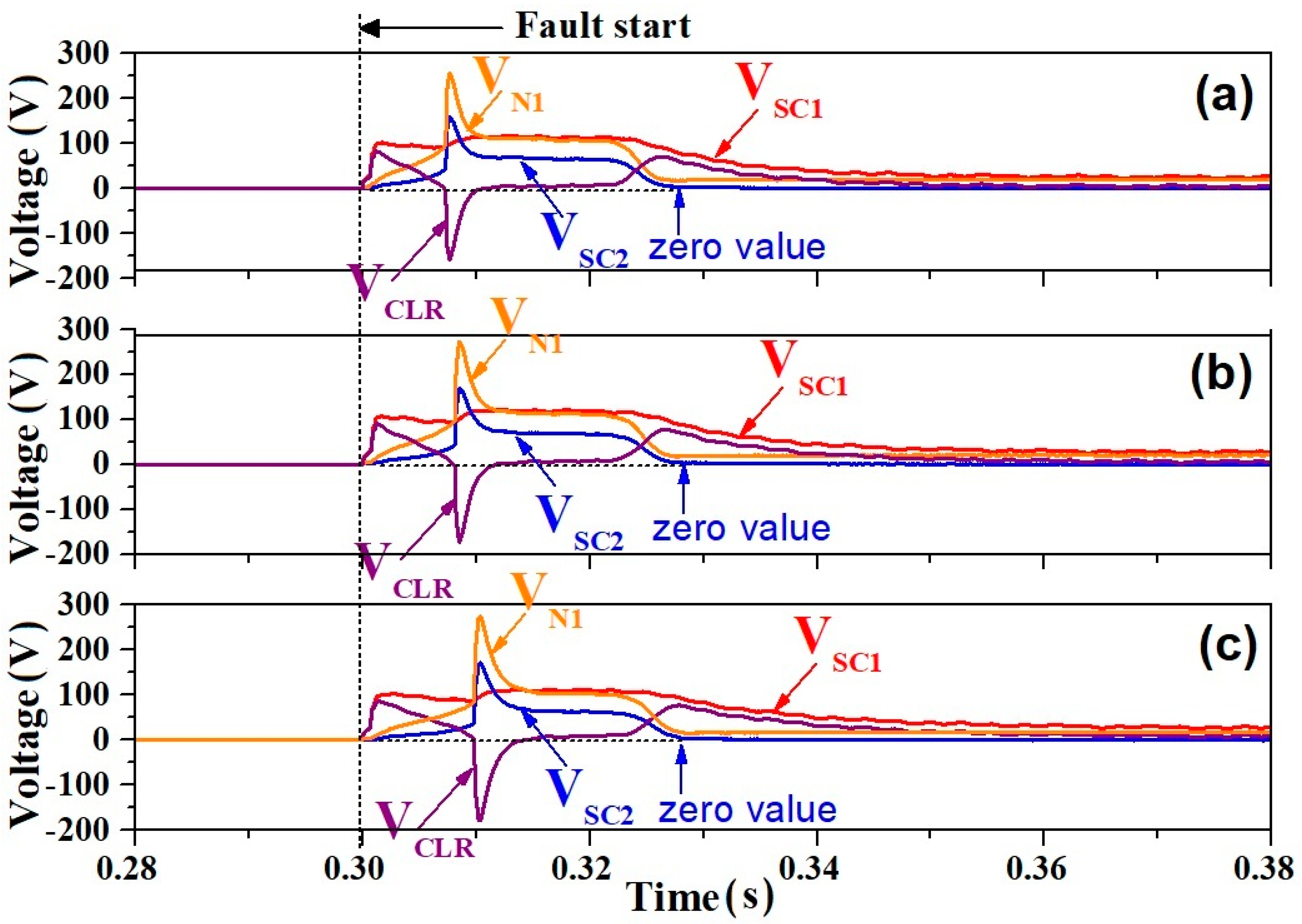

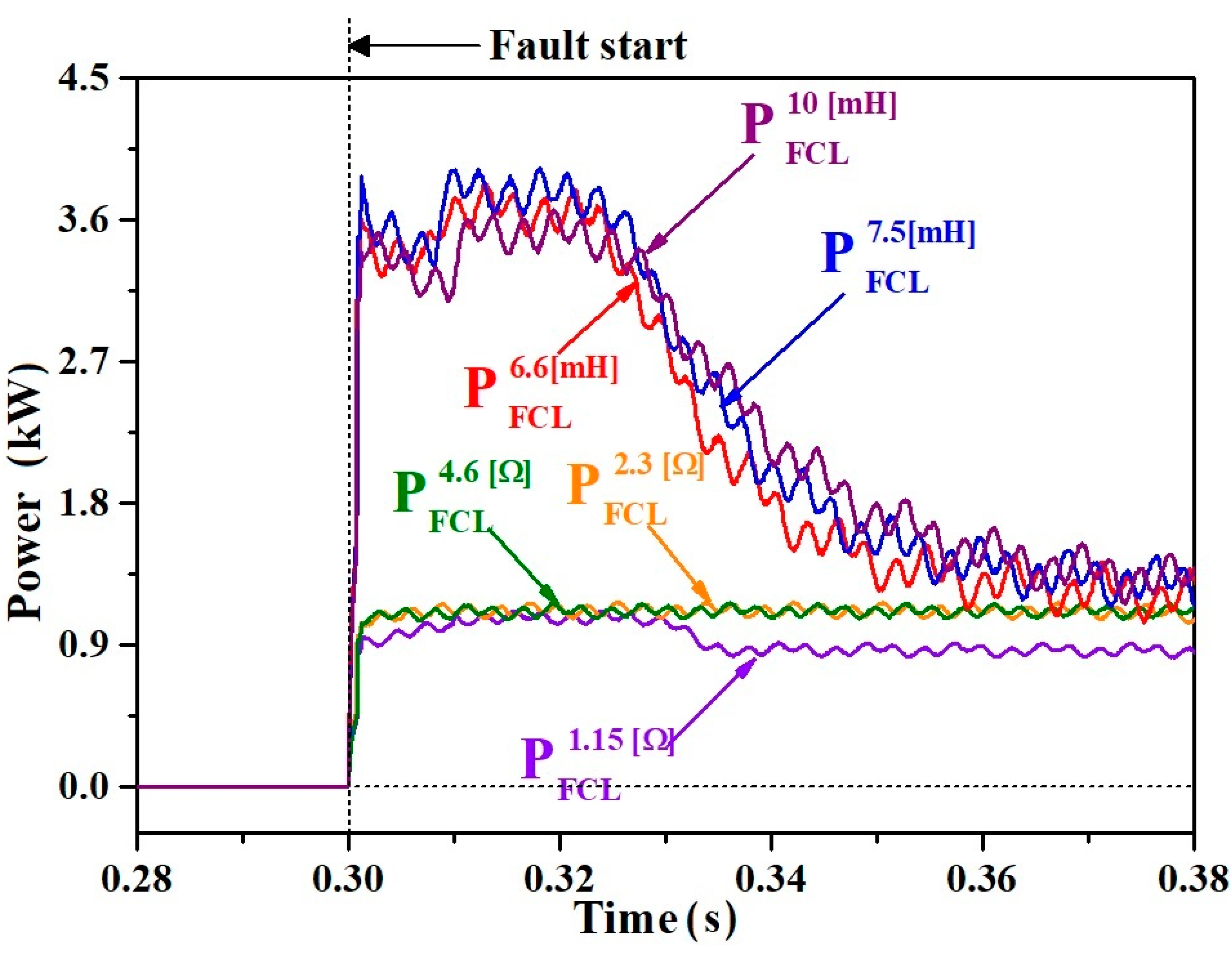

3. Result and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhou, Y.; Zhuojiang, D.; Fenwang, Y. The Development of HVDC Transmission System. In Proceedings of the Digital Manufacturing and Automation (ICDMA), 2012 Third International Conference, Guilin, China, 31 July–2 August 2012; pp. 907–910. [Google Scholar]

- Okba, M.H.; Saied, M.H.; Mostafa, M.Z.; Abdel-Moneim, T.M. High voltage direct current transmission—A review, part I. In Proceedings of the 2012 IEEE Energytech, Cleveland, OH, USA, 30–31 May 2012; pp. 1–7. [Google Scholar]

- Moon, H.B. High Voltage Direct Current Technology Trends. J. Electr. World Mon. Mag. Korea Electr. Assoc. 2009, 392, 29–37. [Google Scholar]

- Ganhao, Z. Study on DC Circuit Breaker. In Proceedings of the 2014 Fifth International Conference on Intelligent Systems Design and Engineering Applications (ISDEA), Hunan, China, 15–16 June 2014; pp. 942–945. [Google Scholar]

- Bae, S.H.; Kim, H.R.; Park, J.W.; Lee, S.H. A Study on SFCL with IGBT Based DC Circuit Breaker in Electric Power Grid. J. Elect. Eng. Technol. 2017, 12, 1805–1811. [Google Scholar]

- Lim, S.H.; You, I.K.; Kim, J.C. Study on Peak Current Limiting Characteristics of a Flux-Lock Type SFCL Using Its Third Winding. IEEE Trans. Appl. Supercond. 2011, 21, 1275–1279. [Google Scholar] [CrossRef]

- Ko, S.C.; Lim, S.H. Analysis on Magnetizing Characteristics Due to Peak Fault Current Limiting Operation of a Modified Flux-Lock-Type SFCL With Two Magnetic Paths. IEEE Trans. Appl. Supercond. 2016, 26, 5601605. [Google Scholar] [CrossRef]

- Lee, B.W.; Park, K.B.; Sim, J.; Oh, I.S.; Lee, H.G.; Kim, H.R.; Hyun, O.B. Design and Experiments of Novel Hybrid Type Superconducting Fault Current Limiters. IEEE Trans. Appl. Supercond. 2008, 18, 624–627. [Google Scholar] [CrossRef]

- Chen, Y.; Liu, X.; Sheng, J.; Cai, L.; Jin, Z.; Gu, J.; An, Z.; Yang, X.; Hong, Z. Design and Application of a Superconducting Fault Current Limiter in DC Systems. IEEE Trans. Appl. Supercond. 2014, 24, 5601305. [Google Scholar] [CrossRef]

- Liang, S.; Tang, Y.; Xia, Z.; Ren, L.; Chen, L.; Xu, Y.; Wang, Z.; Yan, S. Study on the Current Limiting Performance of a Novel SFCL in DC Systems. IEEE Trans. Appl. Supercond. 2017, 27, 5601106. [Google Scholar] [CrossRef]

- Lim, S.H.; Choi, H.-S.; Chung, D.-C.; Jeong, Y.-H.; Han, Y.-H.; Sung, T.-H.; Han, B.-S. Fault Current Limiting Characteristics of Resistive Type SFCL using a Transformer. IEEE Trans. Appl. Supercond. 2005, 15, 2055–2058. [Google Scholar] [CrossRef]

- Lim, S.H.; Cho, Y.S.; Choi, H.S.; Han, B.S. Improvement of Current Limiting Capability of HTSC Elements in Hybrid Type SFCL. IEEE Trans. Appl. Supercond. 2007, 17, 1807–1810. [Google Scholar] [CrossRef]

- Lim, S.T.; Ko, S.C.; Lim, S.H. Analysis on Current Limiting Characteristics of Transformer Type SFCL with Additionally Coupled Circuit. J. Elect. Eng. Technol. 2018, 13, 533–539. [Google Scholar]

- Lim, S.T.; Lim, S.H.; Han, T.H. Analysis on Operation Characteristics and Power Burdens of the Double Quench Trigger Type SFCLs. Prog. Supercond. Cryog. 2017, 19, 33–37. [Google Scholar]

- Lee, H.J.; Kim, J.S.; Lim, S.H.; Kim, J.C. Analysis on Operational Characteristics of Double Quench Flux Lock Type Superconducting Fault Current Limiter. IEEE Trans. Appl. Supercond. 2020, 30, 5600505. [Google Scholar]

- Lim, S.H. Study on Current Limiting Characteristics of SFCL with Two Trigger Current Levels. Physica C 2010, 445, 1631–1635. [Google Scholar] [CrossRef]

- Martini, L.; Bocchi, M.; Angeli, G.; Ascade, M.; Rossi, V.; Valzasina, A.; Ravetta, C.; Fratti, S.; Martino, E. Live Grid Field-Testing Final Results of the First Italian Superconducting Fault Current Limiter and Severe 3-Phase Fault Experience. IEEE Trans. Appl. Supercond. 2015, 25, 5600405. [Google Scholar] [CrossRef]

- Naoki, H.; Yuya, M.; Hiroki, K. Fault Current Limitation Coordination in Electric Power Grid with Superconducting Fault Current Limiters. IEEE Trans. Appl. Supercond. 2018, 28, 5602304. [Google Scholar]

- Hyun, O.B.; Yim, S.W.; Yu, S.D.; Yang, S.E.; Kim, W.S.; Kim, H.R.; Lee, G.H.; Sim, J.; Park, K.B. Long-Term Operation and Fault Tests of a 22.9 kV Hybrid SFCL in the KEPCO Test Grid. IEEE Trans. Appl. Supercond. 2011, 21, 2131–2134. [Google Scholar] [CrossRef]

- Kim, H.R.; Yang, S.E.; Yu, S.D.; Kim, H.; Park, B.J.; Han, Y.H.; Park, K.; Yu, J. Development and Grid Operation of Superconducting Fault Current Limiters in KEPCO. IEEE Trans. Appl. Supercond. 2014, 24, 5602504. [Google Scholar]

- Lee, H.S.; Jung, C.; Song, C.S.; Lee, S.R.; Yang, B.M.; Jang, G. Novel Protection Scheme with the Superconducting Power Cables and Fault Current Limiters through RTDS Test in Icheon Substation. IEEE Trans. Appl. Supercond. 2012, 22, 4705304. [Google Scholar]

- Han, Y.H.; Yang, S.; Kim, H.; Park, B.J.; Yu, J.; Kim, H.R.; In, S.; Hong, Y.J.; Yeom, H. Development and Long-Term Test of a Compact 154 kV SFCL. IEEE Trans. Appl. Supercond. 2019, 29, 5600106. [Google Scholar] [CrossRef]

| DC Test Circuit | Value | Unit |

|---|---|---|

| VDC | 110 | V |

| RLoad | 10 | Ω |

| RFire | 2.5 | Ω |

| Transformer and CLR | Value | Unit |

| Turns Ratio (N1/N2) | 3 | |

| CLR (RS) | 4.6/2.3/1.15 | Ω |

| CLR (LS) | 6.6/7.5/10 | mH |

| Superconducting elements (Rsc1 and Rsc2) | Value | Unit |

| Fabrication Type | Thin Film | |

| Material | YBCO | |

| Critical Current | 25 | A |

| Total Meander Line Length | 420 | mm |

| Line Width | 2 | mm |

| Thin Film Thickness | 0.3 | μm |

| Gold Layer Thickness | 0.2 | μm |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cho, K.-C.; Park, M.-K.; Lim, S.-H. Analysis of the DC Fault Current Limiting Characteristics of a DC Superconducting Fault Current Limiter Using a Transformer. Energies 2020, 13, 4210. https://doi.org/10.3390/en13164210

Cho K-C, Park M-K, Lim S-H. Analysis of the DC Fault Current Limiting Characteristics of a DC Superconducting Fault Current Limiter Using a Transformer. Energies. 2020; 13(16):4210. https://doi.org/10.3390/en13164210

Chicago/Turabian StyleCho, Kang-Cheol, Min-Ki Park, and Sung-Hun Lim. 2020. "Analysis of the DC Fault Current Limiting Characteristics of a DC Superconducting Fault Current Limiter Using a Transformer" Energies 13, no. 16: 4210. https://doi.org/10.3390/en13164210

APA StyleCho, K.-C., Park, M.-K., & Lim, S.-H. (2020). Analysis of the DC Fault Current Limiting Characteristics of a DC Superconducting Fault Current Limiter Using a Transformer. Energies, 13(16), 4210. https://doi.org/10.3390/en13164210