Multi-Objective Optimization of the Gate Driver Parameters in a SiC-Based DC-DC Converter for Electric Vehicles

Abstract

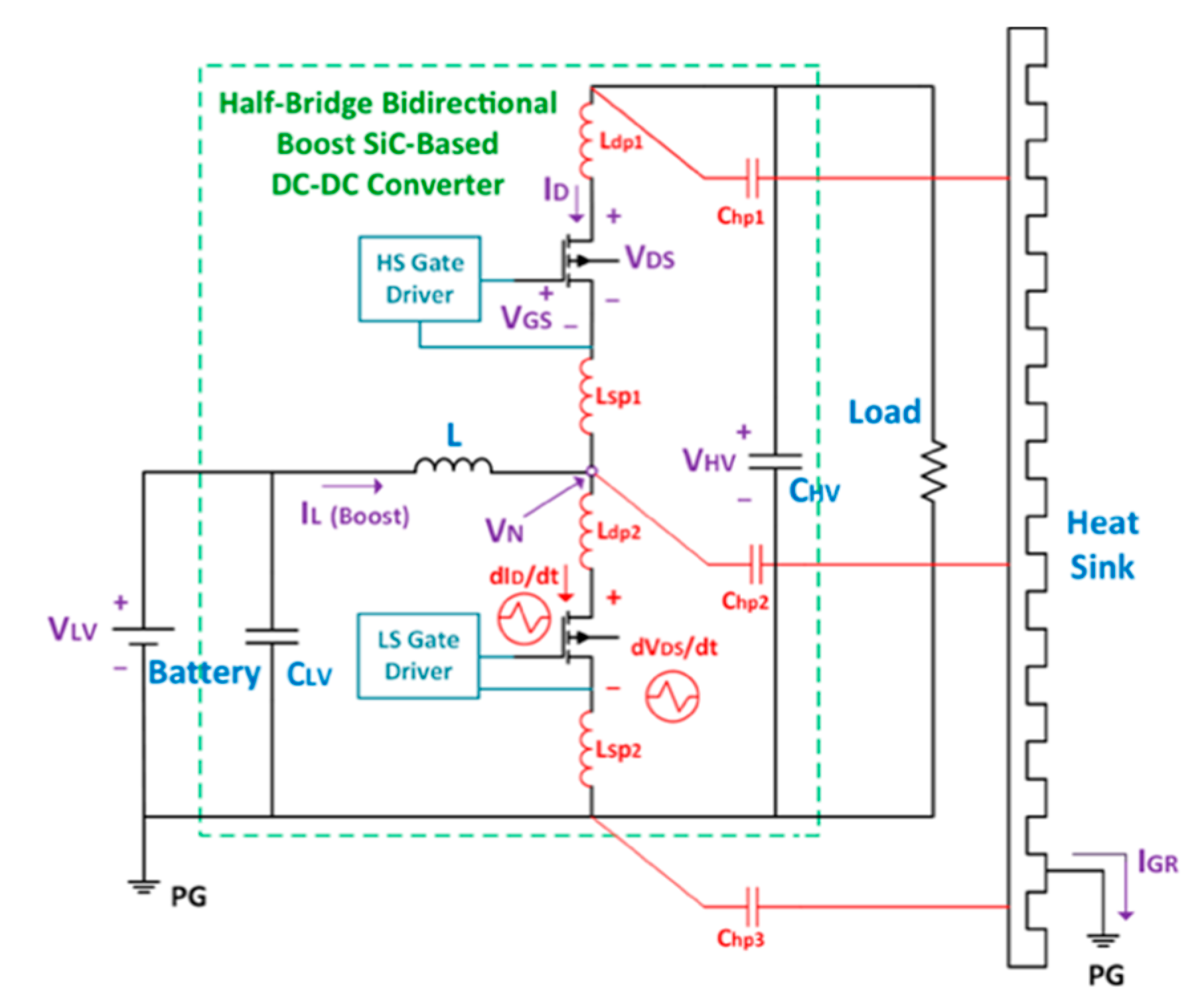

1. Introduction

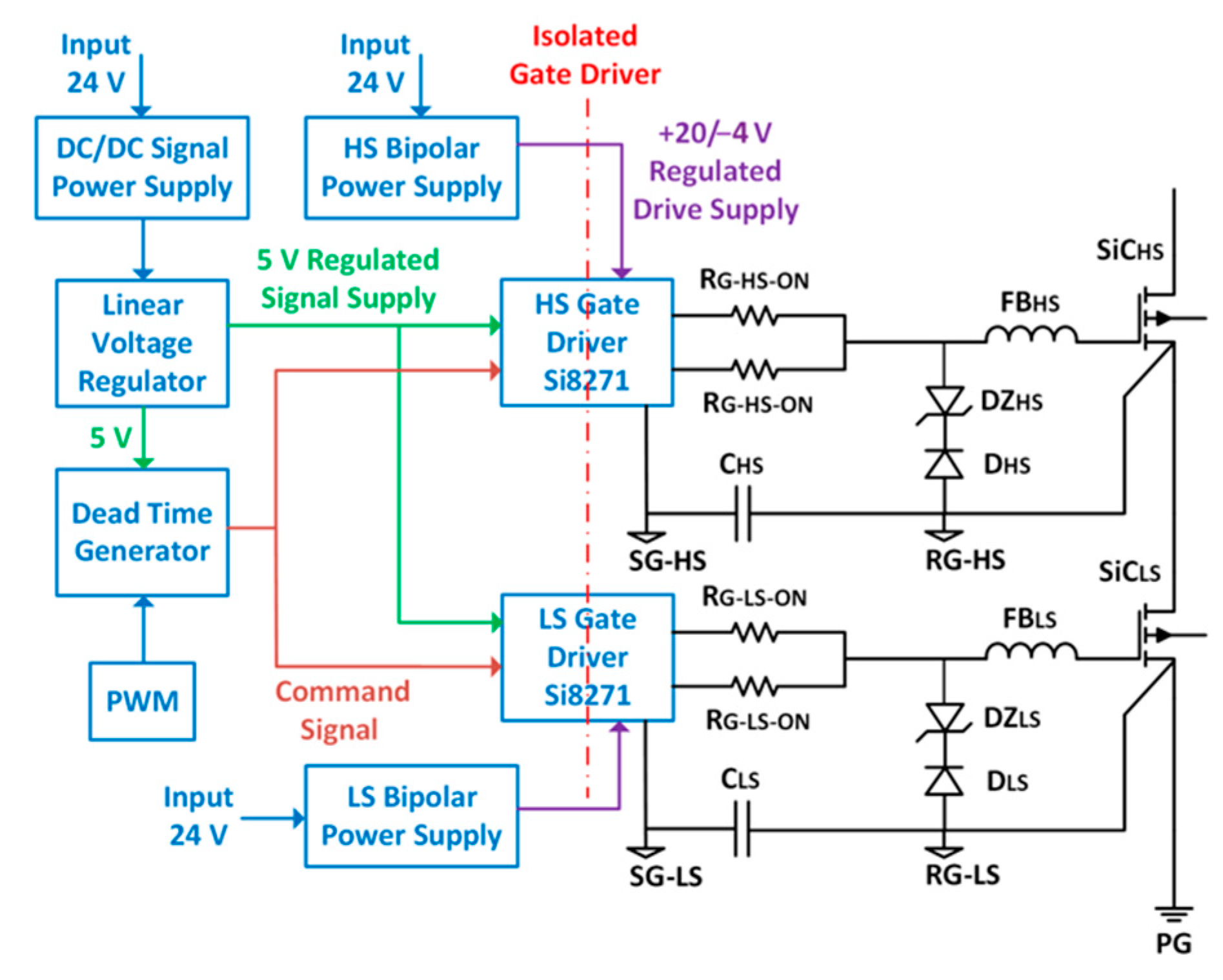

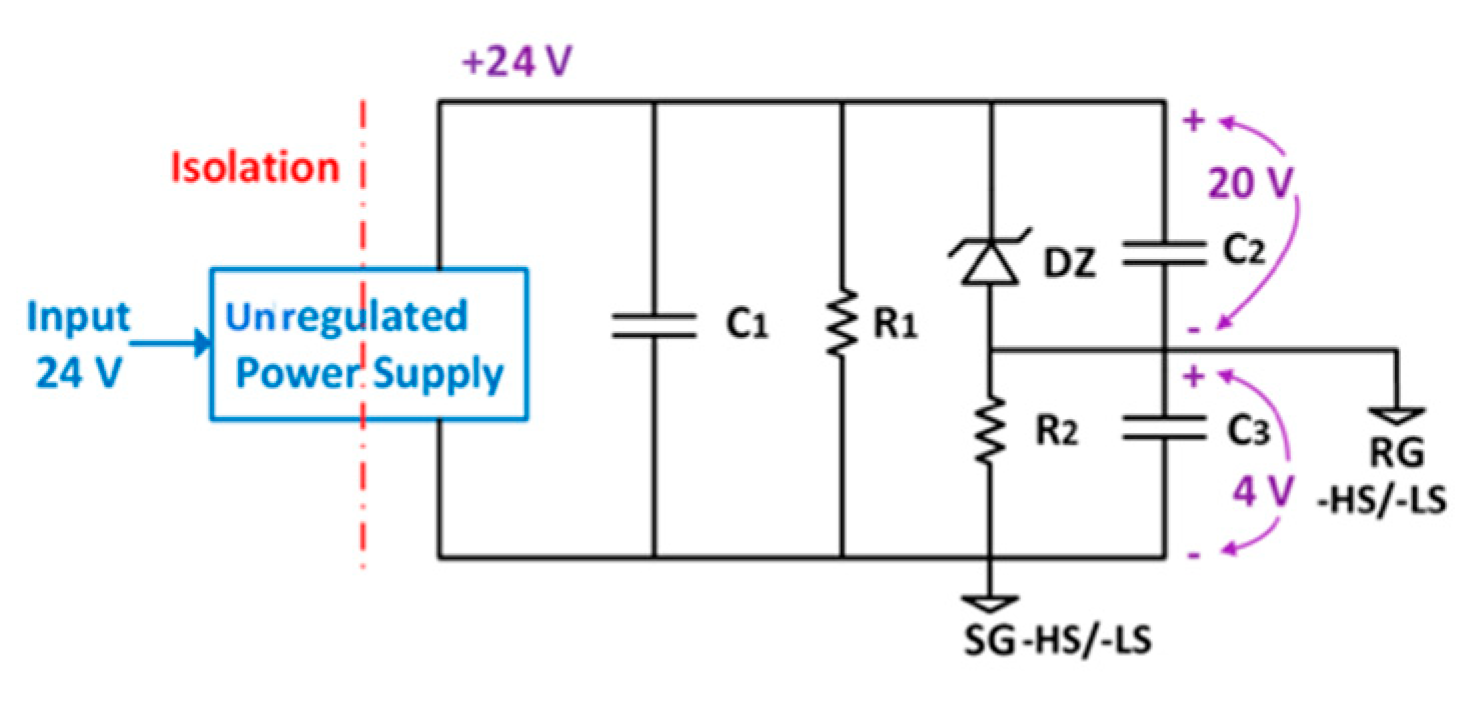

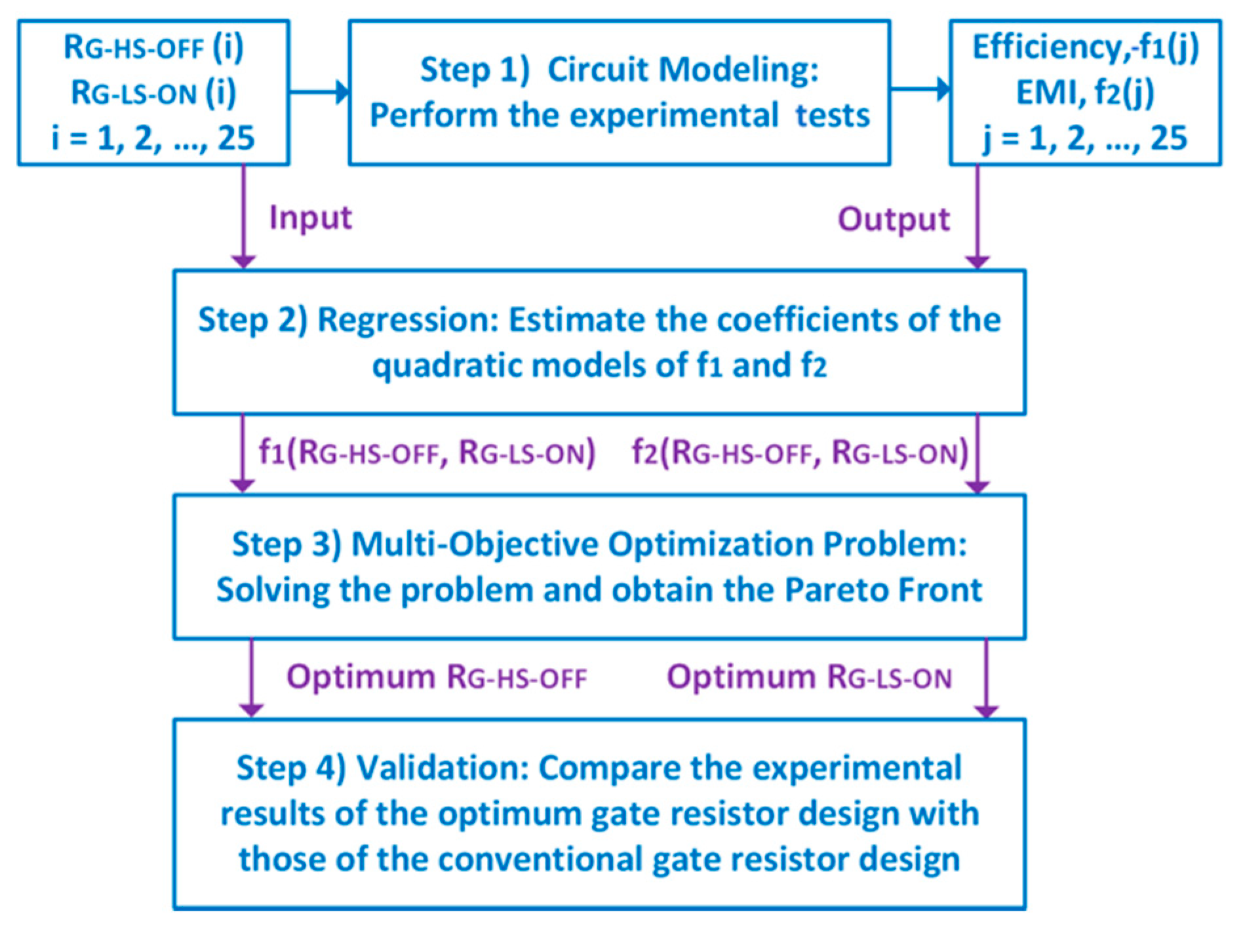

2. Multi-Objective Optimization of the Gate Driver Parameters

3. Experimental Results and Discussion

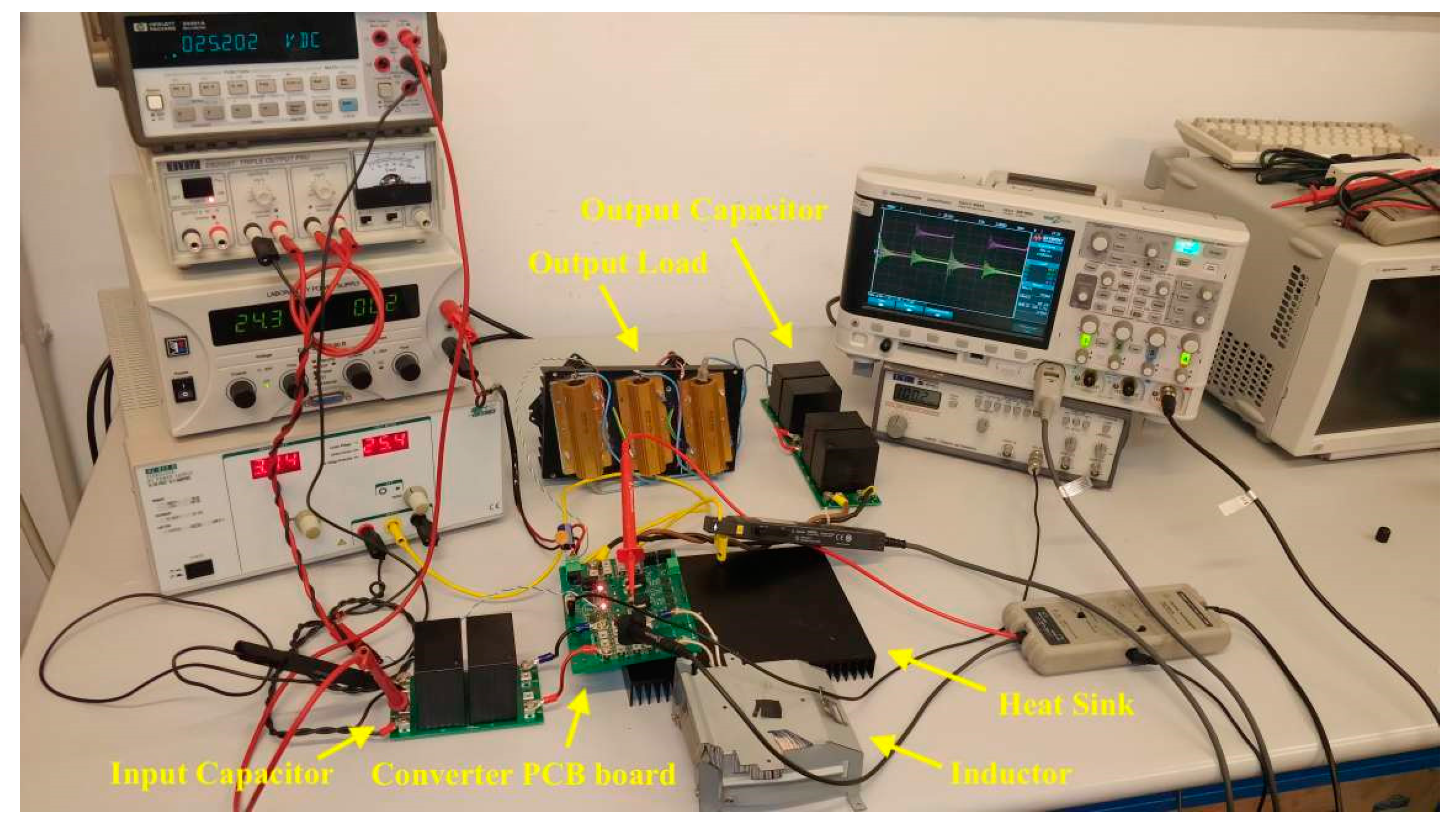

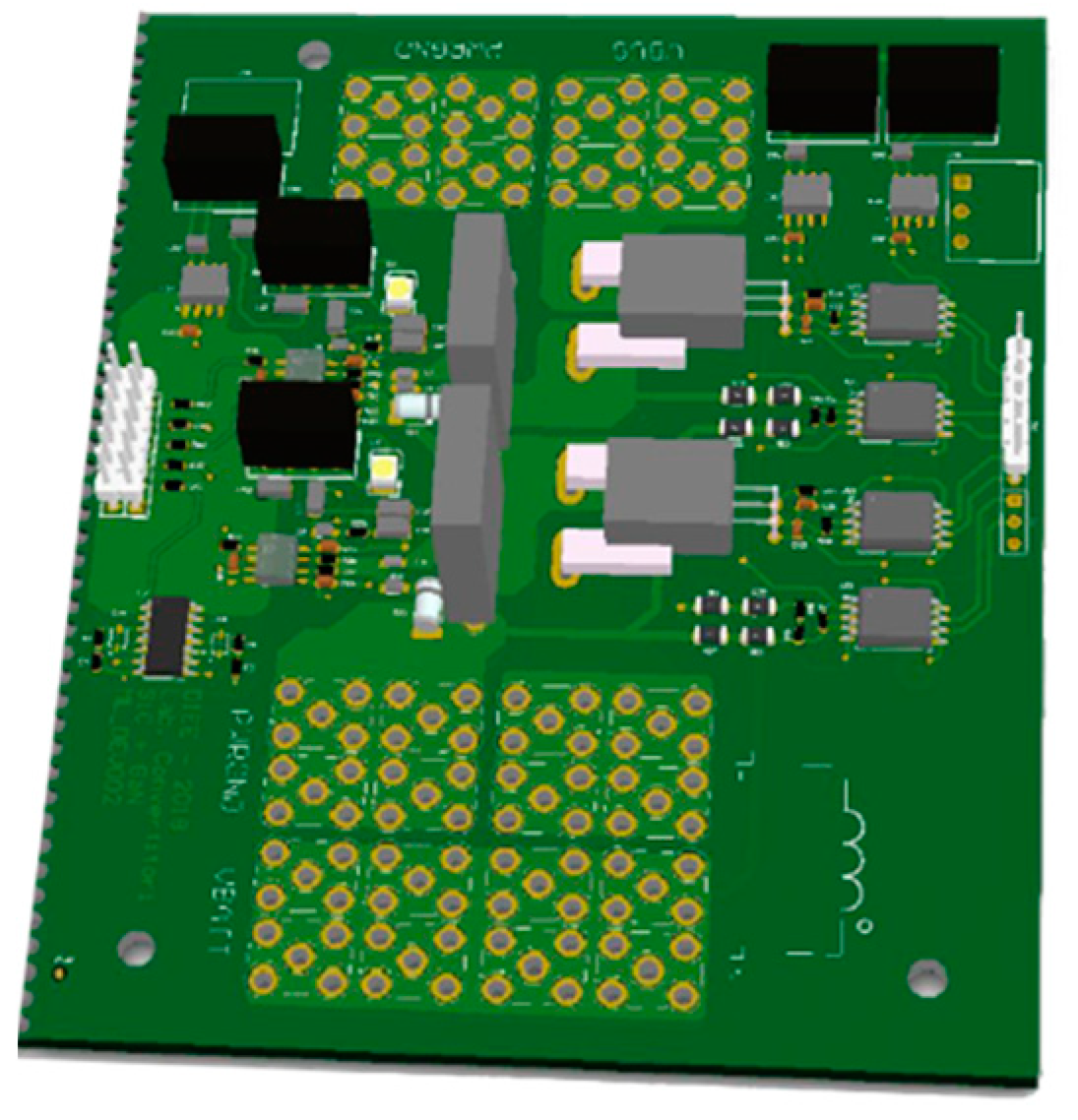

3.1. Test Set-up, Measurement Tools, and Test Conditions

3.2. Regression Functions

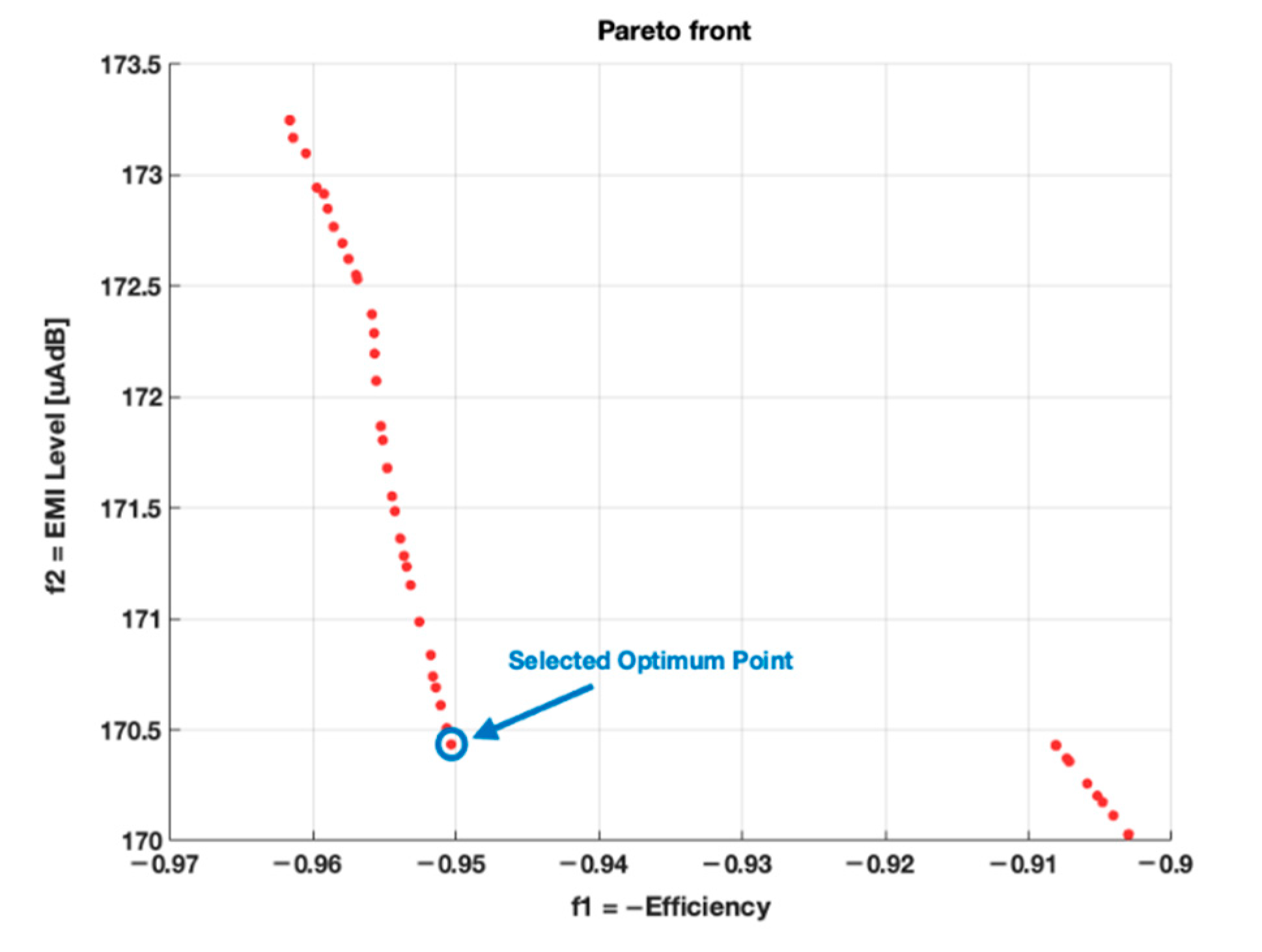

3.3. Multi-Objective Optimization Problem and Pareto Front

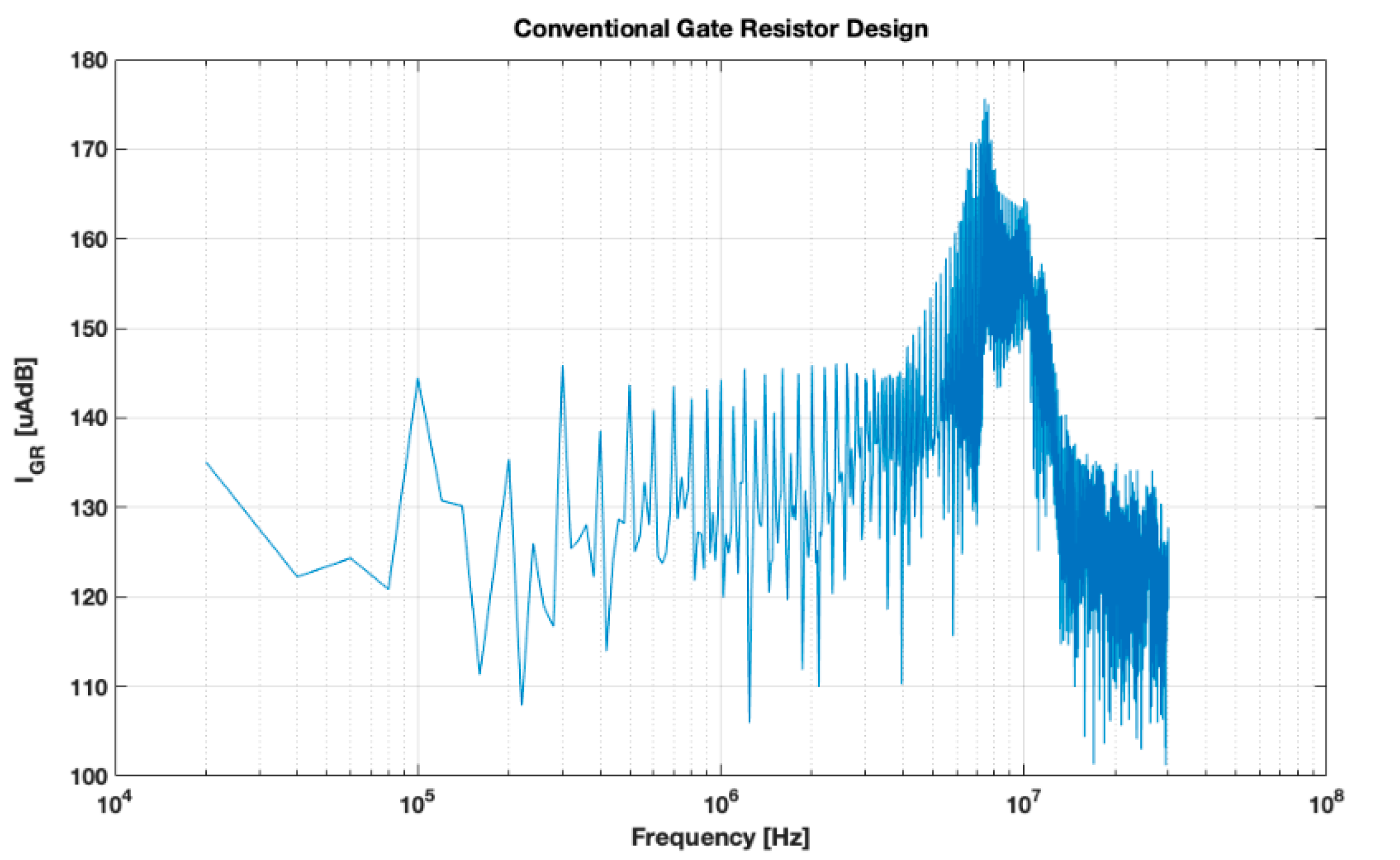

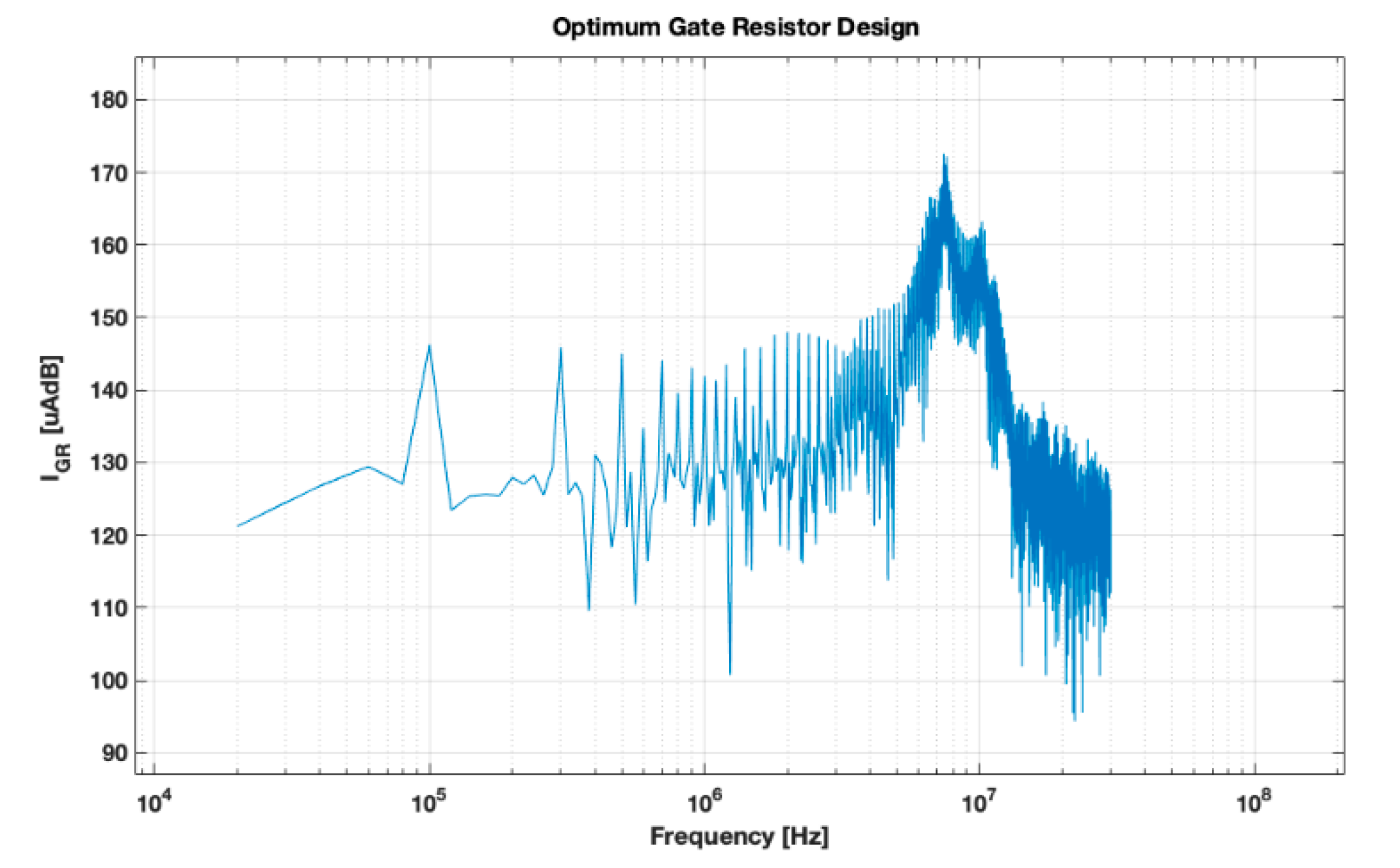

3.4. Optimum Gate Resistor Design

3.5. Discussion and Future Works

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Gerber, J.P.; Oliver, J.A.; Cordero, N.; Harder, T.; Cobos, J.; Hayes, M.; O’Mathuna, S.C.; Prem, E. Power Electronics Enabling Efficient Energy Usage: Energy Savings Potential and Technological Challenges. IEEE Trans. Power Elect. 2012, 27, 2338–2353. [Google Scholar] [CrossRef]

- Power Electronics Europe. Available online: https://www.power-mag.com/pdf/issuearchive/78.pdf (accessed on 13 November 2019).

- Khaligh, A.; Li, Z. Battery, Ultracapacitor, Fuel Cell, and Hybrid Energy Storage Systems for Electric, Hybrid Electric, Fuel Cell, and Plug-In Hybrid Electric Vehicles: State of the Art. IEEE Trans. Veh. Tech. 2010, 59, 2806–2814. [Google Scholar] [CrossRef]

- Emadi, A.; Lee, Y.J.; Rajashekara, K. Power Electronics and Motor Drives in Electric, Hybrid Electric, and Plug-In Hybrid Electric Vehicles. IEEE Trans. Ind. Elect. 2008, 55, 2237–2245. [Google Scholar] [CrossRef]

- Amjadi, Z.; Williamson, S.S. Power-Electronics-Based Solutions for Plug-in Hybrid Electric Vehicle Energy Storage and Management Systems. IEEE Trans. Ind. Elect. 2010, 57, 608–616. [Google Scholar] [CrossRef]

- Lai, J.; Nelson, D.J. Energy Management Power Converters in Hybrid Electric and Fuel Cell Vehicles. Proc. IEEE 2007, 95, 766–777. [Google Scholar] [CrossRef]

- Yilmaz, M.; Krein, P.T. Review of Battery Charger Topologies, Charging Power Levels, and Infrastructure for Plug-In Electric and Hybrid Vehicles. IEEE Trans. Power Elect. 2013, 28, 2151–2169. [Google Scholar] [CrossRef]

- Onar, O.C.; Kobayashi, J.; Khaligh, A. A Fully Directional Universal Power Electronic Interface for EV, HEV, and PHEV Applications. IEEE Trans. Power Elect. 2013, 28, 5489–5498. [Google Scholar] [CrossRef]

- Shen, Z.J.; Omura, I. Power Semiconductor Devices for Hybrid, Electric, and Fuel Cell Vehicles. Proc. IEEE 2007, 95, 778–789. [Google Scholar] [CrossRef]

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Elect. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Biela, J.; Schweizer, M.; Waffler, S.; Kolar, J.W. SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC–DC Converter Systems by SiC Power Semiconductors. IEEE Trans. Ind. Elect. 2011, 58, 2872–2882. [Google Scholar] [CrossRef]

- Whitaker, B.; Barkley, A.; Cole, Z.; Passmore, B.; Martin, D.; McNutt, T.R.; Lostetter, A.B.; Lee, J.S.; Shiozaki, K. A High-Density, High-Efficiency, Isolated On-Board Vehicle Battery Charger Utilizing Silicon Carbide Power Devices. IEEE Trans. Power Elect. 2014, 29, 2606–2617. [Google Scholar] [CrossRef]

- Wrzecionko, B.; Biela, J.; Kolar, J.W. SiC Power Semiconductors in HEVs: Influence of Junction Temperature on Power Density, Chip Utilization and Efficiency. In Proceedings of the 35th Annual Conference of IEEE Industrial Electronics (IECON), Porto, Portugal, 3–5 November 2009. [Google Scholar]

- Waffler, S.; Preindl, M.; Kolar, J.W. Multi-Objective Optimization and Comparative Evaluation of Si Soft-Switched and SiC Hard-Switched Automotive DC-DC Converters. In Proceedings of the 35th Annual Conference of IEEE Industrial Electronics (IECON), Porto, Portugal, 3–5 November 2009. [Google Scholar]

- Choi, W.; Son, D.; Hallenberger, M. Driving and Layout Design for Fast Switching Super-Junction MOSFETs; Fairchild Semiconductor Corporation Application Note, AN-9005; Fairchild Semiconductor: Sunnyvale, CA, USA, 2013. [Google Scholar]

- Zaman, H.; Wu, X.; Zheng, X.; Khan, S.; Ali, H. Suppression of Switching Crosstalk and Voltage Oscillations in a SiC MOSFET Based Half-Bridge Converter. Energies 2018, 11, 3111. [Google Scholar] [CrossRef]

- Bhargava, A.; Pommerenke, D.; Kam, K.W.; Centola, F.; Lam, C.W. DC-DC Buck Converter EMI Reduction Using PCB Layout Modification. IEEE Trans. Electromagn. Compat. 2011, 53, 806–813. [Google Scholar] [CrossRef]

- Reusch, D.; Strydom, J. Understanding the Effect of PCB Layout on Circuit Performance in a High-Frequency Gallium-Nitride-Based Point of Load Converter. IEEE Trans. Power Elect. 2014, 29, 2008–2015. [Google Scholar] [CrossRef]

- Wang, K.; Wang, L.; Yang, X.; Zeng, X.; Chen, W.; Li, H. A Multiloop Method for Minimization of Parasitic Inductance in GaN-Based High-Frequency DC–DC Converter. IEEE Trans. Power Elect. 2017, 32, 4728–4740. [Google Scholar] [CrossRef]

- Zhang, Z.; Guo, B.; Wang, F.; Tolbert, M.; Blalock, B.J. Impact of Ringing on Switching Losses of Wide Band-gap Devices in a Phase-leg Configuration. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 16–20 March 2014. [Google Scholar]

- Cai, A.; Pereira, A.; Tanzania, R.; Tan, Y.K.; Siek, L. A High Frequency, High Efficiency GaN HFET Based Inductive Power Transfer System. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015. [Google Scholar]

- Moradpour, M.; Lai, A.; Serpi, A.; Gatto, G. Multi-objective optimization of gate driver circuit for GaN HEMT in electric vehicles. In Proceedings of the 43rd Annual Conference of the IEEE Industrial Electronics Society (IECON), Beijing, China, 29 October–1 November 2017. [Google Scholar]

- Ghorbani, H.; Sala, V.; Camacho, A.P.; Romeral Martinez, J.L. A Simple Closed-Loop Active Gate Voltage Driver for Controlling diC/dt and dvCE/dt in IGBTs. MDPI Electron. 2019, 8, 144. [Google Scholar] [CrossRef]

- Obara, H.; Wada, K.; Miyazaki, K.; Takamiya, M.; Sakurai, T. Active Gate Control in Half-Bridge Inverters Using Programmable Gate Driver ICs to Improve Both Surge Voltage and Converter Efficiency. IEEE Trans. Ind. A 2018, 54, 4603–4611. [Google Scholar] [CrossRef]

- Gao, F.; Zhou, Q.; Wang, P.; Zhang, C. A Gate Driver of SiC MOSFET for Suppressing the Negative Voltage Spikes in a Bridge Circuit. IEEE Trans. Power Elect. 2018, 33, 2339–2353. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Active Gate Driver for Crosstalk Suppression of SiC Devices in a Phase-Leg Configuration. IEEE Trans. Power Elect. 2014, 29, 1986–1997. [Google Scholar] [CrossRef]

- Moradpour, M.; Gatto, G. A New SiC-GaN-Based Two-Phase Interleaved Bidirectional DC-DC Converter for Plug-In Electric Vehicles. In Proceedings of the International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), Amalfi, Italy, 20–22 June 2018. [Google Scholar]

- SiC Power Devices and Modules; ROHM Semiconductor Application Note, 14103EBY01; ROHM: Kyoto, Japan, 2014.

- Gong, X.; Ferreira, J.A. Investigation of Conducted EMI in SiC JFET Inverters Using Separated Heat Sinks. IEEE Trans. Ind. Elect. 2014, 61, 115–125. [Google Scholar] [CrossRef]

- Si827x Data Sheet; Revision 0.6; Silicon Labs: Austin, TX, USA, 2017.

- Design with GaN Enhancement mode HEMT; GaN Systems Application Note, GN001; GaN Systems: Ottawa, ON, Canada, 2018.

- Abbatelli, L.; Brusca, C.; Catalisano, G. How to Fine Tune Your SiC MOSFET Gate Driver to Minimize Losses; STMicroelectronics Application Note, AN4671; STMicroelectronics: Geneve, Switzerland, 2015. [Google Scholar]

- Ringing Reduction Techniques for NexFETTM High Performance MOSFETs; Texas Instruments Application Note, SLPA010; Texas Instruments: Dallas, TX, USA, 2011.

- Taylor, R.; Manack, R. Controlling Switch-Node Ringing in Synchronous Buck Converters; Texas Instruments Application Note; Texas Instruments: Dallas, TX, USA, 2012. [Google Scholar]

| Parameter | Value |

|---|---|

| SiC MOSFET [V, A] | SCT3022AL (650, 93) |

| Inductor L [m] | 2.55 |

| Low voltage CLV [] | 50 |

| High voltage CHV [] | 100 |

| Maximum input/output voltage [V] | 300/600 |

| Switching frequency [kHz] | 100 |

| Parameter | Value |

|---|---|

| Gate driver IC | Si8271 |

| Input voltage range | 3.3/5 V |

| Peak current | 4 A |

| Output | Sink/Source |

| Gate Driver Parameters | |

| Ferrite beads (FBHS/FBLS) | MPZ1608S221A 220 @ 100 MHz |

| Zener diodes (DZHS/DZLS) | 2.4 V |

| Diodes (DHS/DLS) | 20 V |

| Capacitors (CHS/CLS) | 1 |

| Bipolar Power Supply | |

| Drive voltage | +20/−5 V |

| Resistors (R1/R2) | 1 |

| Capacitors (C1/C2/C3) | 4.7 |

| Zener diode (DZ) | 20 V |

| Parameter | Value |

|---|---|

| Input/output Current Probe | Agilent 1146A |

| Current range | 100 mA–100 A |

| Bandwidth | 100 kHz |

| Ground Current Probe | Agilent N2893A |

| Maximum current | 15 A |

| Bandwidth | 100 MHz |

| Differential Voltage Probe | Agilent N2791A |

| Bandwidth | 25 MHz |

| Oscilloscope | DSO-X 3054A |

| Parameter | Value |

|---|---|

| Input voltage [V] | 25 |

| Duty cycle [%] | 50 |

| Output power [W] | 75 |

| Switching frequency [kHz] | 100 |

| Design | R-HS-OFF | R-LS-ON | Efficiency | EMI Level |

|---|---|---|---|---|

| Conventional | 2.2 Ohm | 4.7 Ohm | 0.9530 | 175.56 μAdB |

| Optimum | 1.5 Ohm | 14 Ohm | 0.9624 | 172.33 μAdB |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Moradpour, M.; Pirino, P.; Losito, M.; Franke, W.-T.; Kumar, A.; Gatto, G. Multi-Objective Optimization of the Gate Driver Parameters in a SiC-Based DC-DC Converter for Electric Vehicles. Energies 2020, 13, 3720. https://doi.org/10.3390/en13143720

Moradpour M, Pirino P, Losito M, Franke W-T, Kumar A, Gatto G. Multi-Objective Optimization of the Gate Driver Parameters in a SiC-Based DC-DC Converter for Electric Vehicles. Energies. 2020; 13(14):3720. https://doi.org/10.3390/en13143720

Chicago/Turabian StyleMoradpour, Milad, Paolo Pirino, Michele Losito, Wulf-Toke Franke, Amit Kumar, and Gianluca Gatto. 2020. "Multi-Objective Optimization of the Gate Driver Parameters in a SiC-Based DC-DC Converter for Electric Vehicles" Energies 13, no. 14: 3720. https://doi.org/10.3390/en13143720

APA StyleMoradpour, M., Pirino, P., Losito, M., Franke, W.-T., Kumar, A., & Gatto, G. (2020). Multi-Objective Optimization of the Gate Driver Parameters in a SiC-Based DC-DC Converter for Electric Vehicles. Energies, 13(14), 3720. https://doi.org/10.3390/en13143720