Design and Implementation of a Hybrid Single T-Type Double H-Bridge Multilevel Inverter (STDH-MLI) Topology

Abstract

:1. Introduction

2. Description and Analysis of the Proposed Topology

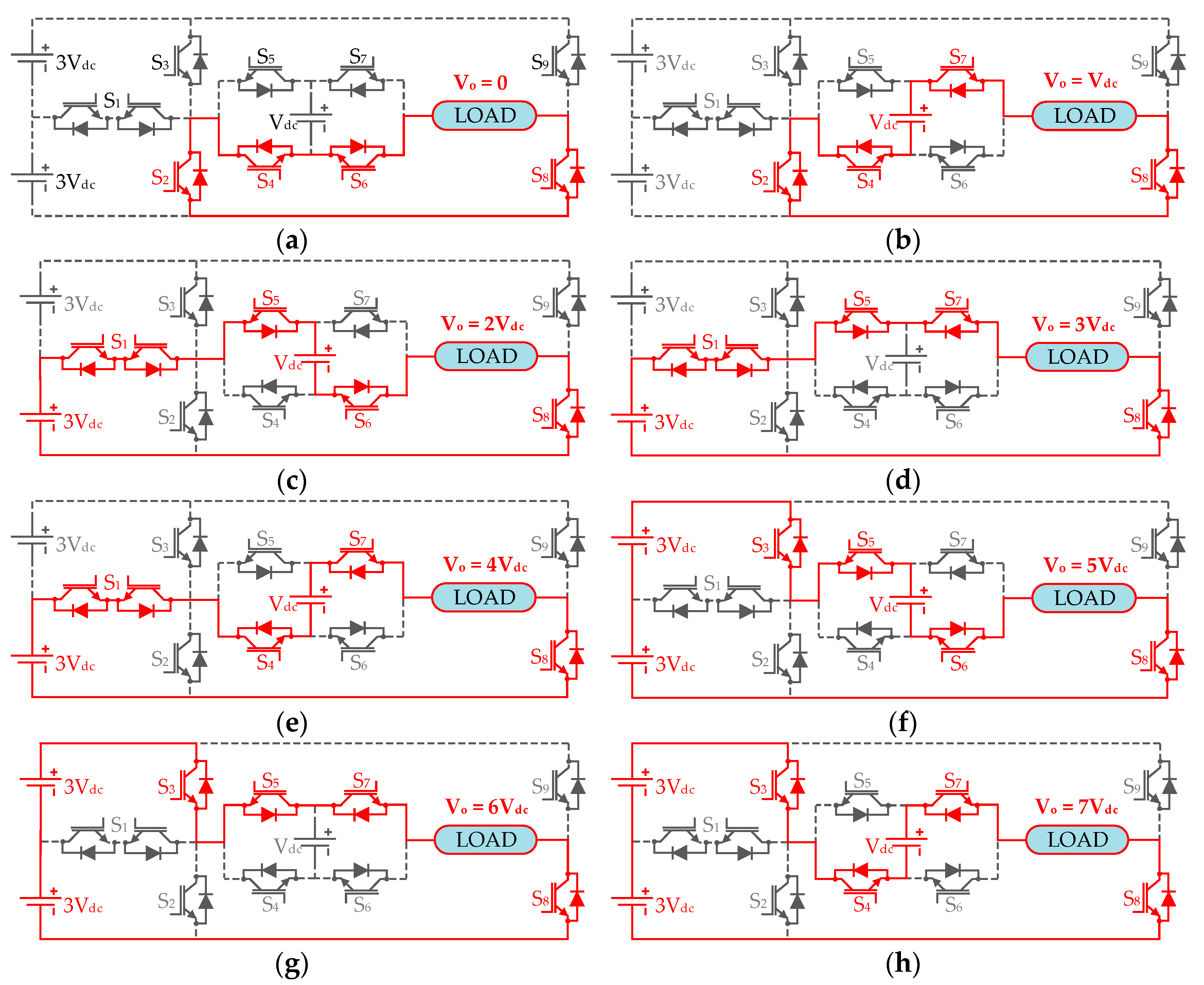

2.1. Basic Unit of the Proposed Topology

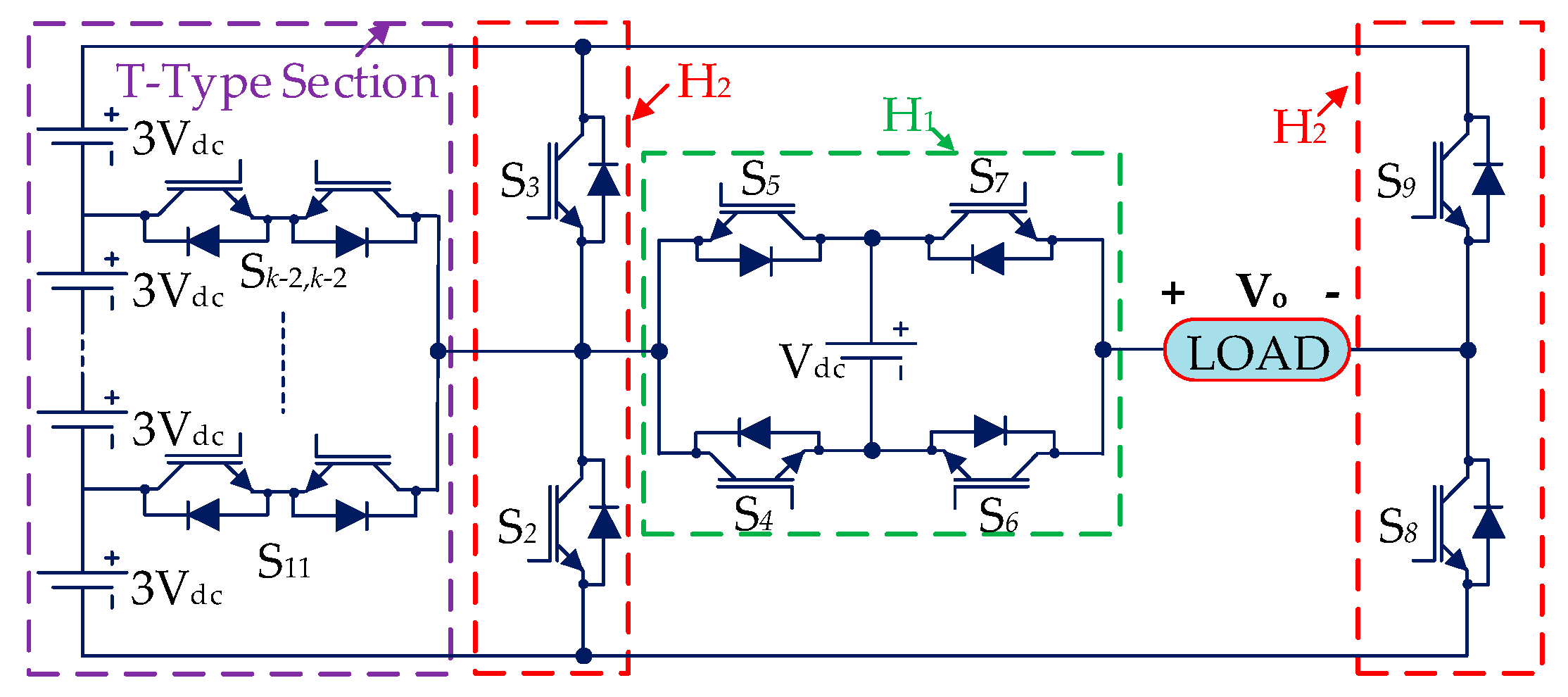

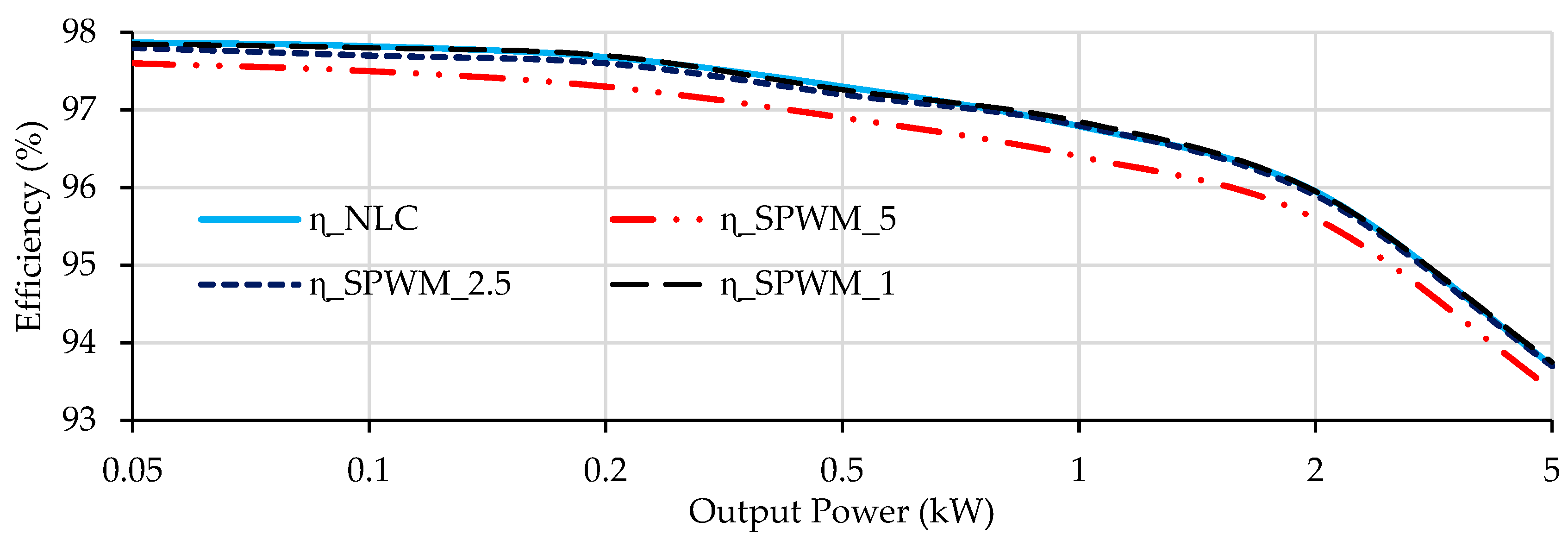

2.2. Generalized Structure of the Proposed Topology

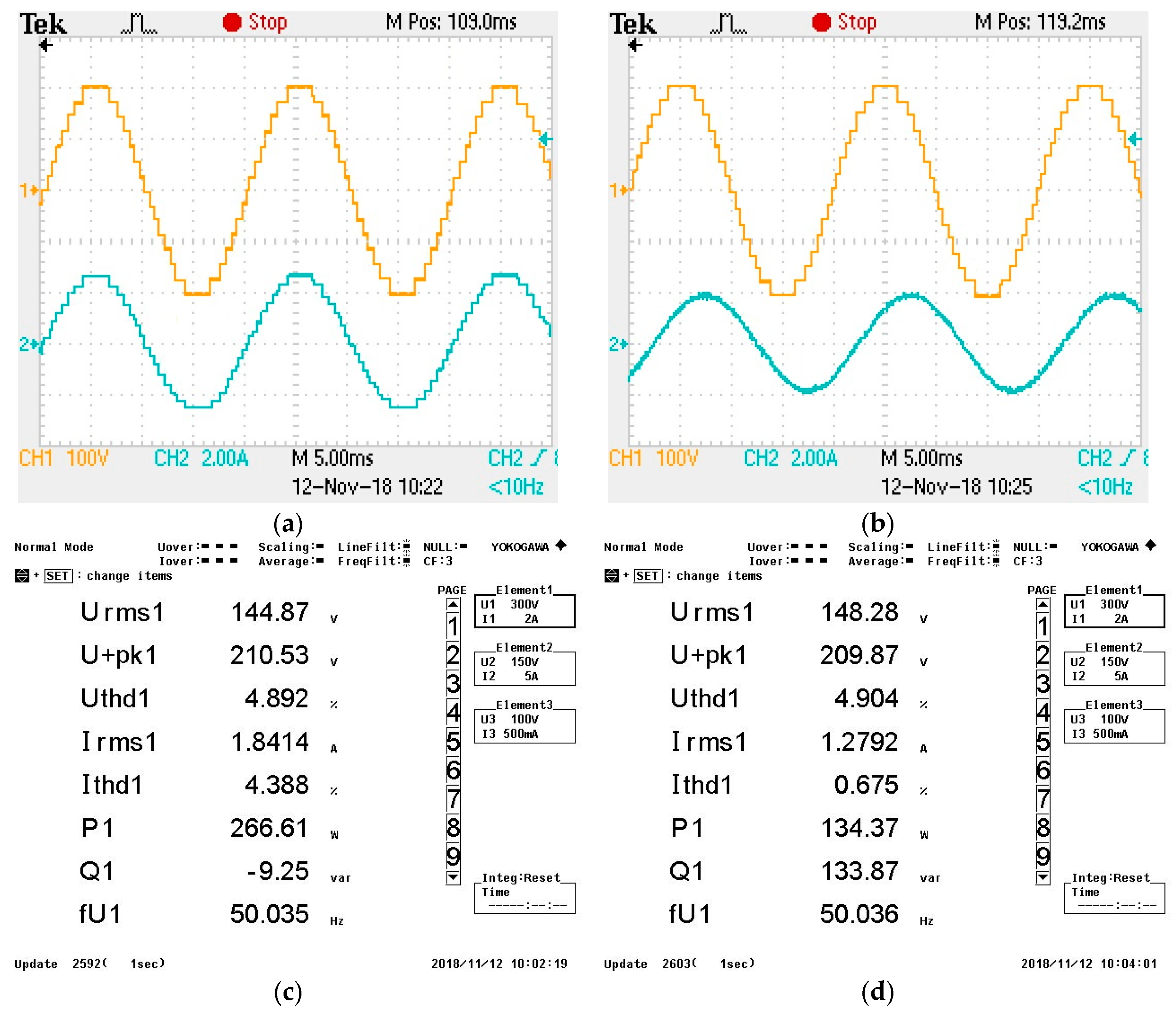

2.3. Calculation of Total Standing Voltage (TSV)

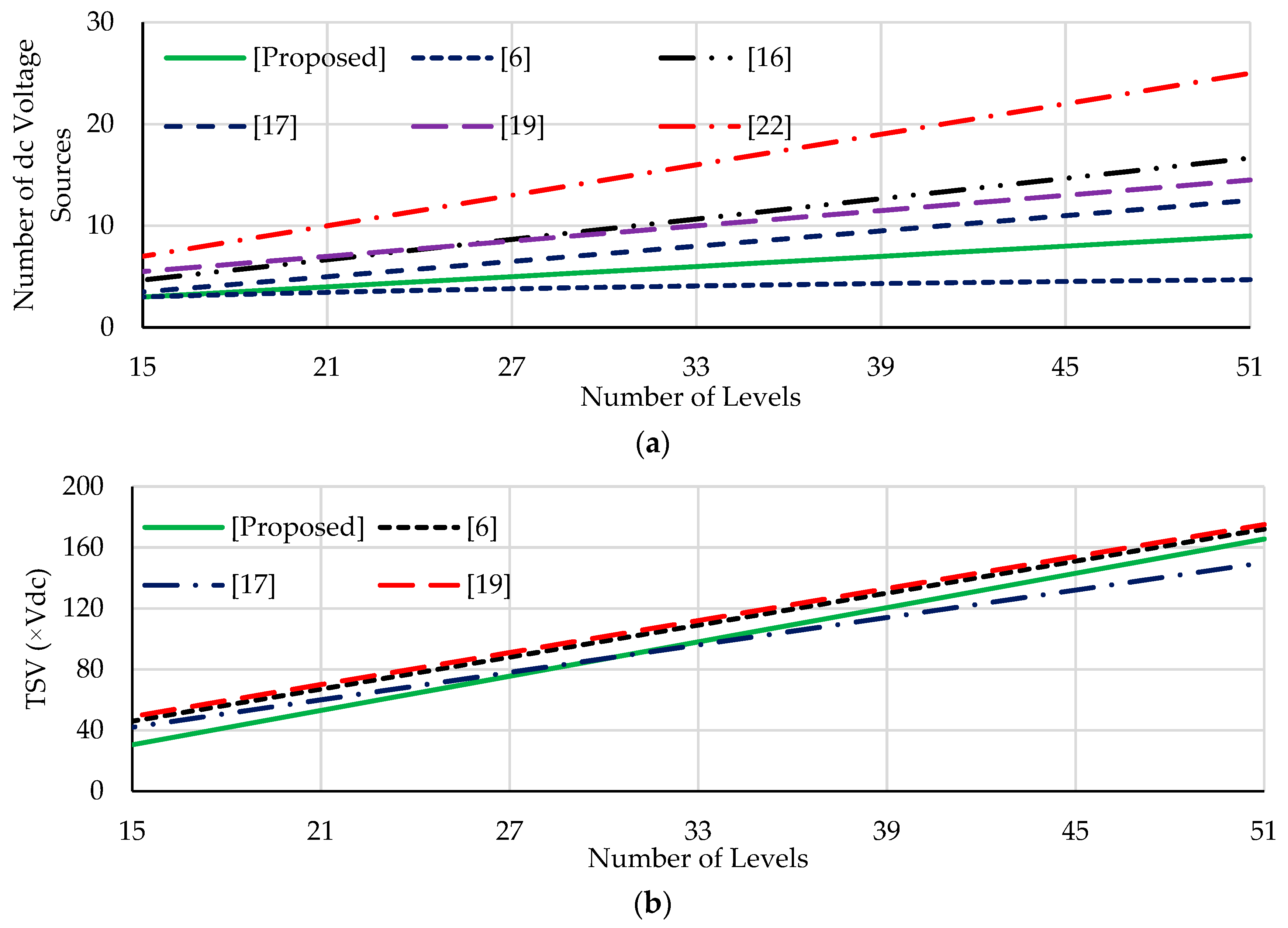

3. Comparative Study

3.1. Comparison of Basic Units

3.2. Comparison of Generalized Structure

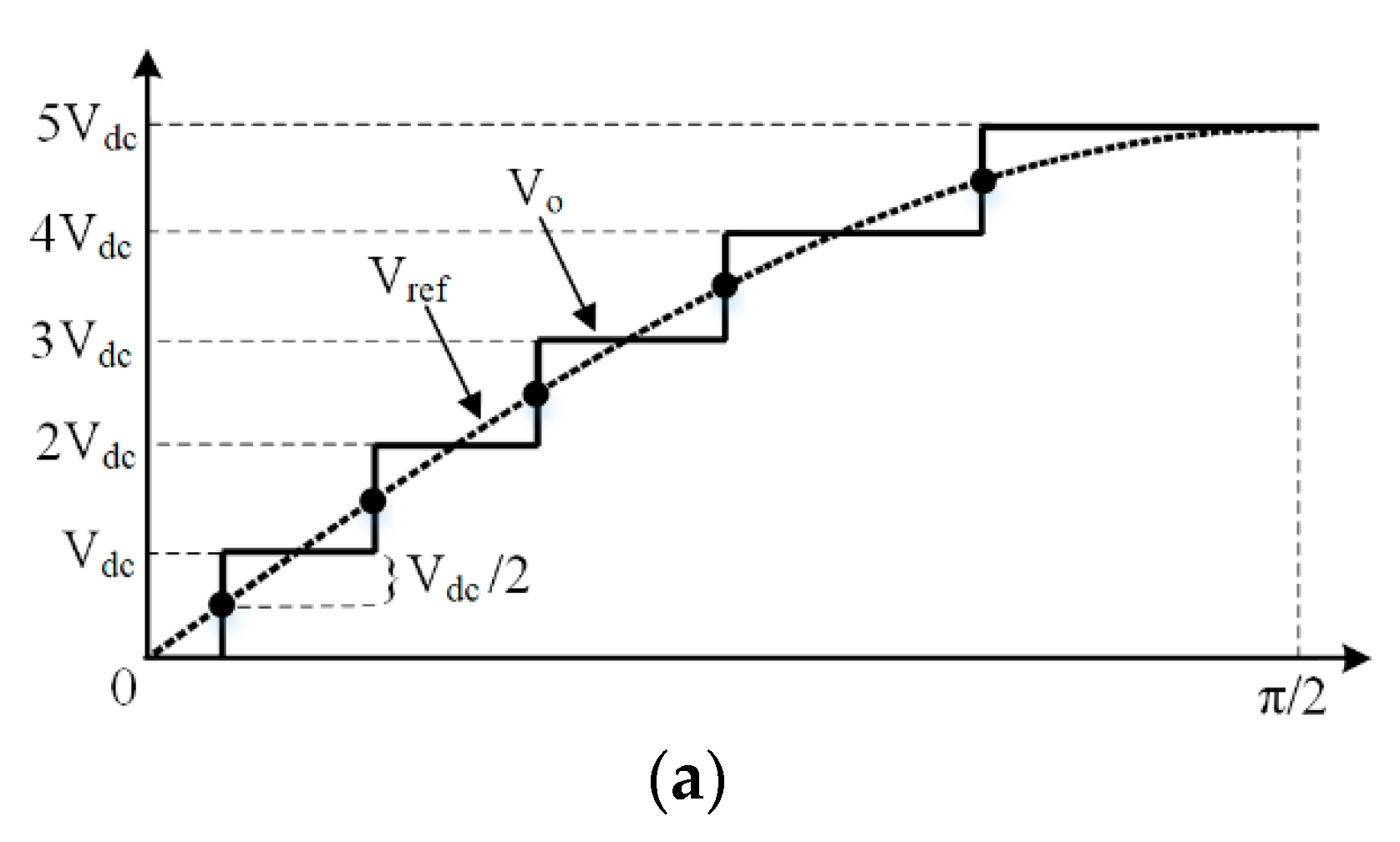

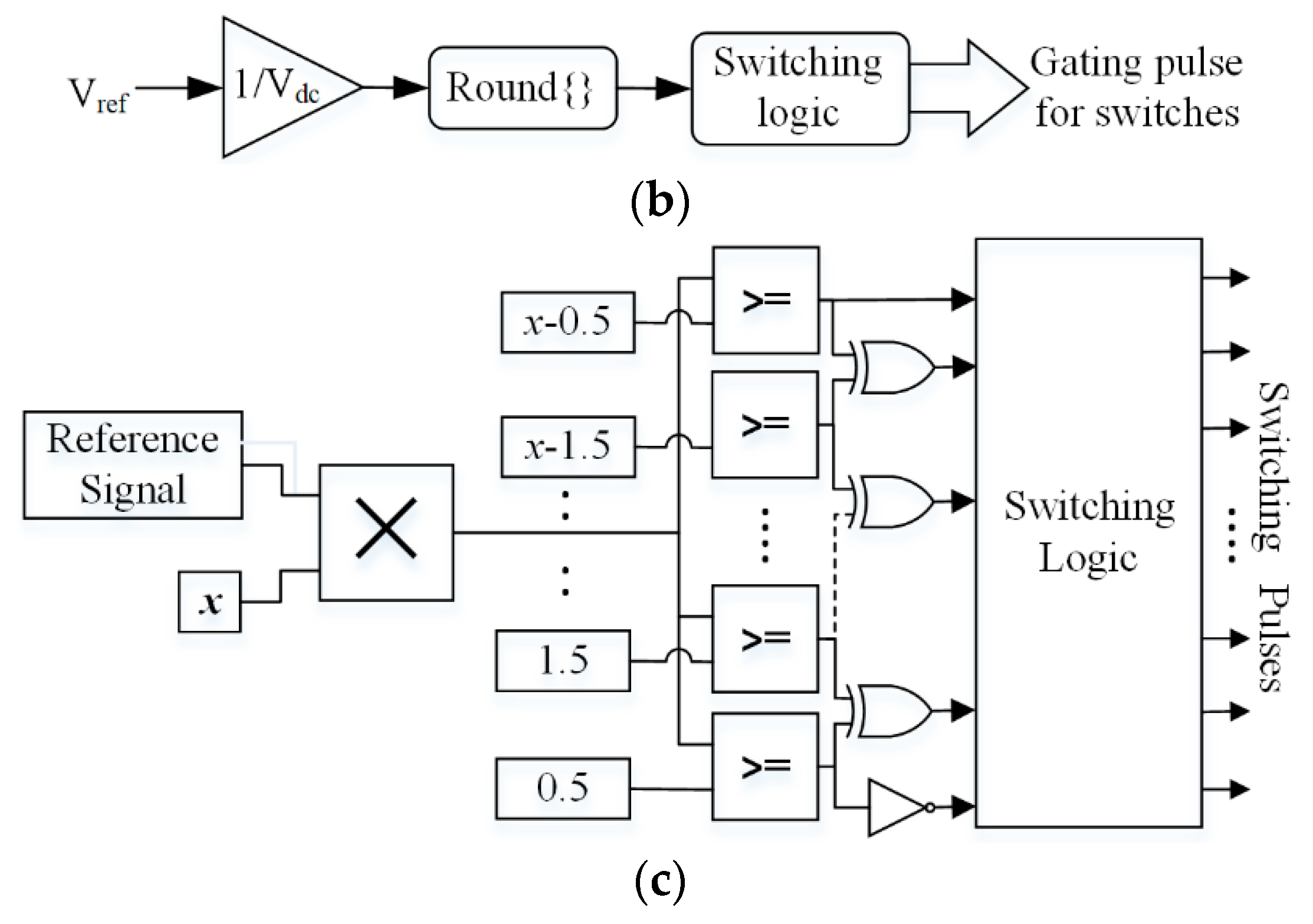

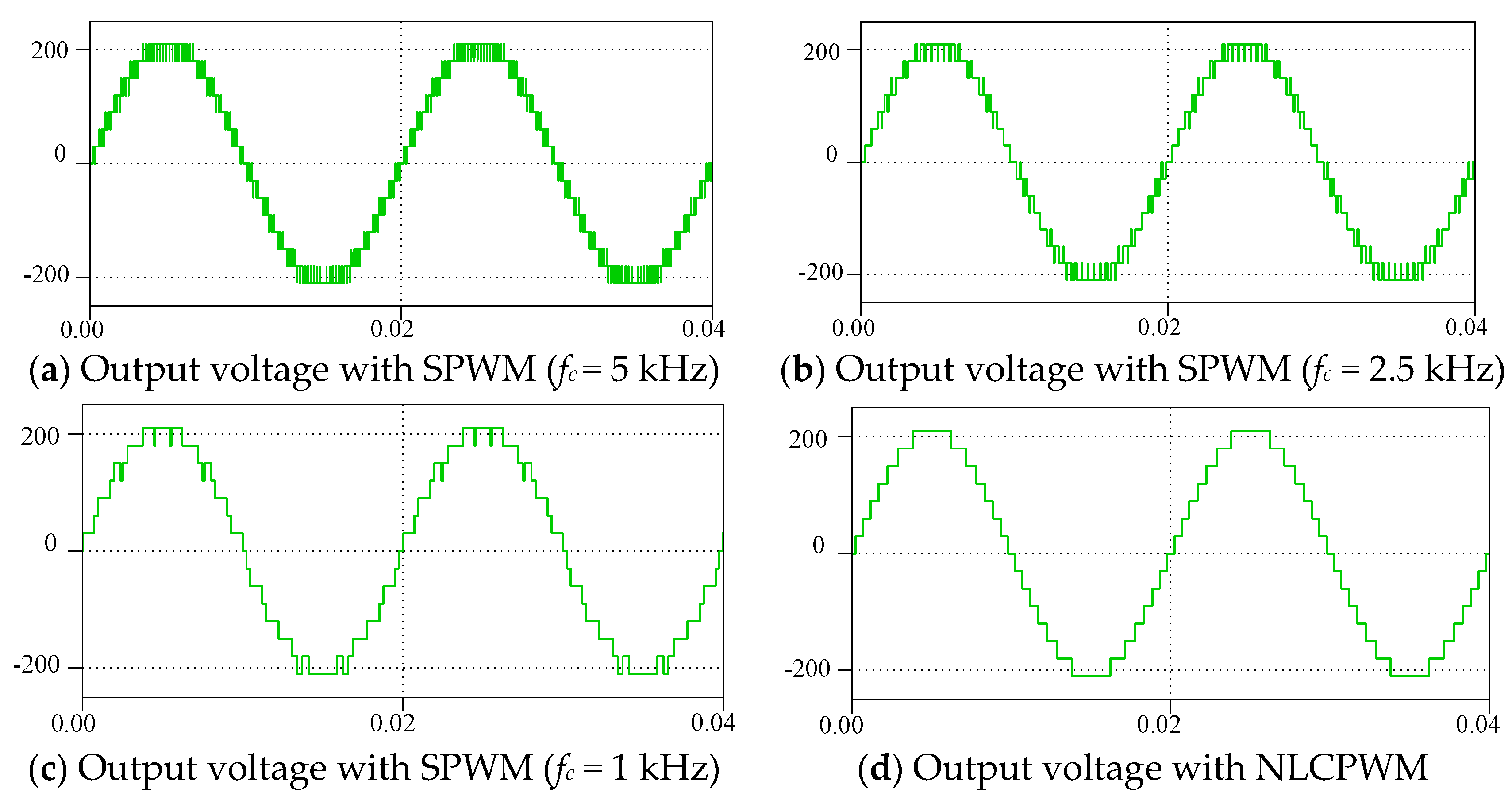

4. Nearest Level Control Modulation Method

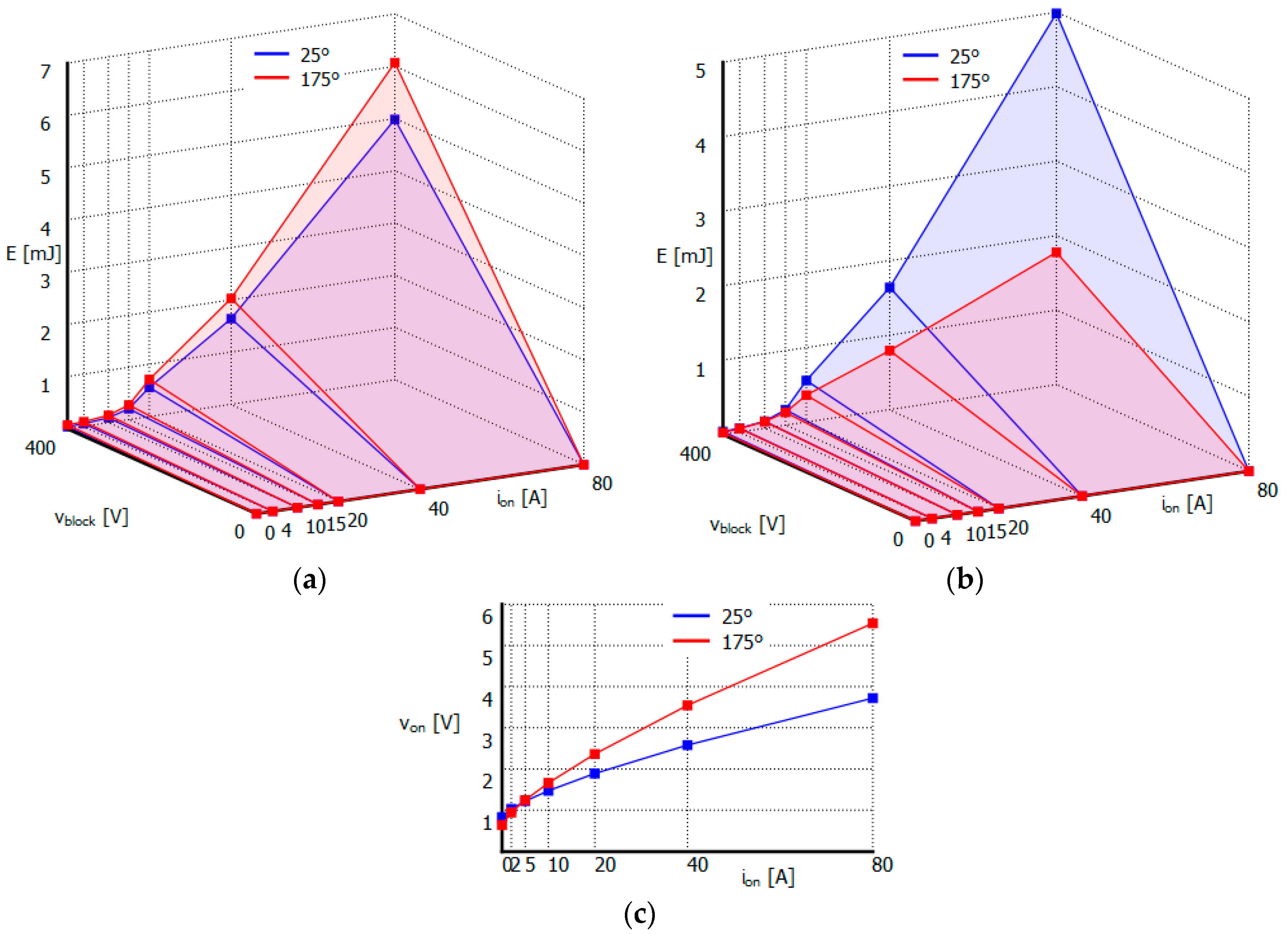

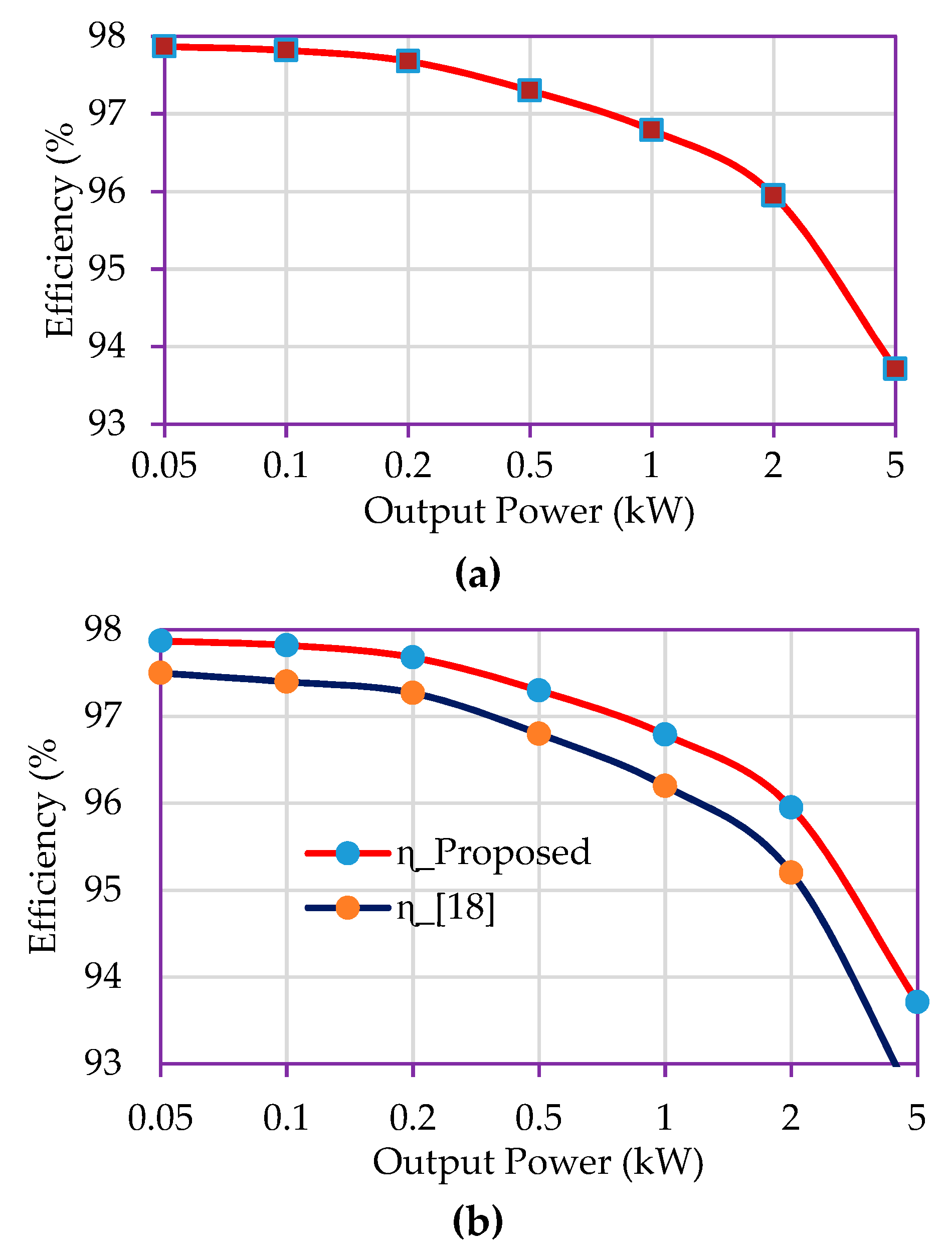

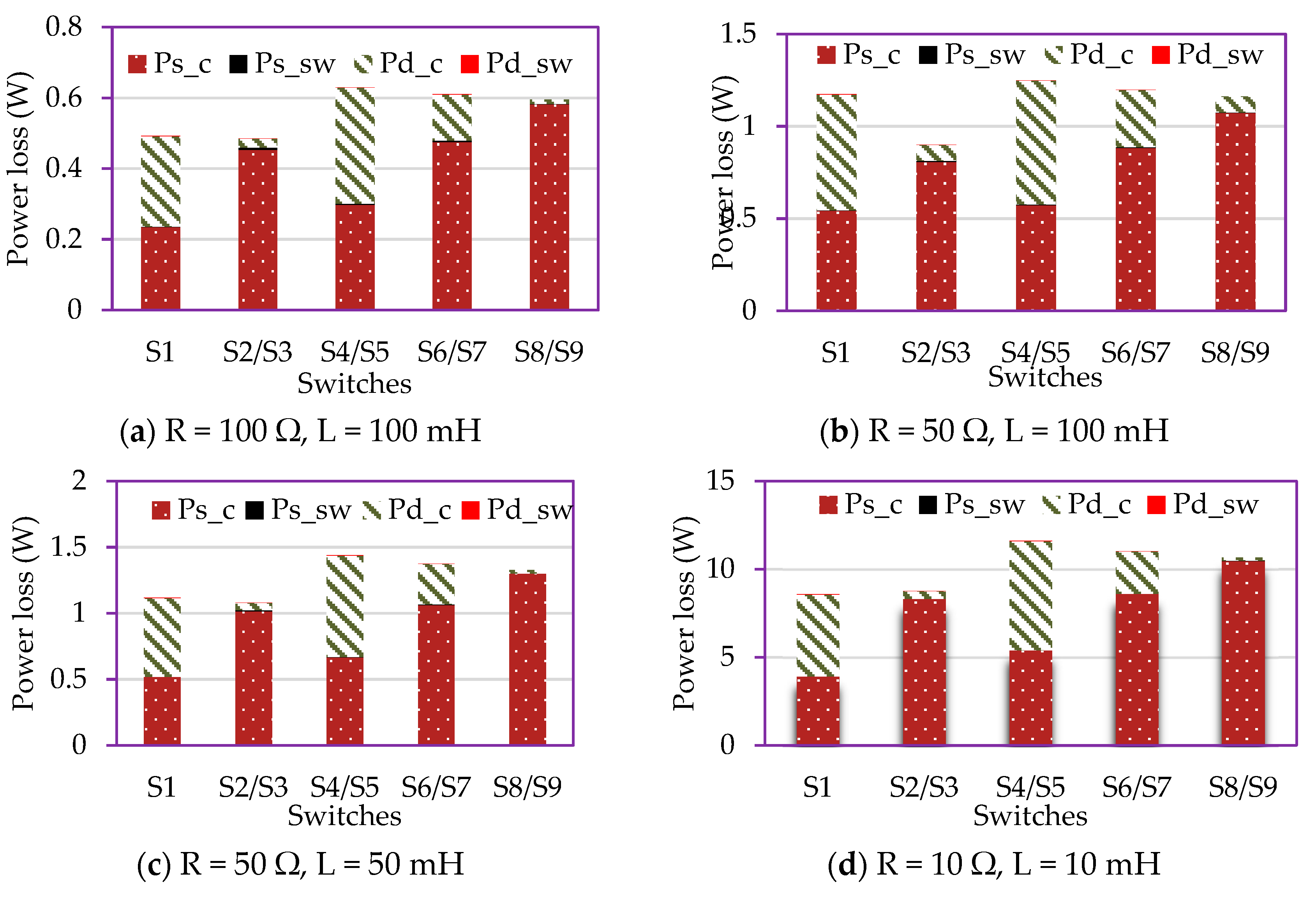

5. Power Loss Analysis

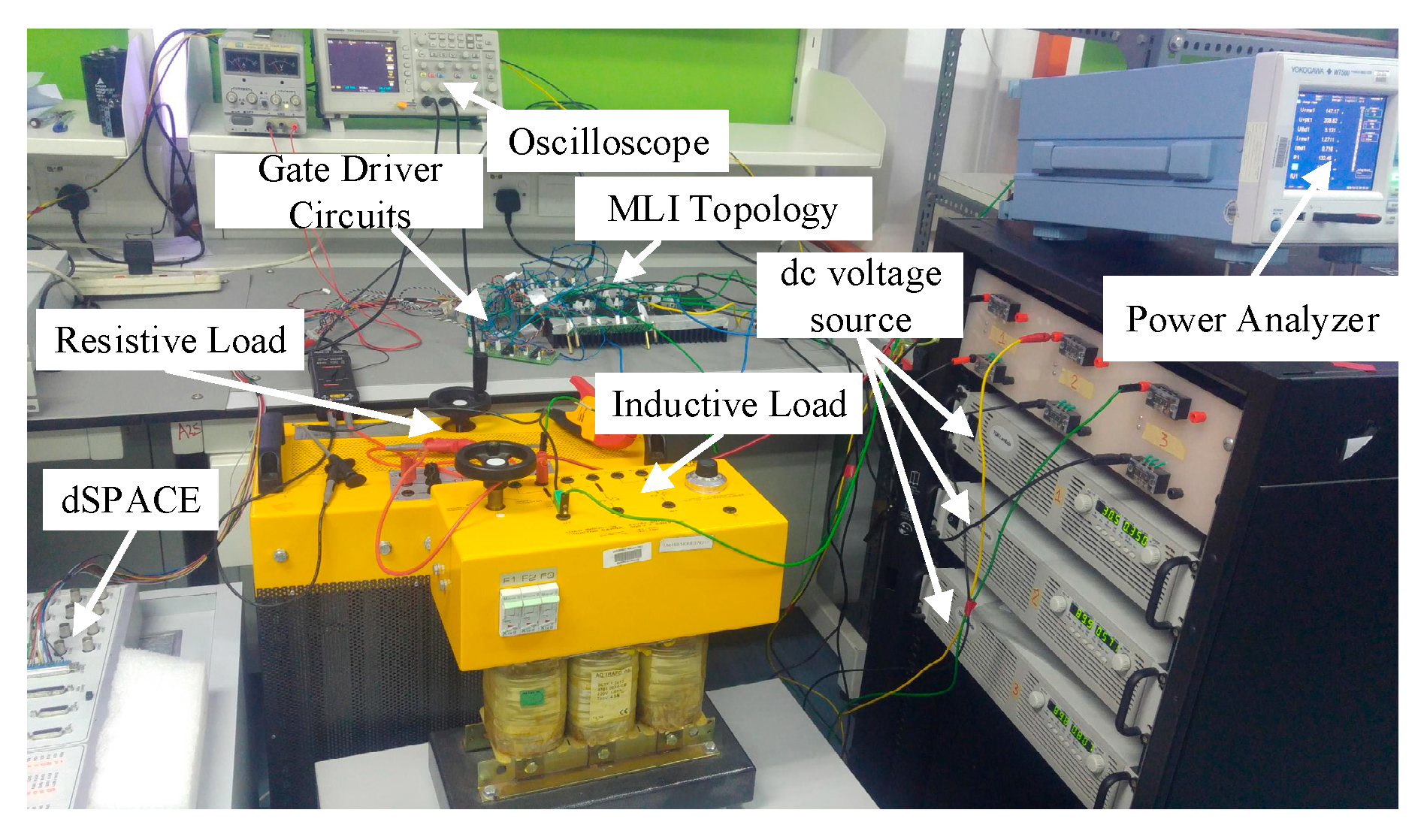

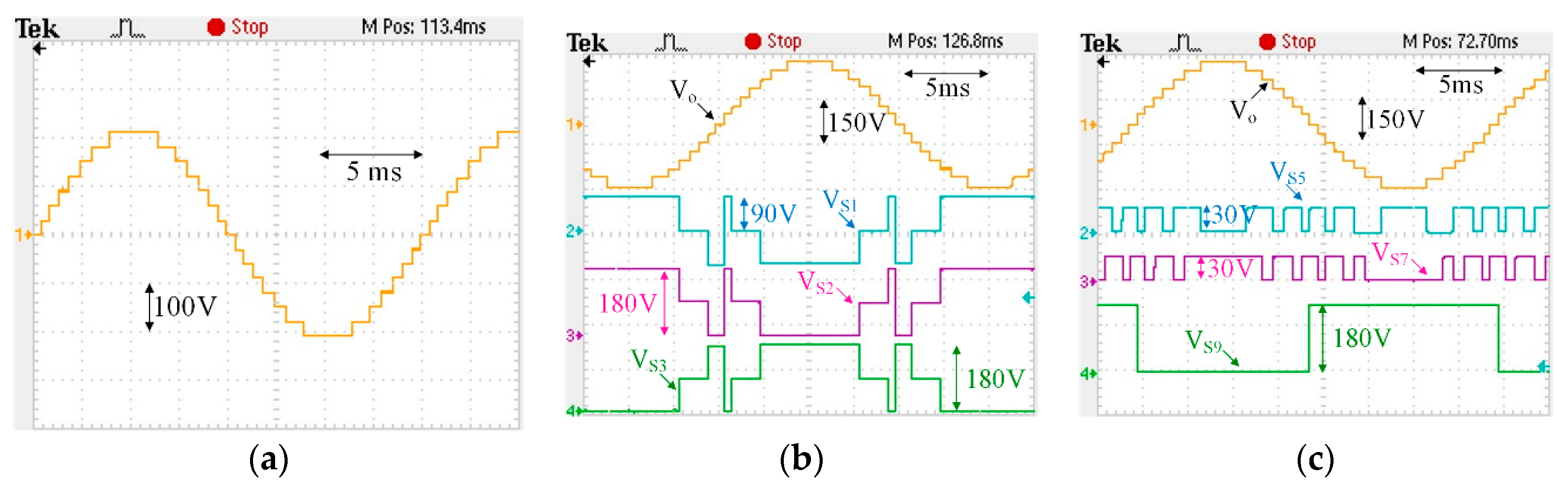

6. Results and Discussion

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Rodríguez, J.; Lai, J.S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Akagi, H. Multilevel Converters: Fundamental Circuits and Systems. Proc. IEEE 2017, 105, 2048–2065. [Google Scholar] [CrossRef]

- Gupta, K.K.; Ranjan, A.; Bhatnagar, P.; Sahu, L.K.; Jain, S. Multilevel Inverter Topologies With Reduced Device Count: A Review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar]

- Venkataramanaiah, J.; Suresh, Y.; Panda, A.K. A review on symmetric, asymmetric, hybrid and single DC sources based multilevel inverter topologies. Renew. Sustain. Energy Rev. 2017, 76, 788–812. [Google Scholar] [CrossRef]

- Hinago, Y.; Koizumi, H. A Single-Phase Multilevel Inverter Using Switched Series/Parallel DC Voltage Sources. IEEE Trans. Ind. Electron. 2010, 57, 2643–2650. [Google Scholar]

- Kang, S.H.; Lee, F.S. A new structure of H-bridge multilevel inverter. In Proceedings of the Annual Fall Conference of Power Electronics (KIPE Conference), Goyang, Korea, 31 October 2008; pp. 388–390. [Google Scholar]

- Choi, W.K.; Kang, F.S. H-bridge based multilevel inverter using PWM switching function. In Proceedings of the INTELEC 2009-31st International Telecommunications Energy Conference, Incheon, Korea, 18–22 October 2009. [Google Scholar]

- Samsami, H.; Taheri, A.; Samanbakhsh, R. New bidirectional multilevel inverter topology with staircase cascading for symmetric and asymmetric structures. IET Power Electron. 2017, 10, 1315–1323. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Babaei, E.; Gharehpetian, G.B. A New Multilevel Converter Topology With Reduced Number of Power Electronic Components. IEEE Trans. Ind. Electron. 2012, 59, 655–667. [Google Scholar] [CrossRef]

- Babaei, E.; Laali, S.; Bayat, Z. A Single-Phase Cascaded Multilevel Inverter Based on a New Basic Unit With Reduced Number of Power Switches. IEEE Trans. Ind. Electron. 2015, 62, 922–929. [Google Scholar]

- Jammala, V.; Yellasiri, S.; Panda, A.K. Development of a New Hybrid Multilevel Inverter Using Modified Carrier SPWM Switching Strategy. IEEE Trans. Power Electron. 2018, 33, 8192–8197. [Google Scholar]

- Yu, H.; Chen, B.; Yao, W.; Lu, Z. Hybrid Seven-Level Converter Based on T-Type Converter and H-Bridge Cascaded under SPWM and SVM. IEEE Trans. Power Electron. 2018, 33, 689–702. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Wei, D.; Fan, B.; Li, Y. Topology and Capacitor Voltage balancing Control of a Symmetrical Hybrid Nine-Level Inverter for High Speed Motor Drives. IEEE Trans. Ind. Appl. 2017, 53, 5563–5572. [Google Scholar] [CrossRef]

- Roy, J.; Chamarthi, P.; Agarwal, V. A hybrid 9-level inverter with minimum number of switches for single phase grid connected solar PV system. In Proceedings of the 43rd Photovoltaic Specialists Conference (PVSC), Portland, OR, USA, 5–10 June 2016; pp. 3252–3257. [Google Scholar]

- Samadaei, E.; Gholamian, S.A.; Sheikholeslami, A.; Adabi, J. An Envelope Type (E-Type) Module: Asymmetric Multilevel Inverters With Reduced Components. IEEE Trans. Ind. Electron. 2016, 63, 7148–7156. [Google Scholar] [CrossRef]

- Samadaei, E.; Sheikholeslami, A.; Gholamian, S.-A.; Adabi, J. A Square T-Type (ST-Type) Module for Asymmetrical Multilevel Inverters. IEEE Trans. Power Electron. 2017, 99, 987–996. [Google Scholar] [CrossRef]

- Su, G.-J. Multilevel DC-Link Inverter. IEEE Trans. Ind. Appl. 2005, 41, 848–854. [Google Scholar] [CrossRef]

- Jayabalan, M.; Jeevarathinam, B.; Sandirasegarane, T. Reduced switch count pulse width modulated multilevel inverter. IET Power Electron. 2017, 10, 10–17. [Google Scholar] [CrossRef]

- Gautam, S.P.; Gupta, S.; Sahu, L.K. Reduction in number of devices for symmetrical and asymmetrical multilevel inverters. IET Power Electron. 2016, 9, 698–709. [Google Scholar] [CrossRef]

- Odeh, C.I.; Obe, E.S.; Ojo, O. Topology for cascaded multilevel inverter. IET Power Electron. 2016, 9, 921–929. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K.; Grégoire, L.A. Packed U cells multilevel converter topology: Theoretical study and experimental validation. IEEE Trans. Ind. Electron. 2011, 58, 1294–1306. [Google Scholar] [CrossRef]

- Shueai Alnamer, S.; Mekhilef, S.; Bin Mokhlis, H. A Four-Level T-Type Neutral Point Piloted Inverter for Solar Energy Applications. Energies 2018, 11, 1546. [Google Scholar] [CrossRef]

- Bassi, H.; Salam, Z. A New Hybrid Multilevel Inverter Topology with Reduced Switch Count and dc Voltage Sources. Energies 2019, 12, 977. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Memon, M.A. Optimal Design of a New Cascaded Multilevel Inverter Topology with Reduced Switch Count. IEEE Access 2019, 7, 24498–24510. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mustafa, A.; Sarwar, A.; Mekhilef, S.; Shah, N.B.M.; Seyedamahmousian, M.; Stojcevski, A.; Horan, B.; Ogura, K. Single phase symmetrical and asymmetrical design of multilevel inverter topology with reduced number of switches. In Proceedings of the 2018 IEEMA Engineer Infinite Conference (eTechNxT), Greater Noida, NCR of Delhi, India, 13–14 March 2018; pp. 1–6. [Google Scholar]

- Thiruvengadam, A. An Enhanced H-Bridge Multilevel Inverter with Reduced THD, Conduction, and Switching Losses Using Sinusoidal Tracking Algorithm. Energies 2018, 12, 81. [Google Scholar] [CrossRef]

- Aganah, K.; Luciano, C.; Ndoye, M.; Murphy, G.; Aganah, K.A.; Luciano, C.; Ndoye, M.; Murphy, G. New Switched-Dual-Source Multilevel Inverter for Symmetrical and Asymmetrical Operation. Energies 2018, 11, 984. [Google Scholar] [CrossRef]

- Konstantinou, G.; Pou, J.; Ceballos, S.; Darus, R.; Agelidis, V. Switching Frequency Analysis of Staircase Modulated Modular Multilevel Converters and Equivalent PWM Techniques. IEEE Trans. Power Deliv. 2015, 31, 28–36. [Google Scholar] [CrossRef]

- Memon, M.A.; Mekhilef, S.; Mubin, M.; Aamir, M. Selective harmonic elimination in inverters using bio-inspired intelligent algorithms for renewable energy conversion applications: A review. Renew. Sustain. Energy Rev. 2018, 82, 2235–2253. [Google Scholar] [CrossRef]

- Memon, M.A.; Mekhilef, S.; Mubin, M. Selective harmonic elimination in multilevel inverter using hybrid APSO algorithm. IET Power Electron. 2018, 11, 1673–1680. [Google Scholar] [CrossRef]

- Dahidah, M.S.A.; Konstantinou, G.; Agelidis, V.G. A Review of Multilevel Selective Harmonic Elimination PWM: Formulations, Solving Algorithms, Implementation and Applications. IEEE Trans. Power Electron. 2015, 30, 4091–4106. [Google Scholar] [CrossRef]

- Meshram, P.M.; Borghate, V.B. A simplified nearest level control (NLC) voltage balancing method for modular multilevel converter (MMC). IEEE Trans. Power Electron. 2015, 30, 450–462. [Google Scholar] [CrossRef]

| S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | S9 | Vo |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | Vdc |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 2Vdc |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 3Vdc |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 4Vdc |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 5Vdc |

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 6Vdc |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 7Vdc |

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | −Vdc |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | −2Vdc |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | −3Vdc |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | −4Vdc |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | −5Vdc |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | −6Vdc |

| 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | −7Vdc |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rawa, M.; Siddique, M.D.; Mekhilef, S.; Mohamed Shah, N.; Bassi, H.; Seyedmahmoudian, M.; Horan, B.; Stojcevski, A. Design and Implementation of a Hybrid Single T-Type Double H-Bridge Multilevel Inverter (STDH-MLI) Topology. Energies 2019, 12, 1810. https://doi.org/10.3390/en12091810

Rawa M, Siddique MD, Mekhilef S, Mohamed Shah N, Bassi H, Seyedmahmoudian M, Horan B, Stojcevski A. Design and Implementation of a Hybrid Single T-Type Double H-Bridge Multilevel Inverter (STDH-MLI) Topology. Energies. 2019; 12(9):1810. https://doi.org/10.3390/en12091810

Chicago/Turabian StyleRawa, Muhyaddin, Marif Daula Siddique, Saad Mekhilef, Noraisyah Mohamed Shah, Hussain Bassi, Mehdi Seyedmahmoudian, Ben Horan, and Alex Stojcevski. 2019. "Design and Implementation of a Hybrid Single T-Type Double H-Bridge Multilevel Inverter (STDH-MLI) Topology" Energies 12, no. 9: 1810. https://doi.org/10.3390/en12091810

APA StyleRawa, M., Siddique, M. D., Mekhilef, S., Mohamed Shah, N., Bassi, H., Seyedmahmoudian, M., Horan, B., & Stojcevski, A. (2019). Design and Implementation of a Hybrid Single T-Type Double H-Bridge Multilevel Inverter (STDH-MLI) Topology. Energies, 12(9), 1810. https://doi.org/10.3390/en12091810