Abstract

In this paper, a new, high step-up quadratic boost converter with high conversion efficiency is discussed. A storage capacitor and resonant inductor are connected in series with a clamp capacitor through a diode. These compose a voltage multiplier cell, which is applied on the switch of the quadratic boost converter. The clamp capacitor can protect the switch from a voltage spike and absorb energy when the switch turns off; then, the storage capacitor and resonant inductor are charged by the energy stored in the clamped capacitor to increase the voltage transfer gain. In addition, the voltage multiplier cell can also reduce the voltage stresses of power devices. Then, a 16 V input, 200 V output prototype with 80 W nominal power is built up and tested. Furthermore, a finite time fast terminal sliding mode (NFTSM) control is proposed, with constant frequency for the voltageFundamental Building B213:tracking control of this converter. The new NFTSM is obtained by introducing an adjustable nonlinear term into fast terminal sliding mode (FTSM) control, and a singularity problem is avoided. The experiment illustrates that the maximum efficiency of the proposed converter achieves 95% at , V. The voltage stress is reduced to half of the corresponding component of the basic boost converter at the same voltage level. Moreover, the proposed NFTSM controller can track the reference signal, and provide a short settling time of about 48 ms with no overshoot, and the system response exhibits strong robustness against 11.7% input voltage disturbance and 30% load variation.

1. Introduction

Recently, the fast development of electronics products, such as solar energies, uninterruptible power supplies (UPS), and electric automobiles have been witnessed [1,2,3]. DC-DC converters has been wildly applied to these applications. However, due to a low and varying input voltage of these applications, the boost converter is a convenient solution for step-up conversion. However, it is difficult for the conventional converter to provide such a high direct-current (DC) voltage gain. Moreover, many power devices of boost converters suffer from overlarge stress at a high output voltage level, leading to decreased efficiency [4].

Some scholars have strived to increase steady voltage gain and efficiency of boost converters. Some structures, such as the cascaded structure or switched-capacitor [5,6,7] can extend the steady voltage gain at a low cost. However, with the increase of voltage gain, more stages are adopted, leading to a complex circuit and significant current ripple [8]. In some isolated converters [9,10], much high-voltage conversion ratios can be achieved at a relatively low-duty cycle, but the leakage inductor of the magnetic elements may give rise to high voltage spikes and inevitable energy decreases. Furthermore, the volume and weight of power transformers are obstacles for a compact converter. A quadratic boost converter with a single switch can also boost the voltage gain with few components [11]. However, most previous converters may suffer from too much voltage stress, leading to reduced the conversion efficiency. The soft switch techniques [12] can recycle the leakage energy of magnetic elements, but at the price of increasing topology complexity. A voltage multiplier cell is a selectable option [13], which can not only alleviate voltage stress, but also improve the voltage gain.

A control strategy is indispensable to stabilize DC-DC converters against external disturbances. Many classical linear control methods which may achieve mediocre performance cannot even guarantee the stability, owing to the strong nonlinear property of boost converters. Therefore, some nonlinear control strategies, such as neural network control, adaptive control, and sliding mode control (SMC) [14,15,16] have been applied to it. The switch operation on the sliding mode surface of SMC is similar to the two operation states of the DC-DC converter (switch “ON” and “Off”) so that SMC is inherently appropriate to DC-DC converters. Moreover, SMC has characteristics of strong robustness and easy implementation, which is why SMC has generally been used on DC-DC converters. In earlier research, a hysteresis was adopted to relieve chattering and reduce switching frequency [17]. However, the variational switching frequency still exists, which may induce power losses and the electromagnetic interference (EMI) problem. To avoid this disadvantage, a fixed frequency SMC had been proposed [18,19] that can provide a constant operation frequency against external disturbances.

One disadvantage of the lineal sliding mode control is that the system can only converge to the equilibrium points asymptotically, leading to an infinite convergence time theoretically. Afterwards, a terminal sliding mode (TSM) control characterized by a nonlinear sliding mode was developed to guarantee finite-time convergence [20]. It can speed up the convergence rate near the equilibrium point, bringing about improved transient performance. However, this TSM control method cannot deliver a fast convergence speed when the system states have a distance from the equilibrium point. To ensure fast transient convergence in whole state space, a fast terminal sliding mode (FTSM) control was adopted [21]. The FTSM control ensures fast transient convergence in a whole convergence process. However, the previous TSM and FTSM methods may both endure a singularity problem. A few methods have been investigated to overcome this difficulty. One approach is the so-called two-phase control strategy. The trajectory was transferred to a specific region where no singularity occurs. Another approach is to add a saturation function to limit the amplitude of singularity term [22]. It should be noticed that these methods need an extra procedure to eliminate the singularity. In this paper, a novel nonsingular fast terminal sliding mode (NFTSM) is proposed without any additional procedures to avoid the singularity problem.

Also in this paper, a new high step-up converter with voltage multiplier is firstly addressed. This scheme is based on a combination of the quadratic boost converter with the voltage multiplier. Secondly, a novel finite-time NFTSM controller is designed for this converter. Finally, the new NFTSM controller is applied onto the proposed converter. Numerical simulations and experiments are provided to illustrate the effectiveness of the novel converter and controller. The arrangement of this paper is given as follows: the operation principle is introduced in Section 2; Section 3 discusses performance and key parameters; the NFTSM controller is designed and analysed in Section 4; the experimental results are introduced in Section 5; then, Section 6 concludes this paper.

Notations. Throughout this paper, Q is a switch; , are input inductors, and is a resonant inductor; , , , are capacitors; , , , , are diodes; and R is a load, respectively. denotes the voltage of across corresponding element; for example, represents the input voltage, and , , , , stand for the voltages across of , , , , . Analogously, symbolise the current flowing through the corresponding element; for example, , , , , represent the current flowing through , , , , . , , , , denote the current flowing through the switch, and , , , respectively. represents the input voltage source, and denotes the driving signal of the switch (Q), especially.

2. Topology of the Proposed High Step-Up DC-DC Converter

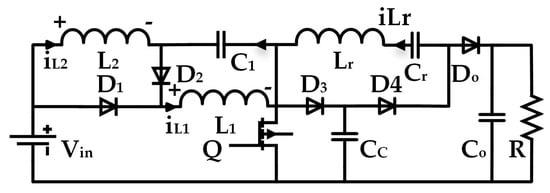

The proposed converter based on a quadratic boost converter and a clamp circuit consisted of , , and was applied on the switch (Q) to clamp the voltage of the switch and eliminate voltage spikes in the turned-off state. Then, , , , were composed a multiplier cell so that capacitor could absorb energy from during the turned-on state of the switch in a resonant way, and release energy to the load (R) and output capacitor () during the turned-off state. By recycling the energy stored in , the voltage gain of the proposed converter has been improved. The voltage stresses of output diode and switch Q were halved compared to the conventional boost converter, and the conversion efficiency was promoted, owing to the clamp circuit. More detailed theoretical analyses can be found later on.

2.1. Operational Principles

Figure 1 plots the simplified equivalent circuit of the proposed converter. Some assumptions were postulated to simplify circuit analysis, as the following:

Figure 1.

The equivalent circuit of the proposed converter.

- (1)

- The converter works with high operation frequency, and all components are ideal;

- (2)

- , are sufficiently large, such that the circuit operates under the current continuous mode (CCM);

- (3)

- , are also large enough, such that the voltage across them are considered as a constant.

In accordance with above assumptions, a complete period mainly includes six operation modes, and the simplified equivalent circuit of every mode is shown in Figure 2. It restarts the whole process after mode 6 is finished.

Figure 2.

Operation modes: (a) mode 1; (b) mode 2; (c) mode 3; (d) mode 4; (e) mode 5; (f) mode 6.

Mode 1 ([–], (a)): at the instant , the switch Q is turned off, , , are reverse biased, and , are conducted. The input source () and , release energy to through , and to through . During this mode, the converter can be modeled as follows:

where , , , denote the current flowing through , , , and , respectively; , , denote the averaged input voltage, output voltage, and the voltage across .

Mode 2 ([–], (b)): at the instant , , are reverse biased, and begins to be conducted. The input source () and , release energy to , , R, and unceasingly. , decrease linearly until the switch is turned on. The resonant inductor current () increases linearly until it equals the input current (). In this mode, the new dynamics of this converter can be modeled as follows:

Mode 3 ([–], (c)): at the instances , , , is reverse biased, and , were conducted. The charging process of was completed. The input source () and , release energy to R and , sequentially. In this mode, the extra dynamics of this converter can be modeled as follows:

Mode 4 ([–], (d)): at the instant , the switch Q is turned on, and , , were reverse biased, and , were conducted. , start to absorb energy from the input sources () and . The resonant inductor current reduces to zero until is blocked. In this mode, the new dynamics can be modeled as follows:

Mode 5 ([–], (e)): at the instances , , , it is reverse-biased. The resonant process starts when is reverse-biased. The diode transfers energy stored in to in a resonant way [23]. is blocked when half of the resonant period is completed at the instant . It is noticed that the average output voltage of the proposed converter is equal to the average voltage across , plus the voltage of . The new dynamics in this mode can be modeled as follows:

where denotes the equivalent capacitance of the multiplier cell, and is the angular frequency of this cell.

Mode 6 ([–], (f)): at the instant , the resonant process stops, and is reverse biased. , store energy from the input source () and sequentially until the switch is turned off. A new period restarts from mode 1. In this mode, the new dynamics can be modeled as follows:

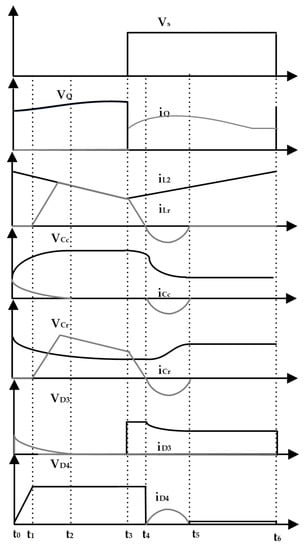

Figure 3 shows the theoretical operation waveforms of some key variables in a case of a duty cycle D = 0.5 to exhibit operating principles of the converter ulteriorly. The time period from – represents a complete operating cycle, where – represents a duration of the switch turned off, and – represents a duration of the switch turned on.

Figure 3.

Key operation waveforms.

Observing Figure 3, one can see that the resonant inductor current () starts to rise at until it reaches the value of , and then decreases linearly during –. A half period of a resonant procedure is completed during –.

2.2. Performance Analysis

2.2.1. The Voltage Gain

To simplify the analysis, only modes 2, 3, 5, and 6 were considered, while modes 1, 4 were neglected due to their short duration and micro-variation of the related variables. During modes 2 and 3, the switch was turned off, and and started to release energy to , , R. The voltage of inductors functions are described in (1), (2).

When the switch is turned on during modes 5 and 6, , start to store energy from the input source () and , demonstrated in (11)–(12). When the circuit arrives at a steady state, using the inductor voltage-second balance principle on the inductors and in the whole period, the following equations can be achieved:

where D denotes the duty cycle.

According to (20)–(21), the steady voltage of and can be obtained by:

The average voltage of is equal to the average voltage across Cc because it is charged by during mode 5. Moreover, is connected in series with the output of the quadratic converter. The output voltage gain of this converter is given by:

The voltage gain of boost converter is expressed as:

According to [11], the voltage gain of the quadratic boost converter is given by:

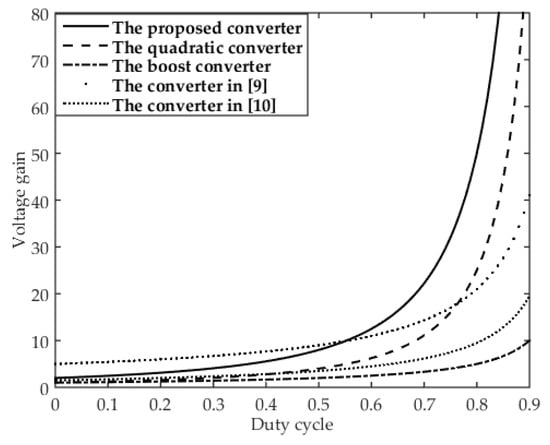

The comparison between the voltage gain and duty cycle of the proposed converter and other converters are plotted in Figure 4. According to Equations (24)–(26) and from Figure 4, one can observe that the voltage gain of the proposed converter is higher than that of a conventional boost converter and twice as much as that of quadratic converter under the same duty cycle. The voltage gain of the converter in [9] where a coupling inductor exists is higher than the proposed converter at the duty cycle under 0.55. However, the proposed converter provides the highest voltage gain among these converters when the duty cycle is larger than 0.55.

Figure 4.

Voltage gain comparison of converters.

2.2.2. The Power Device Stresses

The voltage across the switch (Q) equals when it is turned off. During modes 1, 5, and 6, is reverse biased, meaning this voltage of can be described as follows:

The maximum voltage stresses of the switch (Q) and output diode () compared with those in [9,10] are given in Table 1. n, k represent the turns ratio of a coupling-inductor and switching capacitor stages in Table 1. It shows that the voltage stresses are half of those of a quadratic converter and boost converter at the same voltage level. The voltage stress in converters [9,10] changes with the duty cycle. Moreover, the switching voltage stresses of the proposed converter is also smaller than that of converters in [9,10].

Table 1.

The voltage stress comparison of key devices.

2.3. Key Parameters Design

Input inductances: When the switch is turned on, the current variation of the input inductor and can be described by:

The average current of the input inductor and in the whole period can be described by:

To ensure that the proposed converter is operating in CCM, the current variation (, ) of input inductors and must be smaller than double that of the average current (, ) in the whole period.

According to (28)–(32), the inductances are given by:

where f denotes the switching frequency.

Stored capacitors: , representing the voltage ripple of , can be described by:

According to (31), the capacitances of are calculated by:

thus, the capacitance of is also calculated by

Voltage multiplier capacitors: The maximum output power is limited by the energy stored in , . The output voltage will decrease if the load power increases above that of the nominal output power () [24]. In other words, the voltage multiplier will lose voltage boost effect and only operate as a clamp circuit. The capacitance of should be about ten times larger or more than . The minimum capacitance of is calculated by:

Resonant inductor: Half of the resonant period must be smaller than the duration of the switch turned on.

where denotes the resonant period of the voltage multiplier cell, and T denotes the switching period.

According to (39), the resonant inductance and capacitance must satisfy the following inequality:

The resonant inductor limits the current variation of the switch. Thus, the inductance can be selected according to the maximum current rate of change of a actual switch device. The minimum inductance is calculated by:

where is the maximum current change rate of the switch.

3. Modeling of the Proposed Converter

According to the aforementioned assumption and analysis, modes 1 and 4 were neglected. The current flowing into was also neglected. The voltages of and were considered as a constant. During modes 2 and 3, the switch was turned off, and the relative state equations can be described as (1)–(3) and

During modes 5 and 6, the switch was turned on, and the relative state equations can be described as (11)–(14). Thus, the switch model of the proposed converter operating in CCM can be written as:

where u is the control input which takes “0” to be the turned-off state and “1” as the turned-on state of the switch, respectively.

To design the proposed finite sliding mode controller for the converter, the output voltage was set as the control variable. The tracking error can be explicated as:

where is the voltage error, and is the reference voltage.

Taking the derivative of (44), one can obtain a differential equation. Then, substituting (43) into this equation yields:

4. Improved Finite Time Fast Terminal Sliding Mode

Many typical TSM and FTSM can be described as:

where , , , a is formed of , and p, q, , are both positive odd integers satisfying , , respectively.

It is evident that TSM accelerates the convergence rate within the vicinity of the equilibrium point and the state trajectory converges the sliding surface in finite time, owing to the non-linearly term . However, TSM also offers a relatively slow convergence rate when the system trajectory stays at a distance from the equilibrium point. Based on (42), it can be concluded that the dynamics are globally finite-time stable, and it reaches the steady state within the time:

In FTSM, guarantees the convergence rate when the system dynamic is far away from the equilibrium point. Moreover, determines finite time convergence when the system state trajectory is close to the equilibrium point. Thus, the dynamic converges quickly in the whole convergence process, and converges to an equilibrium point within the time:

where represents the Hypergeometric Function [25], and the coefficients of , a, , attract to keep convergent.

In order to accelerate the convergence rate further, an improved NFTSM scheme was proposed as follows:

where , , , b, c are also formed of , respectively. , , , are both positive odd integers satisfying , , . It is concluded that the system will arrive at the equilibrium point, and the convergence time is given by:

From the above equation, it is observed that the convergence time of is shorter than and because of the extra item, .

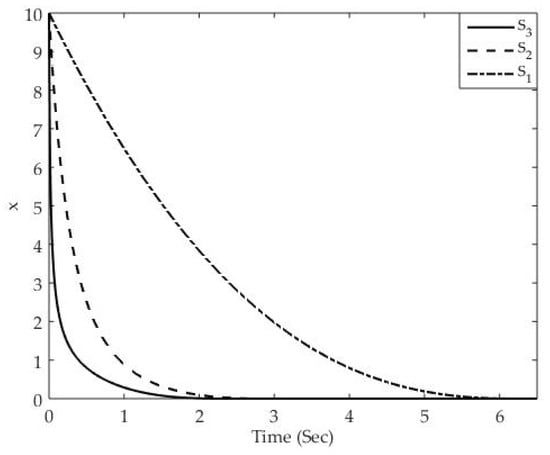

There is a convergence performance comparison between TSM, FTSM, and the improved NFTSM. The following sliding modes are considered:

with the initial value . The corresponding response curves are given by Figure 5. It can be seen that the improved NFTSM () has a faster convergence rate than FTSM () and TSM ().

Figure 5.

The comparison of convergence performance between NFTSM, FTSM, and TSM.

5. Controller Design of DC-DC Converter

Now, consider the dynamical system (45), according to the scheme of NFTSM, the switching surface is defined as follows:

For the proposed converter with a single switch, a general control law satisfying the hitting condition can be plotted as:

To guarantee that the system state stays within the vicinity of the sliding surface, the existence condition derived from Lyapunov’s direct method must be obeyed:

where is the time derivative of , and is shown as follows:

Substituting (56) into (55) gives the following existence condition:

every coefficient must be satisfied by (57), considering the minimum of the load.

To overcome a variable switching frequency of this system suffering external disturbance, an equivalent sliding mode control with constant operation frequency is adopted.

Equating

yields the equivalent control input:

To improve the transient response, an exponential reaching law is chosen, and can be expressed as:

where , are positive parameters.

When (60) is solved for u, the control input can be obtained as:

Finally, the control input u and ramp signal with a constant frequency were fed into a pulse-width modulator to produce the practical control input. Thanks to u, the system converged quickly to an equilibrium point within a finite time. It should be noted that no singularity exists during the whole process, owing to .

Theorem 1.

For the system (45), when the control input is chosen as (61), the system trajectory will then converge quickly to a steady state within a finite time.

Proof of Theorem 1.

Consider the Lyapunov function candidate as:

whose time derivative is

It can be seen that when , , the system state will slide to the sliding mode within a finite time. When , by substituting (61) into the second equation of (45), one can obtain:

Equation (64) can be rewritten as:

This equation indicates that for and for . Therefore, the system trajectory will continue moving to an equilibrium point instead of staying on the state of and . Moreover, it can be assumed that there exists a vicinity of , , ( is a positive constant) and satisfying for and for , respectively. Therefore, the crossing of trajectories between two boundaries of is achieved in a finite time, and the trajectory from the region reach the boundaries in finite time too. It can be summarized that the system controlled by (61) can converge to from any initial state within a finite time. This completes the proof. □

6. Experimental Results

To illustrate the effectiveness of the previous theoretical analysis, a laboratory prototype of the proposed converter was built and experimented. The related parameters of this system are shown in Table 2.

Table 2.

Related parameters of this system.

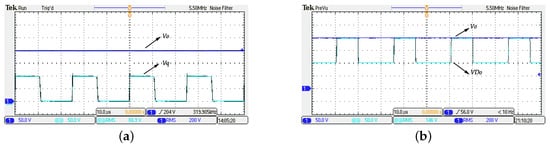

Figure 6 shows the voltage waveforms across the switch and output diode (), respectively when the output voltage is at 200 V. From (a), it shows that the voltage of the switch equals to 100 V at the “OFF” state, with a small voltage spike about 10 V at the moment when the switch turned off. The subgraph (b) shows that the anode voltage of the output diode () to the ground reaches 100 V at the reversed state when the cathode voltage is at 200 V with no voltage spike. One can see that the voltage stress of the output diode arrives at 100 V equalling to half of the output voltage too. Therefore, the voltage stresses of the output diode and switch have been alleviated.

Figure 6.

The performance of the proposed converter: (a) the voltage wave of the switch (Q); (b) the voltage wave of the output diode ().

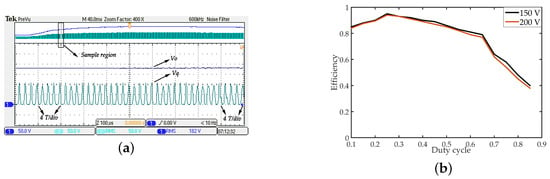

Figure 7a indicates that the switching waveform maintains about four periods in a grid that represents 100 s against a variational output voltage. One can see that the equivalent control (u) keeps the switching period constant, at about 25 s.

Figure 7.

The experiment performance of the proposed converter: (a) the switching frequency against the output voltage variation; (b) the efficiency versus duty cycle and output voltage.

The efficiency versus a wide range of duty cycle and output voltage is plotted in Figure 7b. It shows that the peak efficiency reaches 95% at , V. The efficiency reduces with the increase of the duty cycle, due to an increasing duty cycle accompanied by a more severe conduction loss of the switch and reverse loss of diodes. In addition, the efficiency, at a 150 V output voltage, only has a small advantage than when the output voltage is 200 V, meaning that the output voltage also has a slight impact on the efficiency. This is because the improved output voltage aggravates the heat loss of inductors and capacitors.

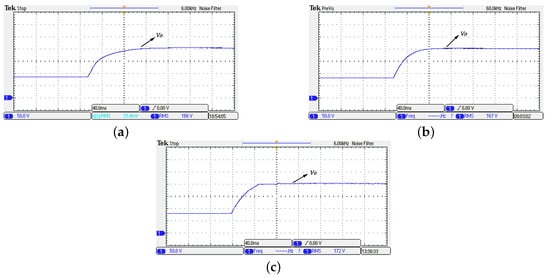

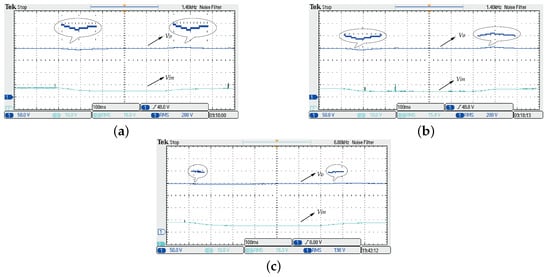

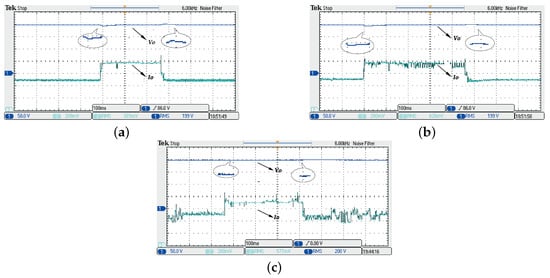

An experiment was also carried out for the performance analysis of the proposed NFTSM controller. The result is given in Figure 8, Figure 9 and Figure 10. The startup transient response is shown in Figure 8, the output voltage against input voltage variation plots in Figure 9, and the output voltage versus load disturbance is illustrated in Figure 10, respectively.

Figure 8.

The transient response of the system: (a) controlled by the TSM controller (); (b) controlled by the FTSM controller (); (c) controlled by the proposed NFTSM controller ().

Figure 9.

The response of the system versus input voltage variation: (a) controlled by the TSM controller (); (b) controlled by the FTSM controller (); (c) controlled by the proposed NFTSM controller ().

Figure 10.

The response of the system against load disturbance: (a) Controlled by the TSM controller (); (b) controlled by the FTSM controller (); (c) controlled by the proposed NFTSM controller ().

Figure 8 shows the transient response of the output voltage. Figure 8c, one can seen that the output voltage controlled by the proposed controller can track the reference value (200 V) with no overshoot, and has a settling time about 48 ms. Figure 8a, the system controlled by the TSM controller () takes 104 ms to reach the reference value (200 V), and the system controlled by the FTSM controller () has a settling time of 64 ms in Figure 8b. we can notice that the proposed controller has a 29.4%, 64.8% settling time improvement than FTSM and TSM, respectively, in this system.

Figure 9 shows the steady output voltage () comparison against input voltage disturbance. The input voltage changes from 17 V to 15 V (11.7%) and then returns to 17 V. From the Figure 9c, the output voltage () response exhibits no obvious variation. Figure 9a, one can see that the output voltage () response controlled by the TSM controller () takes about 100 ms to recover to the reference value, accompanied by a variation of 10 V (5%). The output voltage () response controlled by the FTSM controller () has a 80 ms recovery time, and a variation of 10 V too in Figure 9b. However, a sharp voltage spike was not visible in the three responses.

The steady output voltage response versus the output load variation is demonstrated in Figure 10. Here, resistance changes of −150 (−30% variation) were added to a nominal output load of 500 , and then the load returned to 500 . Figure 10c, one can see that the output voltage controlled by the proposed controller almost remains constant at the reference value. Figure 10a, the output voltage controlled by the TSM () controller has a slight voltage variation of about 8 V, and takes about 60 ms of recovery time after the moment where the load’s resistance has been decreased, and has a settling time of 25 ms with a variation of 8 V after the moment of the load’s resistance turns back. Figure 10b, the output voltage controlled by the FTSM () controller has 80 ms recovery time with a variation of 5 V after the instant where the load’s resistance is been changed the first time; then, it takes 40 ms to reach the reference signal with a small variation after the moment of the load’s resistance turning back. According to Figure 9 and Figure 10, it can be seen that the proposed NFTSM controller has the strongest robustness amongst the three methods. Based on the above results, it can be noticed that the proposed controller has faster convergence time and greater robustness compared with the TSM () and FTSM () controller. Thus, the proposed control scheme is more superior than the TSM and FTSM control strategies for the high step-up converter. In addition, there was no sharp voltage spike in the voltage waveforms of the switch, diodes, and output voltage at different test conditions, meaning that some low-cost elements can be used.

7. Conclusions

A high step-up DC-DC converter based on a single-switch quadratic boost converter and a limited time converge fast terminal sliding mode control strategy was proposed in this paper. Firstly, the operation modes, performance discussion, and key parameter design of the proposed converter were presented. Owing to the voltage multiplier cell, the voltage gain of the proposed converter was highly enhanced; in particular, the peak efficiency reached 95% at an output voltage range of (100 V–200 V). At the mean time, the voltage stresses of the switch and diodes (, , ) were decreased to half of the output voltage, and the conversion efficiency was improved. Then, a new finite-time NFTSM scheme was proposed. This can provide a faster convergence rate and stronger robustness than the conventional TSM and FTSM schemes. In particular, the singularity problem does not exist during the whole convergence process. Finally, the proposed controller was applied to the converter to stabilize it and track the reference signal. The experiment demonstrates that the system controlled by the proposed controller can track the reference voltage with a short settling time of about 48 ms and no overshoot. The strong robustness of the proposed controller against input voltage variation and load disturbances was also verified.

Author Contributions

Y.L. designed the NFTSM controller and accomplished the theoretical proof; J.W. designed the topology of the proposed converter, implemented the experiments, and wrote the paper; H.T. designed the circuit and analysed the data.

Acknowledgments

This research was supported by Science and Technology Support Program of Sichuan Province (Grant No. 2016GZ0104).

Conflicts of Interest

The authors declare no conflict of interest. The founding sponsors had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, and in the decision to publish the results.

References

- Das, M.; Agarwal, V. Novel High-Performance Stand-Alone Solar PV System With High-Gain High-Efficiency DC-DC Converter Power Stages. IEEE Trans. Ind. Appl. 2015, 51, 4718–4728. [Google Scholar] [CrossRef]

- Pahlevaninezhad, M.; Das, P.; Drobnik, J.; Jain, P.K.; Bakhshai, A. A novel zvzcs full-bridge dc/dc converter used for electric vehicles. IEEE Trans. Power Electron. 2012, 27, 2752–2769. [Google Scholar] [CrossRef]

- Lai, C.M.; Cheng, Y.H.; Hsieh, M.H.; Lin, Y.C. Development of a bidirectional dc/dc converter with dual-battery energy storage for hybrid electric vehicle system. IEEE Trans. Veh. Technol. 2018, 67, 1036–1052. [Google Scholar] [CrossRef]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power electronics converter, applications and design. Microelectronics 1997, 28, 105–106. [Google Scholar]

- Forouzesh, M.; Shen, Y.; Yari, K.; Siwakoti, Y.P.; Blaabjerg, F. High-efficiency high step-up dc-dc converter with dual coupled inductors for grid-connected photovoltaic systems. IEEE Trans. Power Electron. 2018, 33, 5967–5982. [Google Scholar] [CrossRef]

- Shi, Y.; Yang, X. Wide Load Range ZVS Three-Level DC–DC Converter: Four Primary Switches, Capacitor Clamped, Two Secondary Switches, and Smaller Output Filter Volume. IEEE Trans. Power Electron. 2016, 28, 3431–3443. [Google Scholar] [CrossRef]

- Wong, Y.S.; Chen, J.F.; Liu, K.B.; Hsieh, Y.P. A novel high step-up dc-dc converter with coupled inductor and switched clamp capacitor techniques for photovoltaic systems. Energies 2017, 10. [Google Scholar] [CrossRef]

- Wong, Y.S.; Chen, J.F.; Liu, K.B.; Jimichi, T.; Fujita, H.; Akagi, H. A Dynamic Voltage Restorer Equipped With a High-Frequency Isolated DC-DC Converter. IEEE Trans. Ind. Appl. 2011, 47. [Google Scholar] [CrossRef]

- Saravanan, S.; Babu, N.R. Design and development of single switch high step-up dc-dc converter. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 855–863. [Google Scholar] [CrossRef]

- Wong, Y.S.; Chen, J.F.; Liu, K.B. Realizability conditions and bounds on synthesis of switched-capacitor DC-DC voltage multiplier circuits. IEEE Trans. Circuits Syst. I 1997, 44, 684–691. [Google Scholar] [CrossRef]

- Leyva-Ramos, J.; Ortiz-Lopez, M.G.; Diaz-Saldierna, L.H. Switching regulator using a quadratic boost converter for wide DC conversion ratios. IET Power Electron. 2009, 8, 605–613. [Google Scholar] [CrossRef]

- Zhang, N.; Sutanto, D.; Muttaqi, K.M.; Zhang, B. High-voltage-gain quadratic boost converter with voltage multiplier. IET Power Electron. 2015, 8, 2511–2519. [Google Scholar] [CrossRef]

- Beni, S.H.; Mirtalaei, S.M.M.; Kianpour, A.; Beni, S.A. Design and improvement of a soft switching high step-up boost converter with voltage multiplier. IET Power Electron. 2017, 10, 2163–2169. [Google Scholar] [CrossRef]

- López, M.; De Vicuña, L.G.; Castilla, M.; Gayà, P.; López, O. Current distribution control design for paralleled DC/DC converters using sliding-mode control. IEEE Trans. Ind. Electron. 2004, 51, 419–428. [Google Scholar] [CrossRef]

- Babazadeh, A.; Maksimovic, D. Hybrid Digital Adaptive Control for Fast Transient Response in Synchronous Buck DC-DC Converters. IEEE Trans. Power Electron. 2009, 24, 2625–2638. [Google Scholar] [CrossRef]

- Hsu, C.F.; Lee, T.T.; Wen, Y.W.; Ding, F.S. Intelligent Control for DC-DC Power Converter with Recurrent Fuzzy Neural Network Approach. In Proceedings of the 2006 IEEE International Conference on Fuzzy Systems, Vancouver, BC, Canada, 16–21 July 2006. [Google Scholar] [CrossRef]

- Wai, R.; Shih, L. Design of Voltage Tracking Control for DC-DC Boost Converter Via Total Sliding-Mode Technique. IEEE Trans. Ind. Electron. 2011, 58, 2505–2511. [Google Scholar] [CrossRef]

- Tan, S.C.; Lai, Y.M.; Chi, K.T. General design issues of sliding-mode controllers in DC-DC converters. IEEE Trans. Ind. Electron. 2008, 55, 1160–1174. [Google Scholar] [CrossRef]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. A unified approach to the design of pwm-based sliding-mode voltage controllers for basic dc-dc converters in continuous conduction mode. IEEE Trans. Circuits Syst. 2006, 53, 1816–1827. [Google Scholar] [CrossRef]

- He, Y.; Luo, F.L. Sliding-mode control for dc-dc converters with constant switching frequency. IEE Proc. Control Theory Appl. 2006, 53, 37–45. [Google Scholar] [CrossRef]

- Wu, Y.Q.; Yu, X.; Man, Z. Terminal sliding mode control design for uncertain dynamic systems. Syst. Control Lett. 1998, 34, 281–288. [Google Scholar] [CrossRef]

- Yu, X.; Man, Z. Fast terminal sliding-mode control design for nonlinear dynamical systems. IEEE Trans. Circuits Syst. 2002, 49, 261–264. [Google Scholar] [CrossRef]

- Abramowitz, M.; Stegun, I.A. The title of the cited contribution. In Handbook of Mathematical Functions: With Formulas, Graphs, and Mathematical Tables; Publishing House: New York, NY, USA, 1972. [Google Scholar]

- Prudente, M.; Pfitscher, L.L.; Emmendoerfer, G.; Romaneli, E.F.; Gules, R. Voltage Multiplier Cells Applied to Non-isolated DC-DC Converters. IEEE Trans. Power Electron. 2008, 49, 871–887. [Google Scholar] [CrossRef]

- Feng, Y.; Yu, X.; Man, Z. Non-singular terminal sliding mode control of rigid manipulators. IET Power Electron. 2002, 38. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).