Integrated Control and Modulation for Three-Level NPC Rectifiers

Abstract

1. Introduction

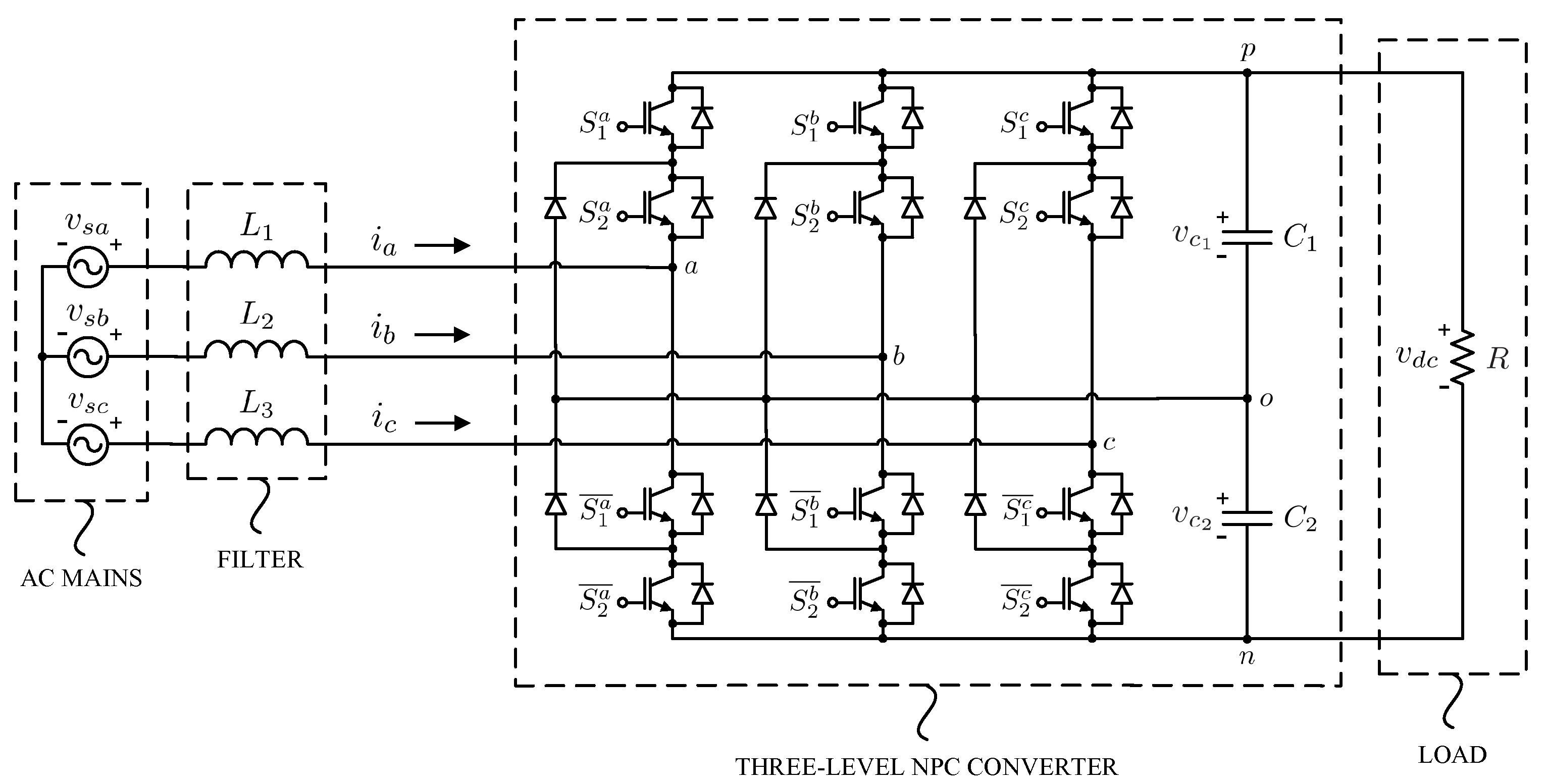

2. Dynamic Model of the System

Considered System Model

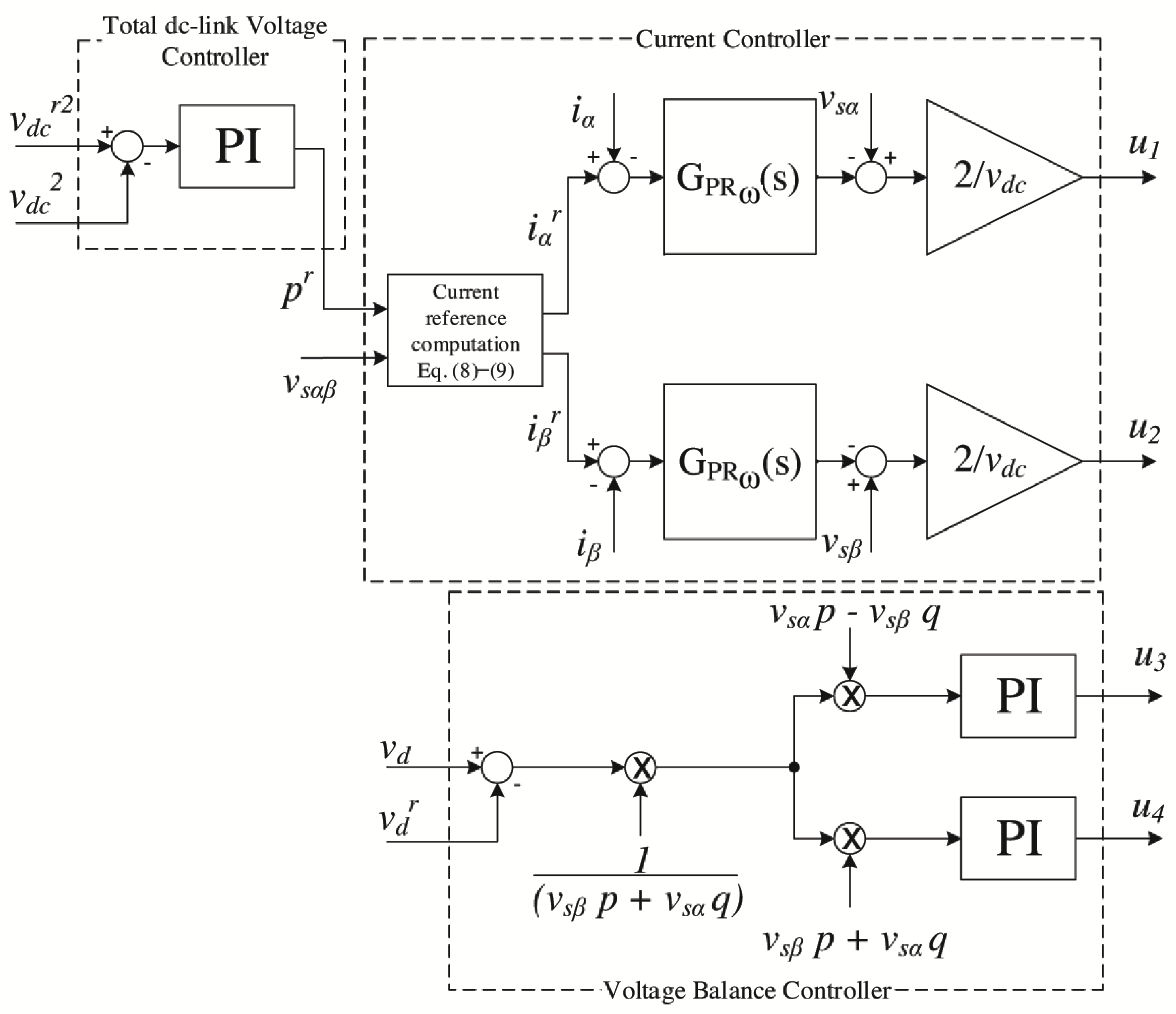

3. Controller Design

3.1. Total DC-Link Voltage Controller

3.2. Current Controller

3.3. Voltage Balance Controller

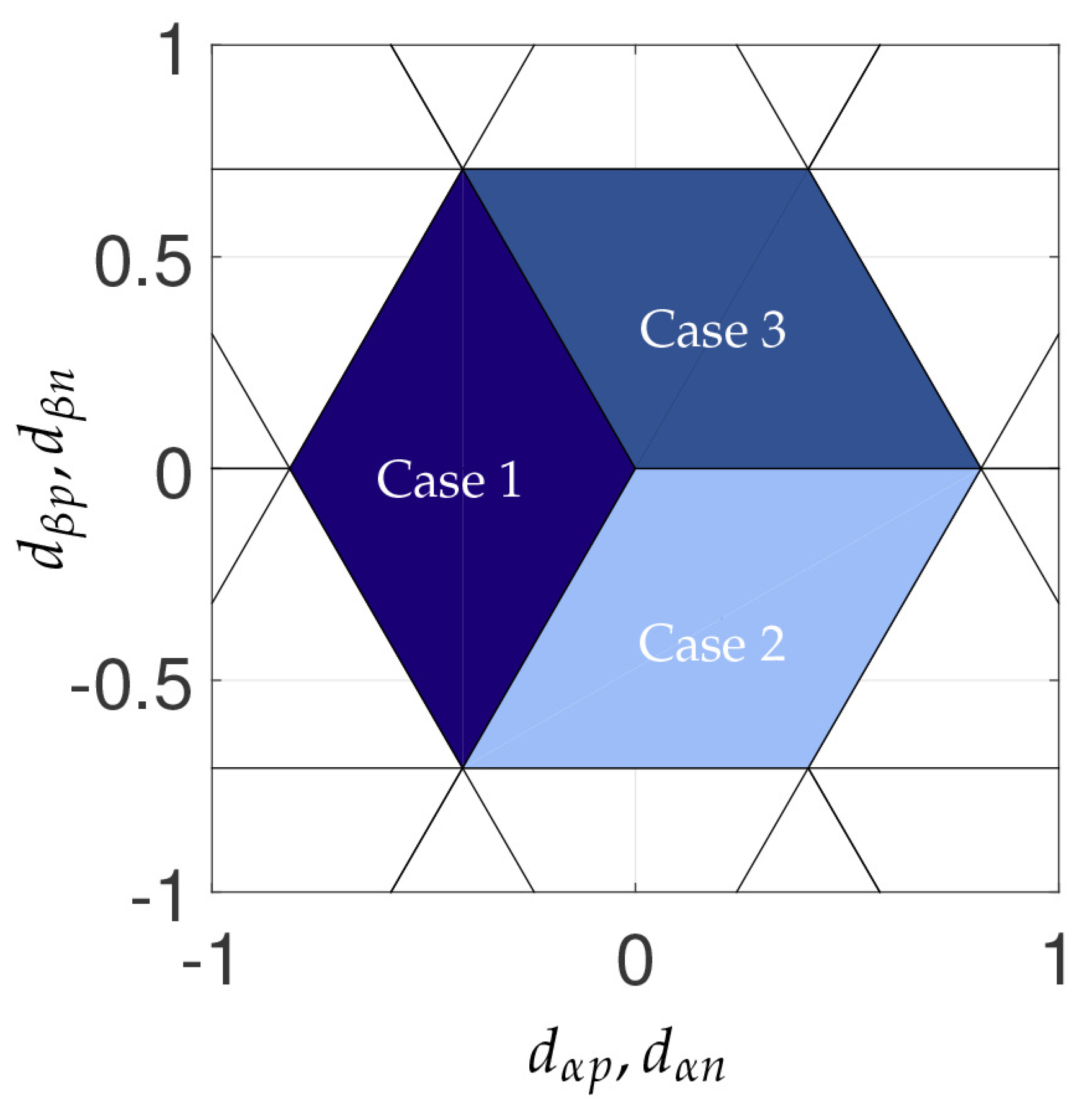

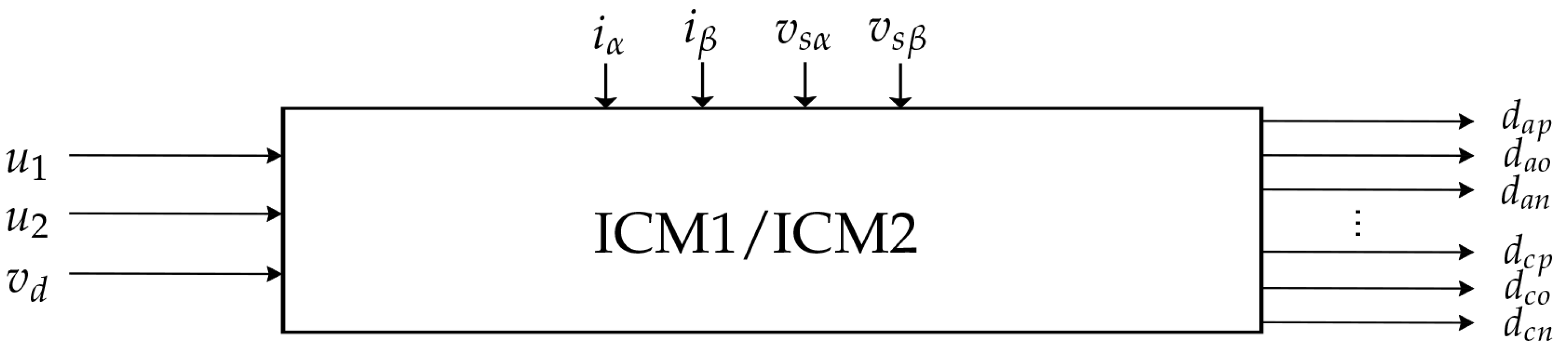

4. Modulation Strategy

4.1. First Proposal, ICM1

4.2. Second Proposal, ICM2

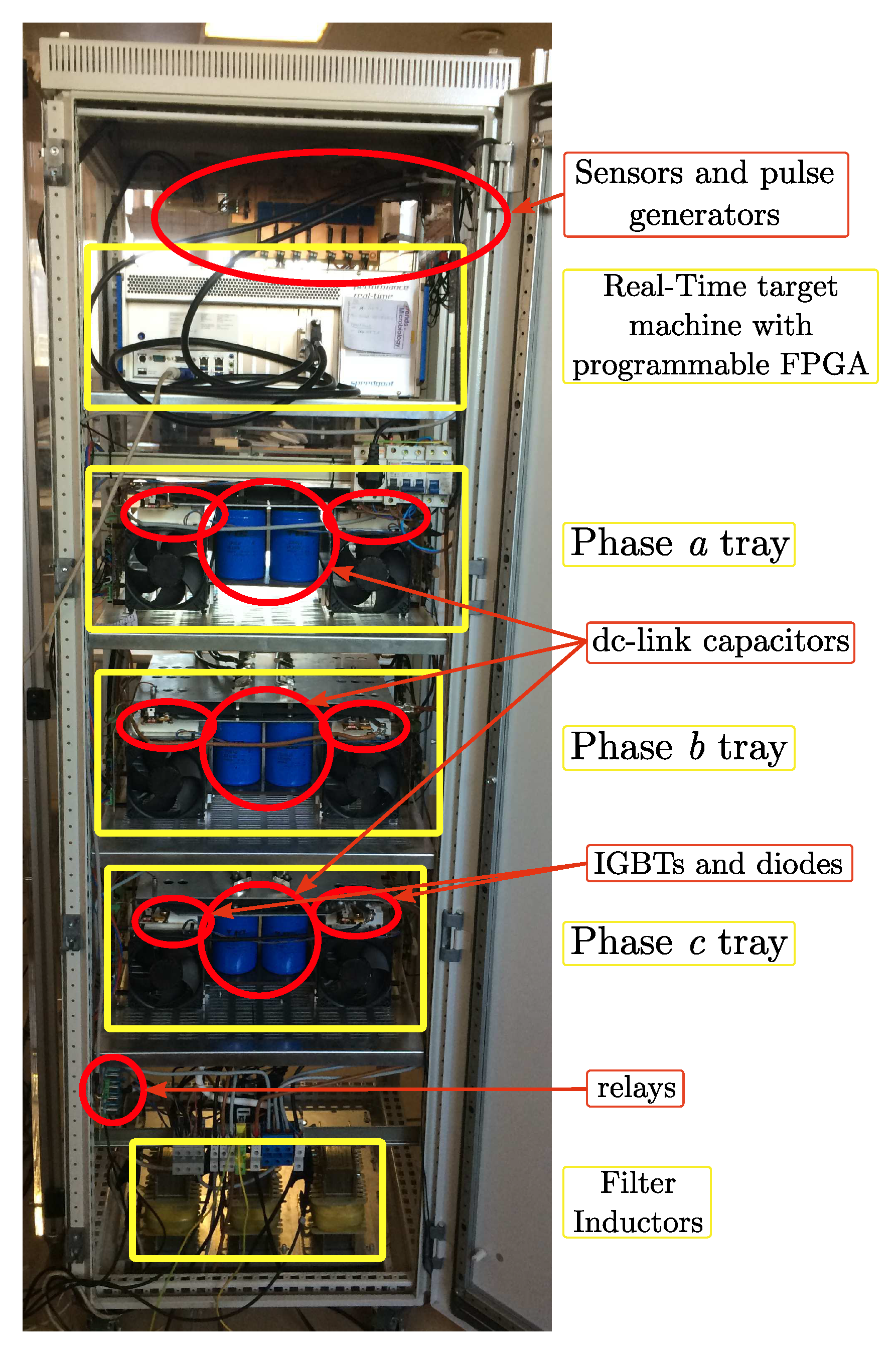

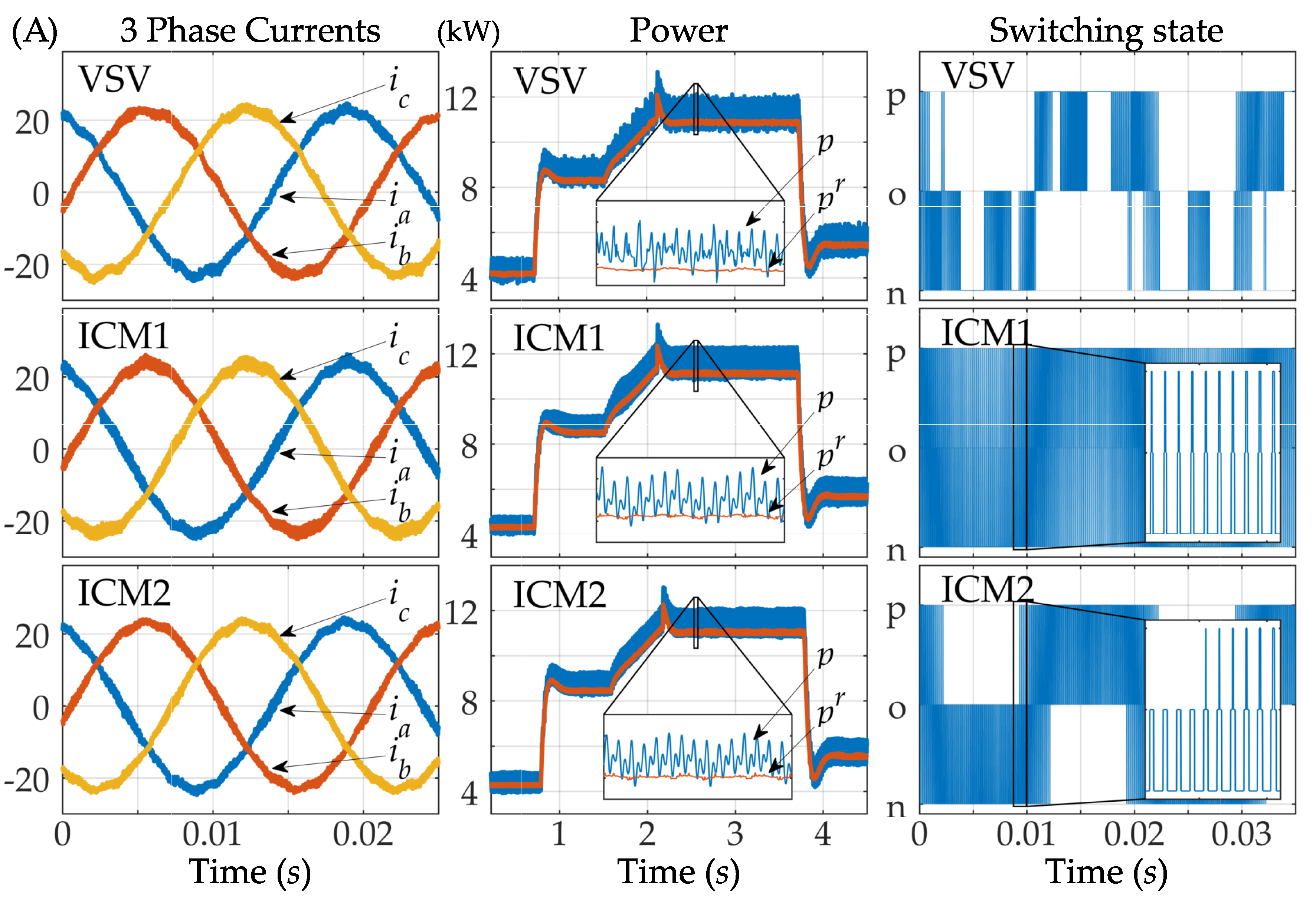

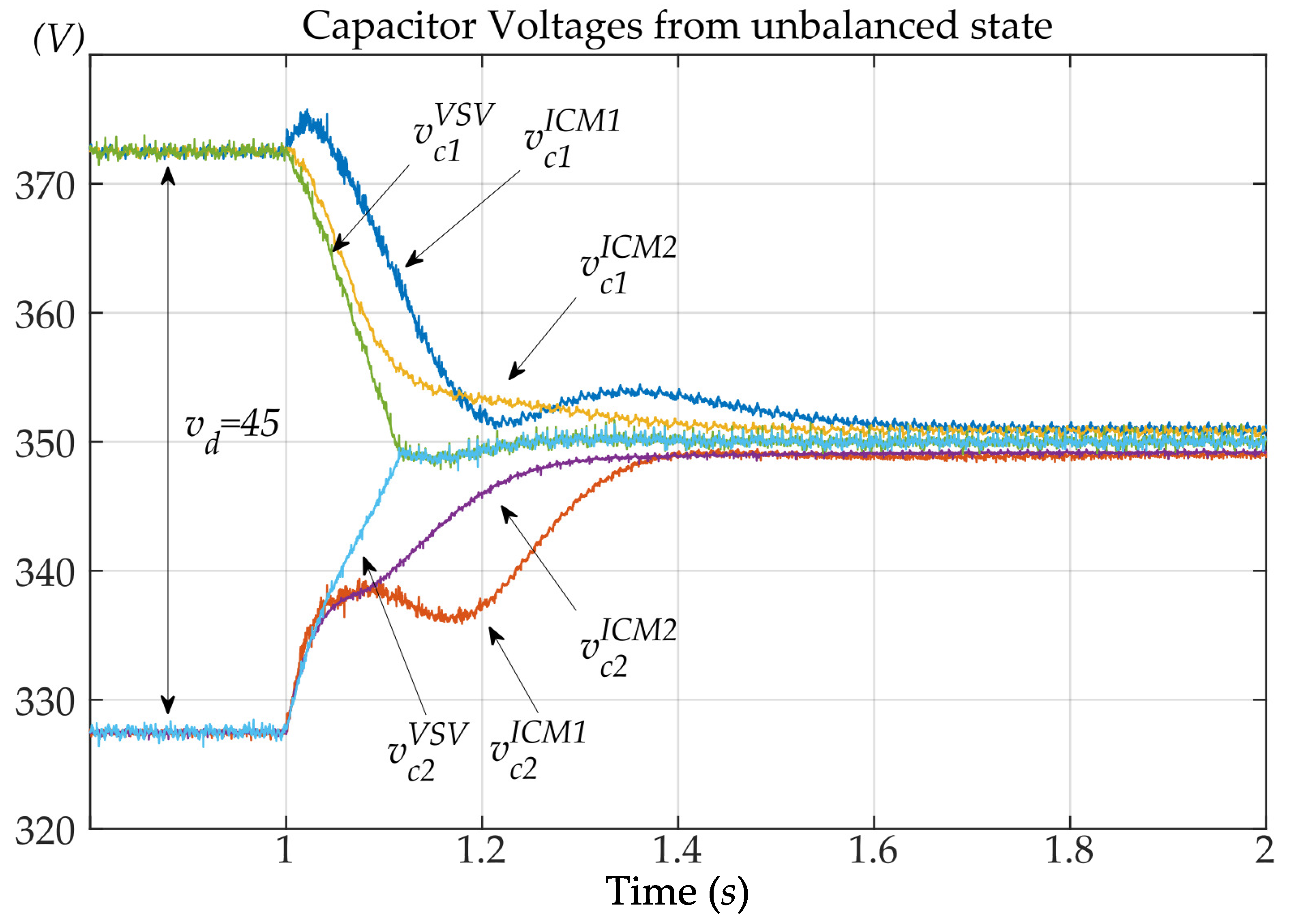

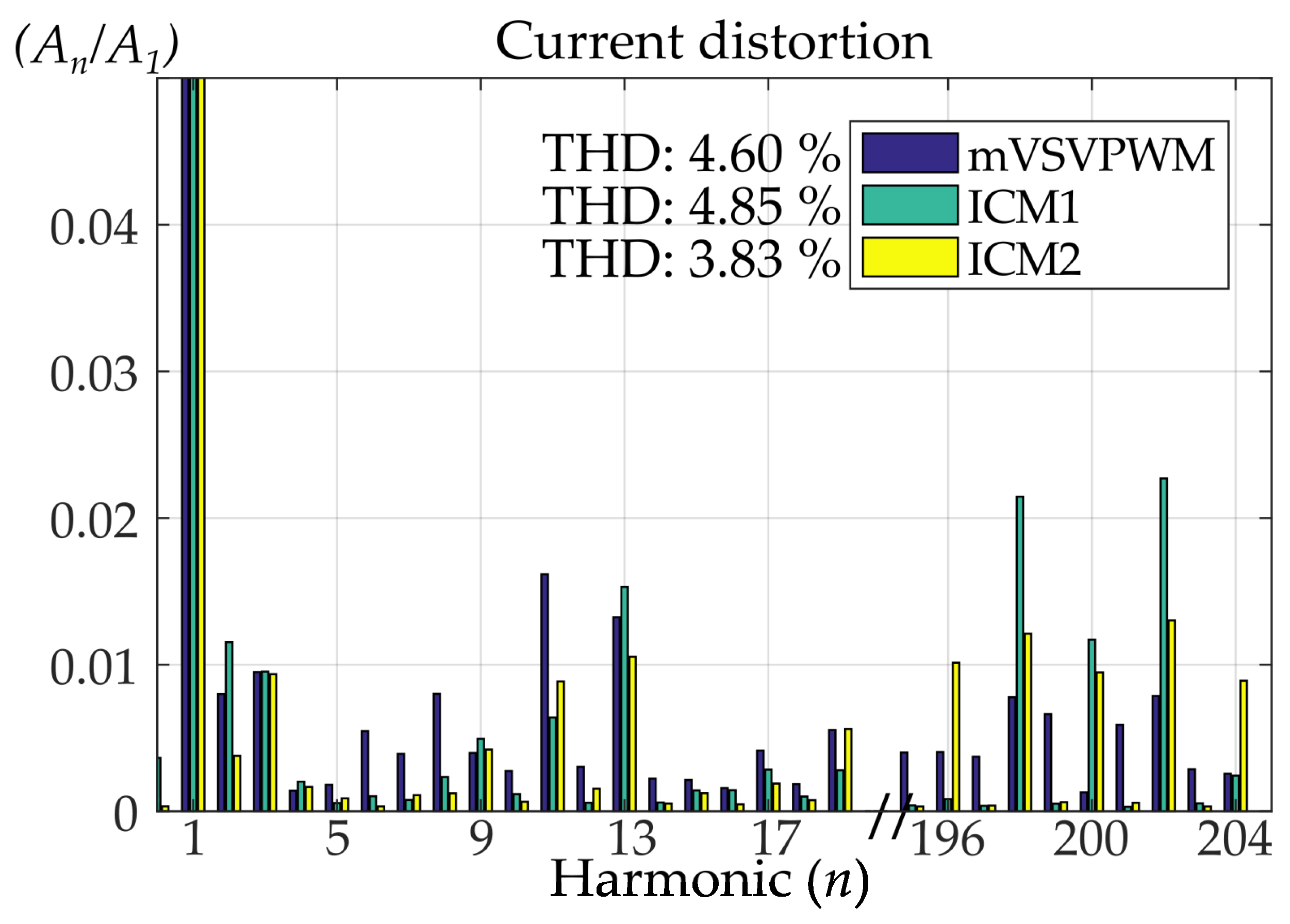

5. Experimental Verification

6. Concluding Remarks

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| NPC | Neutral Point Clamped |

| PWM | Pulse Width Modulation |

| SVM | Space Vector Modulation |

| CB-PWM | Carrier Based Pulse Width Modulation |

| DPC | Direct Power Control |

| ICM | Integrated Control and Modulation |

| ICM1 | Integrated Control and Modulation variant 1 |

| ICM2 | Integrated Control and Modulation variant 2 |

| mVSVPWM | Modified Virtual Space Vector Modulation |

| THD | Total Harmonic Distortion |

References

- Franquelo, L.G.; Rodríguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.A.M. The Age of Multilevel Converters Arrives. IEEE Ind. Electron. Mag. 2008, 2, 28–39. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.; Wu, B.W.B.; Rodriguez, J.; Pérez, M.; Leon, J. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Zhang, J.; Xu, S.; Din, Z.; Hu, X.; Zhang, J.; Xu, S.; Din, Z.; Hu, X. Hybrid Multilevel Converters: Topologies, Evolutions and Verifications. Energies 2019, 12, 615. [Google Scholar] [CrossRef]

- Rodríguez, J.; Bernet, S.; Wu, B.; Pontt, J.O.; Kouro, S. Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Rodriguez, J.; Kazmierkowski, M.P.; Espinoza, J.R.; Zanchetta, P.; Abu-Rub, H.; Young, H.A.; Rojas, C.A. State of the art of finite control set model predictive control in power electronics. IEEE Trans. Ind. Inform. 2013, 9, 1003–1016. [Google Scholar] [CrossRef]

- Krishna, R.; Soman, D.E.; Kottayil, S.K.; Leijon, M. Pulse delay control for capacitor voltage balancing in a three-level boost neutral point clamped inverter. IET Power Electron. 2015, 8, 268–277. [Google Scholar] [CrossRef]

- Von Jouanne, A.; Dai, S.; Zhang, H. A multilevel inverter approach providing DC-link balancing, ride-through enhancement, and common-mode voltage elimination. IEEE Trans. Ind. Electron. 2002, 49, 739–745. [Google Scholar] [CrossRef]

- Stala, R. Application of balancing circuit for DC-link voltages balance in a single-phase diode-clamped inverter with two three-level legs. IEEE Trans. Ind. Electron. 2011, 58, 4185–4195. [Google Scholar] [CrossRef]

- Umbría, F.; Gordillo, F.; Salas, F.; Vázquez, S. Voltages Balance Control in Three Phase Three-Level NPC Rectifiers. In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 4–7 July 2010; pp. 3018–3023. [Google Scholar] [CrossRef]

- Pulikanti, S.R.; Dahidah, M.S.A.; Agelidis, V.G. Voltage Balancing Control of Three-Level Active NPC Converter Using SHE-PWM. IEEE Trans. Power Deliv. 2011, 26, 258–267. [Google Scholar] [CrossRef]

- Omri, B.; Ammous, K.; Ammous, A. New Method for Balancing Capacitors Voltages in NPC Inverter without DC-link Voltages Sensors. Int. J. Comput. Appl. 2013, 65, 17–24. [Google Scholar]

- Choudhury, A.; Pillay, P.; Williamson, S.S. DC-Bus Voltage Balancing Algorithm for Three-Level Neutral-Point-Clamped (NPC) Traction Inverter Drive With Modified Virtual Space Vector. IEEE Trans. Ind. Appl. 2016, 52, 3958–3967. [Google Scholar] [CrossRef]

- In, H.C.; Kim, S.M.; Lee, K.B.; In, H.C.; Kim, S.M.; Lee, K.B. Design and Control of Small DC-Link Capacitor-Based Three-Level Inverter with Neutral-Point Voltage Balancing. Energies 2018, 11, 1435. [Google Scholar] [CrossRef]

- Hammami, M.; Rizzoli, G.; Mandrioli, R.; Grandi, G.; Hammami, M.; Rizzoli, G.; Mandrioli, R.; Grandi, G. Capacitors Voltage Switching Ripple in Three-Phase Three-Level Neutral Point Clamped Inverters with Self-Balancing Carrier-Based Modulation. Energies 2018, 11, 3244. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Bordonau, J.; Boroyevich, D.; Somavilla, S. The Nearest Three Virtual Space Vector PWM—A Modulation for the Comprehensive Neutral-Point Balancing in the Three-Level NPC Inverter. IEEE Power Electron. Lett. 2004, 2, 11–15. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Ortega, J.; Bordonau, J.; Beristain, J.; Rocabert, J. Closed-Loop Control of a Three-Phase Neutral-Point-Clamped Inverter Using an Optimized Virtual-Vector-Based Pulsewidth Modulation. IEEE Trans. Ind. Electron. 2008, 55, 2061–2071. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T.A. Pulse Width Modulation for Power Converters: Principles and Practice; Wiley-IEEE Press: Piscataway, NJ, USA, 2003; p. 724. [Google Scholar]

- Leon, J.I.; Kouro, S.; Franquelo, L.G.; Rodriguez, J.; Wu, B. The Essential Role and the Continuous Evolution of Modulation Techniques for Voltage-Source Inverters in the Past, Present, and Future Power Electronics. IEEE Trans. Ind. Electron. 2016, 63, 2688–2701. [Google Scholar] [CrossRef]

- Holtz, J. Pulse width Modulation-A Survey. IEEE Trans. Ind. Electron. 1992, 39, 410–420. [Google Scholar] [CrossRef]

- Pan, Z.; Peng, F.Z. A sinusoidal PWM method with voltage balancing capability for diode-clamped five-level converters. IEEE Trans. Ind. Appl. 2009, 45, 1028–1034. [Google Scholar] [CrossRef]

- Rodríguez, J.; Morán, L.; Silva, C.; Correa, P. A high performance vector control of a 11-level inverter. In Proceedings of the IPEMC 2000: 3rd International Power Electronics and Motion Control Conference, Beijing, China, 15–18 August 2000; Volume 3, pp. 1116–1121. [Google Scholar]

- Noguchi, T.; Tomiki, H.; Kondo, S.; Takahashi, I. Direct power control of PWM converter without power-source voltage sensors. IEEE Trans. Ind. Appl. 1998, 34, 473–479. [Google Scholar] [CrossRef]

- Kouro, S.; Cortés, P.; Vargas, R.; Ammann, U.; Rodríguez, J. Model Predictive Control-A Simple and Powerful Method to Control Power Converters. IEEE Trans. Ind. Electron. 2009, 56, 1826–1838. [Google Scholar] [CrossRef]

- Vazquez, S.; Leon, J.I.; Franquelo, L.G.; Rodríguez, J.; Young, H.A.; Marquez, A.; Zanchetta, P. Model Predictive Control: A Review of Its Applications in Power Electronics. IEEE Ind. Electron. Mag. 2014, 8, 16–31. [Google Scholar] [CrossRef]

- Umbría, F.; Gordillo, F.; Salas, F. Model-based NPC Converter Regulation for Synchronous Rectifier Applications. In Proceedings of the IECON 2014—40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; pp. 4669–4675. [Google Scholar] [CrossRef]

- Alepuz, S.; Busquets-Monge, S.; Bordonau, J.; Gago, J.; González, D.; Balcells, J. Interfacing Renewable Energy Sources to the Utility Grid Using a Three-Level Inverter. IEEE Trans. Ind. Electron. 2006, 53, 1504–1511. [Google Scholar] [CrossRef]

- Celanovic, N.; Boroyevich, D. A Fast Space-Vector Modulation Algorithm for Multilevel Three-Phase Converters. IEEE Trans. Ind. Appl. 2001, 37, 637–641. [Google Scholar] [CrossRef]

- Yao, W.; Hu, H.; Lu, Z. Comparisons of Space-Vector Modulation and Carrier-Based Modulation of Multilevel Inverter. IEEE Trans. Power Electron. 2008, 23, 45–51. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Vazquez, S.; Sanchez, J.A.; Carrasco, J.M.; Leon, J.I.; Galvan, E. A Model-Based Direct Power Control for Three-Phase Power Converters. IEEE Trans. Ind. Electron. 2008, 55, 1647–1657. [Google Scholar] [CrossRef]

- Malinowski, M.; Jasin, M.; Kazmierkowski, M.P. Simple Direct Power Control of Three-Phase PWM Rectifier Using Space-Vector. IEEE Trans. Ind. Electron. 2004, 51, 447–454. [Google Scholar] [CrossRef]

- Escobar, G.; Stankovic, A.; Carrasco, J.; Galván, E.; Ortega, R. Analysis and design of direct power control (DPC) for a three phase synchronous rectifier via output regulation subspaces. IEEE Trans. Power Electron. 2003, 18, 823–830. [Google Scholar] [CrossRef]

- Oruganti, H.; Dash, S.; Nallaperumal, C.; Ramasamy, S.; Oruganti, H.; Dash, S.S.; Nallaperumal, C.; Ramasamy, S. A Proportional Resonant Controller for Suppressing Resonance in Grid Tied Multilevel Inverter. Energies 2018, 11, 1024. [Google Scholar] [CrossRef]

- Teodorescu, R.; Blaabjerg, F.; Liserre, M.; Loh, P.C. Proportional-resonant controllers and filters for grid-connected voltage-source converters. IEE Proc. Electr. Power Appl. 2006, 153, 750–762. [Google Scholar] [CrossRef]

- Wei, S.; Wu, B.; Li, F.; Liu, C. A general space vector PWM control algorithm for multilevel inverters. In Proceedings of the Eighteenth Annual IEEE Applied Power Electronics Conference and Exposition, APEC’03, Miami Beach, FL, USA, 9–13 February 2003; Volume 1, pp. 562–568. [Google Scholar] [CrossRef]

- Tamasas, M.E.; Saleh, M.; Shaker, M.; Hammoda, A. Comparison of different third harmonic injected PWM strategies for 5-level diode clamped inverter. In Proceedings of the 2017 IEEE Power and Energy Conference at Illinois (PECI), Champaign, IL, USA, 23–24 February 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Bordonau, J.; Cosan, M.; Borojevic, D.; Mao, H.; Lee, F. A State-Space Model for the Comprehensive Dynamic Analysis of Three-Level Voltage-Source Inverters. In Proceedings of the PESC97 Record 28th Annual IEEE Power Electronics Specialists Conference, Saint Louis, MO, USA, 27 June 1997; Volume 2, pp. 942–948. [Google Scholar] [CrossRef]

- Antoniewicz, P.; Kazmierkowski, M. Virtual-Flux-Based Predictive Direct Power Control of AC/DC Converters with Online Inductance Estimation. IEEE Trans. Ind. Electron. 2008, 55, 4381–4390. [Google Scholar] [CrossRef]

| Parameter | Value | Parameter | Value | Parameter | Value |

|---|---|---|---|---|---|

| 250 rad/s | Sampling frequency () | 10 KHz | 1 | ||

| 230 | Switching frequency () | 10 KHz | 5 | ||

| L | 2 mH | 1 rad/s | 100 | ||

| C | 3300 | 700 → 800 V | 0.1 | ||

| R | 120 → 60 → 120 | 0.05 |

| Approach | THD Value | Number of Conmutations | Balancing Time (Figure 7) | Computational Burden (% Reduction) |

|---|---|---|---|---|

| mVSVPWM | 4.6% | 375 | 0.12 s | – |

| ICM1 | 4.85% | 800 | 0.50 s | 67% |

| ICM2 | 3.83% | 532 | 0.40 s | 61% |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ventosa-Cutillas, A.; Montero-Robina, P.; Umbría, F.; Cuesta, F.; Gordillo, F. Integrated Control and Modulation for Three-Level NPC Rectifiers. Energies 2019, 12, 1641. https://doi.org/10.3390/en12091641

Ventosa-Cutillas A, Montero-Robina P, Umbría F, Cuesta F, Gordillo F. Integrated Control and Modulation for Three-Level NPC Rectifiers. Energies. 2019; 12(9):1641. https://doi.org/10.3390/en12091641

Chicago/Turabian StyleVentosa-Cutillas, Antonio, Pablo Montero-Robina, Francisco Umbría, Federico Cuesta, and Francisco Gordillo. 2019. "Integrated Control and Modulation for Three-Level NPC Rectifiers" Energies 12, no. 9: 1641. https://doi.org/10.3390/en12091641

APA StyleVentosa-Cutillas, A., Montero-Robina, P., Umbría, F., Cuesta, F., & Gordillo, F. (2019). Integrated Control and Modulation for Three-Level NPC Rectifiers. Energies, 12(9), 1641. https://doi.org/10.3390/en12091641