A New Hybrid Multilevel Inverter Topology with Reduced Switch Count and dc Voltage Sources

Abstract

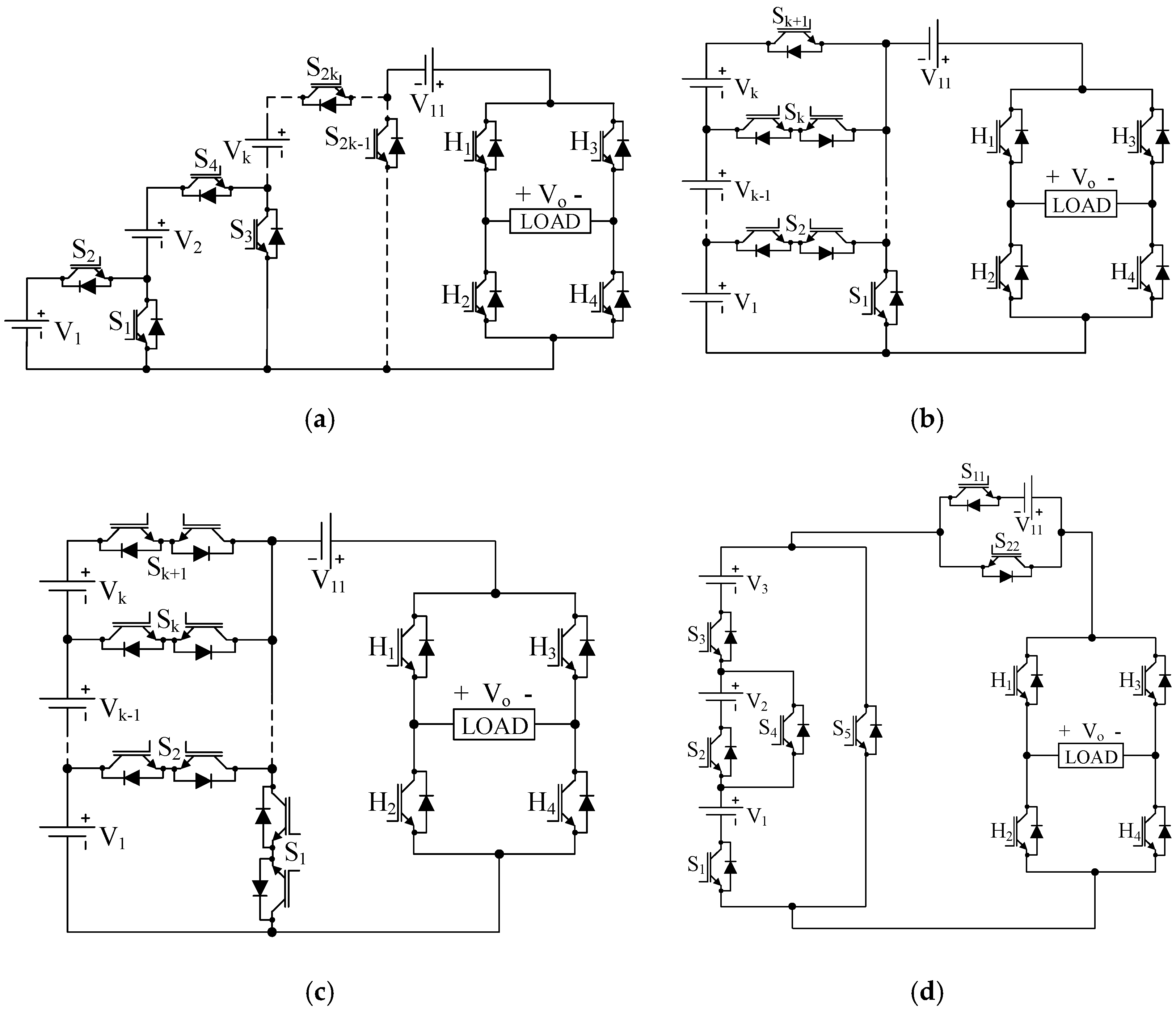

:1. Introduction

- The proposed MLI utilizes fewer switches to generate a higher number of levels.

- It also allows for parallel operation of the different dc voltage sources, thus allowing load sharing among different dc voltage sources. This results in equal loading stress across each dc voltage source

- The higher number of levels is achieved by incorporating an auxiliary module between the level generation and polarity changing parts.

- The zero level is obtained by introducing a switching scheme at the polarity changing circuit.

- The proposed topology is capable of handling inductive loads.

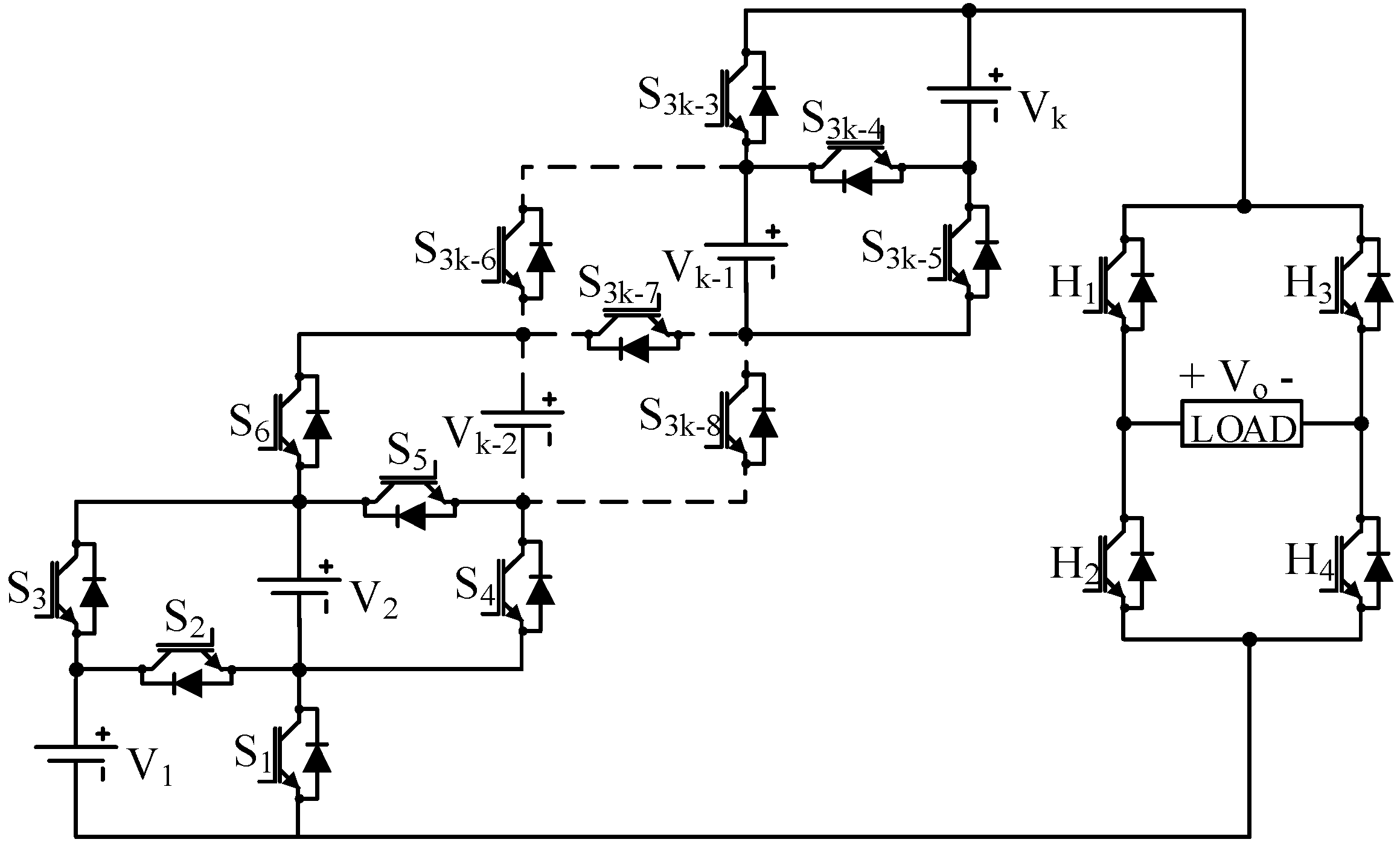

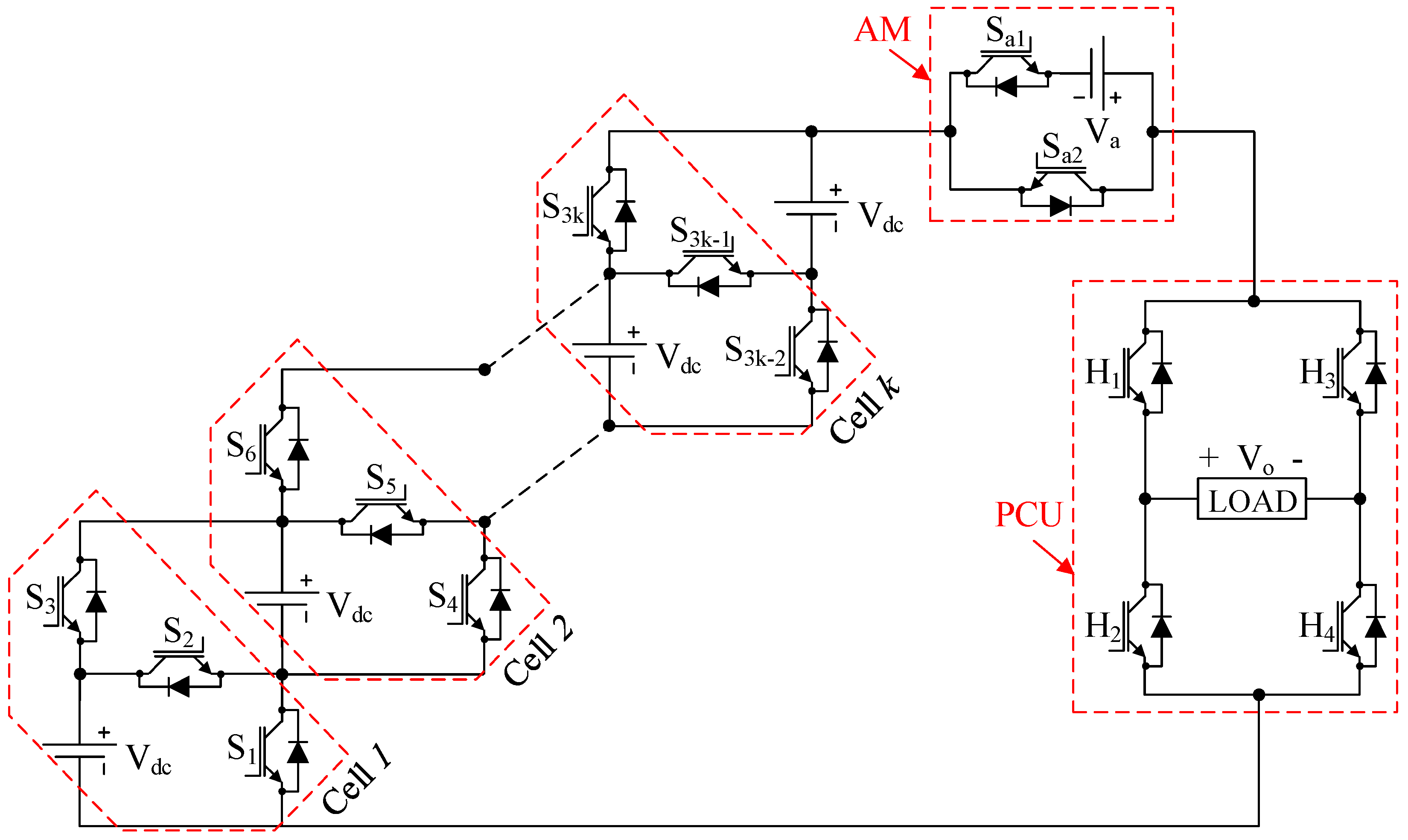

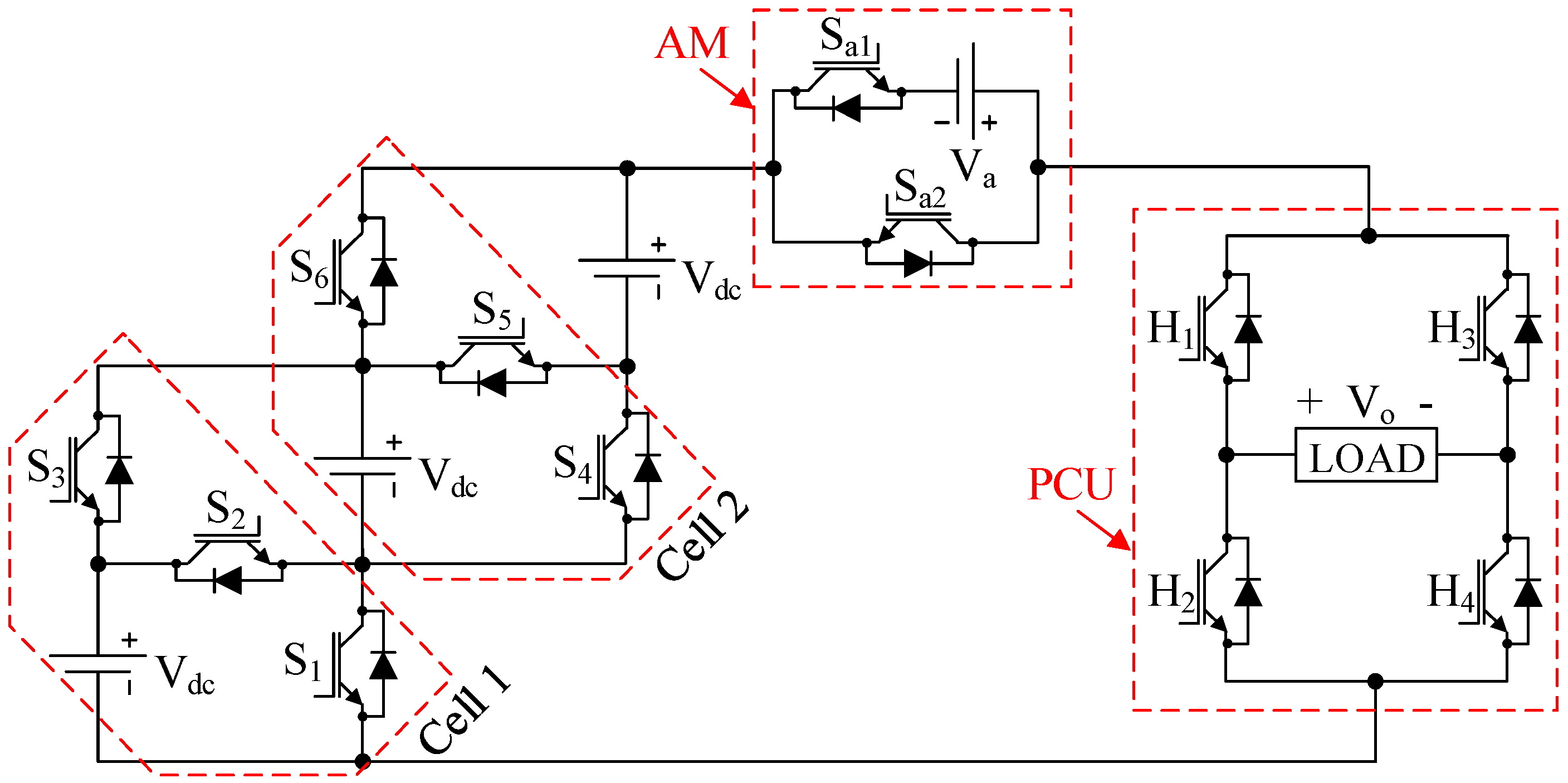

2. The Proposed Multilevel Inverter

2.1. Generalized Structure of the Topology

2.1.1. The Level Generation Module (LGM)

2.1.2. The Auxiliary Module (AM)

2.1.3. Polarity Changing Unit (PCU)

2.2. Working Principles

2.3. Selection of dc Source Magnitudes

2.3.1. Mode I

2.3.2. Mode II

2.4. Total Standing Voltage Calculation

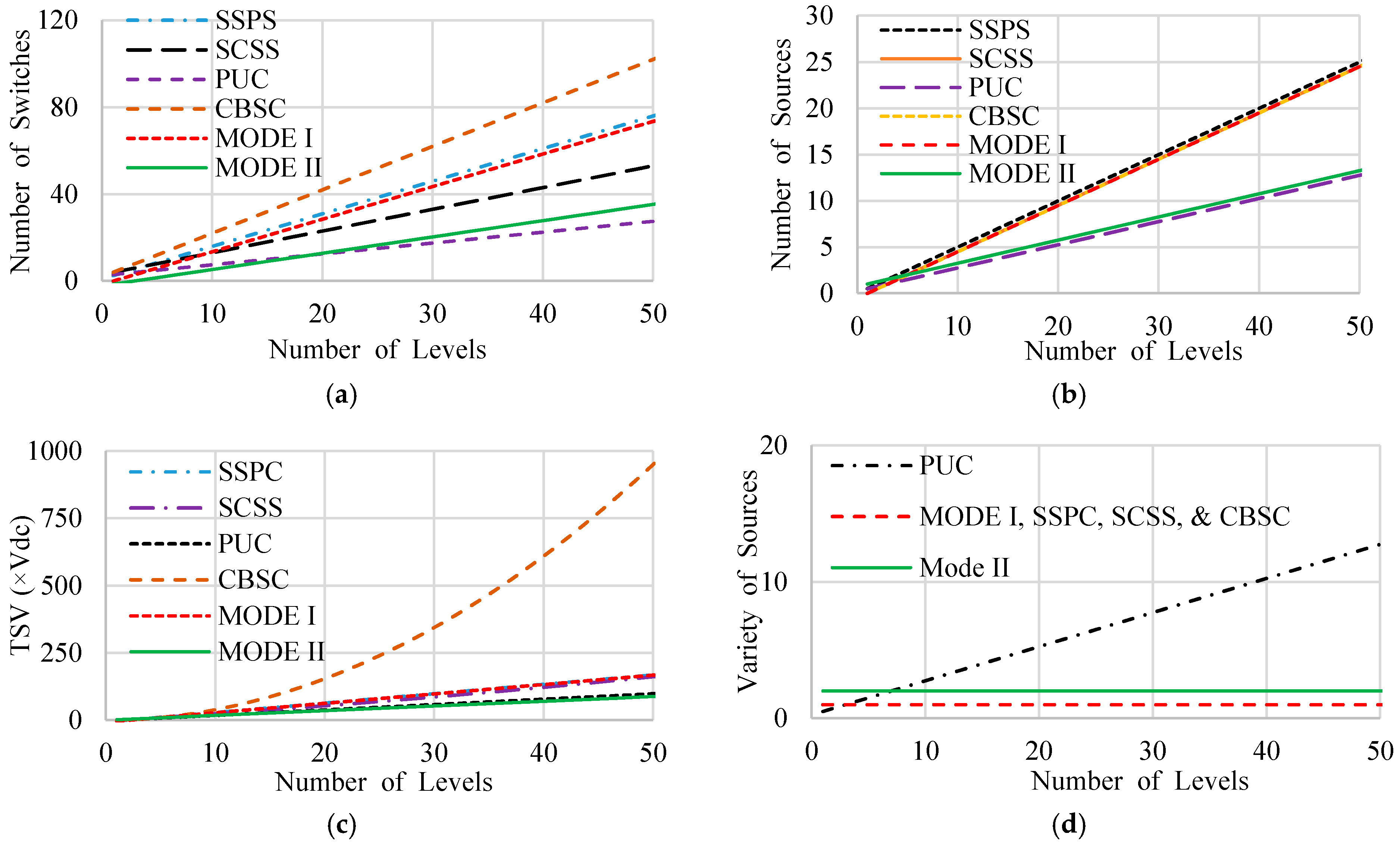

3. Comparative Study

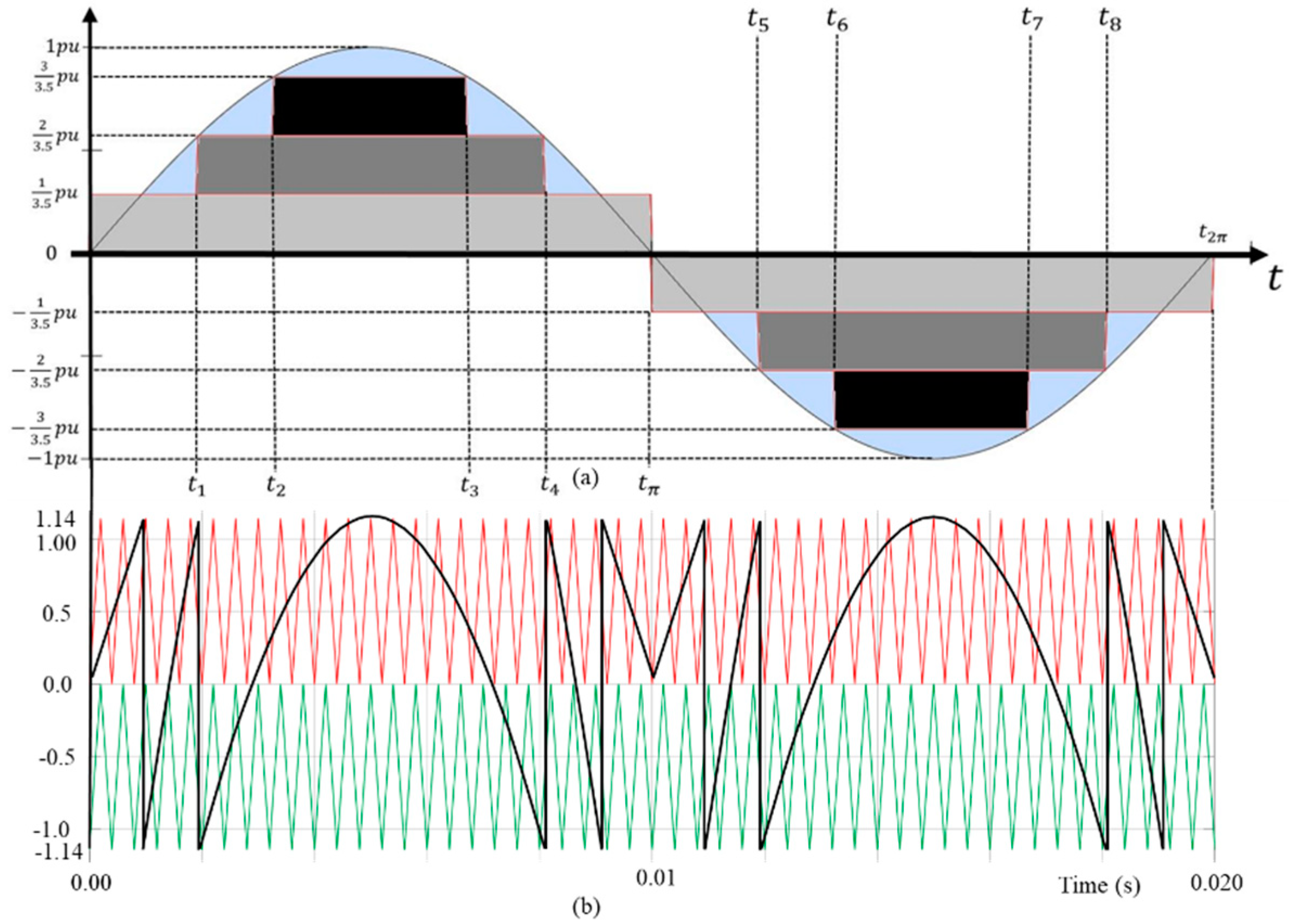

4. Modulation Technique

5. Results and Discussion

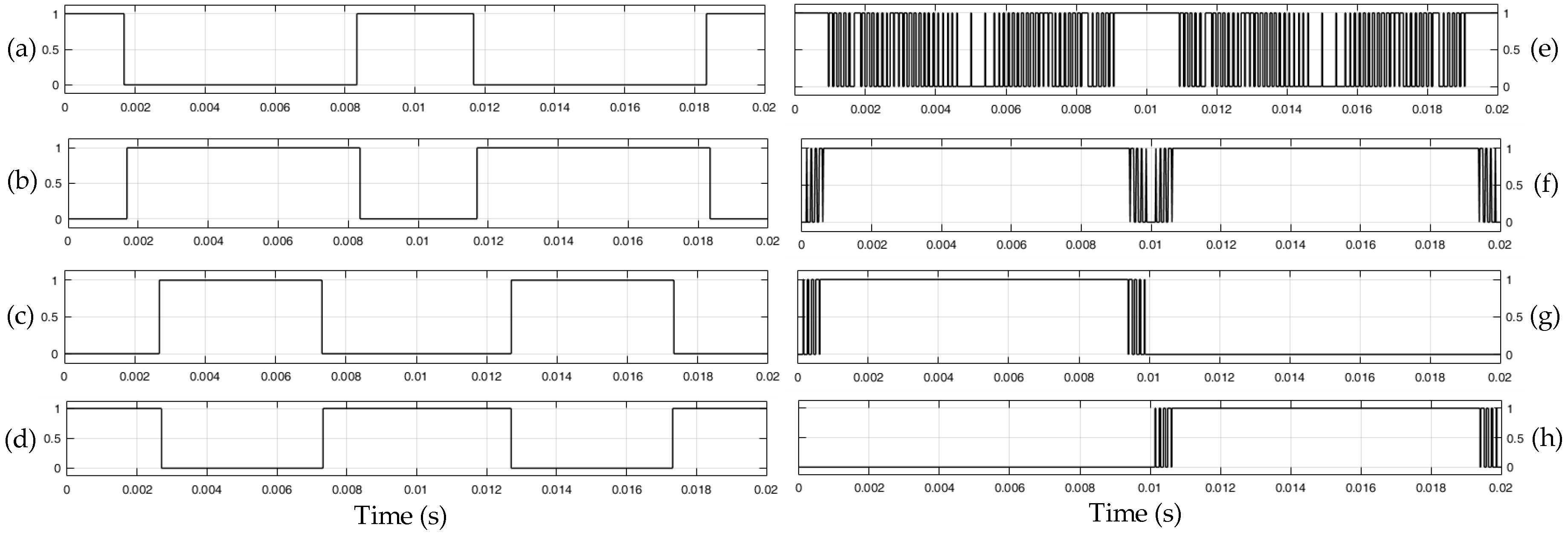

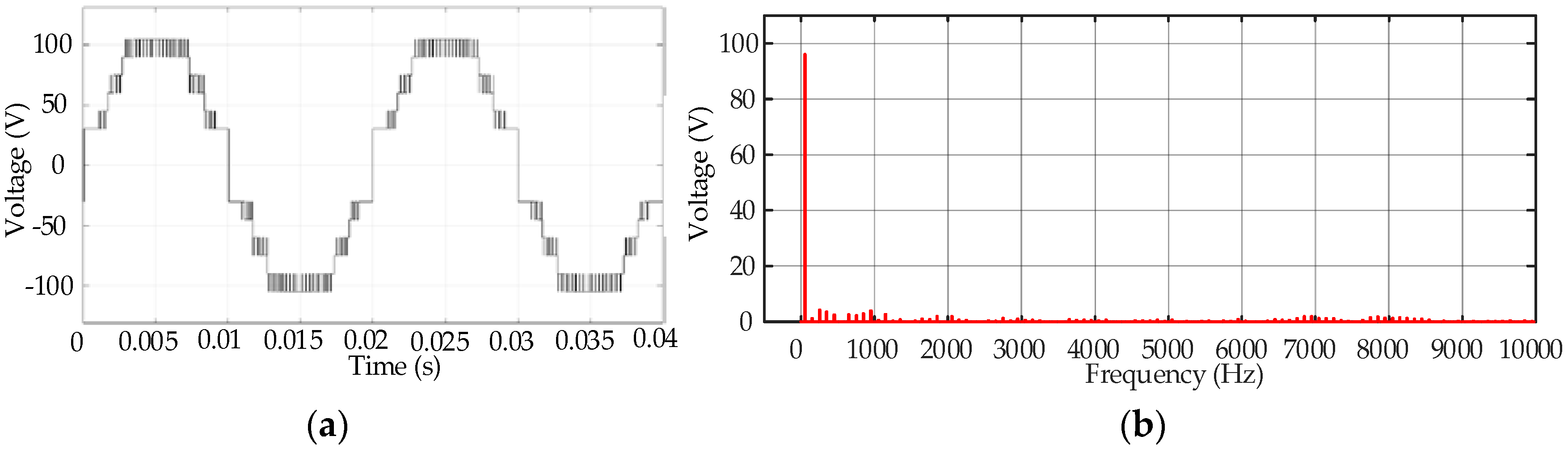

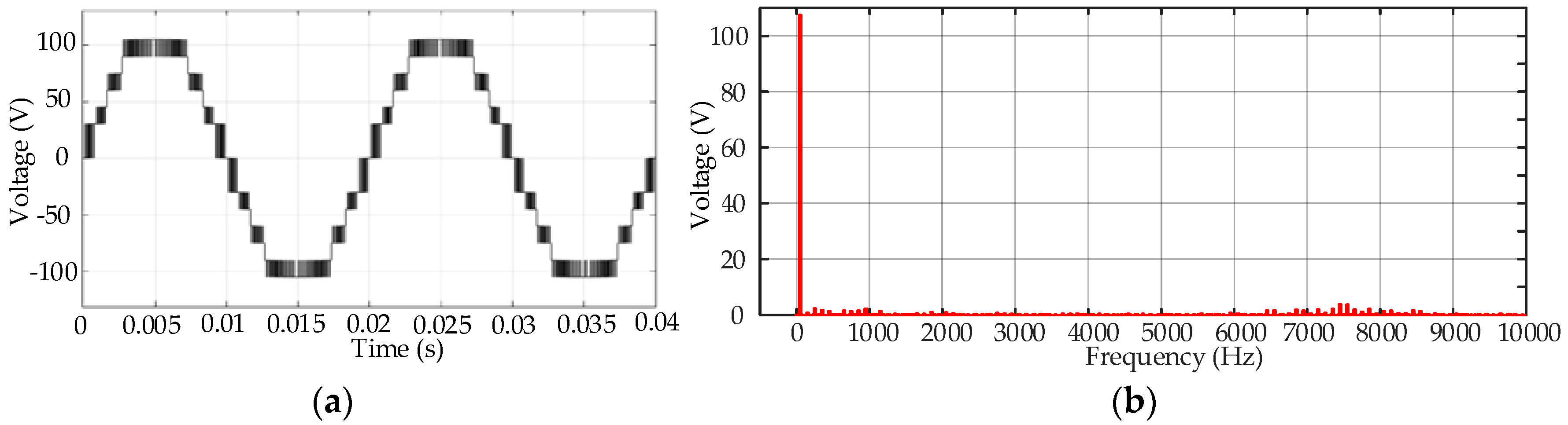

5.1. Simulation Results

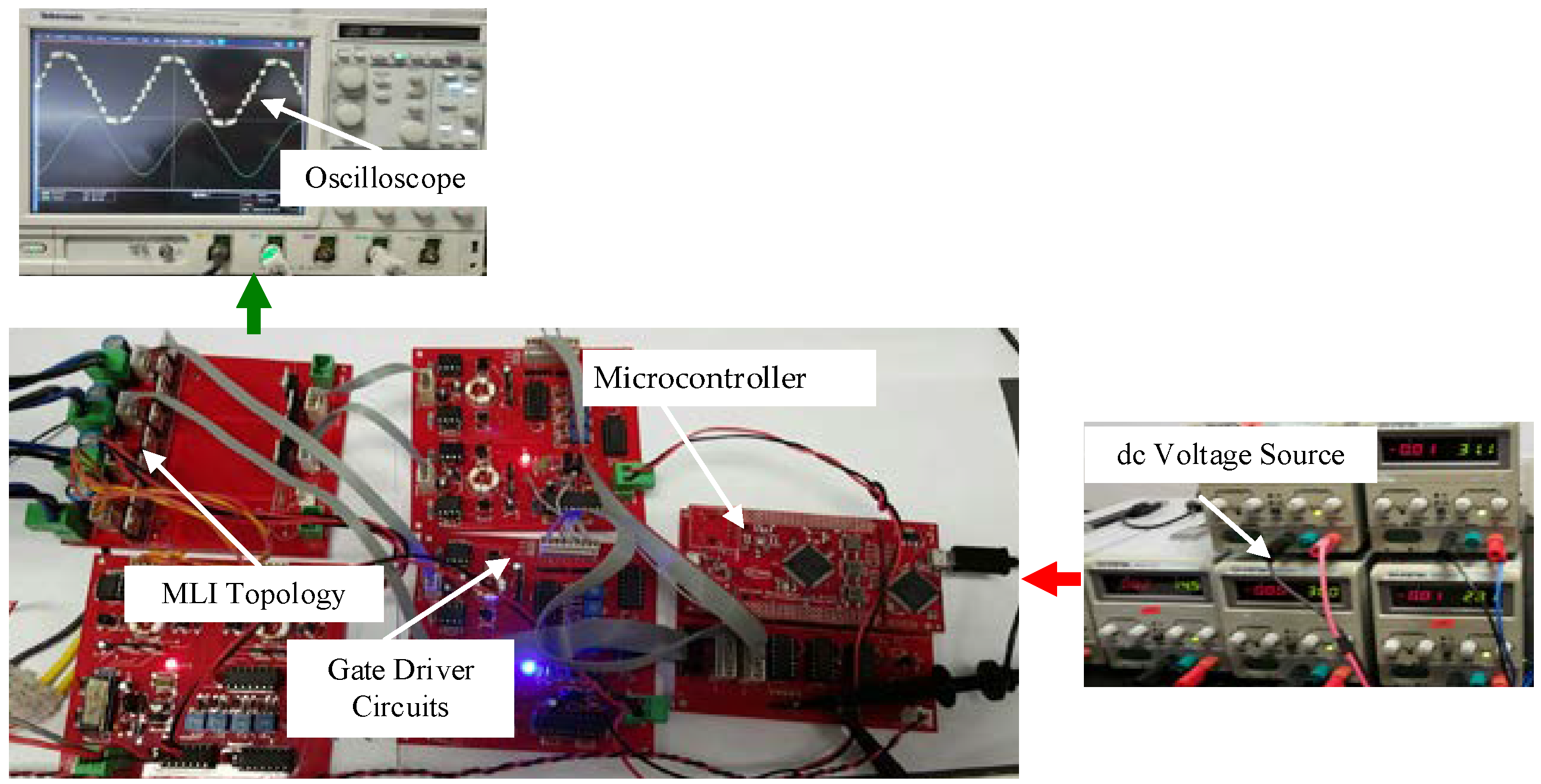

5.2. Experimental Verification

5.2.1. Experimental Setup

5.2.2. Experimental Results

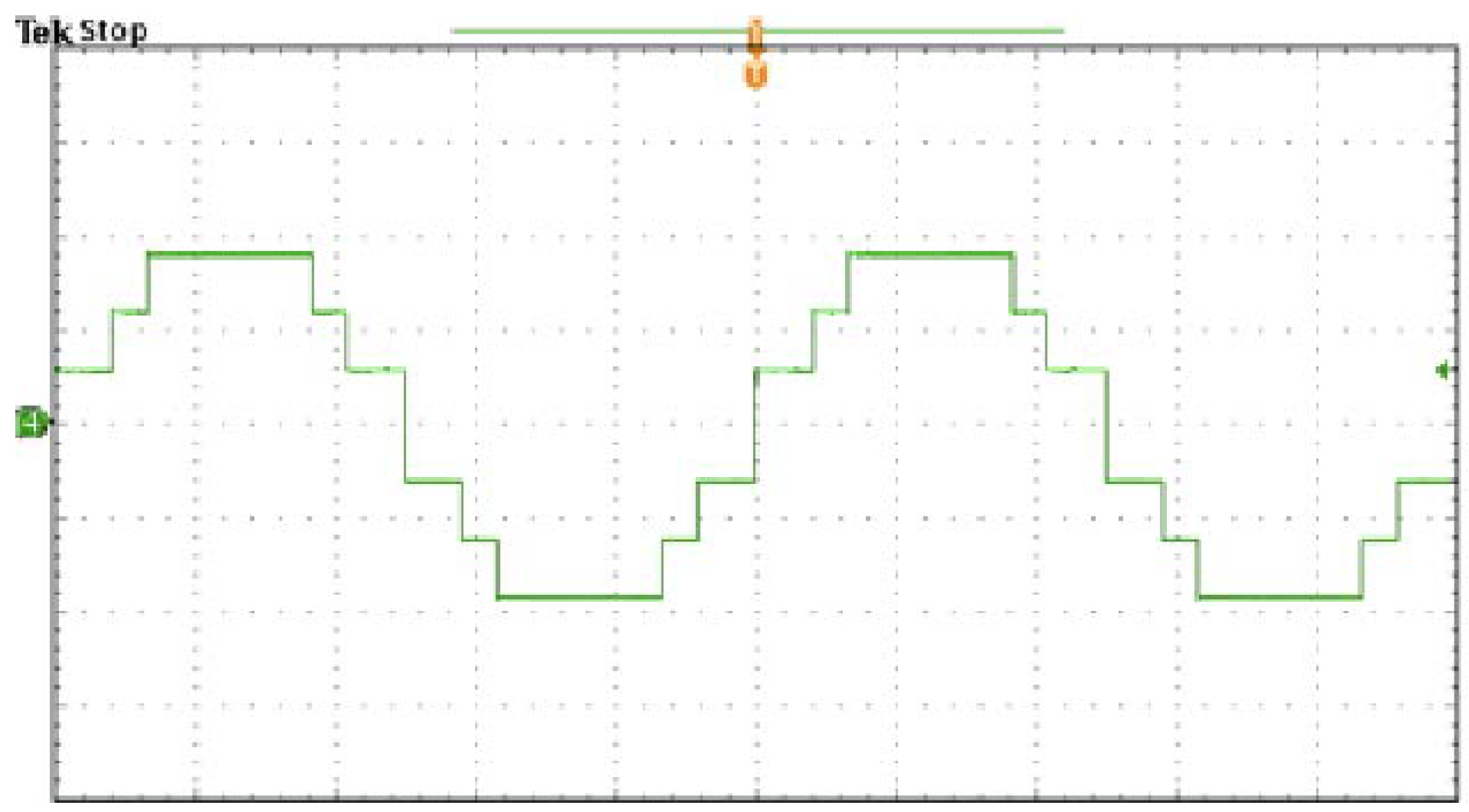

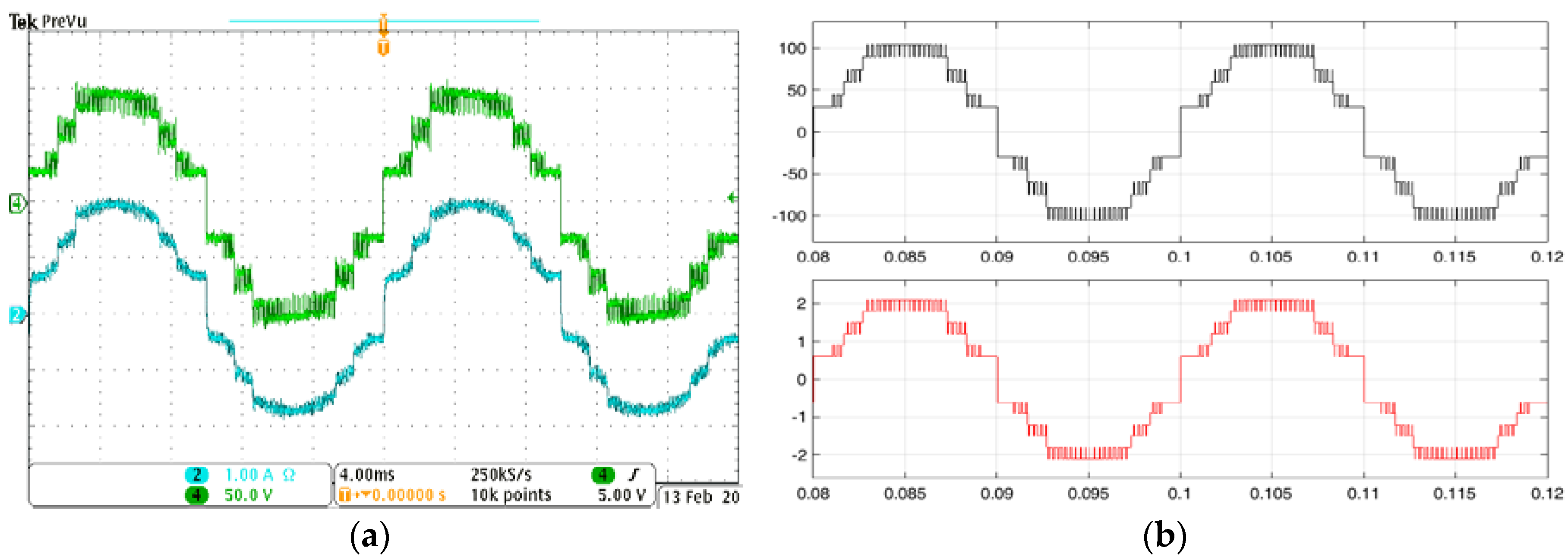

No Load Condition: Mode I and II

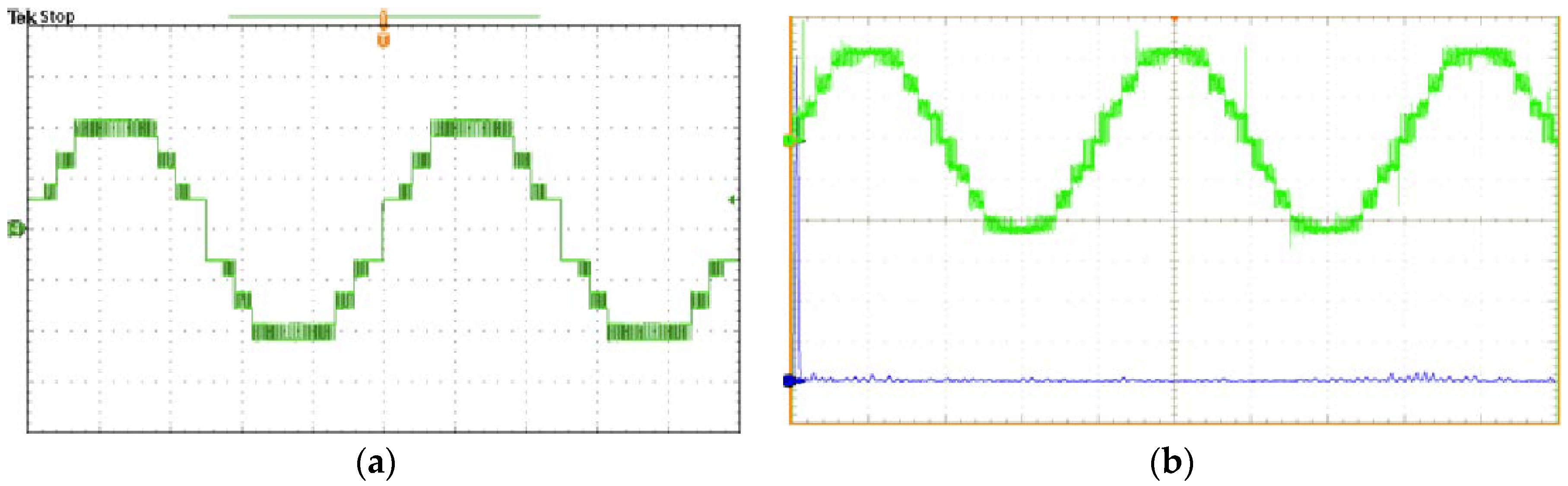

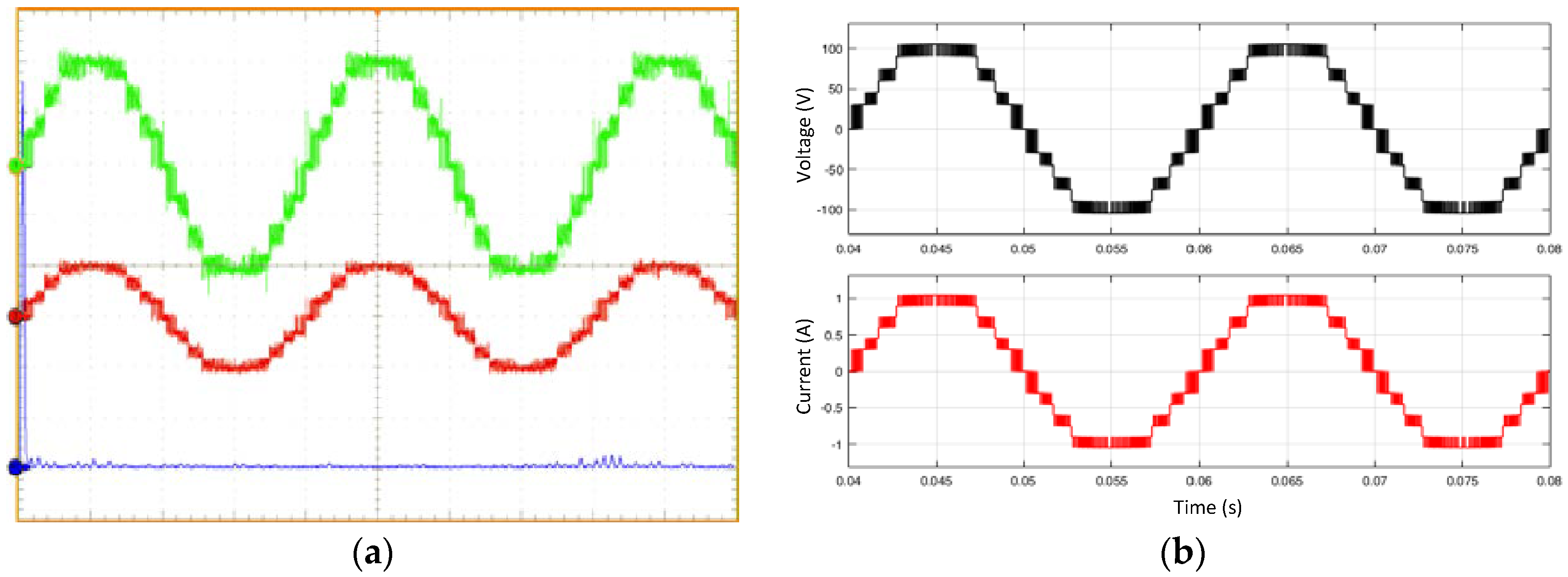

Mode II with Resistive Load

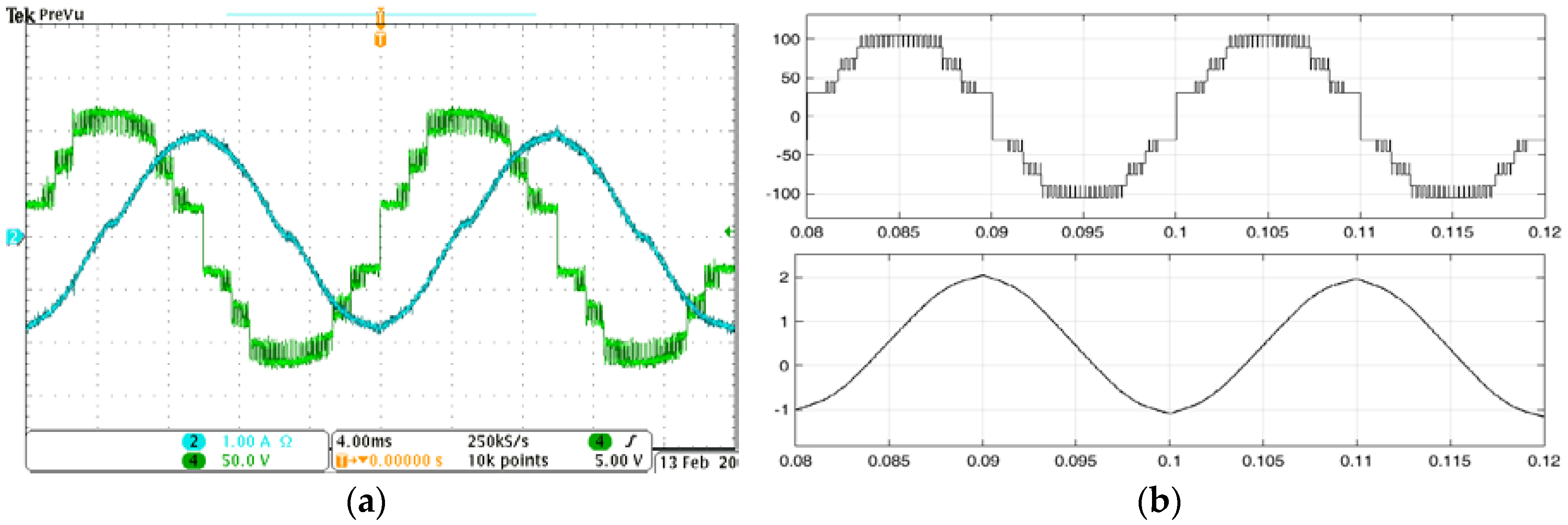

Mode II with Resistive-Inductive Load

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Vijeh, M.; Rezanejad, M.; Samadaei, E.; Bertilsson, K. A General Review of Multilevel Inverters Based on Main Submodules: Structural Point of View. IEEE Trans. Power Electron. 2019. [Google Scholar] [CrossRef]

- Aganah, K.; Luciano, C.; Ndoye, M.; Murphy, G.; Aganah, K.A.; Luciano, C.; Ndoye, M.; Murphy, G. New Switched-Dual-Source Multilevel Inverter for Symmetrical and Asymmetrical Operation. Energies 2018, 11, 984. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.W.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Akagi, H. Multilevel Converters: Fundamental Circuits and Systems. Proc. IEEE 2017, 105, 2048–2065. [Google Scholar] [CrossRef]

- Gupta, K.K.; Ranjan, A.; Bhatnagar, P.; Sahu, L.K.; Jain, S. Multilevel Inverter Topologies With Reduced Device Count: A Review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar] [CrossRef]

- Zhang, J.; Xu, S.; Din, Z.; Hu, X.; Zhang, J.; Xu, S.; Din, Z.; Hu, X. Hybrid Multilevel Converters: Topologies, Evolutions and Verifications. Energies 2019, 12, 615. [Google Scholar] [CrossRef]

- Hinago, Y.; Koizumi, H. A Single-Phase Multilevel Inverter Using Switched Series/Parallel DC Voltage Sources. IEEE Trans. Ind. Electron. 2010, 57, 2643–2650. [Google Scholar] [CrossRef]

- Lee, F.S.; Kang, S.H. A new structure of H-bridge multilevel inverter. In Proceedings of the KIPE Conference, Jeonnam, Korea, 30 June–3 July 2008; pp. 388–390. [Google Scholar]

- Su, G.-J. Multilevel DC-Link Inverter. IEEE Trans. Ind. Appl. 2005, 41, 848–854. [Google Scholar] [CrossRef]

- Choi, W.-K.; Kang, F. H-bridge based multilevel inverter using PWM switching function. In Proceedings of the INTELEC 2009—31st International Telecommunications Energy Conference, Incheon, Korea, 18–22 October 2009; pp. 1–5. [Google Scholar]

- Samsami, H.; Taheri, A.; Samanbakhsh, R. New bidirectional multilevel inverter topology with staircase cascading for symmetric and asymmetric structures. IET Power Electron. 2017, 10, 1315–1323. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Babaei, E.; Gharehpetian, G.B. A New Multilevel Converter Topology With Reduced Number of Power Electronic Components. IEEE Trans. Ind. Electron. 2012, 59, 655–667. [Google Scholar] [CrossRef]

- Babaei, E.; Laali, S.; Bayat, Z. A Single-Phase Cascaded Multilevel Inverter Based on a New Basic Unit With Reduced Number of Power Switches. IEEE Trans. Ind. Electron. 2015, 62, 922–929. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K. A new high power efficiency cascaded U cells multilevel converter. In Proceedings of the 2009 IEEE International Symposium on Industrial Electronics, Seoul, Korea, 5–8 July 2009; pp. 483–488. [Google Scholar]

- Ounejjar, Y.; Al-Haddad, K. A novel high energetic efficiency multilevel topology with reduced impact on supply network. In Proceedings of the 2008 34th Annual Conference of IEEE Industrial Electronics, Orlando, FL, USA, 10–13 November 2008; pp. 489–494. [Google Scholar]

- Babaei, E. A Cascade Multilevel Converter Topology With Reduced Number of Switches. IEEE Trans. Power Electron. 2008, 23, 2657–2664. [Google Scholar] [CrossRef]

- Samadaei, E.; Gholamian, S.A.; Sheikholeslami, A.; Adabi, J. An Envelope Type (E-Type) Module: Asymmetric Multilevel Inverters With Reduced Components. IEEE Trans. Ind. Electron. 2016, 63, 7148–7156. [Google Scholar] [CrossRef]

- Samadaei, E.; Sheikholeslami, A.; Gholamian, S.A.; Adabi, J. A Square T-Type (ST-Type) Module for Asymmetrical Multilevel Inverters. IEEE Trans. Power Electron. 2018, 33, 987–996. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Memon, M.A. Optimal Design of a New Cascaded Multilevel Inverter Topology with Reduced Switch Count. IEEE Access 2019, 7, 24498–24510. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M. A New General Multilevel Converter Topology Based on Cascaded Connection of Submultilevel Units with Reduced Switching Components, DC Sources, and Blocked Voltage by Switches. IEEE Trans. Ind. Electron. 2016, 63, 7157–7164. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M. Optimal Design of New Cascaded Switch-Ladder Multilevel Inverter Structure. IEEE Trans. Ind. Electron. 2017, 64, 2072–2080. [Google Scholar] [CrossRef]

- Shalchi Alishah, R.; Sabahi, M.; Nazarpour, D.; Hosseini, S.H. Novel multilevel inverter topologies for medium and high-voltage applications with lower values of blocked voltage by switches. IET Power Electron. 2014, 7, 3062–3071. [Google Scholar] [CrossRef]

- Shueai Alnamer, S.; Mekhilef, S.; Bin Mokhlis, H.; Shueai Alnamer, S.; Mekhilef, S.; Bin Mokhlis, H. A Four-Level T-Type Neutral Point Piloted Inverter for Solar Energy Applications. Energies 2018, 11, 1546. [Google Scholar] [CrossRef]

- Prabaharan, N.; Arun, V.; Sanjeevikumar, P.; Mihet-Popa, L.; Blaabjerg, F.; Prabaharan, N.; Arun, V.; Sanjeevikumar, P.; Mihet-Popa, L.; Blaabjerg, F. Reconfiguration of a Multilevel Inverter with Trapezoidal Pulse Width Modulation. Energies 2018, 11, 2148. [Google Scholar] [CrossRef]

- Bassi, H.M. Floating source multilevel inverter uses hybrid double switching frequencies. In Proceedings of the 2017 52nd International Universities Power Engineering Conference (UPEC), Heraklion, Greece, 28–31 August 2017; pp. 1–5. [Google Scholar]

- Murai, Y.; Watanabe, T.; Iwasaki, H. Waveform Distortion and Correction Circuit for PWM Inverters with Switching Lag-Times. IEEE Trans. Ind. Appl. 1987, IA-23, 881–886. [Google Scholar] [CrossRef]

| S1/S3 | S2 | S4/S6 | S5 | Sa1 | Sa2 | H1 | H2 | H3 | H4 | Vo |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | Vdc |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | Vdc + Va |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 2Vdc |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 2Vdc + Va |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 3Vdc |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 3Vdc + Va |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | −Vdc |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | −(Vdc + Va) |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | −2Vdc |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | −(2Vdc + Va) |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | −3Vdc |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | −(3Vdc + Va) |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bassi, H.M.; Salam, Z. A New Hybrid Multilevel Inverter Topology with Reduced Switch Count and dc Voltage Sources. Energies 2019, 12, 977. https://doi.org/10.3390/en12060977

Bassi HM, Salam Z. A New Hybrid Multilevel Inverter Topology with Reduced Switch Count and dc Voltage Sources. Energies. 2019; 12(6):977. https://doi.org/10.3390/en12060977

Chicago/Turabian StyleBassi, Hussain Mohammad, and Zainal Salam. 2019. "A New Hybrid Multilevel Inverter Topology with Reduced Switch Count and dc Voltage Sources" Energies 12, no. 6: 977. https://doi.org/10.3390/en12060977

APA StyleBassi, H. M., & Salam, Z. (2019). A New Hybrid Multilevel Inverter Topology with Reduced Switch Count and dc Voltage Sources. Energies, 12(6), 977. https://doi.org/10.3390/en12060977