Experimental Investigation on the Performances of a Multilevel Inverter Using a Field Programmable Gate Array-Based Control System

Abstract

1. Introduction

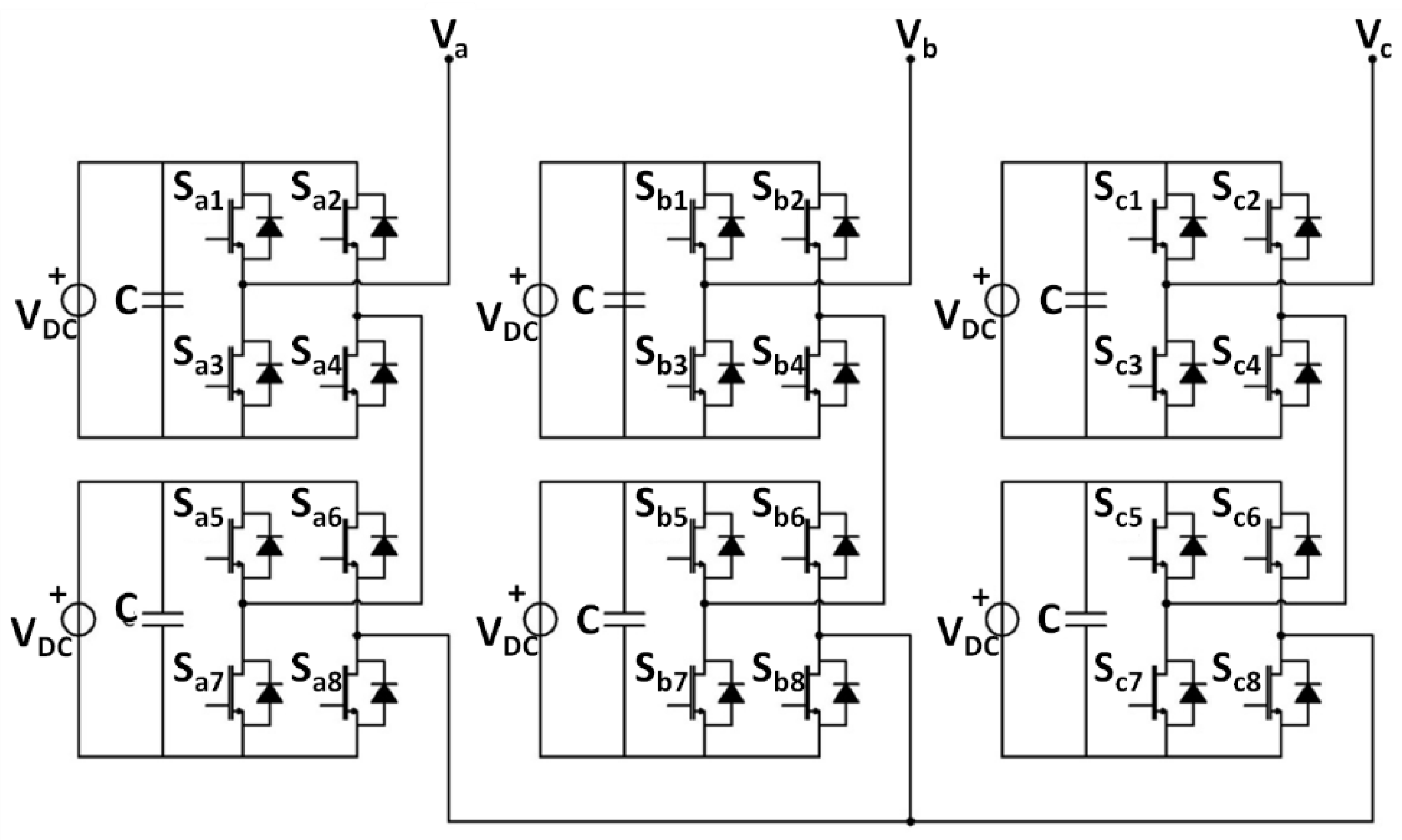

2. Cascaded H-Bridge Multilevel Inverter

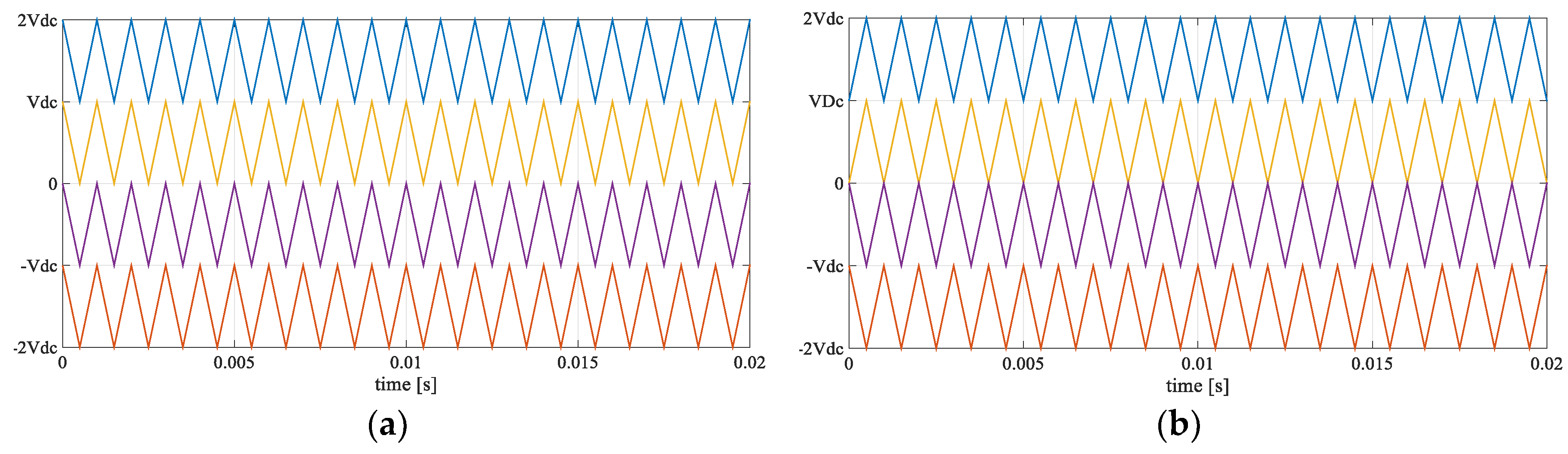

3. Overview of Multicarrier Modulation Techniques

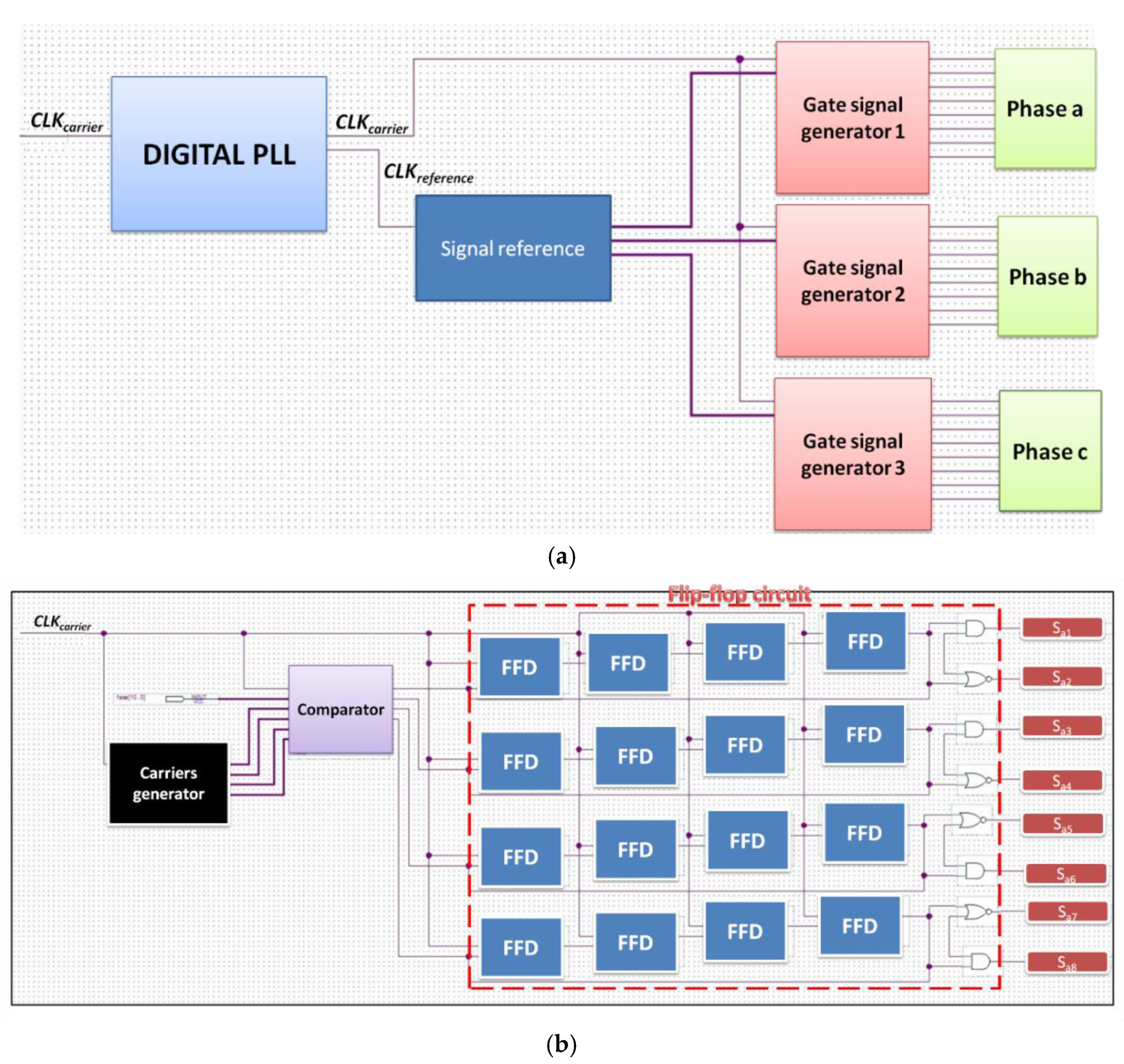

4. FPGA Design of the Control Software

4.1. Features of the Control Software

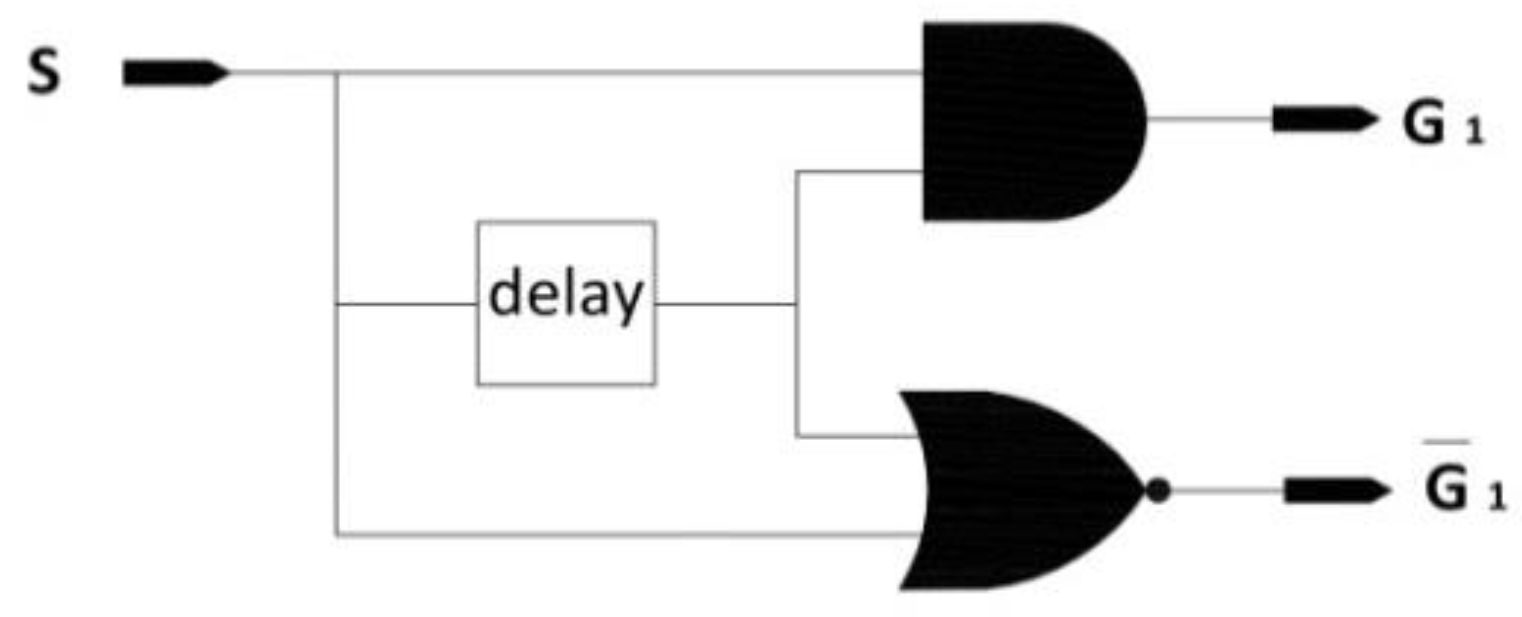

4.2. Digital System Design

4.3. FPGA and Software Environment

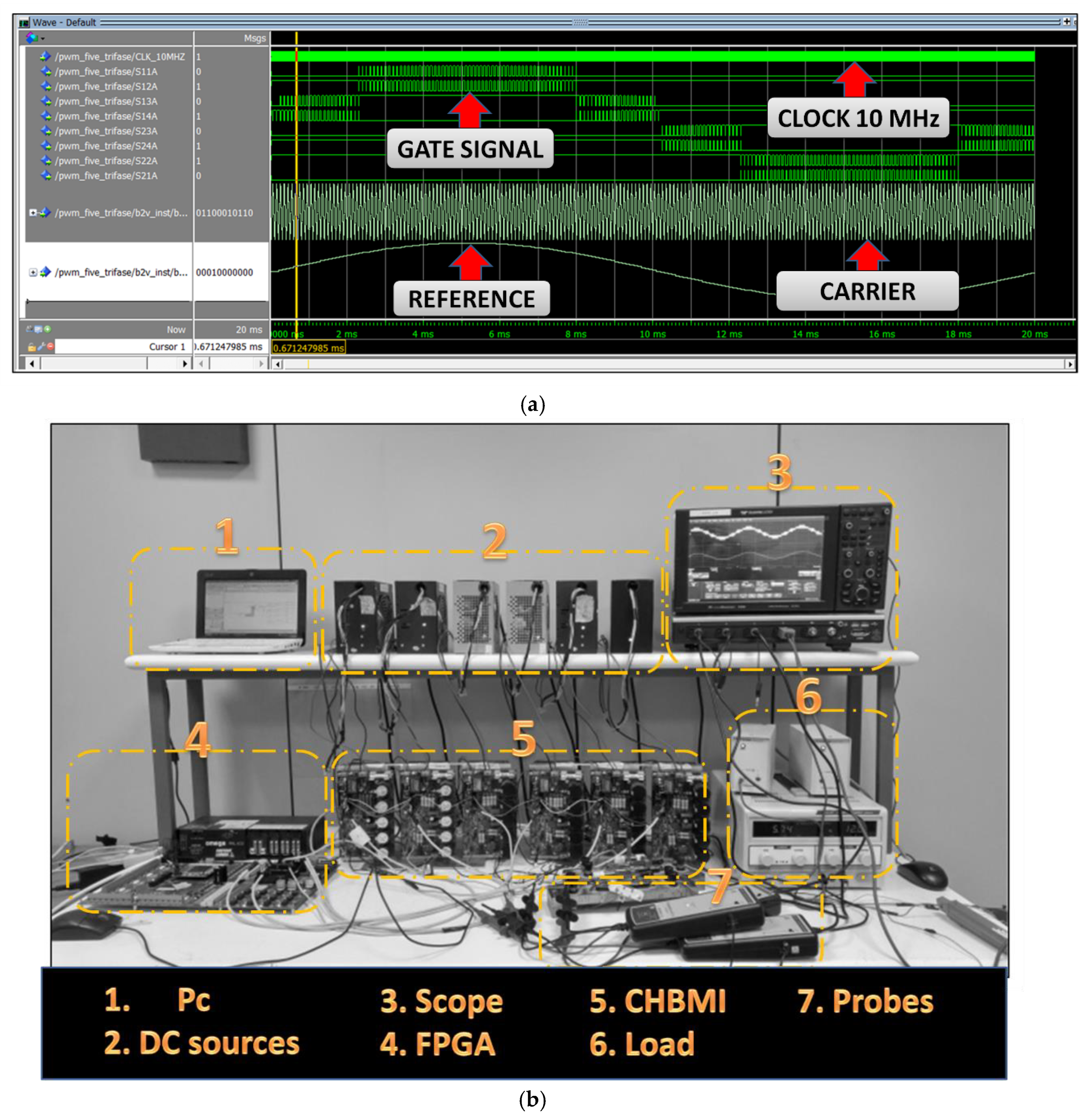

4.4. Gate Level Simulation

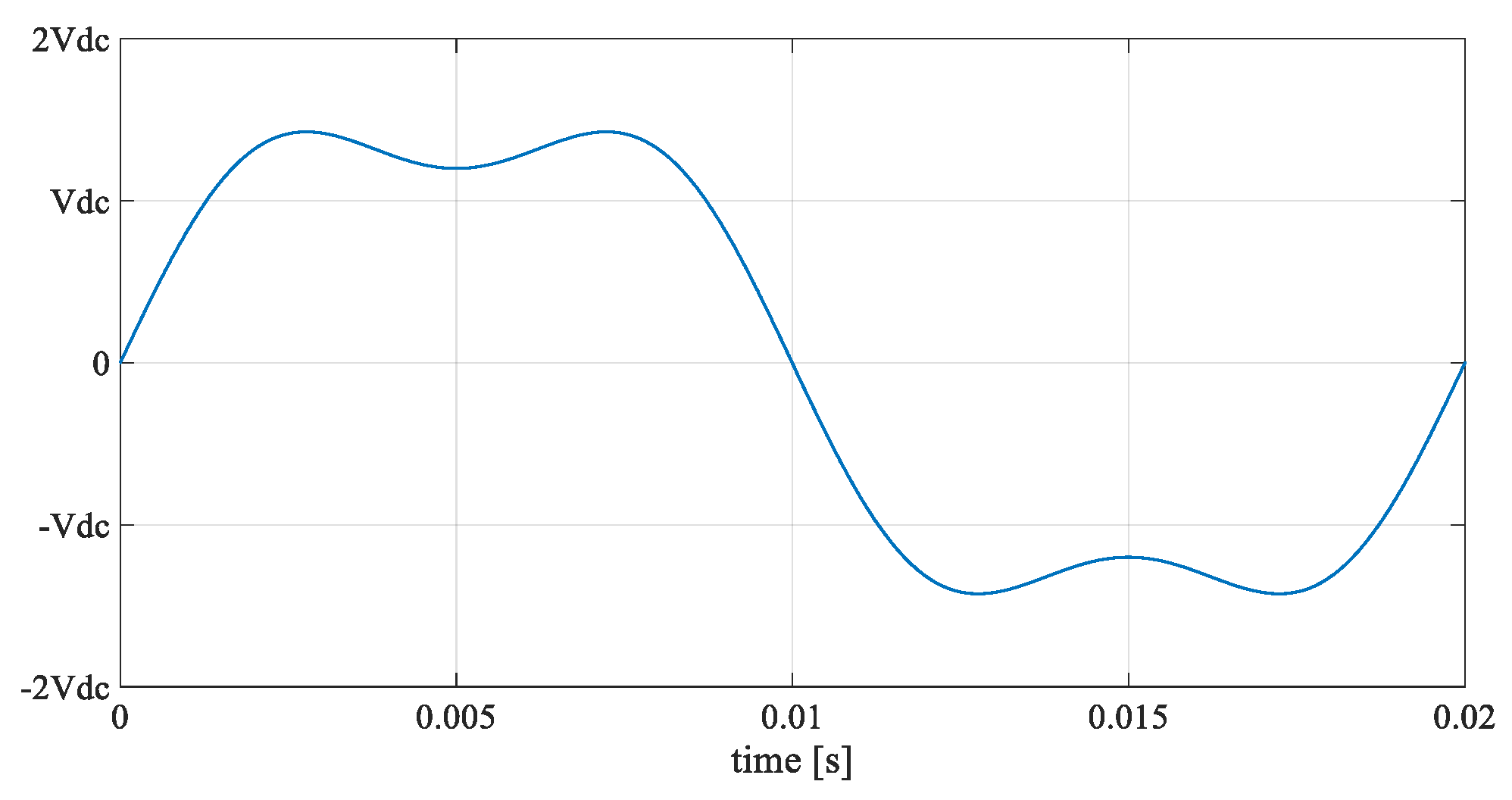

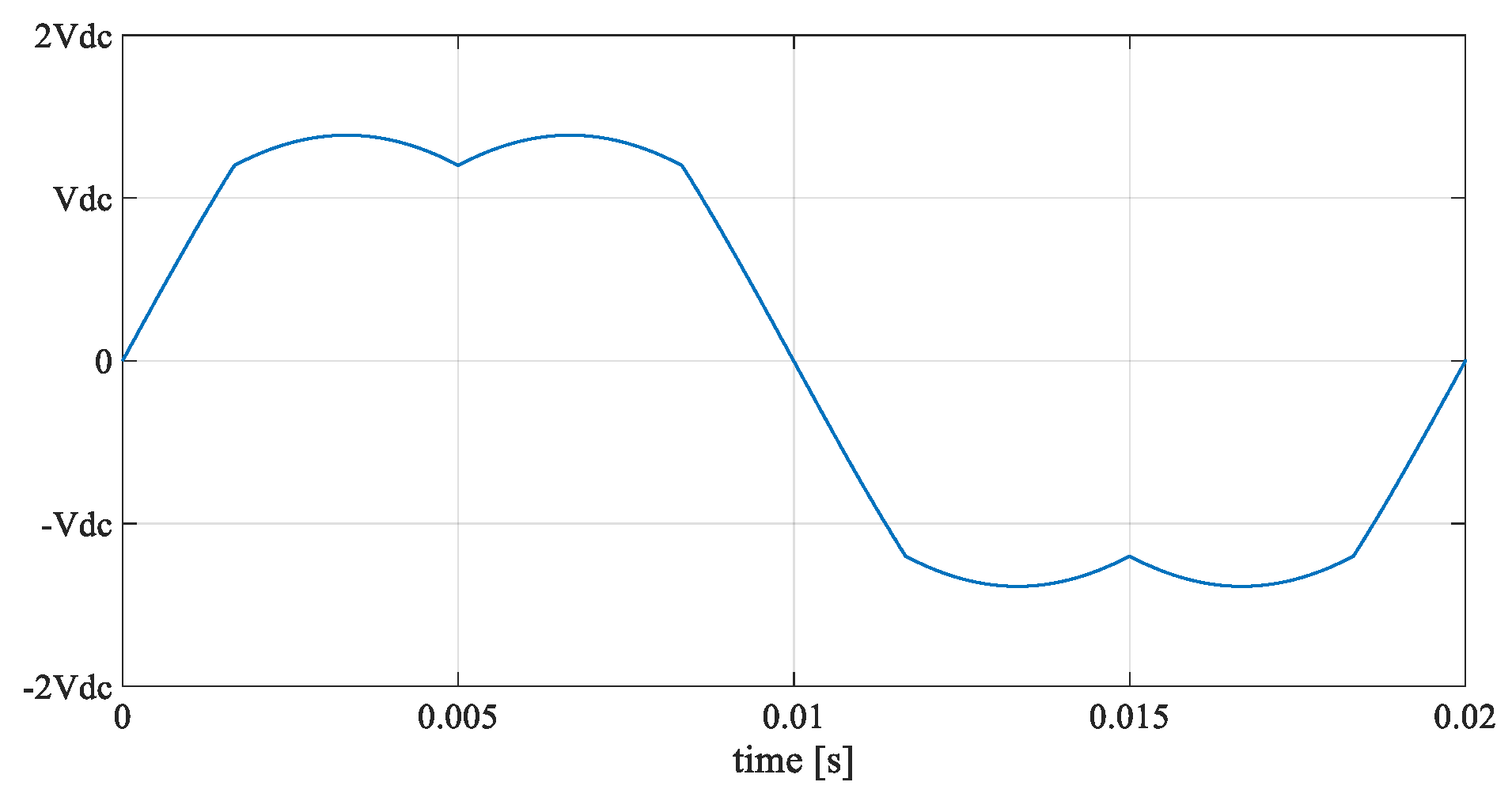

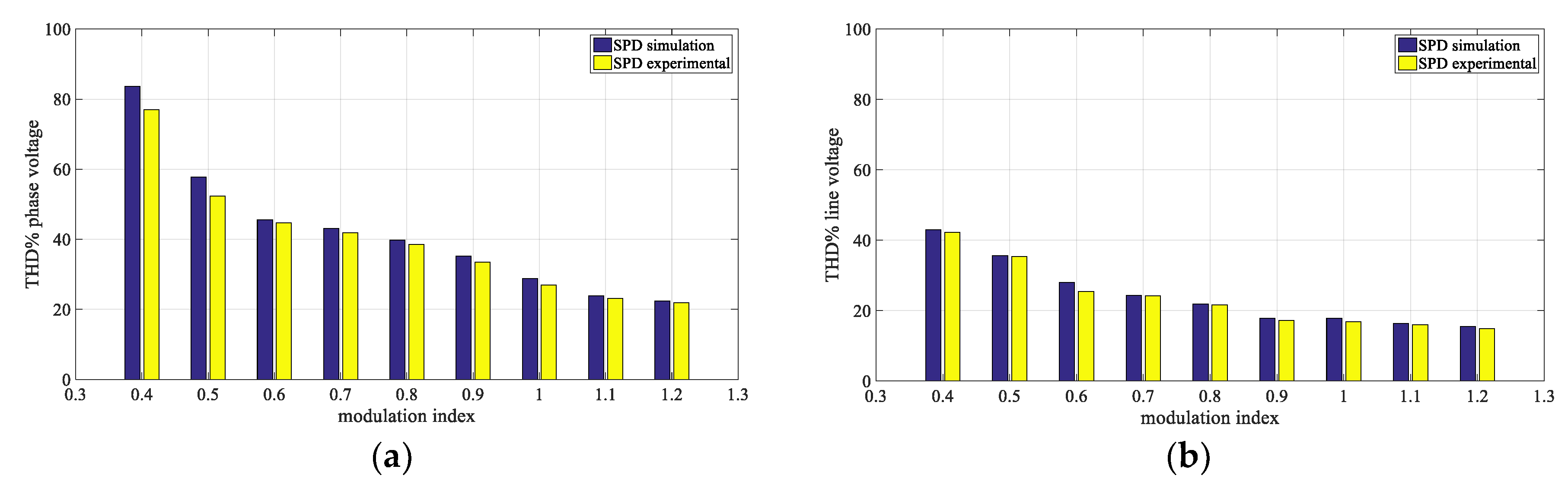

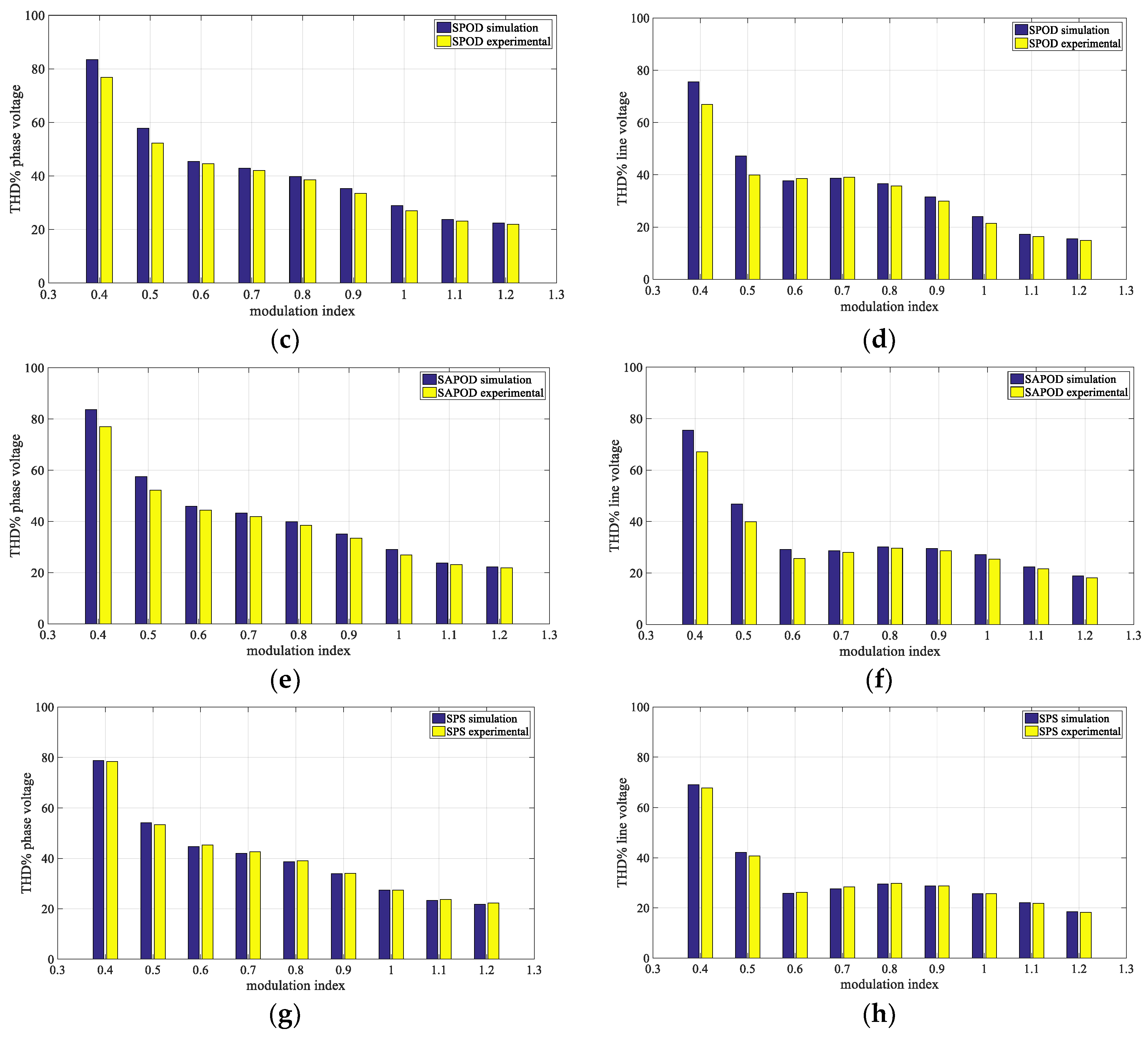

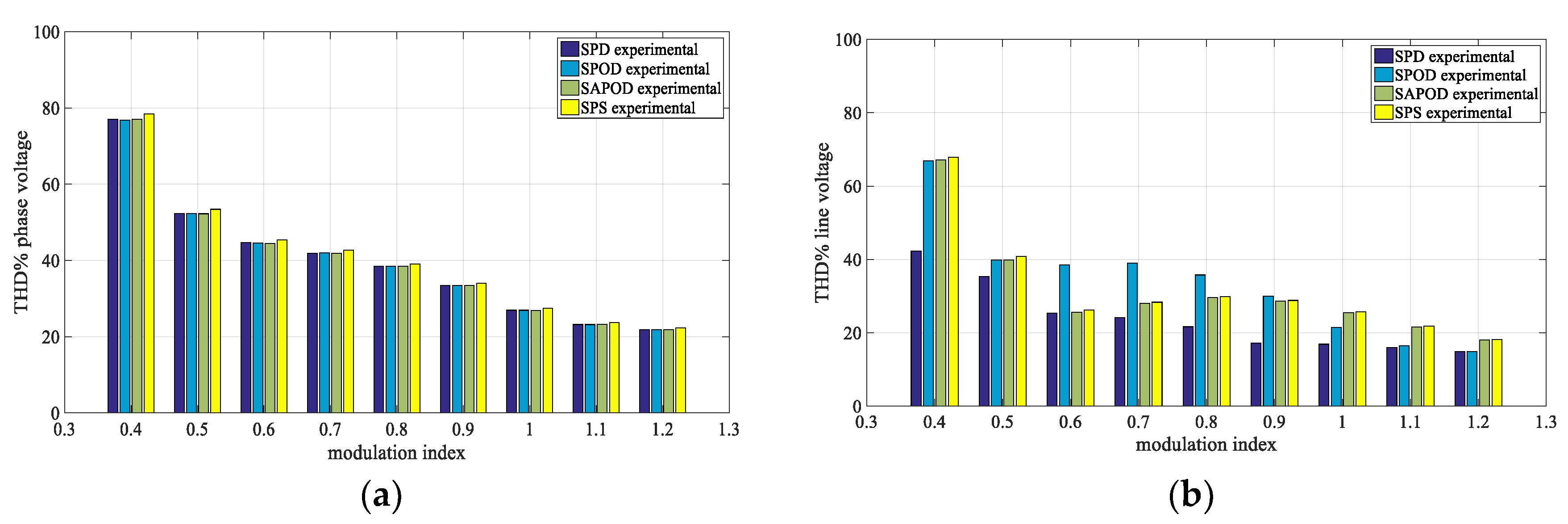

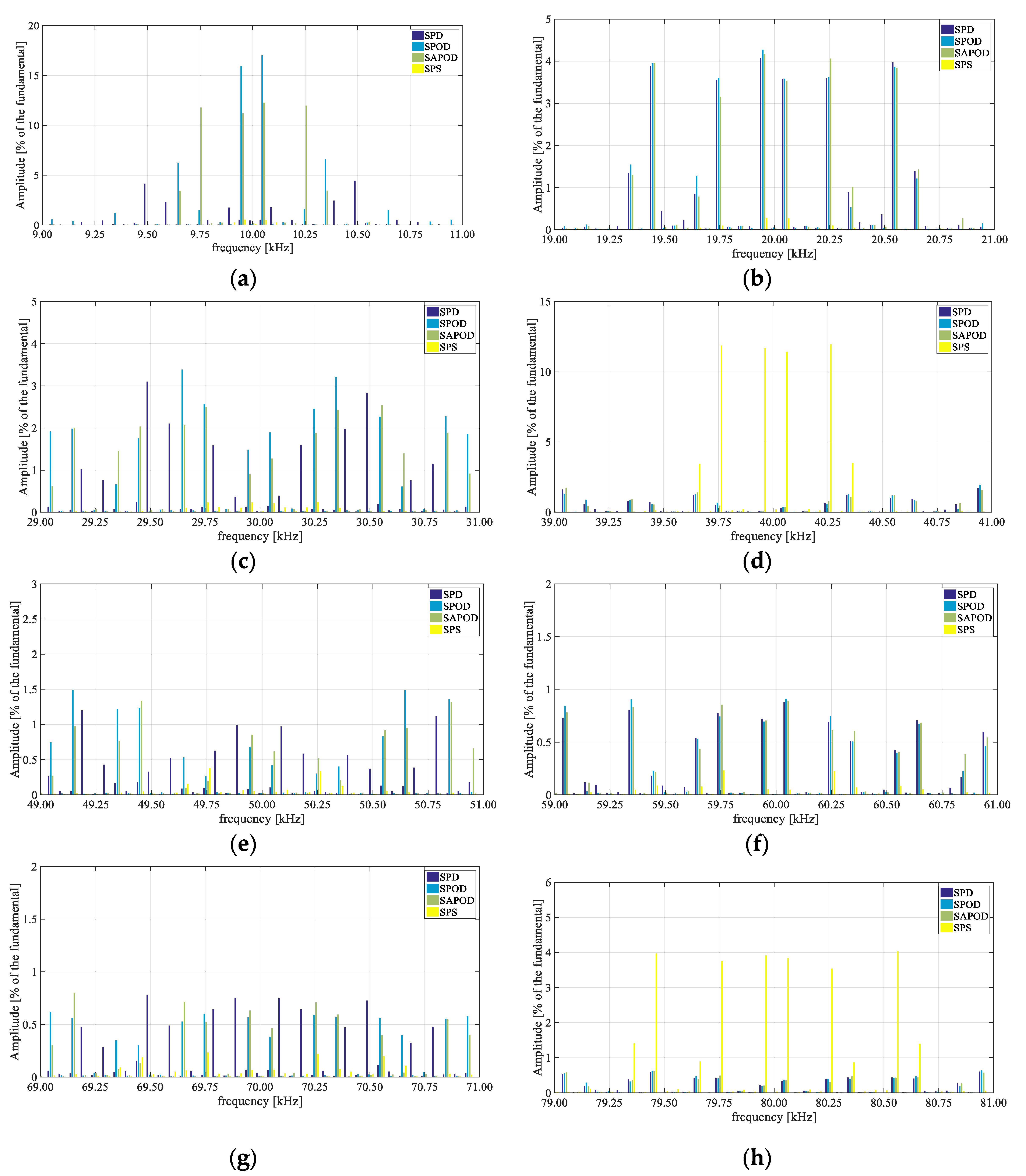

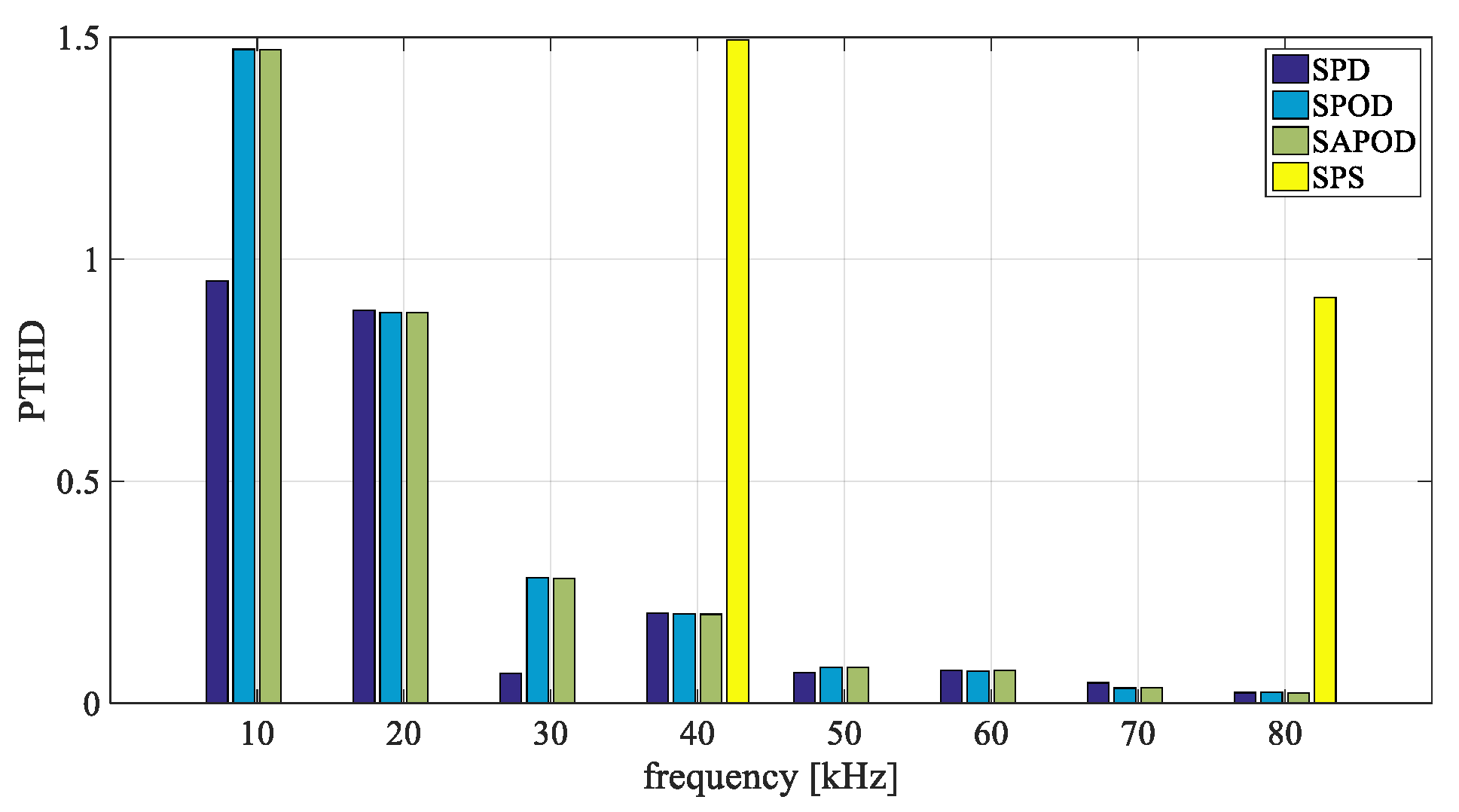

5. Comparison between Simulation and Experimental Results

- A prototype of FPGA-based control board (Cyclone III–ALTERA®, DigiPowers.r.l);

- Six power MOSFET-based H-bridge prototypes (model IRFB4115PbF, DigiPowers.r.l, city, country), whose technical features are summarized in Table 1;

- A LeCroy WaveRunner 6Zi scope (Teledyne, city, state abbrev if USA, country) used for the real-time monitoring and acquisition of the related waveforms;

- Six DC sources with 12 V of rated voltage;

- A balanced RL three-phase electric load.

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Buccella, C.; Cecati, C.; Latafat, H. Digital Control of Power Converters—A Survey. IEEE Trans. Ind. Inform. 2012, 8, 437–447. [Google Scholar] [CrossRef]

- Monmasson, E.; Cirstea, M.N. FPGA Design Methodology for Industrial Control Systems—A Review. IEEE Trans. Ind. Electron. 2007, 54, 1824–1842. [Google Scholar] [CrossRef]

- Monmasson, E.; Idkhajine, L.; Cirstea, M.N.; Bahri, I.; Tisan, A.; Naouar, M.W. FPGAs in Industrial Control Applications. IEEE Trans. Ind. Inform. 2011, 7, 224–243. [Google Scholar] [CrossRef]

- Rodríguez-Andina, J.J.; Valdés-Peña, M.D.; Moure, M.J. Advanced Features and Industrial Applications of FPGAs—A Review. IEEE Trans. Ind. Inform. 2015, 11, 853–864. [Google Scholar] [CrossRef]

- Sulaiman, N.; Obaid, Z.A.; Marhaban, M.H.; Hamidon, M.N. Design and implementation of FPGA-based systems—A review. Aust. J. Basic Appl. Sci. 2009, 3, 3575–3596. [Google Scholar]

- Kung, Y.; Fung, R.; Tai, T. Realization of a Motion Control IC for X-Y Table Based on Novel FPGA Technology. IEEE Trans. Ind. Electron. 2009, 56, 43–53. [Google Scholar] [CrossRef]

- Patel, J.; Sood, V.K. Review of Digital Controllers in Power Converters. In Proceedings of the 2018 IEEE Electrical Power and Energy Conference (EPEC), Toronto, ON, Canada, 10–11 October 2018; pp. 1–8. [Google Scholar] [CrossRef]

- Islam, M.R.; Guo, Y.; Zhu, J. FPGA-based control of modular multilevel converters: Modeling and experimental evaluation. In Proceedings of the 2015 International Conference on Electrical & Electronic Engineering (ICEEE), Rajshahi, Bangladesh, 4–6 November 2015; pp. 89–92. [Google Scholar] [CrossRef]

- Zhou, Z.; Wang, Q.; Lin, R. Real-time Simulation Realization of Modular Multilevel Converter Based on FPGA. In Proceedings of the 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Shenzhen, China, 4–7 November 2018; pp. 1–6. [Google Scholar]

- Atoui, E.B.; Mesbah, T.; Atoui, H. FPGA Implementation of Multi-carriers PWM Technique for Modular Multi-level Inverter. In Proceedings of the 2018 International Conference on Applied Smart Systems (ICASS), Medea, Algeria, 24–25 November 2018; pp. 1–6. [Google Scholar]

- Reddy, B.P.; Keerthipati, S. Torque Ripple Minimization of PPMIM Drives with Phase-Shifted Carrier PWM. In Proceedings of the IECON 2018—44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018; pp. 725–730. [Google Scholar]

- Sumam, M.J.; Shiny, G. Rapid Prototyping of High Performance FPGA Controller for an Induction Motor Drive. In Proceedings of the 2018 8th International Conference on Power and Energy Systems (ICPES), Colombo, Sri Lanka, 21–22 December 2018; pp. 76–80. [Google Scholar]

- Aime, M.; Gateau, G.; Meynard, T. Implementation of a peak current control algorithm within a field programmable gate array. IEEE Trans. Ind. Electron. 2007, 54, 406–418. [Google Scholar] [CrossRef]

- Gateau, G.; Lienhardt, A.M.; Meynard, T. Digital sliding mode observer implementation using FPGA. IEEE Trans. Ind. Electron. 2007, 54, 1865–1875. [Google Scholar]

- Coppola, M.; Napoli, F.D.; Guerriero, P.; Iannuzzi, D.; Daliento, S.; Pizzo, A.D. An FPGA-based advanced control strategy of a grid-tied PV CHB inverter. IEEE Trans. Power Electron. 2016, 31, 806–816. [Google Scholar] [CrossRef]

- Moranchel, M.; Huerta, F.; Sanz, I.; Bueno, E.; Rodríguez, F.J. A Comparison of Modulation Techniques for Modular Multilevel Converters. Energies 2016, 9, 1091. [Google Scholar] [CrossRef]

- Prabaharan, N.; Arun, V.; Sanjeevikumar, P.; Mihet-Popa, L.; Blaabjerg, F. Reconfiguration of a Multilevel Inverter with Trapezoidal Pulse Width Modulation. Energies 2018, 11, 2148. [Google Scholar] [CrossRef]

- Jayaraman, M.; Vt, S. Power Quality Improvement in a Cascaded Multilevel Inverter Interfaced Grid Connected System Using a Modified Inductive–Capacitive–Inductive Filter with Reduced Power Loss and Improved Harmonic Attenuation. Energies 2017, 10, 1834. [Google Scholar] [CrossRef]

- Xue, F.; Ling, Z.; Yang, Y.; Miao, X. Design and Implementation of Novel Smart Battery Management System for FPGA Based Portable Electronic Devices. Energies 2017, 10, 264. [Google Scholar] [CrossRef]

- Ricco, M.; Mathe, L.; Monmasson, E.; Teodorescu, R. FPGA-Based Implementation of MMC Control Based on Sorting Networks. Energies 2018, 11, 2394. [Google Scholar] [CrossRef]

- Rodič, M.; Milanovič, M.; Truntič, M. Digital Control of an Interleaving Operated Buck-Boost Synchronous Converter Used in a Low-Cost Testing System for an Automotive Powertrain. Energies 2018, 11, 2290. [Google Scholar] [CrossRef]

- Zhang, B.; Wang, Y.; Tu, S.; Jin, Z. FPGA-Based Real-Time Digital Solver for Electro-Mechanical Transient Simulation. Energies 2018, 11, 2650. [Google Scholar] [CrossRef]

- Naouar, M.W.; Monmasson, E.; Naassani, A.A.; Slama-Belkhodja, I.; Patin, N. FPGA-Based Current Controllers for AC Machine Drives—A Review. IEEE Trans. Ind. Electron. 2007, 54, 1907–1925. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- De, S.; Banerjee, D.; Kumar, K.S.; Gopakumar, K.; Ramchand, R.; Patel, C. Multilevel inverters for low-power application. IET Power Electron. 2011, 4, 384–392. [Google Scholar] [CrossRef]

- Beig, A.R.; Dekka, A. Experimental verification of multilevel inverter-based standalone power supply for low-voltage and low-power applications. IET Power Electron. 2012, 5, 635–643. [Google Scholar] [CrossRef]

- Behrouzian, E.; Bongiorno, M.; de la Parra, H.Z. An overview of multilevel topologies for grid connected applications. In Proceedings of the 2013 15th European Conference on Power Electronics Applications (EPE), Lille, France, 2–6 September 2013. [Google Scholar]

- Rashid, M.H. Power Electronics Handbook, Devices, Circuits and Applications, 3rd ed.; Buttherworth-Heirnann: Oxford, UK, 2011. [Google Scholar]

- Gupta, K.K.; Jain, S. Topology for multilevel inverters to attain maximum number of levels from given DC sources. IET Power Electron. 2012, 5, 435–446. [Google Scholar] [CrossRef]

- Jamaludin, J.; Rahim, N.A.; Ping, H.W. Multilevel voltage source inverter with optimised usage of bidirectional switches. IET Power Electron. 2015, 8, 378–390. [Google Scholar] [CrossRef]

- Gautam, S.P.; Kumar, L.; Gupta, S. Hybrid topology of symmetrical multilevel inverter using less number of devices. IET Power Electron. 2015, 8, 2125–2135. [Google Scholar] [CrossRef]

- ShalchiAlishah, R.; Nazarpour, D.; Hosseini, S.H.; Sabahi, M. Novel multilevel inverter topologies for medium and high-voltage applications with lower values of blocked voltage by switches. IET Power Electron. 2014, 7, 3062–3071. [Google Scholar] [CrossRef]

- Adam, G.P.; Anaya-Lara, O.; Burt, G.M.; Telford, D.; Williams, B.W.; Mcdonald, J.R. Modular multilevel inverter: Pulse width modulation and capacitor balancing technique. IET Power Electron. 2010, 3, 702–715. [Google Scholar] [CrossRef]

- Haji-Esmaeili, M.M.; Naseri, M.; Khoun-Jahan, H.; Abapour, M. Fault-tolerant structure for cascaded H-bridge multilevel inverter and reliability evaluation. IET Power Electron. 2017, 10, 59–70. [Google Scholar] [CrossRef]

- McGrath, B.P.; Holmes, D.G. Multicarrier PWM strategies for multilevel inverters. IEEE Trans. Ind. Electron. 2002, 49, 858–867. [Google Scholar] [CrossRef]

- Balamurugan, C.R.; Natarajan, S.P.; Bensraj, R.; Shanthi, B. A Review on Modulation Strategies of Mulilevel Inverter. Indones. J. Electr. Eng. Comput. Sci. 2016, 3, 681–705. [Google Scholar] [CrossRef]

- Schettino, G.; Buccella, C.; Caruso, M.; Cecati, C.; Castiglia, V.; Miceli, R.; Viola, F. Overview and experimental analysis of MC SPWM techniques for single-phase five level cascaded H-bridge FPGA controller-based. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 4529–4534. [Google Scholar] [CrossRef]

- Benanti, S.; Buccella, C.; Caruso, M.; Castiglia, V.; Cecati, C.; di Tommaso, A.O.; Miceli, R.; Romano, P.; Schettino, G.; Viola, F. Experimental analysis with FPGA controller-based of MC PWM techniques for three-phase five level cascaded H-bridge for PV applications. In Proceedings of the 2016 IEEE International Conference on Renewable Energy Research and Applications (ICRERA), Birmingham, UK, 20–23 November 2016; pp. 1173–1178. [Google Scholar] [CrossRef]

- Miceli, R.; Schettino, G.; Viola, F. A novel computational approach for harmonic mitigation in PV systems with single-phase five-level CHBMI. Energies 2018, 11, 2100. [Google Scholar] [CrossRef]

- Viola, F. Experimental evaluation of the performance of a three-phase five-level cascaded h-bridge inverter by means FPGA-based control board for grid connected applications. Energies 2018, 11, 3298. [Google Scholar] [CrossRef]

- Dordevic, O.; Jones, M.; Levi, E. Analytical Formulas for Phase Voltage RMS Squared and THD in PWM Multiphase Systems. IEEE Trans. Power Electron. 2015, 30, 1645–1656. [Google Scholar] [CrossRef]

- ALTERA, Cyclone III Device Handbook—Volume 1, 101 Innovation Drive San Jose, CA 95134. Available online: http://www.altera.com (accessed on 14 March 2019).

- International Rectifier. Data Sheet IRFB4115PbF. 2014. Available online: www.irf.com (accessed on 14 March 2019).

| Magnitude (unit) | Symbol | Value |

|---|---|---|

| Voltage (V) | Vdss | 150 |

| Resistance (mΩ) | Rds(on) | 9.3 |

| Current (A) | Id (siliconlimited) | 104 |

| Turn on delay (ns) | TD(ON) | 18 |

| Rise time (ns) | tR, rise time | 73 |

| Turn off delay (ns) | TD(OFF), | 41 |

| Fall time (ns) | tF | 39 |

| Reversal recovery (ns) | tRR | 86 |

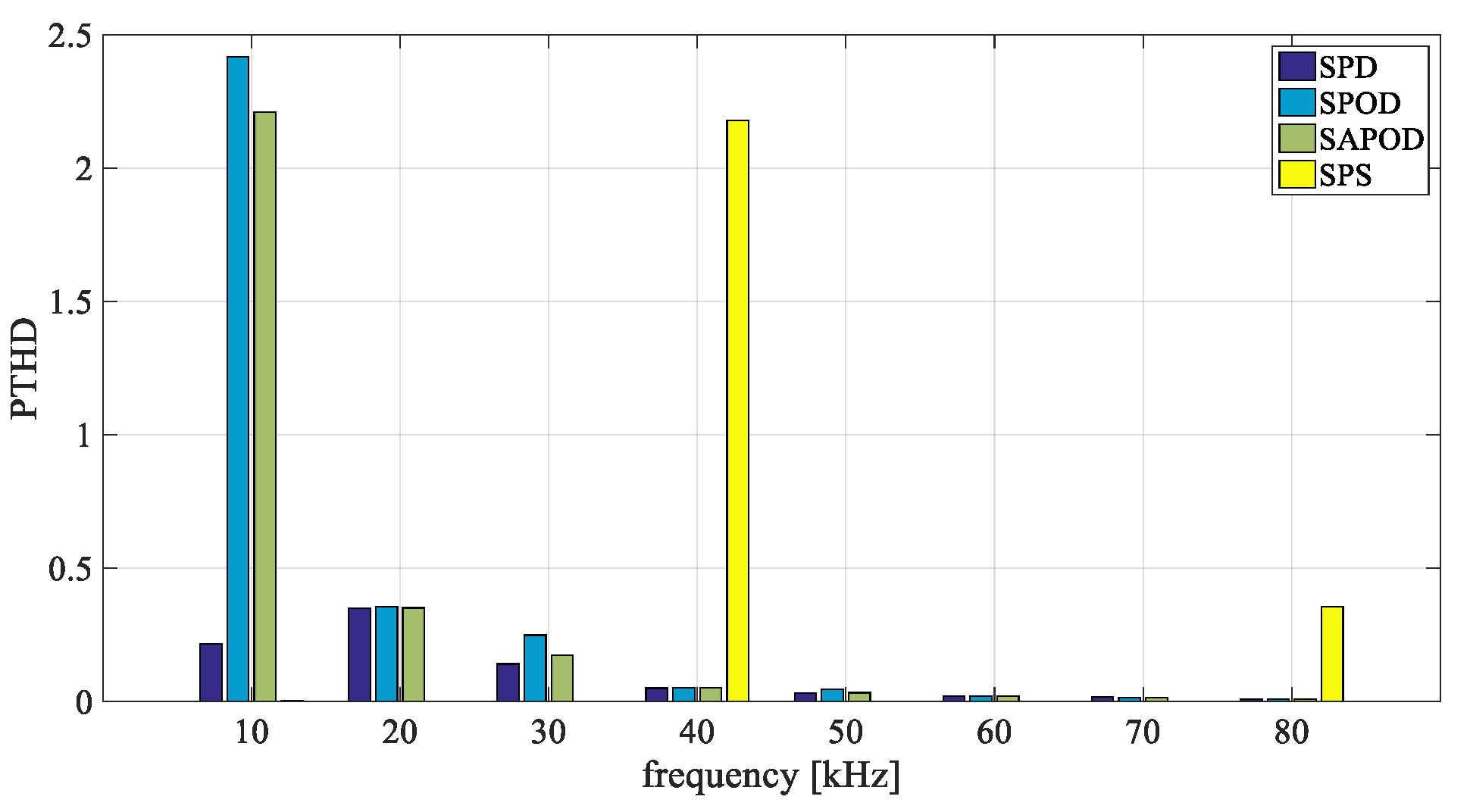

| Modulation Technique | THD% m = 0.5 | THD% m = 0.9 |

|---|---|---|

| SPD | 35.38% | 17.19% |

| SPOD | 39.88% | 29.95% |

| SAPOD | 39.87% | 28.64% |

| SPS | 40.77% | 28.83% |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ala, G.; Caruso, M.; Miceli, R.; Pellitteri, F.; Schettino, G.; Trapanese, M.; Viola, F. Experimental Investigation on the Performances of a Multilevel Inverter Using a Field Programmable Gate Array-Based Control System. Energies 2019, 12, 1016. https://doi.org/10.3390/en12061016

Ala G, Caruso M, Miceli R, Pellitteri F, Schettino G, Trapanese M, Viola F. Experimental Investigation on the Performances of a Multilevel Inverter Using a Field Programmable Gate Array-Based Control System. Energies. 2019; 12(6):1016. https://doi.org/10.3390/en12061016

Chicago/Turabian StyleAla, Guido, Massimo Caruso, Rosario Miceli, Filippo Pellitteri, Giuseppe Schettino, Marco Trapanese, and Fabio Viola. 2019. "Experimental Investigation on the Performances of a Multilevel Inverter Using a Field Programmable Gate Array-Based Control System" Energies 12, no. 6: 1016. https://doi.org/10.3390/en12061016

APA StyleAla, G., Caruso, M., Miceli, R., Pellitteri, F., Schettino, G., Trapanese, M., & Viola, F. (2019). Experimental Investigation on the Performances of a Multilevel Inverter Using a Field Programmable Gate Array-Based Control System. Energies, 12(6), 1016. https://doi.org/10.3390/en12061016