An MPC Reference Governor Approach for Enhancing the Performance of Precompensated Boost DC–DC Converters

Abstract

:1. Introduction

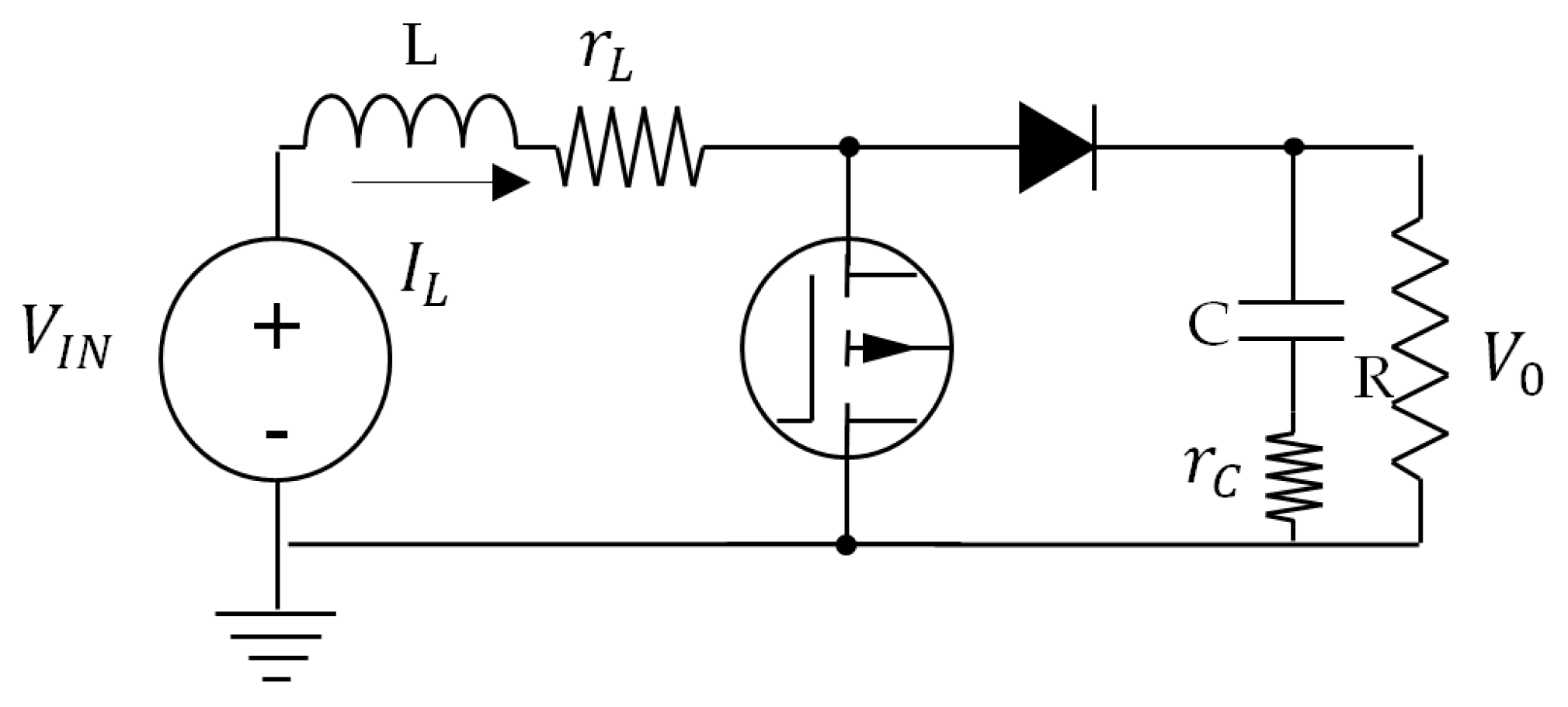

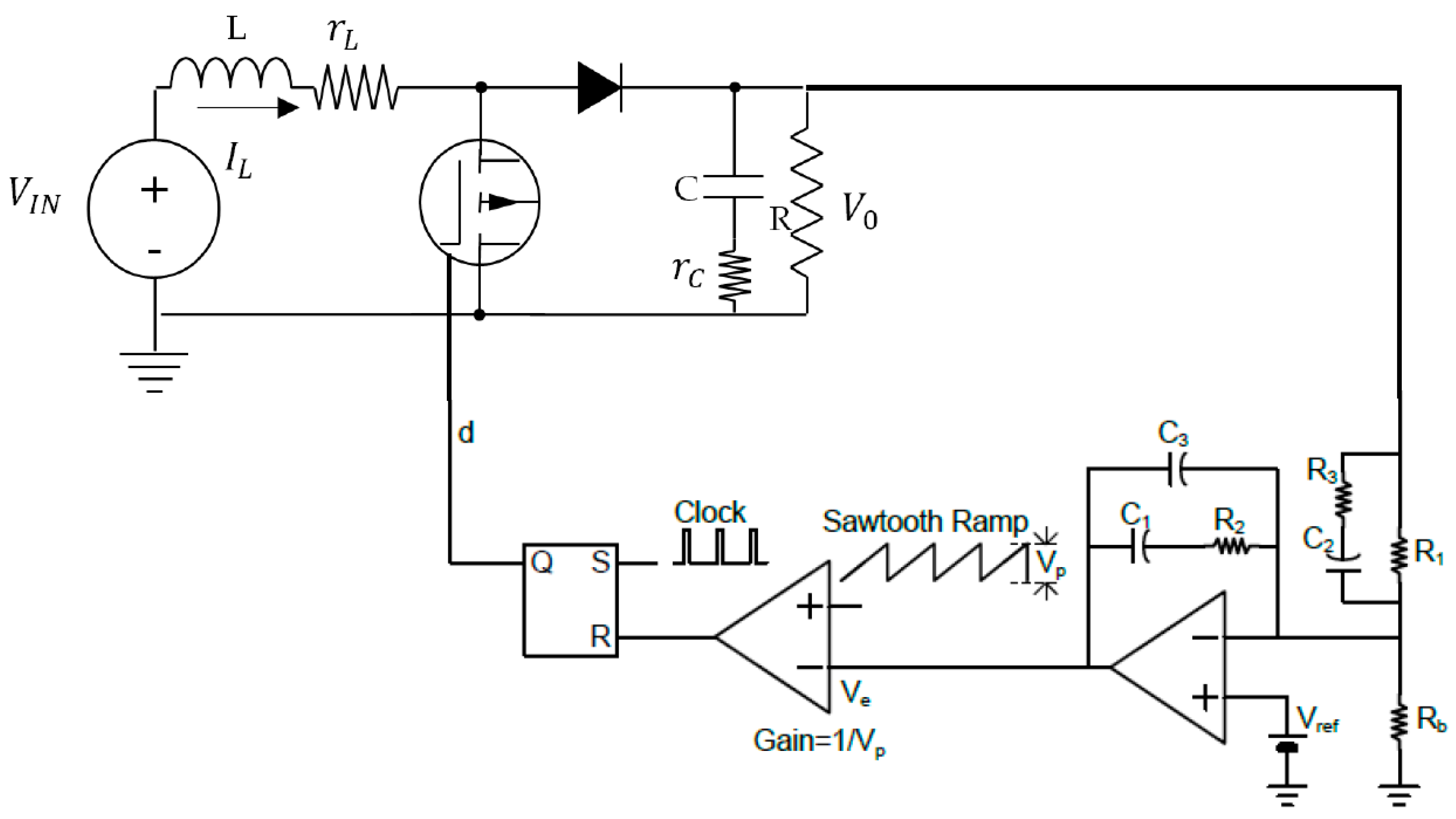

2. DC–DC Boost Converter

3. PID Type III and ARMarkov Predictive Control Design

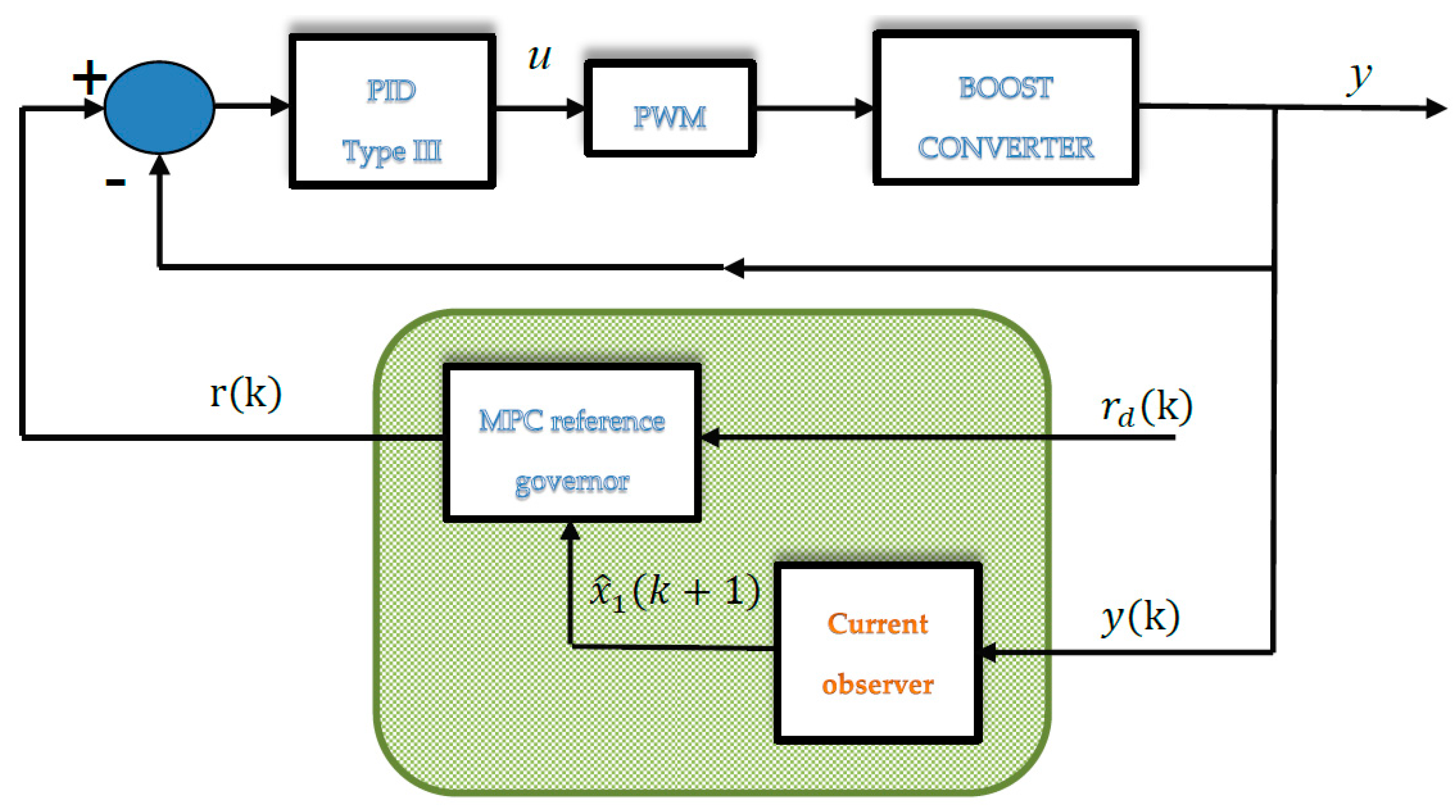

4. MPC Reference Governor Design for a Voltage-Mode-Controlled Converter

4.1. Converter State-Space Modeling

4.2. PID Controller State-Space Form

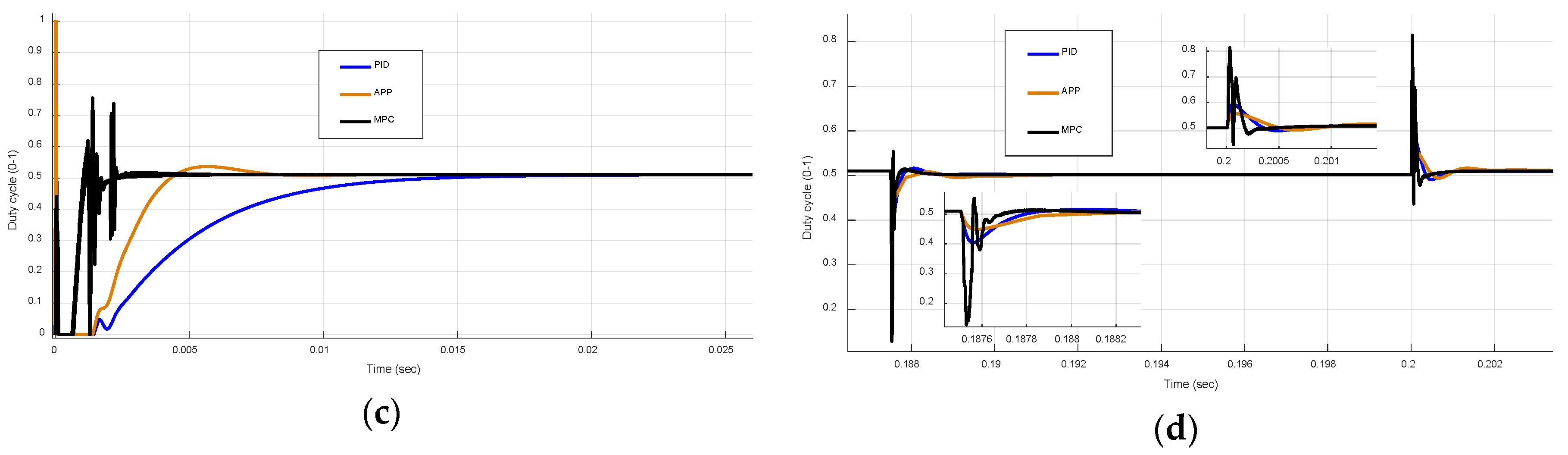

4.3. Reference Governor MPC Design and Tuning

4.4. Nonlinear Current Observer

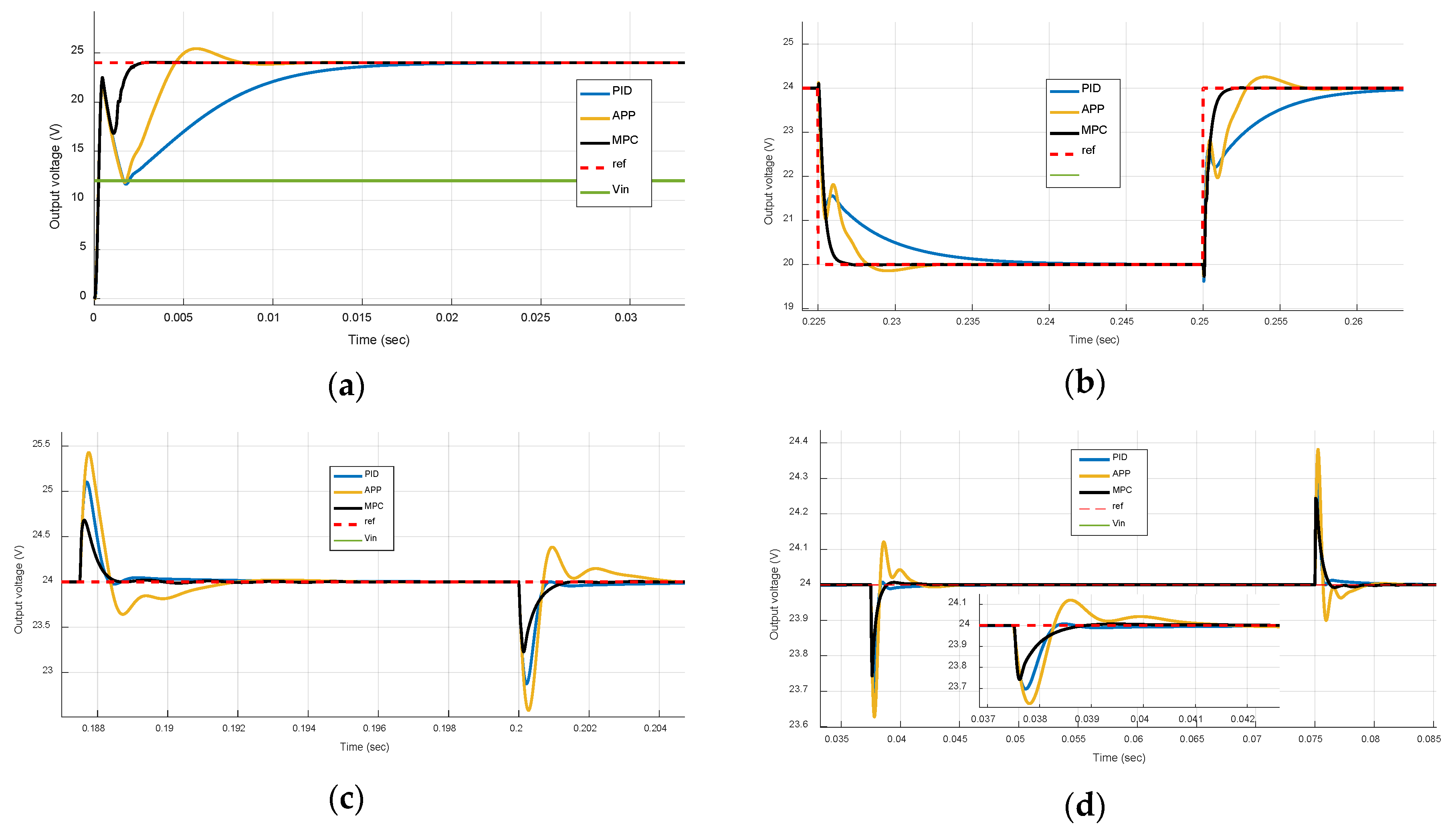

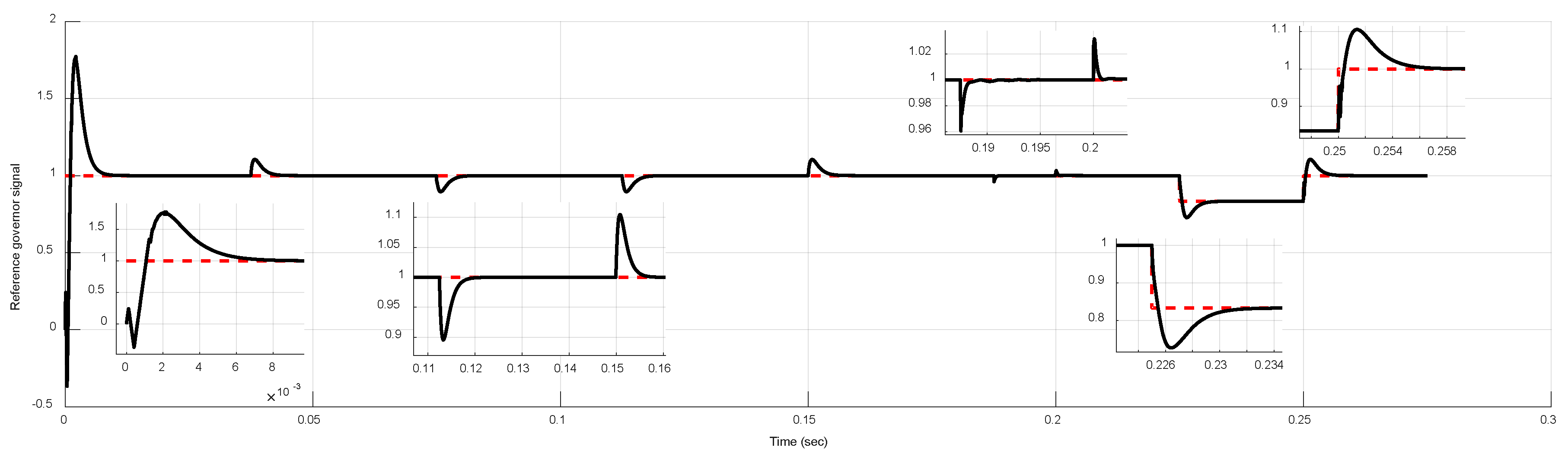

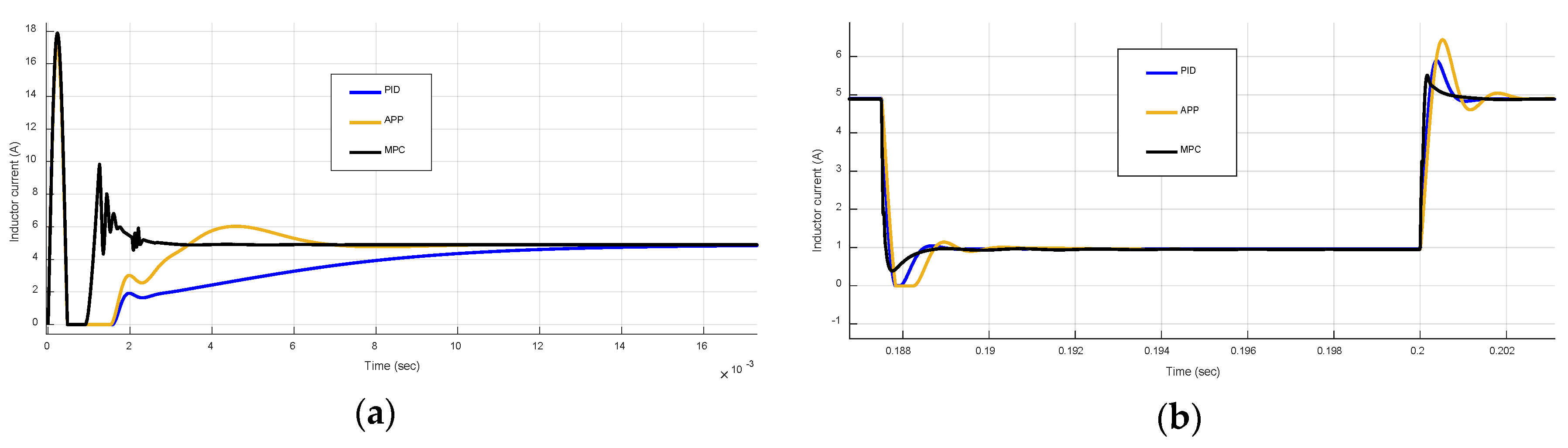

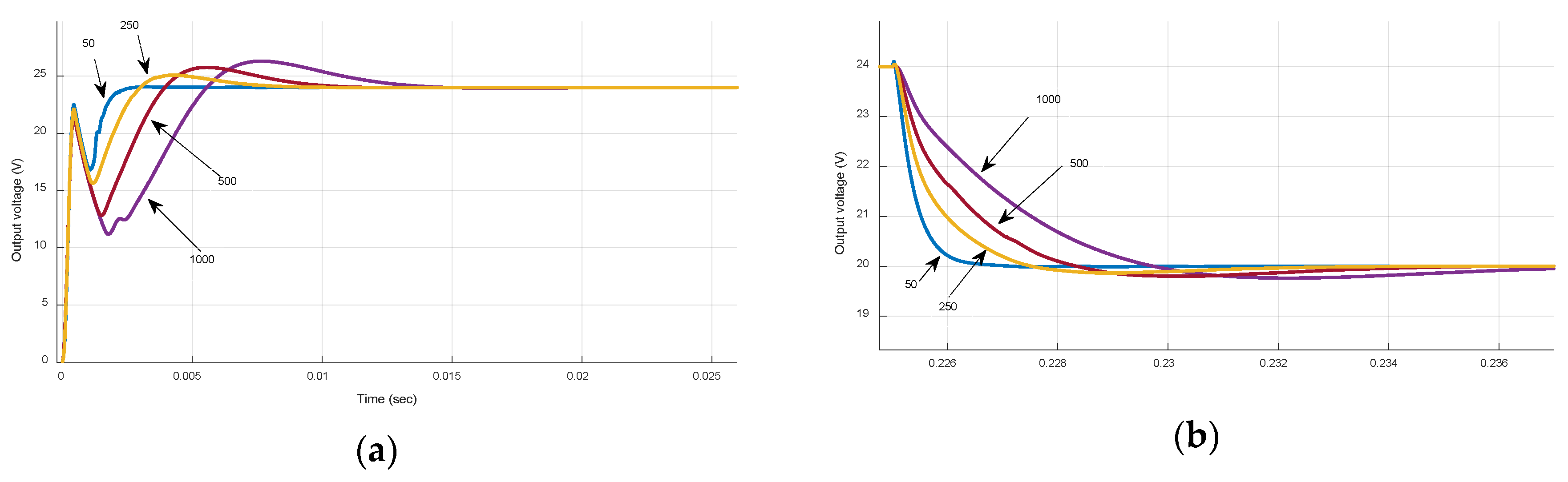

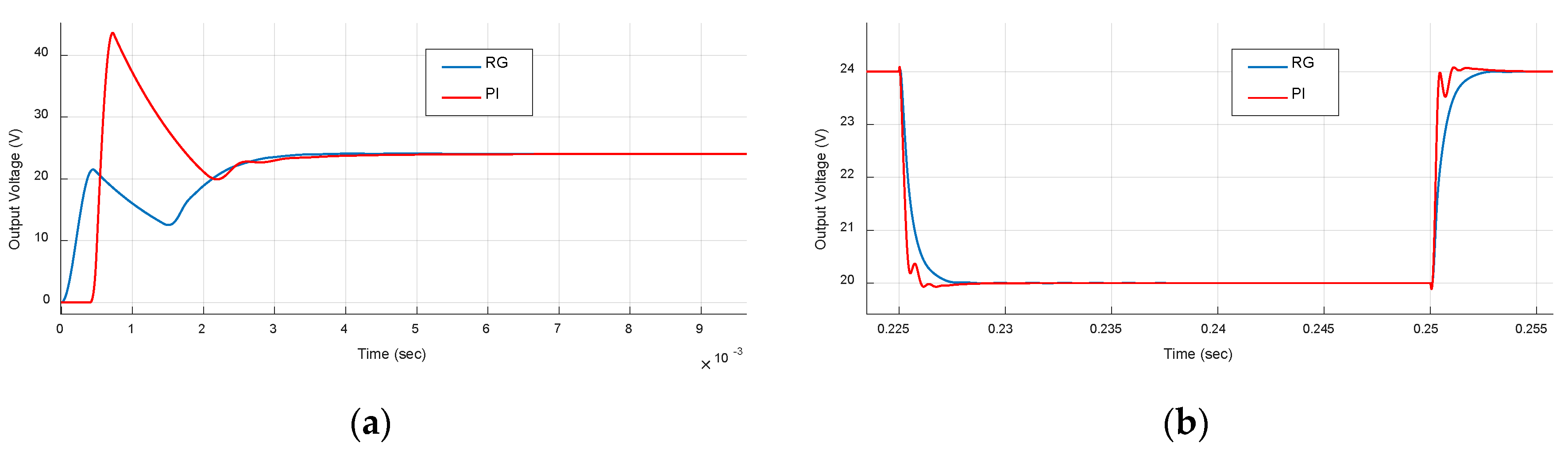

5. Numerical Simulation Results

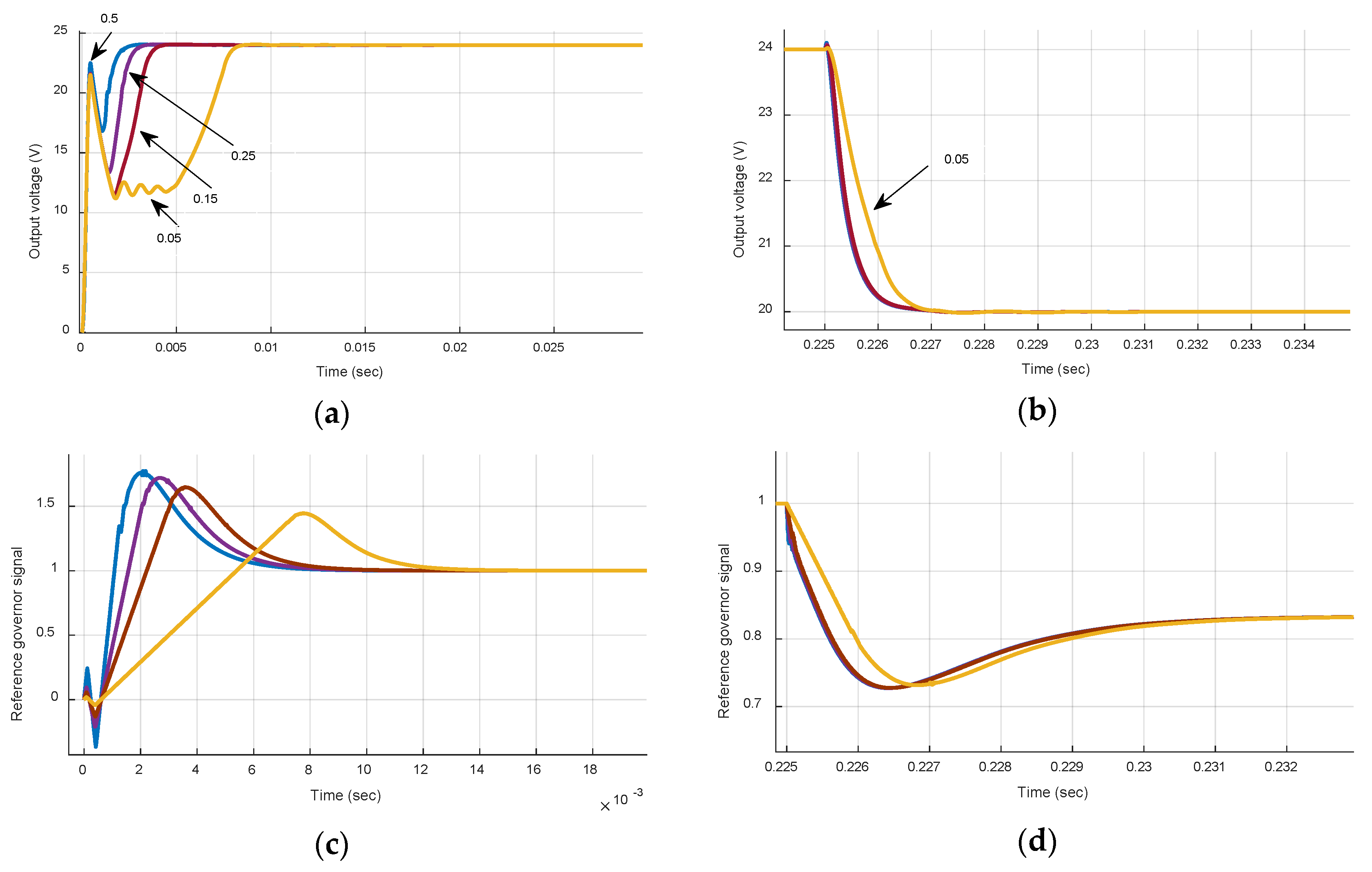

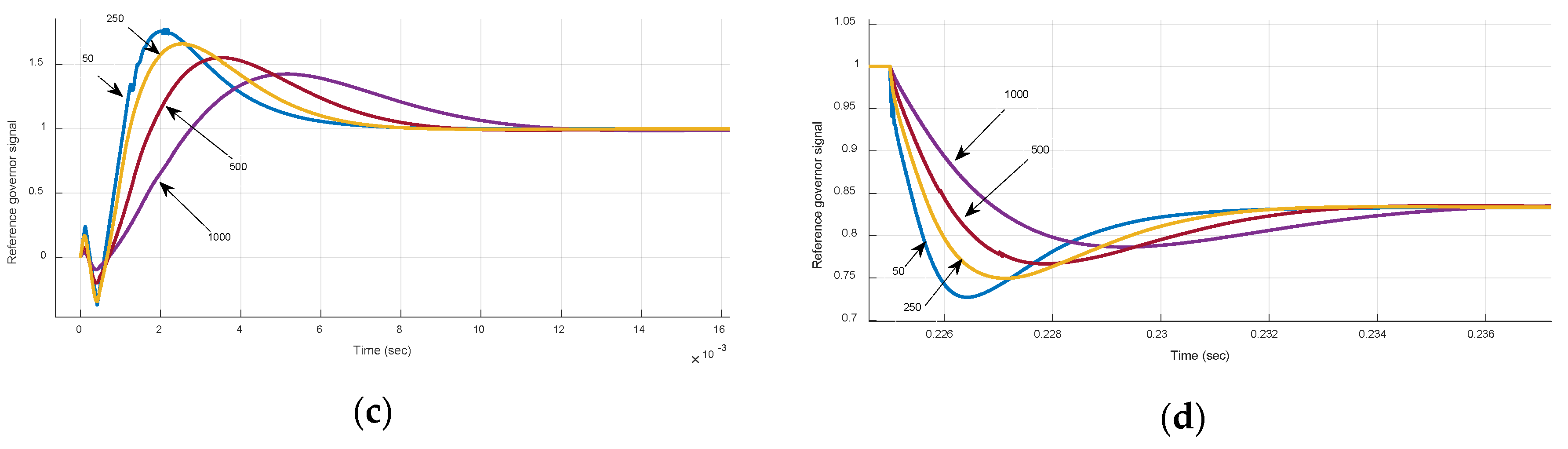

6. MPC Reference Governor Design for a Two-Loop Current-Mode-Controlled Converter

6.1. Two-Loop PI Controller State-Space Form

6.2. Current-Mode Reference Governor MPC Formulation

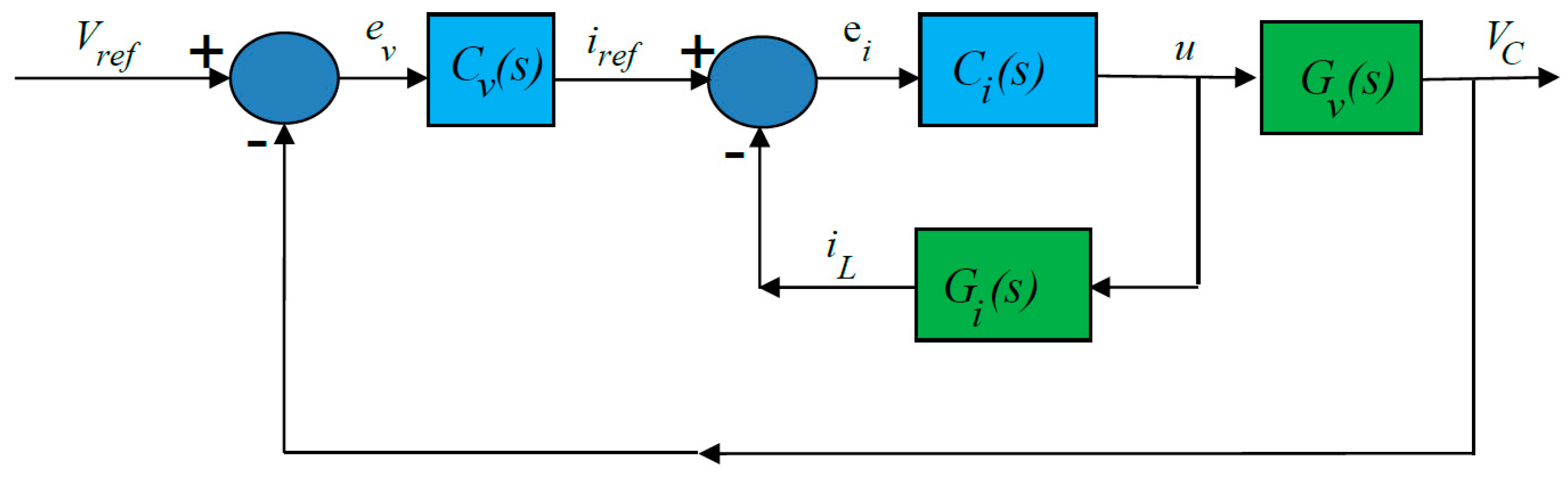

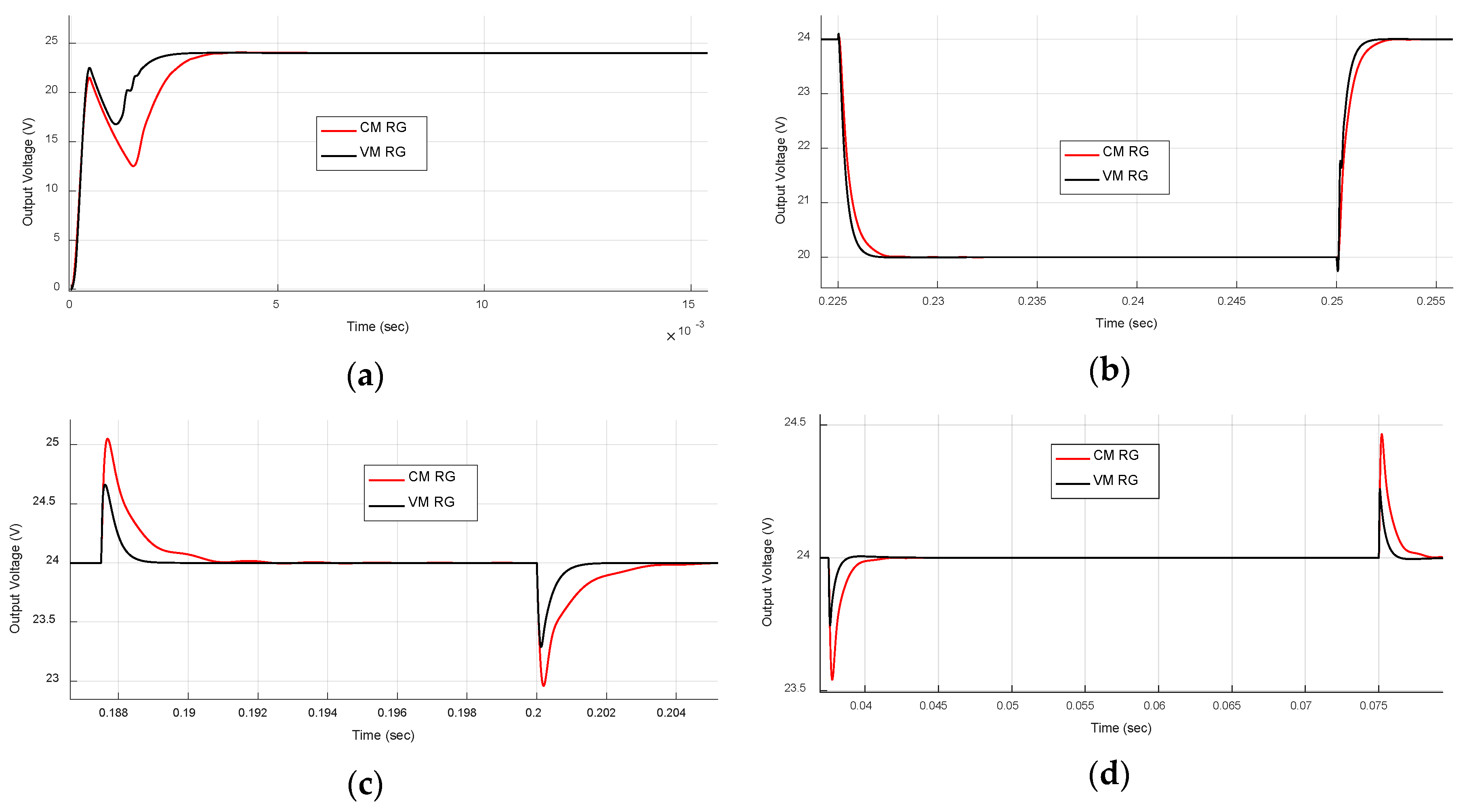

6.3. Numerical Simulation Results

7. Conclusions

Funding

Acknowledgments

Conflicts of Interest

References

- Cavanini, L.; Cimini, G.; Ippoliti, G.; Bemporad, A. Model predictive control for pre-compensated voltage mode controlled DC–DC converters. IET Control Theory Appl. 2017, 11, 2514–2520. [Google Scholar] [CrossRef]

- Cavanini, L.; Cimini, G.; Ippoliti, G. Model Predictive Control for the Reference Regulation of Current Mode Controlled DC–DC Converters. In Proceedings of the 2016 IEEE 14th International Conference on Industrial Informatics (INDIN), Poitiers, France, 19 January 2017. [Google Scholar]

- Kurokawa, F.; Yamanishi, A.; Hirotaki, S. A reference modification model digitally controlled DC–DC converter for improvement of transient response. IEEE Trans. Power Electron. 2016, 31, 871–883. [Google Scholar] [CrossRef]

- Kolmanovsky, I.; Garone, E.; Di Cairano, S. Reference and Command Governors: A Tutorial on Their Theory and Automotive Applications. In Proceedings of the 2014 American Control Conference (ACC), Portland, OR, USA, 21 July 2014; pp. 226–241. [Google Scholar]

- Kogiso, K.; Hirata, K. Reference governor for constrained systems with time-varying references. Robot. Auton. Syst. 2009, 57, 289–295. [Google Scholar] [CrossRef]

- Jade, S.; Hellström, E.; Larimore, J.; Stefanopoulou, A.G.; Jiang, L. Reference governor for load control in a multi cylinder recompression HCCI engine. IEEE Trans. Control Syst. Technol. 2014, 22, 1408–1421. [Google Scholar] [CrossRef]

- Olalla, C.; Leyva, R.; El Aroudi, A. Robust LQR control for PWM converters: An LMI approach. IEEE Trans. Ind. Electron. 2009, 56, 2548–2558. [Google Scholar] [CrossRef]

- Olalla, C.; Leyva, R.; El Aroudi, A.; Garćes, P.; Queinnec, I. LMI robust control design for boost PWM converters. IET Power Electron. 2010, 3, 75–85. [Google Scholar] [CrossRef]

- Olalla, C.; Queinnec, I.; Leyva, R.; El Aroudi, A. Robust optimal control of bilinear DC–DC converters. Control Eng. Pract. 2011, 19, 688–699. [Google Scholar] [CrossRef]

- Olalla, C.; Leyva, R.; Queinnec, I.; Maksimovic, D. Robust gain-scheduled control of switched-mode DC–DC converters. IEEE Trans. Power Electron. 2012, 27, 3006–3019. [Google Scholar] [CrossRef]

- Olalla, C.; Queinnec, I.; Leyva, R.; Aroudi, A.E. Optimal state-feedback control of bilinear DC–DC converters with guaranteed regions of stability. IEEE Trans. Ind. Electron. 2012, 59, 3868–3880. [Google Scholar] [CrossRef]

- Spinu, V.; Athanasopoulos, N.; Lazar, M.; Bitsoris, G. Stabilization of bilinear power converters by affine state feedback under input and state constraints. IEEE Trans. Circuits Syst.-II Express Briefs 2012, 59, 520–524. [Google Scholar] [CrossRef]

- Yfoulis, C.; Giaouris, D.; Stergiopoulos, F.; Ziogou, C.; Voutetakis, S.; Papadopoulou, S. Robust constrained stabilization and tracking of a boost DC–DC converter through bifurcation analysis. Control Eng. Pract. 2015, 35, 67–82. [Google Scholar] [CrossRef]

- Vazquez, S.; Leon, J.I.; Franquelo, L.G.; Rodriguez, J.; Young, H.A.; Marquez, A.; Zanchetta, P. Model predictive control: a review of its applications in power electronics. IEEE Ind. Electron. Mag. 2014, 8, 16–31. [Google Scholar] [CrossRef]

- Mariethoz, S.; Almer, S.; Baja, M.; Giovanni Beccuti, A.; Patino, D.; Wernrud, A.; Buisson, J.; Cormerais, H.; Geyer, T.; Fujioka, H. Comparison of hybrid control techniques for buck and boost DC–DC converters. IEEE Trans. Control Syst. Technol. 2010, 18, 1126–1145. [Google Scholar] [CrossRef]

- Bordons, C.; Montero, C. Basic principles of MPC for power converters: bridging the gap between theory and practice. IEEE Ind. Electron. Mag. 2015, 9, 31–43. [Google Scholar] [CrossRef]

- Kouro, S.; Perez, M.A.; Rodriguez, J.; Llor, A.M. Model predictive control: MPC’s role in the evolution of power electronics. IEEE Ind. Electron. Mag. 2015, 9, 8–21. [Google Scholar] [CrossRef]

- Giovanni Beccuti, A.; Mariethoz, S.; Cliquennois, S.; Wang, S.; Morari, M. Explicit model predictive control of DC–DC switched-mode power supplies with extended Kalman filtering. IEEE Trans. Ind. Electron. 2009, 56, 1864–1874. [Google Scholar] [CrossRef]

- Kim, S.-K.; Park, C.R.; Kim, J.-S.; Lee, Y.I. A stabilizing model predictive controller for voltage regulation of a DC/DC boost converter. IEEE Trans. Control Syst. Technol. 2014, 22, 2016–2023. [Google Scholar] [CrossRef]

- Zaitsu, R. Voltage Mode Boost Converter Small Signal Control Loop Analysis Using the TPS61030; Application Report for Texas instruments; Dallas, TX, USA, January 2009. [Google Scholar]

- Lee, S.W. Practical Feedback Loop Analysis for Voltage-Mode Boost Converter; Application Report for Texas instruments; Dallas, TX, USA, January 2014. [Google Scholar]

- Anzehaee, M.M.; Behnam, B.; Hajihosseini, P. Augmenting ARMarkov-PFC predictive controller with PID-Type III to improve boost converter operation. Control Eng. Pract. 2018, 79, 65–77. [Google Scholar] [CrossRef]

- Basso, C.P. Switch-mode power supplies spice simulations and practical designs; McGraw-Hill Inc.: New York, NY, USA, 2008. [Google Scholar]

- Liuping, W. Model Predictive Control System Design and Implementation Using MATLAB; Springer: New York, NY, USA, 2009. [Google Scholar]

- Cimini, G.; Ippoliti, G.; Orlando, G.; Longhi, S.; Miceli, R. A unified observer for robust sensorless control of DC–DC converters. Control Eng. Pract. 2017, 61, 21–27. [Google Scholar] [CrossRef]

- Bacha, S.; Munteanu, I.; Bratcu, A.I. Power Electronic Converters Modeling and Control: With Case Studies, Advanced Textbooks in Control and Signal Processing; Springer: New York, NY, USA, 2014. [Google Scholar]

- Ozdemir, A.; Erdem, Z. Double-Loop PI Controller Design of the DC–DC Boost Converter with a Proposed Approach for Calculation of the Controller Parameters. Syst. Control Eng. 2018, 232, 137–148. [Google Scholar] [CrossRef]

| 200 | 8–14 | 100 | 0.05 | 200 | 10–50 | 0.01 | 24 | 0.42–0.58 |

| Main Control Frequency | MPC Control Frequency | ||||

|---|---|---|---|---|---|

| 45 | 1 | 50 | 0.5 | 200 kHz | 100 kHz |

| Design | ||||||

|---|---|---|---|---|---|---|

| PI 1 | 0.025 | 126 | 0.84 | 922 | 3 | 0.7 |

| PI 2 | 0.046 | 357 | 1.4 | 1448 | 1 | 0.7 |

| Main Control Frequency | MPC Control Frequency | ||||

|---|---|---|---|---|---|

| 100 | 1 | 200 | 0.5 | 200 KHz | 100 KHz |

© 2019 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yfoulis, C. An MPC Reference Governor Approach for Enhancing the Performance of Precompensated Boost DC–DC Converters. Energies 2019, 12, 563. https://doi.org/10.3390/en12030563

Yfoulis C. An MPC Reference Governor Approach for Enhancing the Performance of Precompensated Boost DC–DC Converters. Energies. 2019; 12(3):563. https://doi.org/10.3390/en12030563

Chicago/Turabian StyleYfoulis, Christos. 2019. "An MPC Reference Governor Approach for Enhancing the Performance of Precompensated Boost DC–DC Converters" Energies 12, no. 3: 563. https://doi.org/10.3390/en12030563

APA StyleYfoulis, C. (2019). An MPC Reference Governor Approach for Enhancing the Performance of Precompensated Boost DC–DC Converters. Energies, 12(3), 563. https://doi.org/10.3390/en12030563