Autonomous Demand-Side Current Scheduling of Parallel Buck Regulated Battery Modules

Abstract

1. Introduction

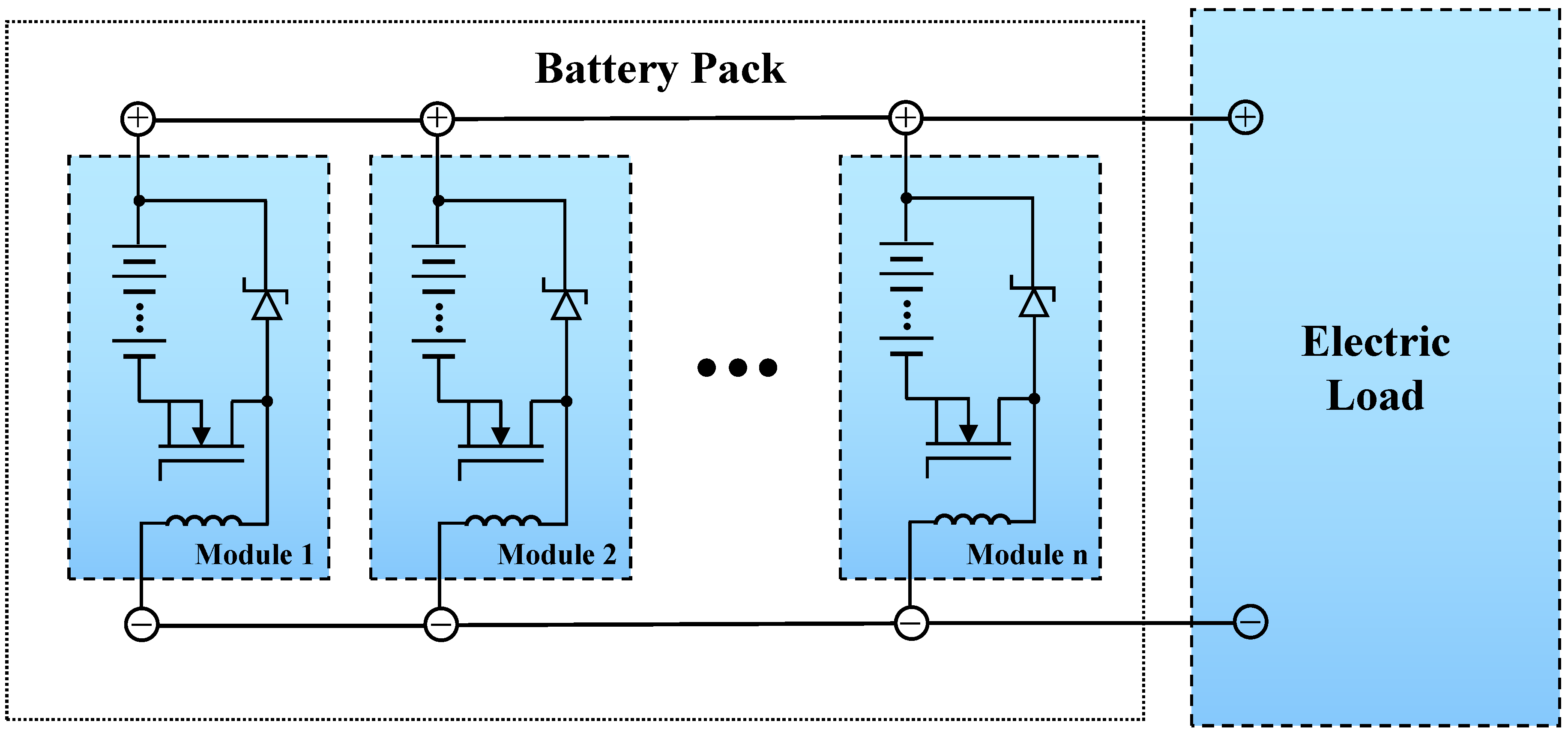

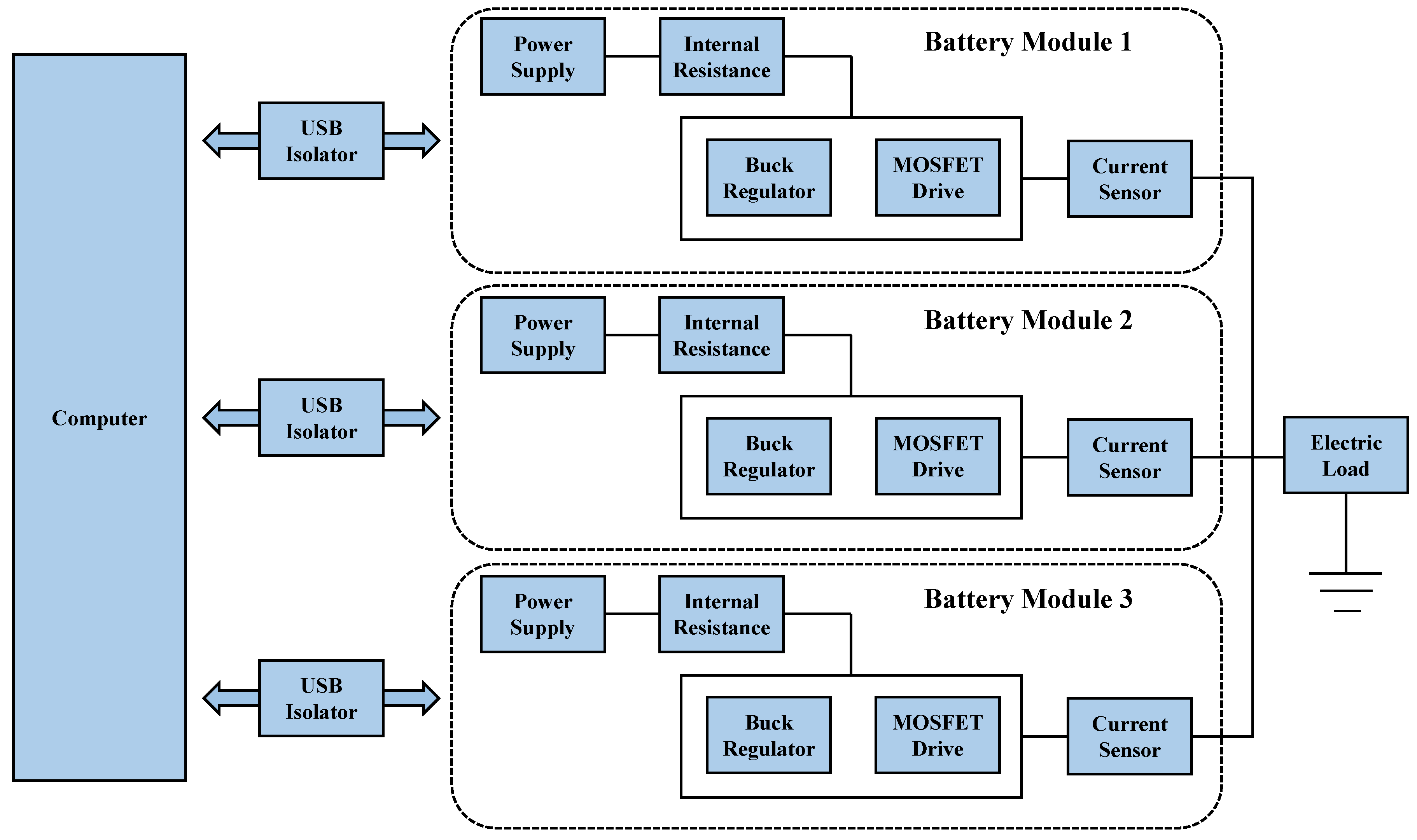

2. Parallel Buck Regulated Battery Modules

2.1. Module Formulation and Assumptions

- The ideal voltage supply can be given by , where the Open Circuit Voltage (OCV) is the terminal voltage of a battery module in the case no external load is connected. The voltage modulation coefficient represents the PWM duty cycle of MOSFET applied by a buck regulator.

- The slowly time-varying internal impedance of a battery module is given by a constant and possibly known value in comparison with the time-varying natural of the external unknown load impedance .

- The algebraic sum of current of each battery module is equal to bus currentdue to Kirchhoff’s current law (KCL).

- Similar to KCL, the bus voltage can be satisfiedfor each battery module k due to Kirchhoff’s voltage law (KVL).

2.2. The Formulation of Module Voltages and Module Currents

2.3. Impedance Matrix and Current Vector

3. Open-Loop Optimal Current Scheduling

3.1. Relative Scaling of Module Currents

3.2. Module Current Scheduling via Linear Programming

3.3. Decentralized Recursive Optimal Current Scheduling

- Assume fixed internal impedances but a time-varying load impedance .

- Set initial time index and communicate the n elements of the initial module voltages to each of the corresponding modules .

- At time index t, each individual module m measures the module current and compute the bus voltagethe bus currentand further update the impedance matrix in Equation (6) with full information of internal impedance and estimated load impedance .

- Before the subsequent time Step , each individual module updates the optimal module voltages according towhere is obtained by the LP problem in Equation (9) solved in each module.

- At time Step , each module m updates the module voltage to of the

- Increment time index and restart from Step 1.

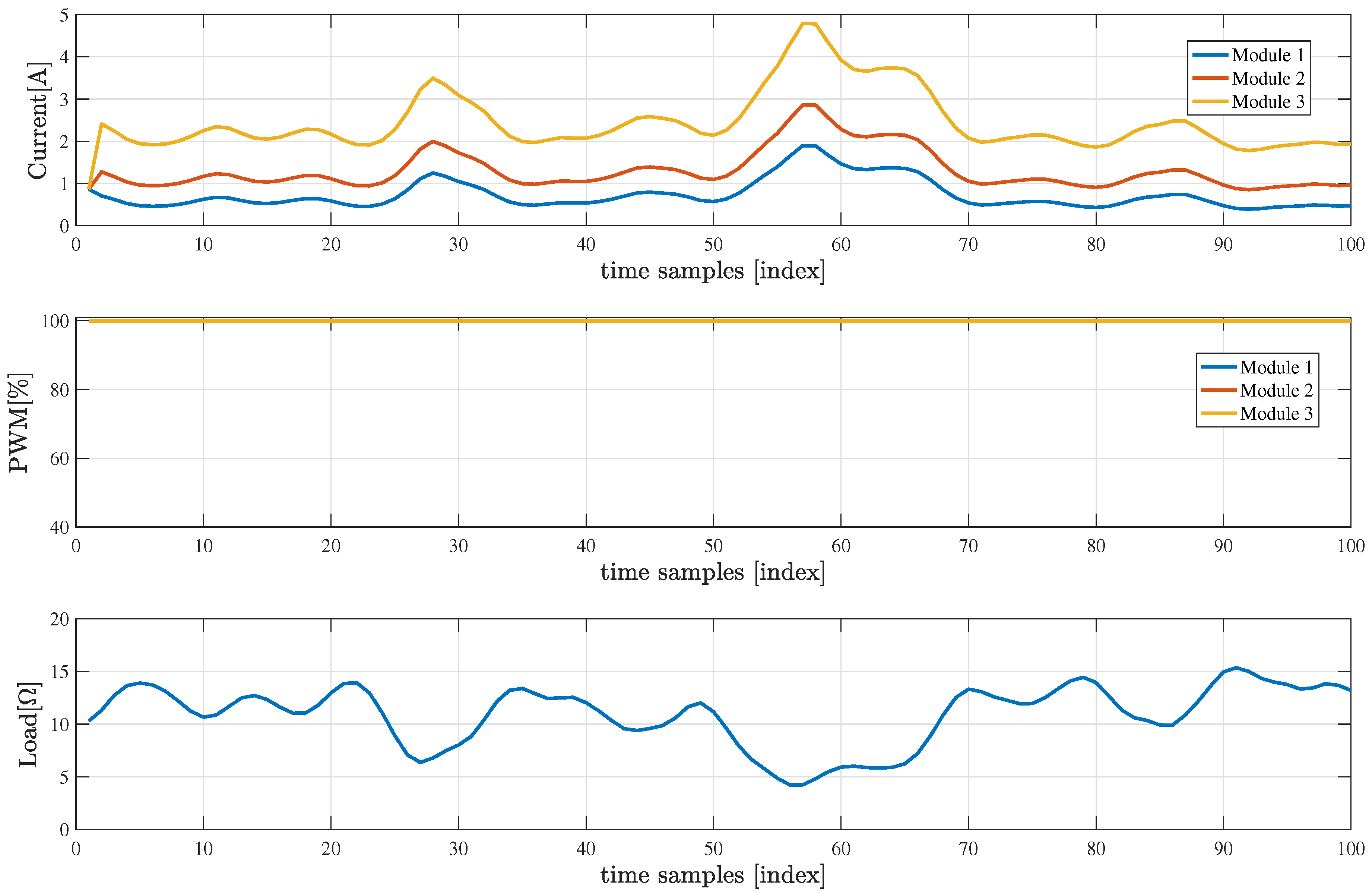

3.4. Numerical Illustration of Recursive Equal SOC Current Scheduling

Unknown, Time-Varying External Load

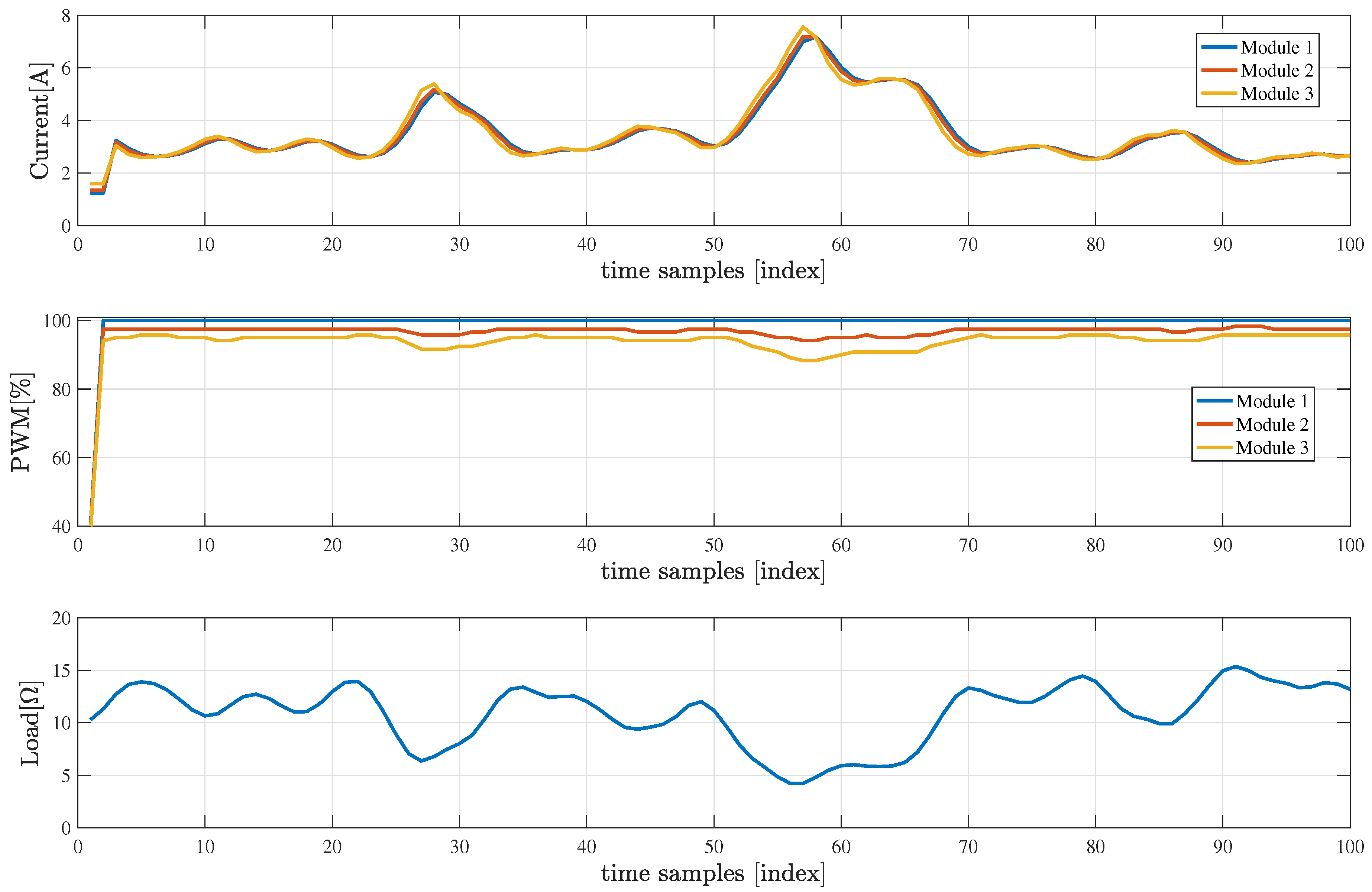

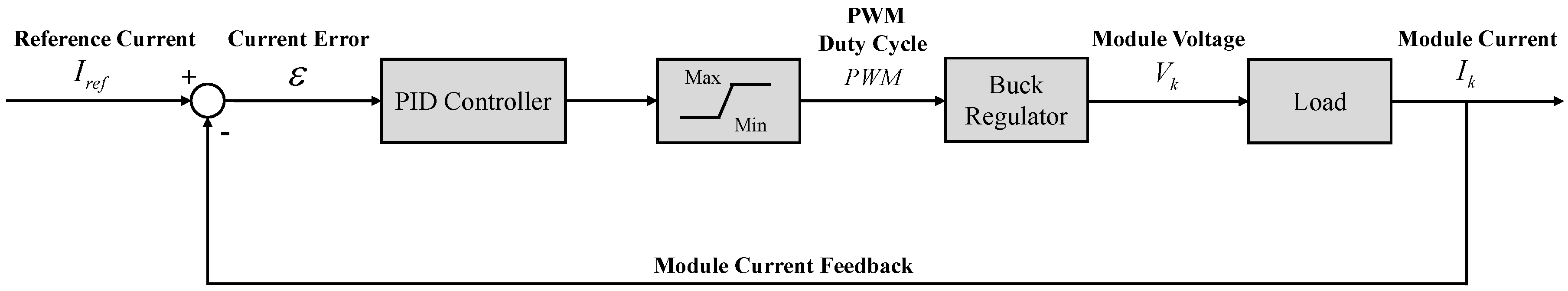

4. Closed-Loop Current Scheduling

4.1. Decentralized Digital Control

4.2. Recursive Reference Adjustment for Load-Tracking

- Set initial time index and communicate the n elements of the initial reference currents to each of the corresponding modules .

- At time index t, perform a monitor of PWM duty cycle and a measurement of module current of every individual module k. If any module gets to duty cycle, go to Step 3, otherwise update the reference current with a fast ramp-up rate noted by “initial rate” to increase module current .

- If any module gets to (full) duty cycle and the absolute current difference between different modules is less than the current difference threshold e, optimal module currents are found and set to be the same value as the reference current sending the system into an idle status. If not, decrease reference current to with a small ramp-down rate and repeat Step 3 until go to idle status.

- After getting into idle status, if the PWM duty cycle of each module suddenly below the threshold value of , the reference current needs to be increased to with relatively large ramp-up rate and repeat from Step 2, to satisfy larger optimal balanced module currents due to load increase (load impedance decrease) demand. If the PWM duty cycle remains larger than or equal to the threshold of value , go to Step 5.

- In the case the PWM duty cycle of every module becomes larger than or equal to threshold PWM value of but absolute current difference between different modules is larger, it is necessary to decrease reference current to with the same ramp-up rate in Step 4 to find optimal balanced current due to load decrease (load impedance increase) demand. Restart from Step 2.

5. Experimental Verification

5.1. Experimental Setup

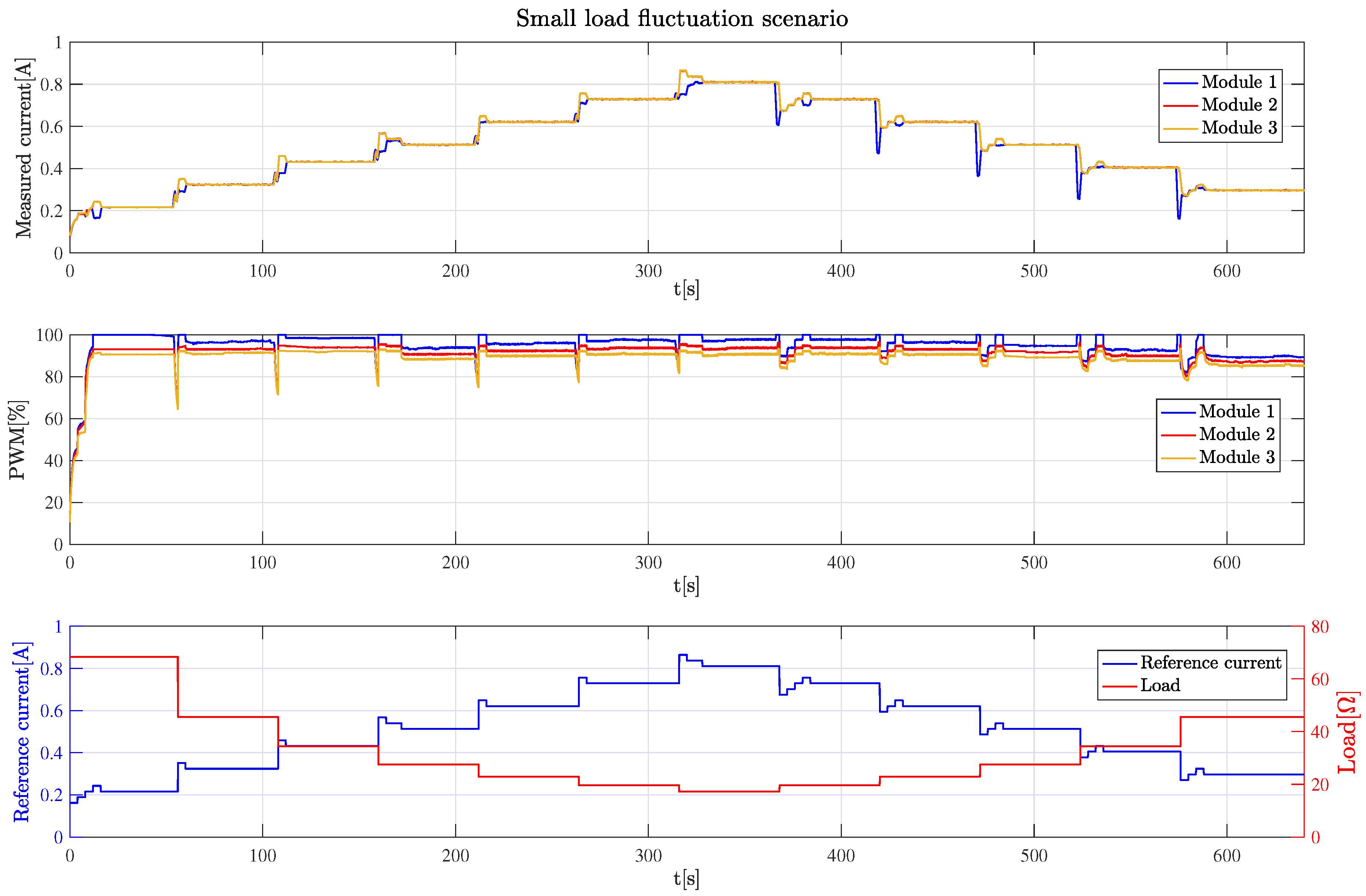

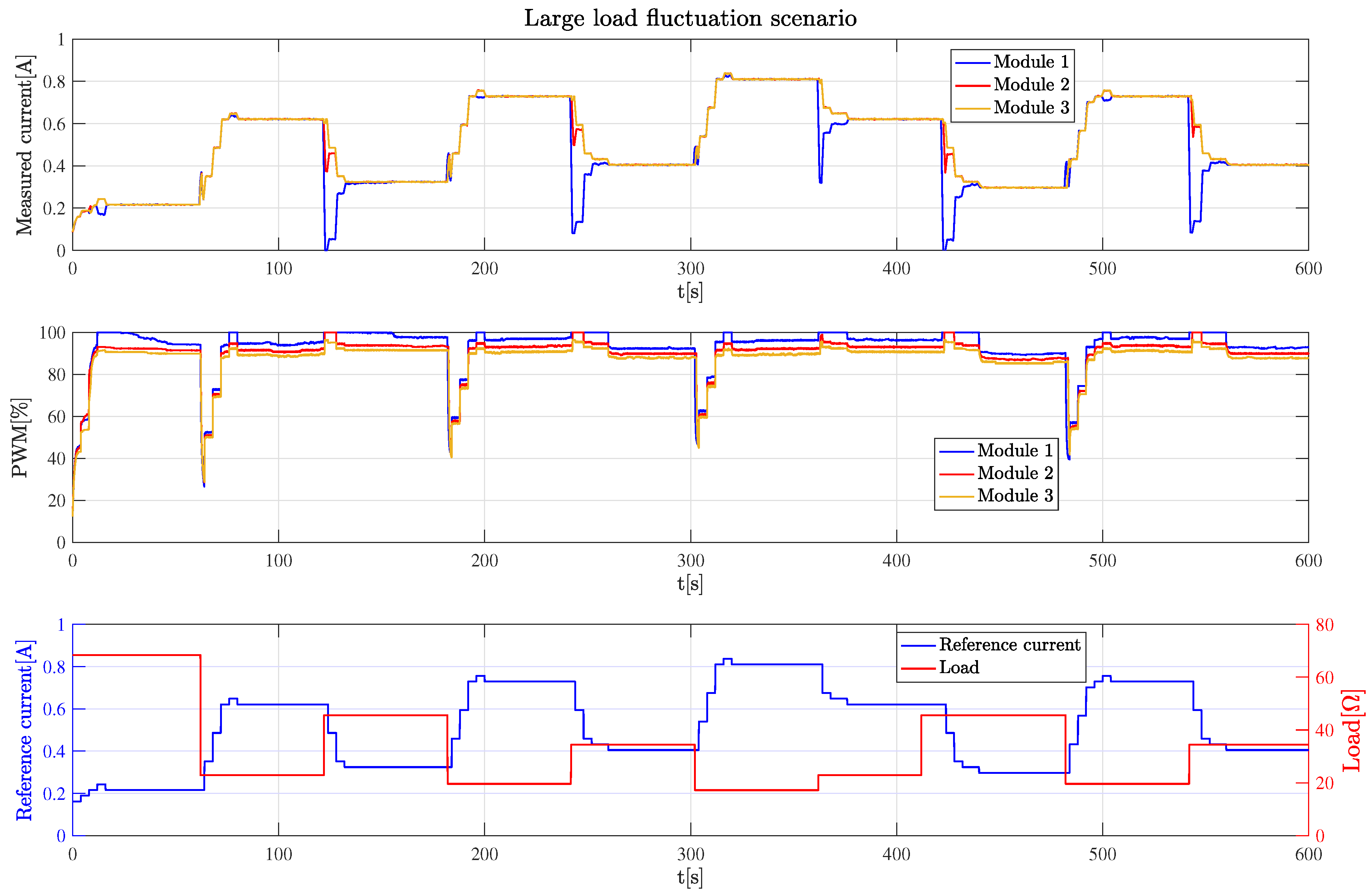

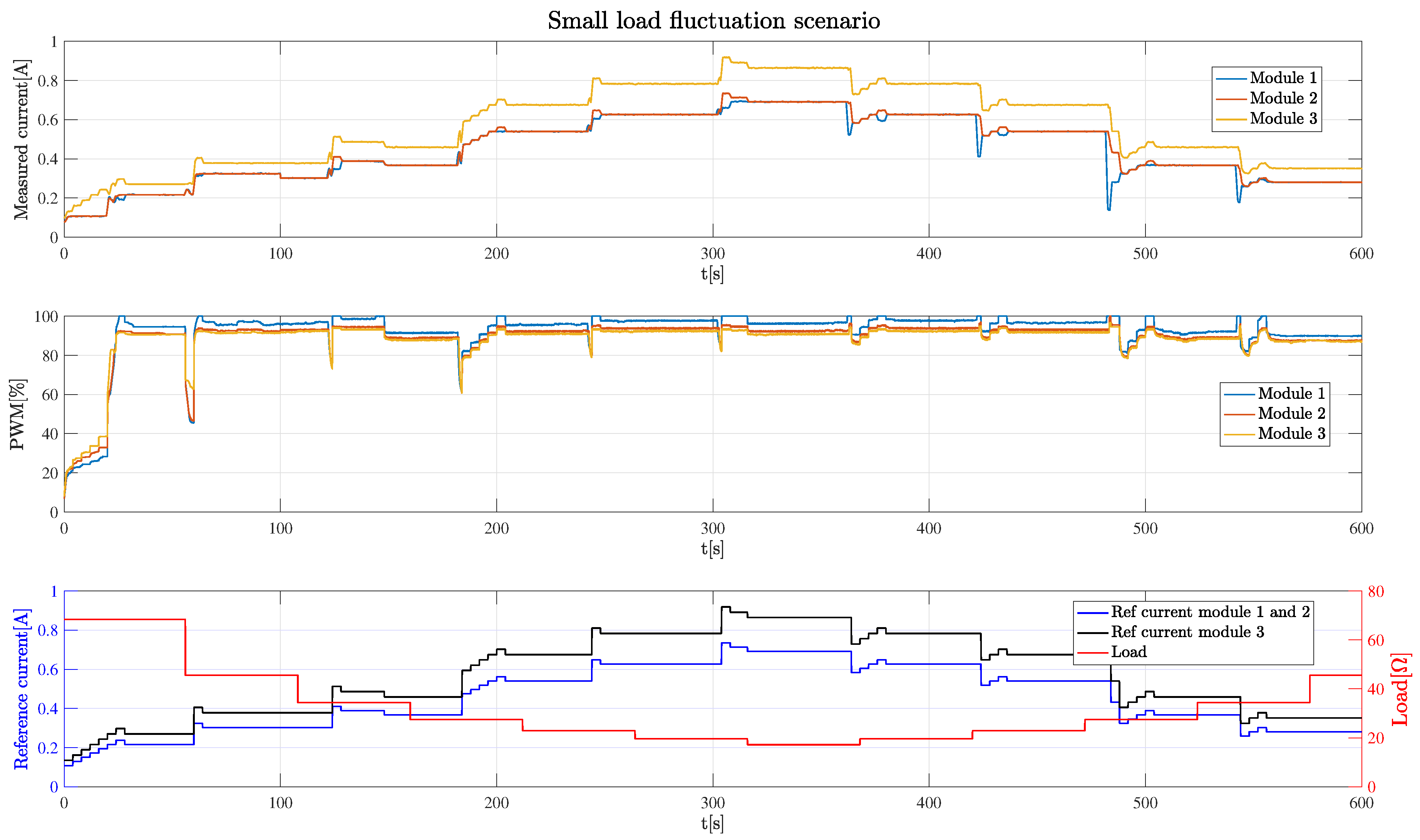

5.2. Experimental Results with Varying Load Conditions

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ren, H.; Zhao, Y.; Chen, S.; Wang, T. Design and implementation of a battery management system with active charge balance based on the SOC and SOH online estimation. Energy 2019, 166, 908–917. [Google Scholar] [CrossRef]

- Wang, Y.; Shi, W.; Wang, B.; Chu, C.C.; Gadh, R. Optimal operation of stationary and mobile batteries in distribution grids. Appl. Energy 2017, 190, 1289–1301. [Google Scholar] [CrossRef]

- Ghorbanzadeh, M.; Astaneh, M.; Golzar, F. Long-term degradation based analysis for lithium-ion batteries in off-grid wind-battery renewable energy systems. Energy 2019, 166, 1194–1206. [Google Scholar] [CrossRef]

- Wang, Y.; Chen, Z.; Zhang, C. On-line remaining energy prediction: A case study in embedded battery management system. Appl. Energy 2017, 194, 688–695. [Google Scholar] [CrossRef]

- Bouchhima, N.; Schnierle, M.; Schulte, S.; Birke, K.P. Optimal energy management strategy for self-reconfigurable batteries. Energy 2017, 122, 560–569. [Google Scholar] [CrossRef]

- Xia, B.; Shang, Y.; Nguyen, T.; Mi, C. A correlation based fault detection method for short circuits in battery packs. J. Power Sources 2017, 337, 1–10. [Google Scholar] [CrossRef]

- Cai, Y.; Ouyang, M.; Yang, F. Impact of power split configurations on fuel consumption and battery degradation in plug-in hybrid electric city buses. Appl. Energy 2017, 188, 257–269. [Google Scholar] [CrossRef]

- Xia, B.; Zhao, X.; De Callafon, R.; Garnier, H.; Nguyen, T.; Mi, C. Accurate Lithium-ion battery parameter estimation with continuous-time system identification methods. Appl. Energy 2016, 179, 426–436. [Google Scholar] [CrossRef]

- Chen, Z.; Xiong, R.; Tian, J.; Shang, X.; Lu, J. Model-based fault diagnosis approach on external short circuit of lithium-ion battery used in electric vehicles. Appl. Energy 2016, 184, 365–374. [Google Scholar] [CrossRef]

- Liu, Z.; He, H. Sensor fault detection and isolation for a lithium-ion battery pack in electric vehicles using adaptive extended Kalman filter. Appl. Energy 2017, 185, 2033–2044. [Google Scholar] [CrossRef]

- Tong, S.J.; Same, A.; Kootstra, M.A.; Park, J.W. Off-grid photovoltaic vehicle charge using second life lithium batteries: An experimental and numerical investigation. Appl. Energy 2013, 104, 740–750. [Google Scholar] [CrossRef]

- Deng, Y.; Li, J.; Li, T.; Zhang, J.; Yang, F.; Yuan, C. Life cycle assessment of high capacity molybdenum disulfide lithium-ion battery for electric vehicles. Energy 2017, 123, 77–88. [Google Scholar] [CrossRef]

- Finesso, R.; Spessa, E.; Venditti, M. Cost-optimized design of a dual-mode diesel parallel hybrid electric vehicle for several driving missions and market scenarios. Appl. Energy 2016, 177, 366–383. [Google Scholar] [CrossRef]

- Siu, M.; Mok, P.K.; Leung, K.N.; Lam, Y.H.; Ki, W.H. A voltage-mode PWM buck regulator with end-point prediction. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 294–298. [Google Scholar]

- Jiang, Y.; Zhao, X.; Valibeygi, A.; de Callafon, R.A. Dynamic prediction of power storage and delivery by data-based fractional differential models of a lithium iron phosphate battery. Energies 2016, 9, 590. [Google Scholar] [CrossRef]

- Sturm, J.; Ennifar, H.; Erhard, S.; Rheinfeld, A.; Kosch, S.; Jossen, A. State estimation of lithium-ion cells using a physicochemical model based extended Kalman filter. Appl. Energy 2018, 223, 103–123. [Google Scholar] [CrossRef]

- Jiang, Y.; Xia, B.; Zhao, X.; Nguyen, T.; Mi, C.; de Callafon, R.A. Identification of Fractional Differential Models for Lithium-ion Polymer Battery Dynamics. IFAC-PapersOnLine 2017, 50, 405–410. [Google Scholar] [CrossRef]

- Jiang, Y.; Xia, B.; Zhao, X.; Nguyen, T.; Mi, C.; de Callafon, R.A. Data-based fractional differential models for non-linear dynamic modeling of a lithium-ion battery. Energy 2017, 135, 171–181. [Google Scholar] [CrossRef]

- Zhao, X.; de Callafon, R.A.; Shrinkle, L. Current Scheduling for Parallel Buck Regulated Battery Modules. IFAC Proc. Vol. 2014, 47, 2112–2117. [Google Scholar] [CrossRef]

- Chiu, K.C.; Lin, C.H.; Yeh, S.F.; Lin, Y.H.; Huang, C.S.; Chen, K.C. Cycle life analysis of series connected lithium-ion batteries with temperature difference. J. Power Sources 2014, 263, 75–84. [Google Scholar] [CrossRef]

- Vetter, J.; Novák, P.; Wagner, M.; Veit, C.; Möller, K.C.; Besenhard, J.; Winter, M.; Wohlfahrt-Mehrens, M.; Vogler, C.; Hammouche, A. Ageing mechanisms in lithium-ion batteries. J. Power Sources 2005, 147, 269–281. [Google Scholar] [CrossRef]

- Diao, W.; Xue, N.; Bhattacharjee, V.; Jiang, J.; Karabasoglu, O.; Pecht, M. Active battery cell equalization based on residual available energy maximization. Appl. Energy 2018, 210, 690–698. [Google Scholar] [CrossRef]

- Altaf, F.; Johannesson, L.; Egardt, B. Simultaneous thermal and state-of-charge balancing of batteries: A review. In Proceedings of the 2014 IEEE Vehicle Power and Propulsion Conference (VPPC), Coimbra, Portugal, 27–30 October 2014; pp. 1–7. [Google Scholar]

- Rehman, M.M.U.; Evzelman, M.; Hathaway, K.; Zane, R.; Plett, G.L.; Smith, K.; Wood, E.; Maksimovic, D. Modular approach for continuous cell-level balancing to improve performance of large battery packs. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 4327–4334. [Google Scholar]

- Rehman, M.M.U.; Zhang, F.; Evzelman, M.; Zane, R.; Smith, K.; Maksimovic, D. Advanced cell-level control for extending electric vehicle battery pack lifetime. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–8. [Google Scholar]

- Altaf, F.; Johannesson, L.; Egardt, B. Evaluating the potential for cell balancing using a cascaded multi-level converter using convex optimization. IFAC Proc. Vol. 2012, 45, 100–107. [Google Scholar] [CrossRef]

- Altaf, F.; Egardt, B. Comparative Analysis of Unipolar and Bipolar Control of Modular Battery for Thermal and State-of-Charge Balancing. IEEE Trans. Veh. Technol. 2017, 66, 2927–2941. [Google Scholar] [CrossRef]

- Jiang, Y.; Habib, A.H.; Zhao, X.; Shrinkle, L.J.; de Callafon, R.A. Centralized Recursive Optimal Scheduling of Parallel Buck Regulated Battery Modules. In Proceedings of the 2017 IEEE 56th Annual Conference on Decision and Control (CDC), Melbourne, Australia, 12–15 December 2017; pp. 2029–2034. [Google Scholar]

- Majumder, R.; Chaudhuri, B.; Ghosh, A.; Majumder, R.; Ledwich, G.F. Improvement of stability and load sharing in an autonomous microgrid using supplementary droop control loop. IEEE Trans. Power Syst. 2010. (Unpublished). Available online: https://eprints.qut.edu.au/31221/ (accessed on 9 March 2010). [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, Y.; Shrinkle, L.J.; de Callafon, R.A. Autonomous Demand-Side Current Scheduling of Parallel Buck Regulated Battery Modules. Energies 2019, 12, 2095. https://doi.org/10.3390/en12112095

Jiang Y, Shrinkle LJ, de Callafon RA. Autonomous Demand-Side Current Scheduling of Parallel Buck Regulated Battery Modules. Energies. 2019; 12(11):2095. https://doi.org/10.3390/en12112095

Chicago/Turabian StyleJiang, Yunfeng, Louis J. Shrinkle, and Raymond A. de Callafon. 2019. "Autonomous Demand-Side Current Scheduling of Parallel Buck Regulated Battery Modules" Energies 12, no. 11: 2095. https://doi.org/10.3390/en12112095

APA StyleJiang, Y., Shrinkle, L. J., & de Callafon, R. A. (2019). Autonomous Demand-Side Current Scheduling of Parallel Buck Regulated Battery Modules. Energies, 12(11), 2095. https://doi.org/10.3390/en12112095