A Novel Fault-Tolerant Control of Modular Multilevel Converter under Sub-Module Faults Based on Phase Disposition PWM

Abstract

:1. Introduction

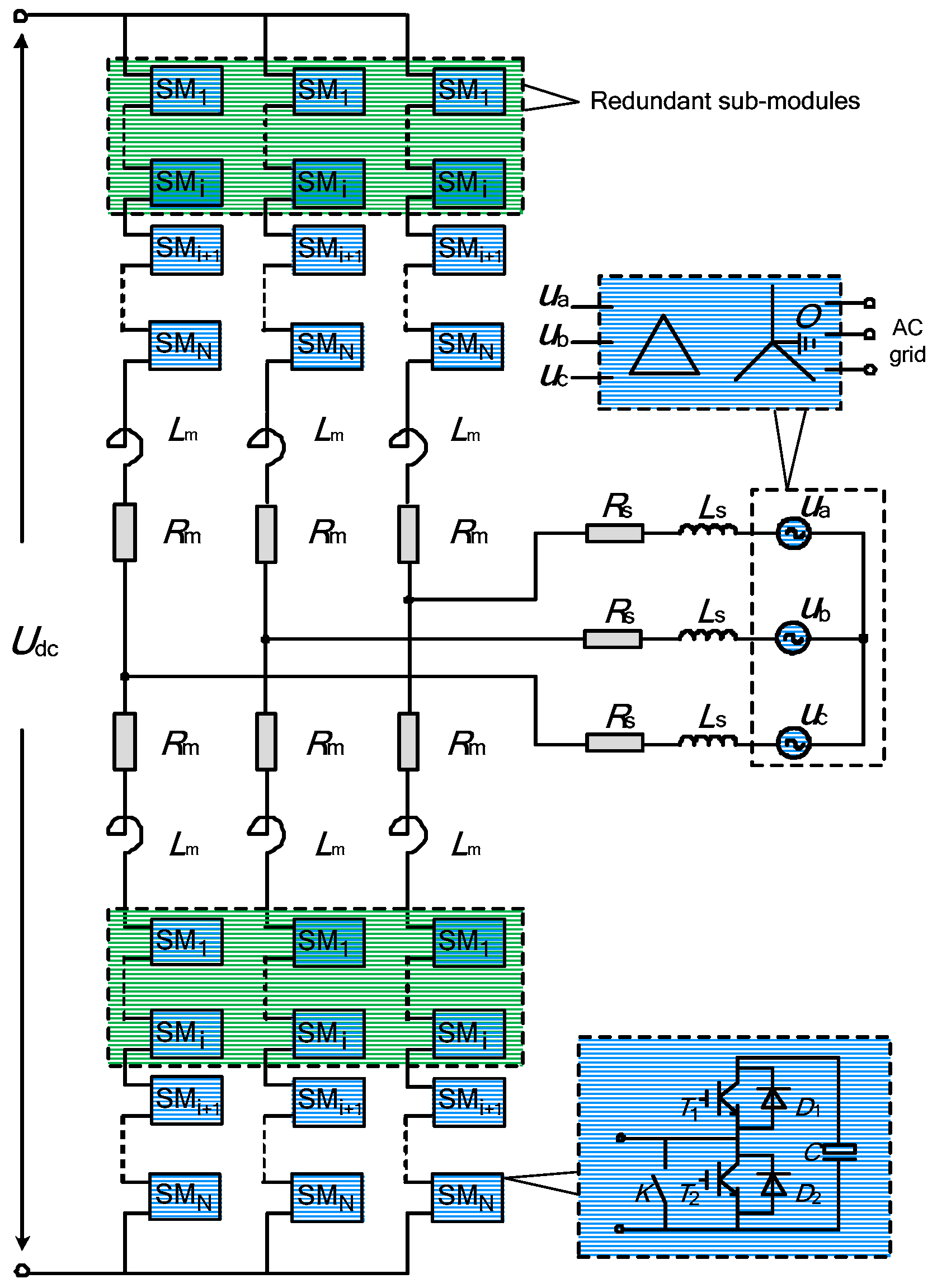

2. Basics Principles of MMC

2.1. MMC Topology

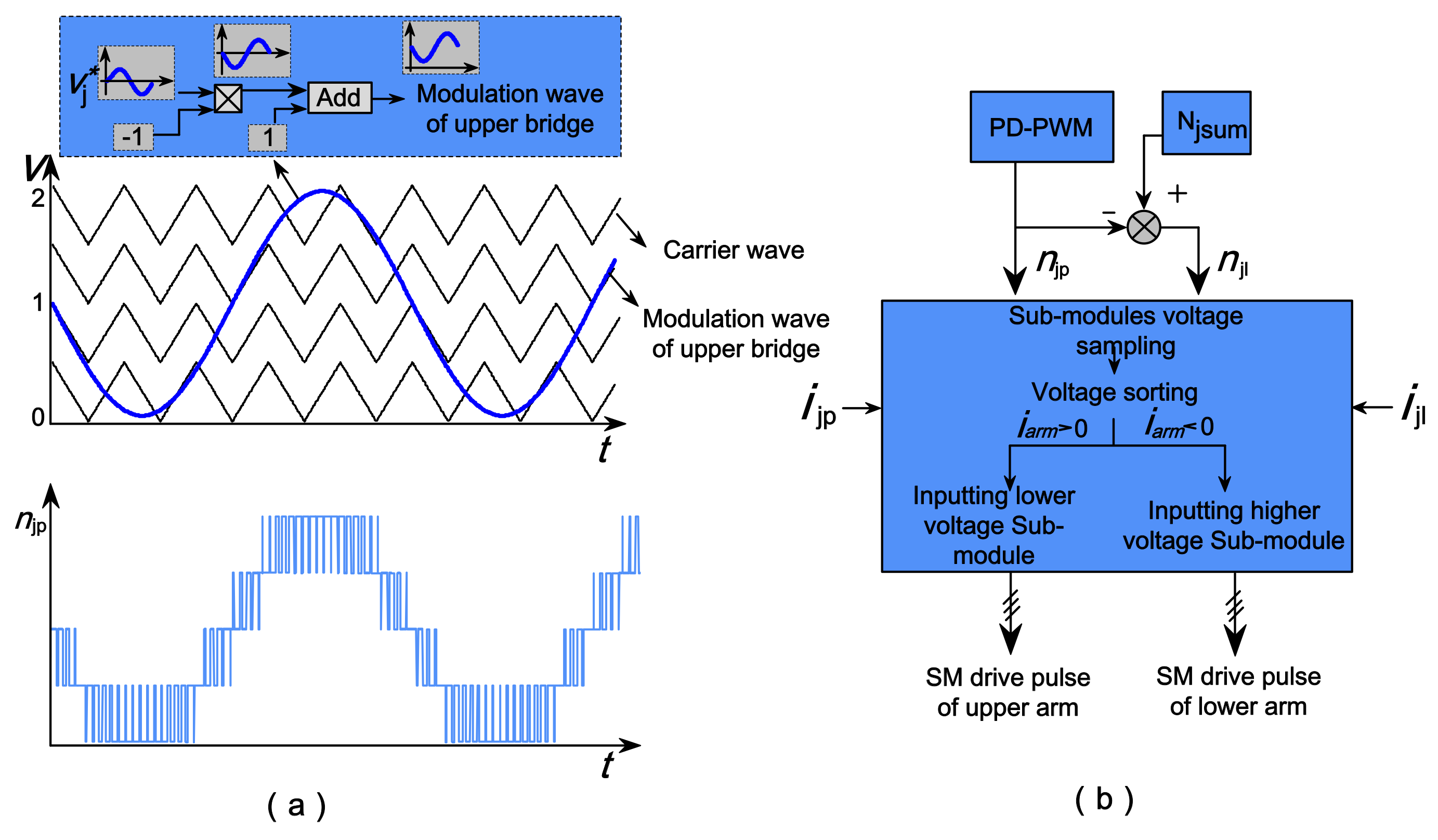

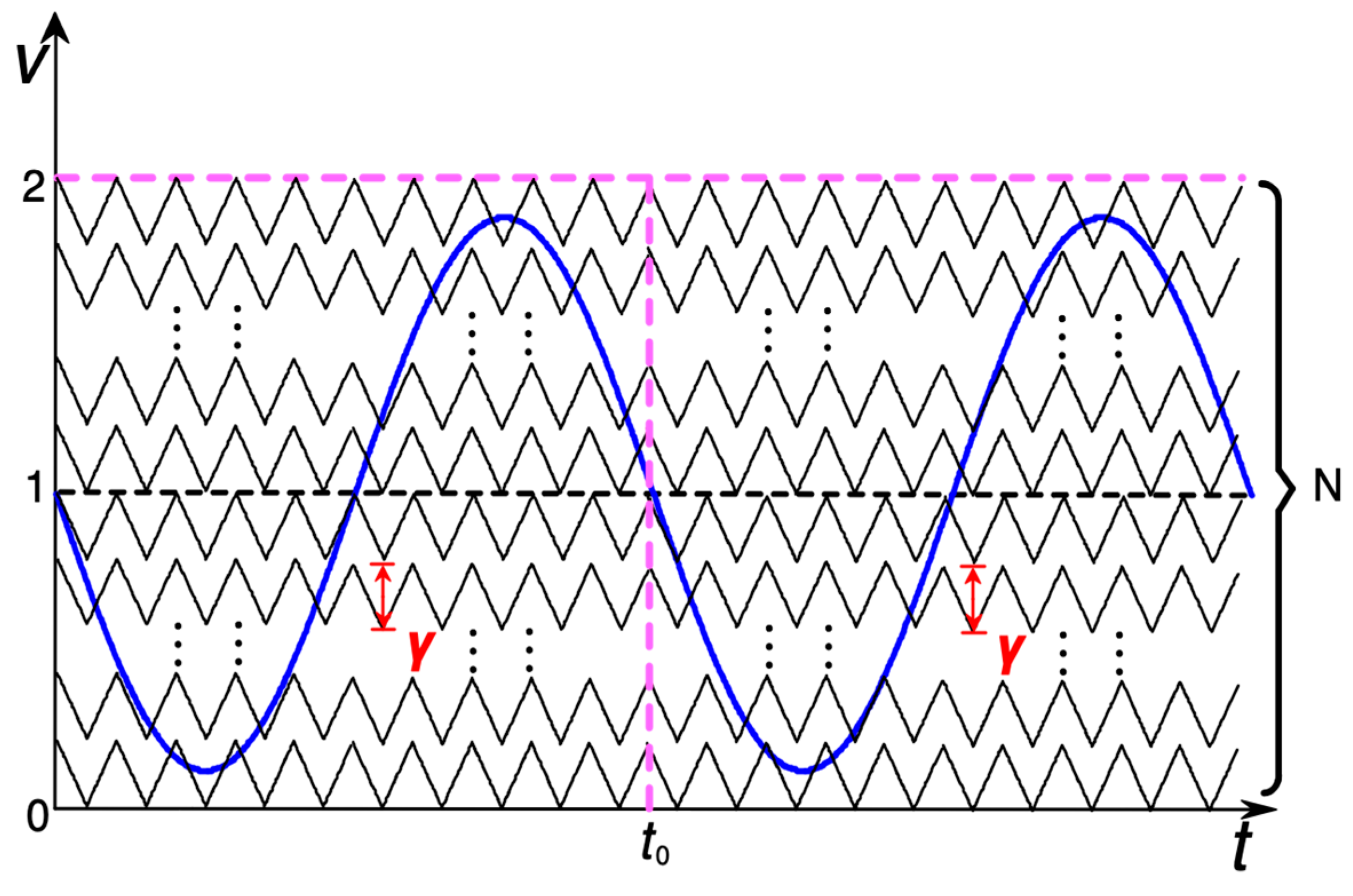

2.2. Phase Disposition PWM and Voltage Balancing Strategy

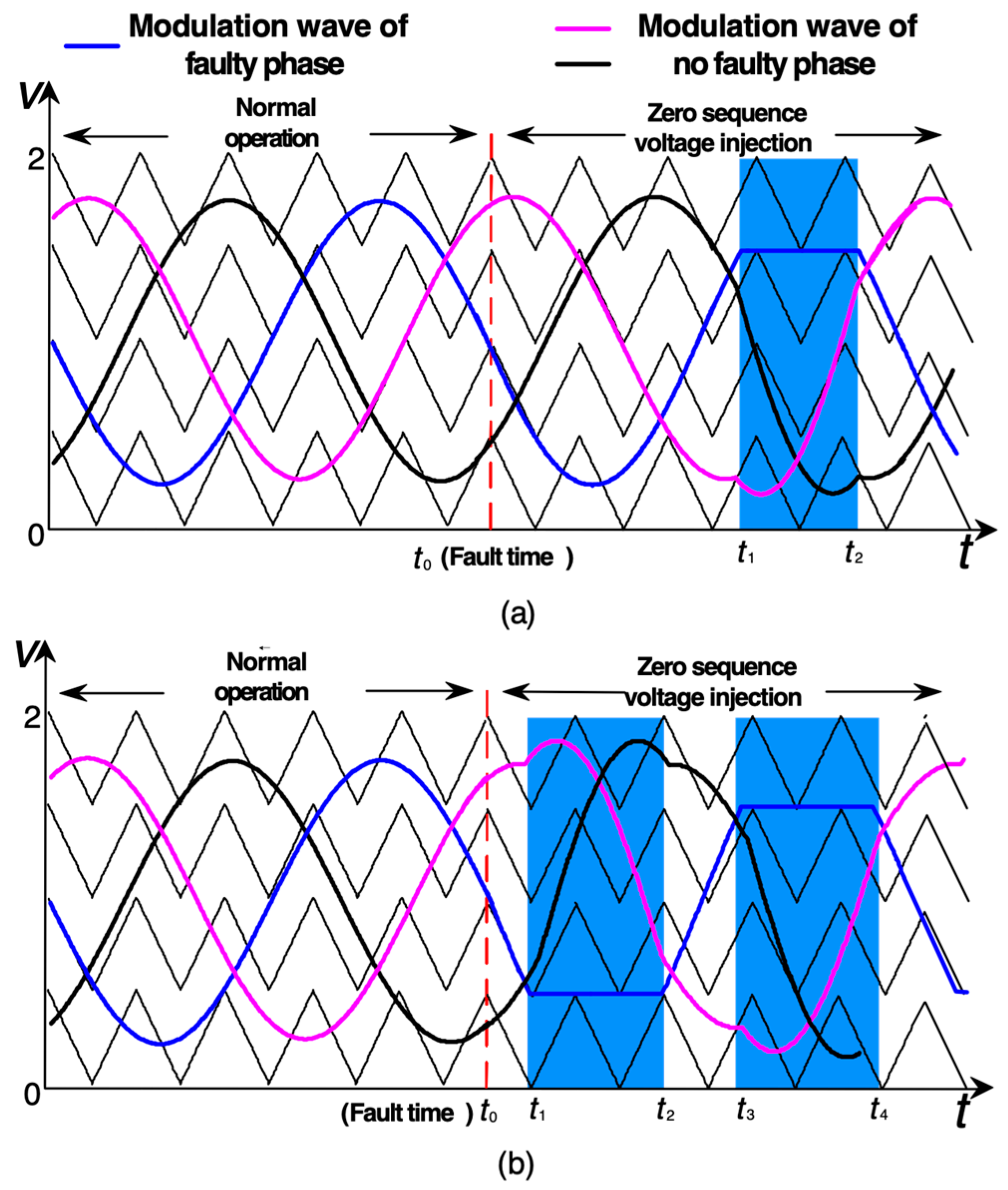

3. Analysis of the Traditional Zero-Sequence Voltage Injection Control Method

4. Novel Fault-Tolerant Control Strategy

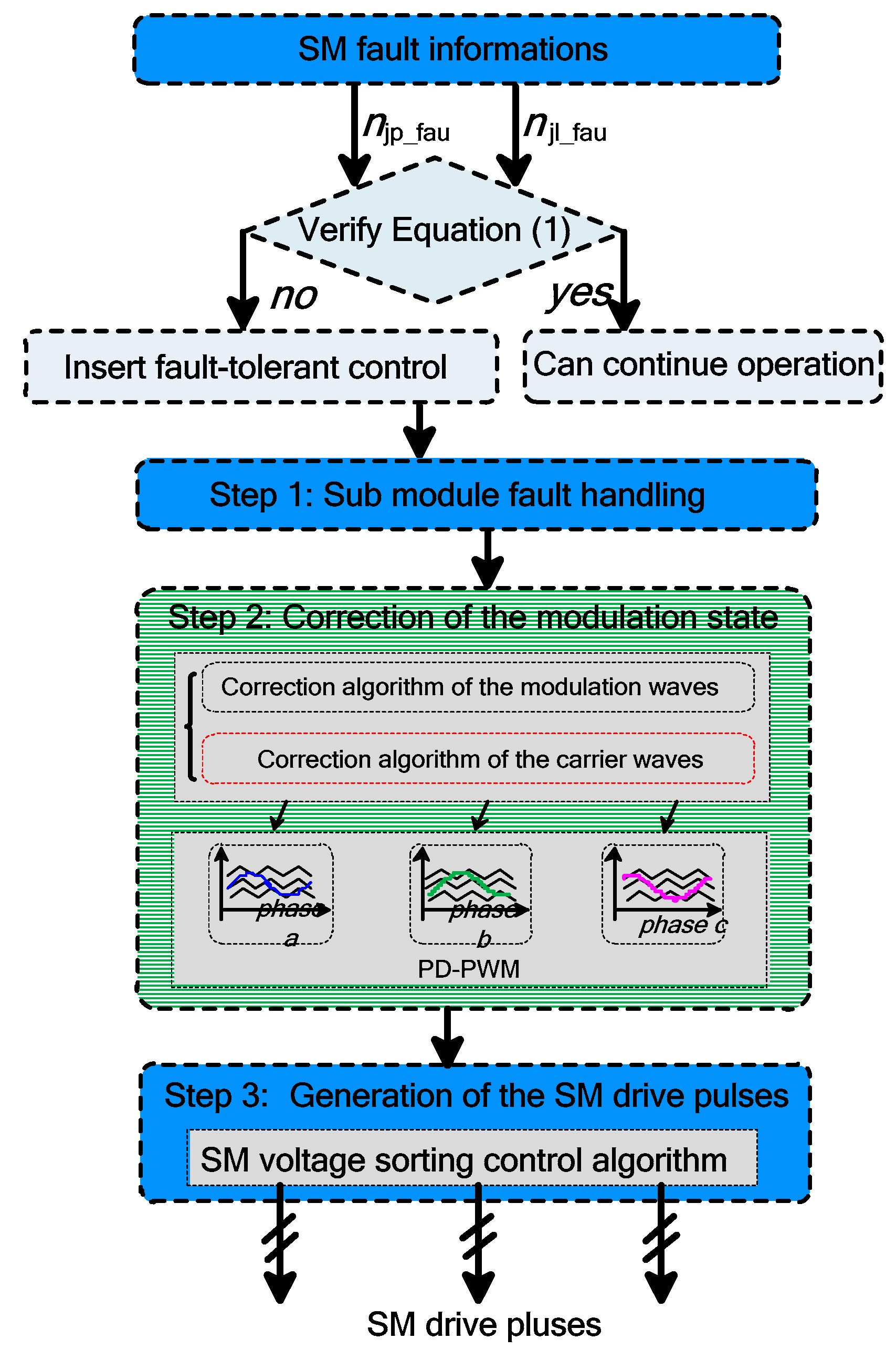

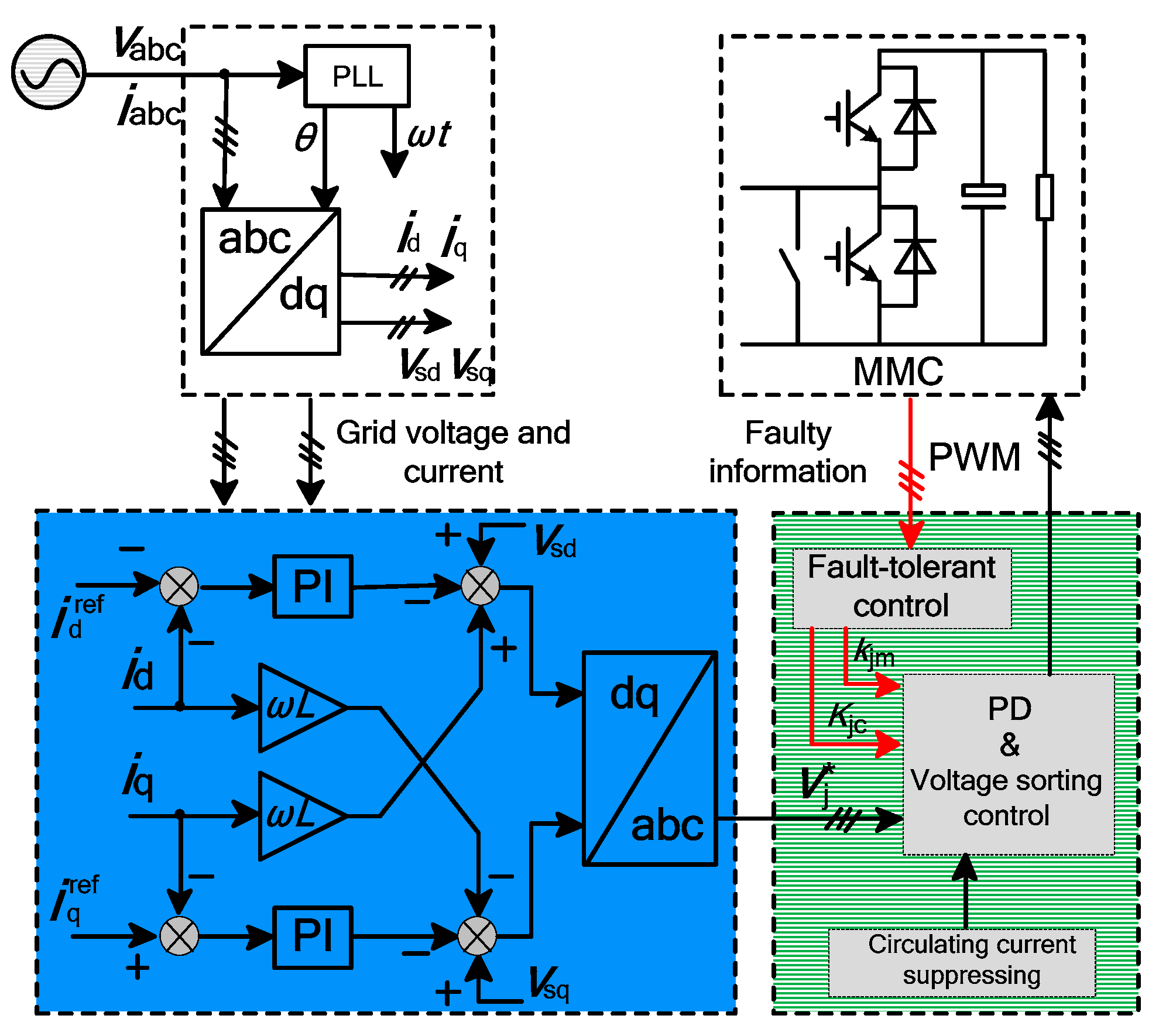

4.1. Overall Control Process of the Proposed Fault-Tolerant Control Strategy

- Sub module fault handling. Its main task is to block the trigger pulse of the faulty SMs and isolate the faulty SMs through closing the bypass switch.

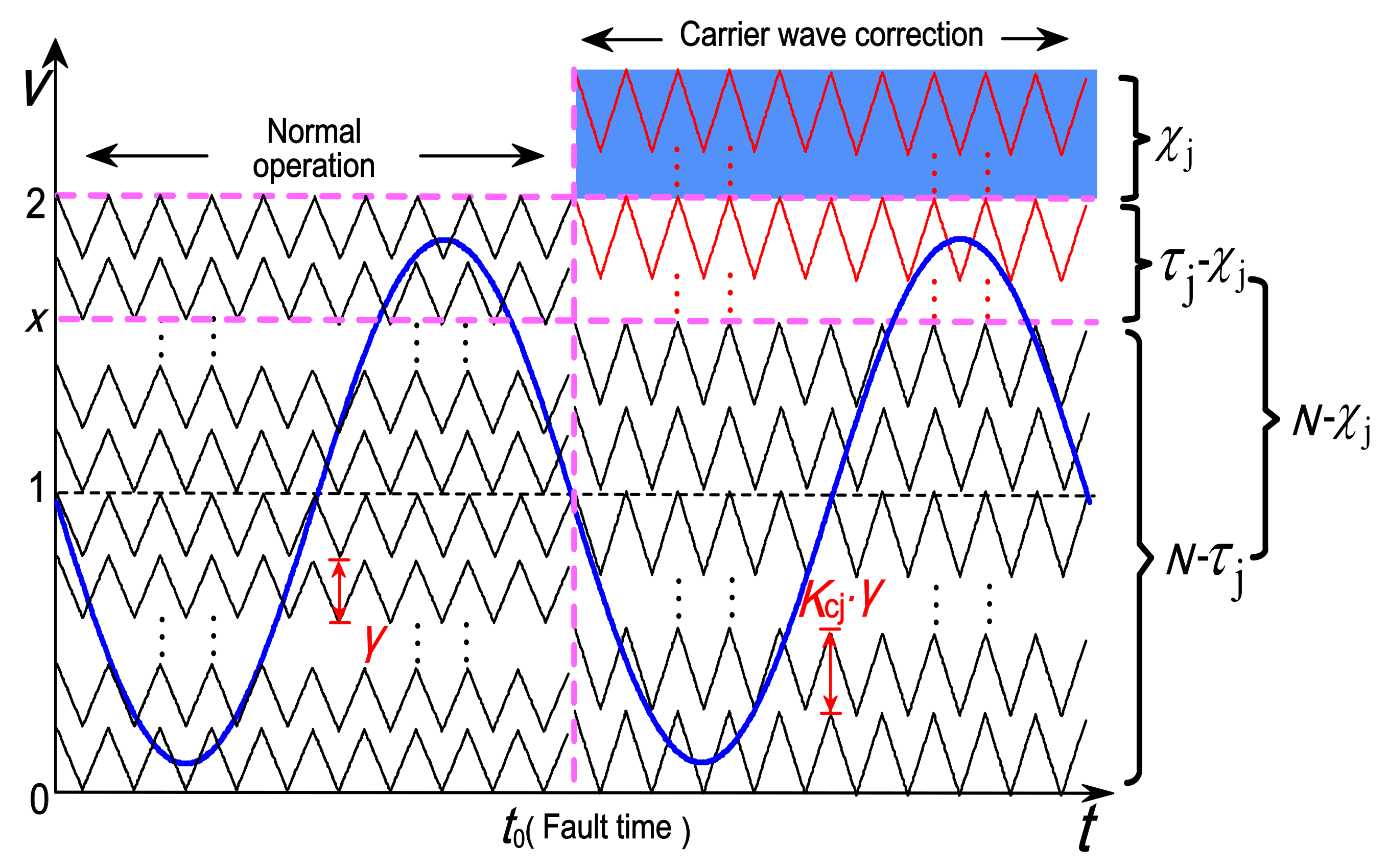

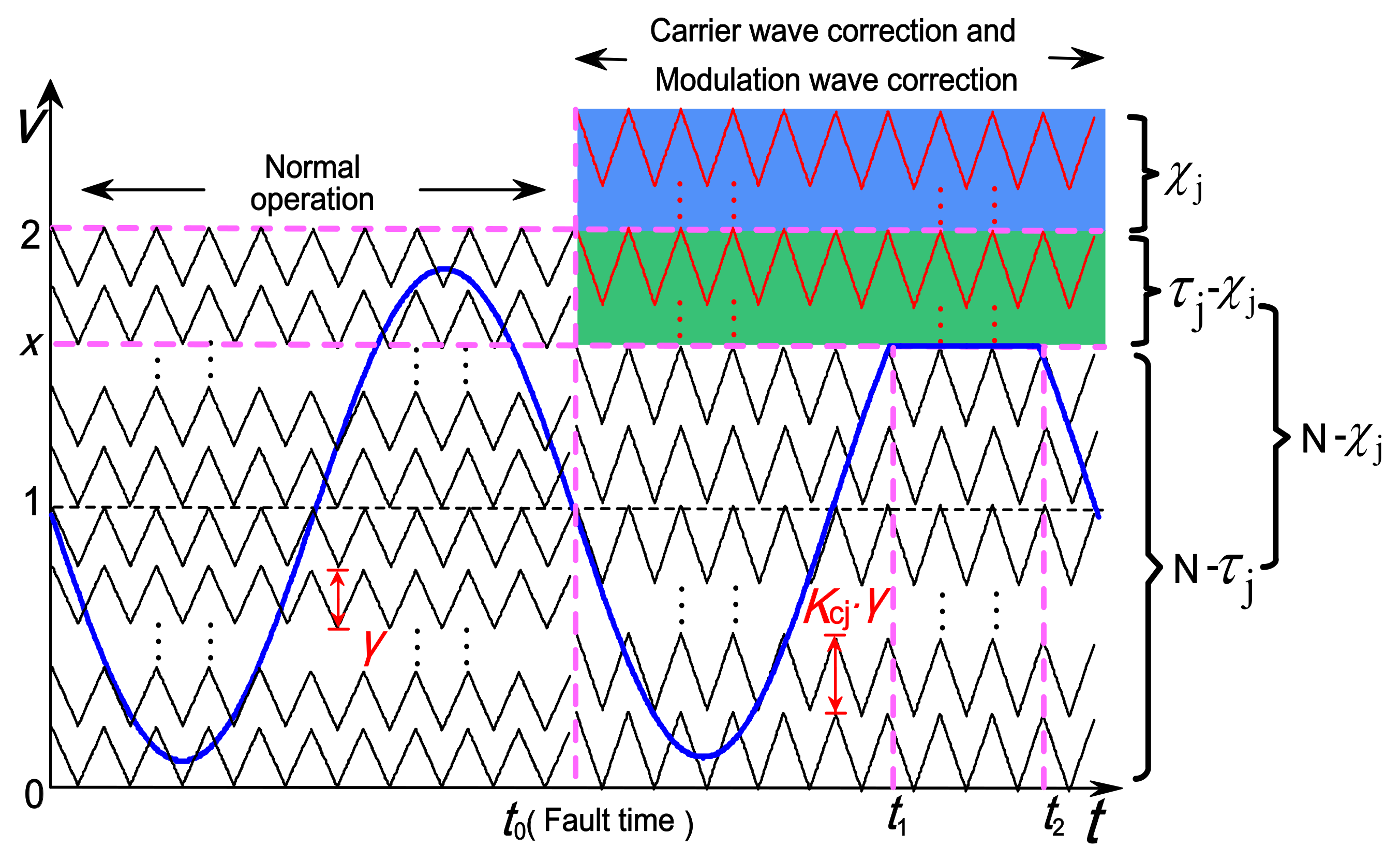

- Correction of the modulation state. The main task of this part is that with combining the faulty SM numbers of the fault phase, achieving the correction of the original carrier and modulation waves by adopting the proposed correction algorithm (where its specific implementation method will be discussed in detail in Section 4.2, thereby obtaining the SM numbers that need to be inserted in each arms after SMs malfunction.In addition, it should be note that this step is the also core part of the fault-tolerant control strategy. In the traditional zero-sequence voltage injection control method, it only with correcting the modulation waves to help achieve the SM fault-crossing. Compared to it, we add the correction algorithm of the carrier waves on the basis of the correction algorithm of the modulation waves, and realized their combination. This effectively simplifies the complexity of traditional control algorithm when deal with multiple arms occurring SM faults.

- Generation of the SM drive pulses. In this part, with combining the SM numbers that need to be inserted in each arms obtained from the step (2), the drive pulses of the remained healthy SMs are generated by using SM voltage sorting control algorithm, and finally completes the fault-tolerant control.

4.2. Specific Implementation Method of the Correction of the Carrier and Modulation Waves

4.2.1. Correction Algorithm of the Carrier Waves

4.2.2. Correction Algorithm of the Modulation Waves

4.3. Maximum Control Range of the Proposed Control Strategy

5. Simulation Studies

5.1. Case 1

5.2. Case 2

5.3. Case 3

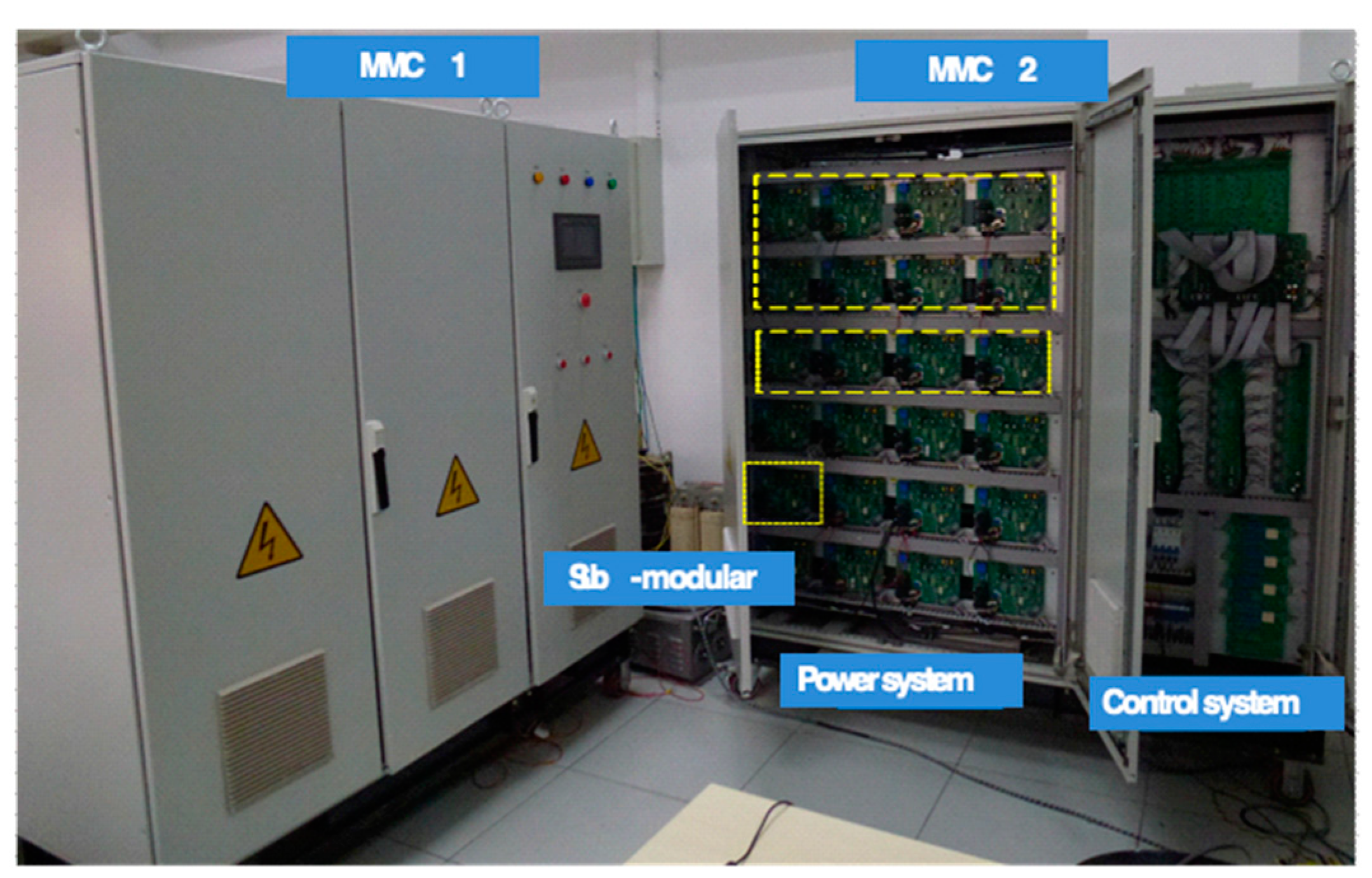

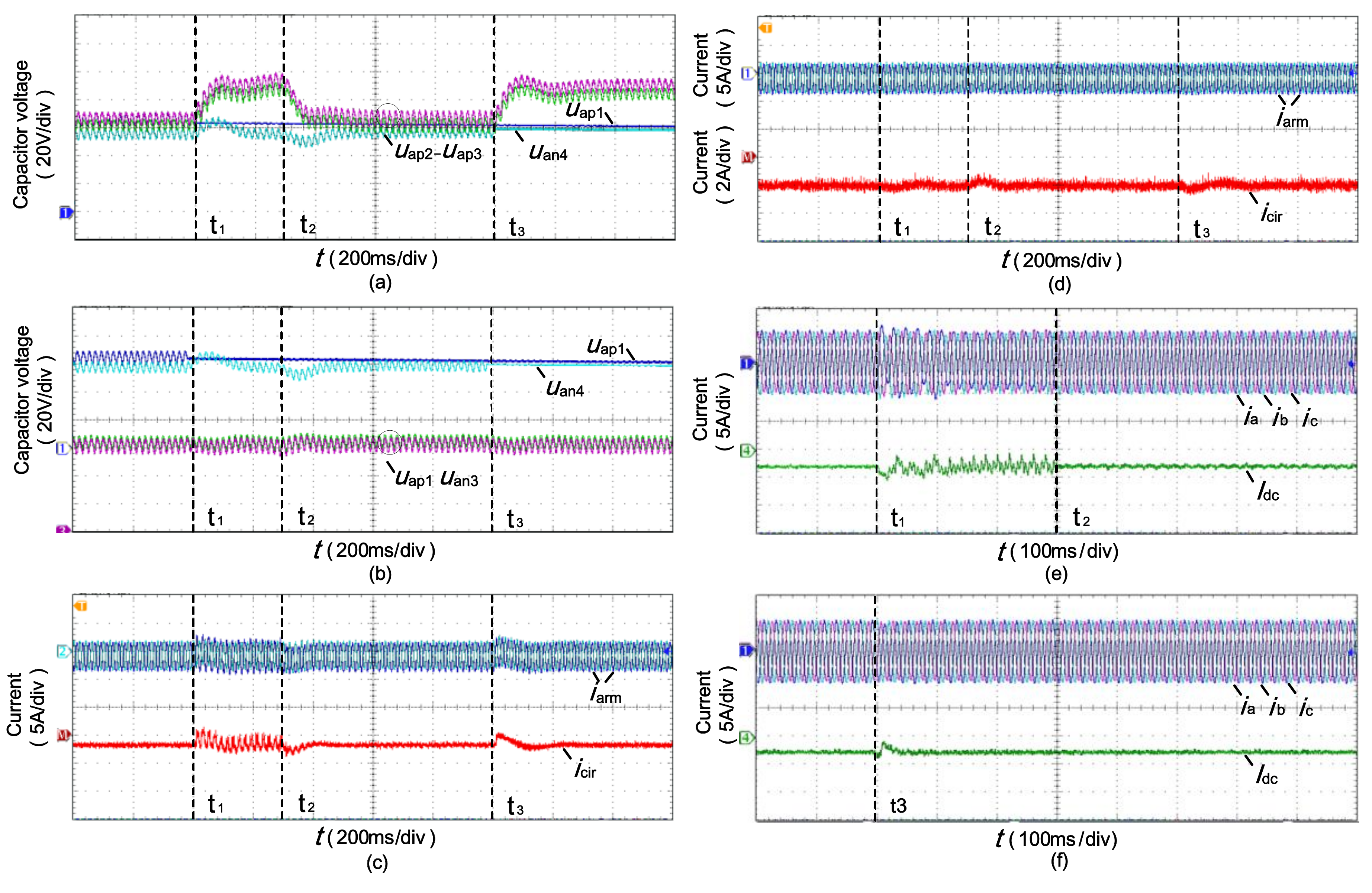

6. Experimental Studies

7. Conclusions

- (1)

- The traditional zero-sequence voltage injection fault-tolerant control algorithm is analyzed detailed. It reveals that the traditional method is easy to implement under the signal arm faulty state. However, if the SM simultaneously occurring faults in the upper and lower arms or appearing multiple arm failures, the required zero-sequence voltages will be calculated difficult. The SM fault-crossing is complicated to realize.

- (2)

- A novel fault-tolerant control strategy based on PD-PWM is proposed, which has three main benefits: (i) it has carrier and modulation wave dual correction mechanism, which control ability is more higher and flexible; (ii) it only needs to inject zero-sequence voltage in half a cycle of the modulation wave, which simplifies the complexity of traditional zero-sequence voltage injection control algorithms and much easier for implement; (iii) furthermore, the zero-sequence voltage can even be avoided injecting under the symmetrical fault conditions.

- (3)

- The simulations in the MATLAB/SIMULINK and experiments with 2-terminal a MMC-based prototype are all studied with the proposed control strategy under different fault conditions. The results confirm the efficiency of the control strategy.

Author Contributions

Acknowledgments

Conflicts of Interest

Appendix A

References

- Popova, L.; Pyrhonen, J.; Ma, K.; Blaabjerg, F. Device loading of modular multilevel converter MMC in wind power application. In Proceedings of the 2014 International Power Electronics Conference (IPEC-Hiroshima 2014—ECCE-ASIA), Hiroshima, Japan, 18–21 May 2014; pp. 548–554. [Google Scholar]

- Gowaid, I.A.; Adam, G.P.; Ahmed, S.; Holliday, D.; Williams, B.W. Analysis and design of a modular multilevel converter with trapezoidal modulation for medium and high voltage DC-DC transformers. IEEE Trans. Power Electron. 2015, 30, 5439–5457. [Google Scholar] [CrossRef]

- Perez, M.A.; Bernet, S.; Rodriguez, J.; Kouro, S.; Lizana, R. Circuit topologies, modeling, control schemes, and applications of modular multilevel converters. IEEE Trans. Power Electron. 2018, 30, 4–17. [Google Scholar] [CrossRef]

- Nami, A.; Liang, J.; Dijkhuizen, F.; Demetriades, G. Modular multilevel converters for HVDC applications: Review on converter cells and functionalities. IEEE Trans. Power Electron. 2015, 30, 18–36. [Google Scholar] [CrossRef]

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the IEEE Bologna Power Tech Conference Proceedings, Bologna, Italy, 23–26 June 2003; pp. 23–26. [Google Scholar]

- Debnath, S.; Saeedifard, M. Simulation-based gradient-descent optimization of modular multilevel converter controller parameters. IEEE Trans Ind. Electron. 2016, 63, 102–112. [Google Scholar] [CrossRef]

- Li, Y.; Jiang, W.; Yu, S.; Zou, X. Design of zhoushan multi-terminal VSC-HVDC transmission project. High Voltage Eng. 2014, 40, 2490–2496. [Google Scholar]

- Wu, W.; Wu, X.; Yin, J.; Jing, L.; Wang, S.; Li, J. Characteristic analysis and fault-tolerant control of circulating current for modular multilevel converters under SM faults. Energies 2017, 10, 1827. [Google Scholar] [CrossRef]

- Abdelsalam, M.; Tennakoon, S.; Griffiths, A.L.; Marei, M. Investigation of sub-module fault types of modular multi-level converters in HVDC networks. In Proceedings of the International Universities Power Engineering Conference (UPEC), Stoke, UK, 1–4 September 2015; pp. 1–6. [Google Scholar]

- Jiang, W.; Wang, C.; Wang, M. Fault detection and remedy of multilevel inverter based on BP neural network. In Proceedings of the Asia-Pacific Power and Energy Engineering Conference (APPEEC), Shanghai, China, 27–29 March 2012; pp. 1–4. [Google Scholar]

- Moon, J.W.; Kim, C.S.; Park, J.W. Circulating current control in MMC under the unbalanced voltage. IEEE Trans. Power Deliv. 2013, 28, 1952–1959. [Google Scholar] [CrossRef]

- Son, G.; Lee, H.J.; Nam, T. Design and control of a modular multilevel HVDC converter with redundant power modules for noninterruptible energy transfer. IEEE Trans. Power Deliv. 2012, 27, 1611–1619. [Google Scholar]

- Konstantinou, G.; Pou, J.; Ceballos, S. Active redundant sub-module configuration in modular multilevel converters. IEEE Trans. Power Deliv. 2013, 28, 2333–2341. [Google Scholar] [CrossRef]

- Liu, G.; Xu, Z.; Xue, Y. Optimized control strategy based on dynamic redundancy for the modular multilevel converter. IEEE Trans. Power Electron. 2015, 30, 339–348. [Google Scholar] [CrossRef]

- Li, S.; Wang, Z.; Wang, G. Fluctuation volt age control and fault-tolerant operation of modular multilevel converters with zero-sequence injection. Int. Trans. Electr. Energy Syst. 2014, 24, 944–959. [Google Scholar] [CrossRef]

- Hu, P.; Jiang, D.; Zhou, Y. Energy-balancing control strategy for modular multilevel converters under submodule Fault Conditions. IEEE Trans. Power Electron. 2014, 29, 5021–5029. [Google Scholar] [CrossRef]

- Peter, W. Enhancing the reliability of modular medium-voltage drives. IEEE Trans Ind. Electron. 2002, 49, 948–954. [Google Scholar]

- Jose, R.; Peter, W.; Jorge, P.; Rodrigo, M.; Maria, J. Operation of a medium-voltage drive under faulty conditions. IEEE Trans Ind. Electron. 2005, 52, 1080–1085. [Google Scholar]

- Pablo, L.; Gabriel, O. Extended operation of cascade multicell converters under fault condition. IEEE Trans Ind. Electron. 2009, 56, 2697–2703. [Google Scholar]

- Fernanda, C.; Humberto, P.; Cassiano, R. Generalized carrier-based modulation strategy for cascaded multilevel converters operating under fault conditions. IEEE Trans. Ind. Electron. 2012, 59, 679–689. [Google Scholar]

- Yang, Q.; Qin, J. A post-fault strategy to control the modular multilevel converter under submodule failure. IEEE Trans. Power Deliv. 2012, 27, 1538–1547. [Google Scholar]

- Shen, K.; Xiao, B.; Mei, J. A modulation reconfiguration based fault-tolerant control scheme for modular multilevel converters. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–31 March 2013; pp. 3251–3255. [Google Scholar]

- Yang, W.; Song, Q.; Xu, S.; Rao, H.; Liu, W. An MMC topology Based on unidirectional current H-bridge submodule with active circulating current injection. IEEE Trans. Power Electron. 2018, 33, 3870–3883. [Google Scholar] [CrossRef]

- Ning, L.; Venkata, D. Dynamic electro-magnetic-thermal modeling of MMC-based DC–DC converter for real-time simulation of MTDC grid. IEEE Trans. Power Deliv. 2018, 33, 1337–1347. [Google Scholar]

- Xu, J.; Penghao, Z.; Zhao, C. Reliability analysis and redundancy configuration of MMC with hybrid submodule topologies. IEEE Trans. Power Electron. 2016, 31, 2720–2729. [Google Scholar] [CrossRef]

- Lu, C. Research on the Control Strategy of Modular Multilevel Converter; China University of Ming and Technology: Beijing, China, 2014. [Google Scholar]

- Wang, D.; Yang, J.; Chen, Z.; Mao, C.; Lu, J. A Transformerless medium voltage multiphase motor drive system. Energies 2016, 9, 323. [Google Scholar] [CrossRef]

- Meshram, P.M.; Borghate, V.B. A Novel Voltage Balancing Method of Modular Multilevel Converter (MMC). In Proceedings of the International Conference on Energy, Automation and Signal, Bhubaneswar, Odisha, India, 28–30 December 2011; pp. 1–5. [Google Scholar]

- Li, J.; Jin, X.; Wu, X. Analysis of Fault Circulating current without redundant SM and its suppression strategy. Power Syst. Technol. 2016, 40, 32–39. [Google Scholar]

| Parameters | Value |

|---|---|

| Ac system nominal voltage | 10 kV |

| Ac System inductance Ls | 5 mH |

| Fundamental frequency | 50 Hz |

| Ac system power losses Rs | 0.03 Ω |

| Arm inductance Lm | 5 mH |

| Series arm resistance Rm | 0.01 Ω |

| Dc bus voltage Udc | 20 kV |

| Number of SMs per arm N | 20 |

| Number of redundant SMs per arm | 5 |

| Sub-module capacitor C | 2000 μF |

| Transformer ratio | 1:1 (Y/Δ) |

| Parameters | Value |

|---|---|

| AC System inductance Ls | 5 mH |

| Arm inductance Lm | 5 mH |

| DC bus voltage Udc | 20 kV |

| Number of SMs per arm N | 4 |

| Number of redundant SMs per arm | 1 |

| Sub-module capacitor C | 2000 μF |

| Transformer ratio | 380 V/380 V (Y/Δ) |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yin, J.; Wu, W.; Wei, T.; Wu, X.; Huo, Q. A Novel Fault-Tolerant Control of Modular Multilevel Converter under Sub-Module Faults Based on Phase Disposition PWM. Energies 2019, 12, 20. https://doi.org/10.3390/en12010020

Yin J, Wu W, Wei T, Wu X, Huo Q. A Novel Fault-Tolerant Control of Modular Multilevel Converter under Sub-Module Faults Based on Phase Disposition PWM. Energies. 2019; 12(1):20. https://doi.org/10.3390/en12010020

Chicago/Turabian StyleYin, Jingyuan, Wen Wu, Tongzhen Wei, Xuezhi Wu, and Qunhai Huo. 2019. "A Novel Fault-Tolerant Control of Modular Multilevel Converter under Sub-Module Faults Based on Phase Disposition PWM" Energies 12, no. 1: 20. https://doi.org/10.3390/en12010020

APA StyleYin, J., Wu, W., Wei, T., Wu, X., & Huo, Q. (2019). A Novel Fault-Tolerant Control of Modular Multilevel Converter under Sub-Module Faults Based on Phase Disposition PWM. Energies, 12(1), 20. https://doi.org/10.3390/en12010020