A Highly Efficient Single-Phase Three-Level Neutral Point Clamped (NPC) Converter Based on Predictive Control with Reduced Number of Commutations

Abstract

:1. Introduction

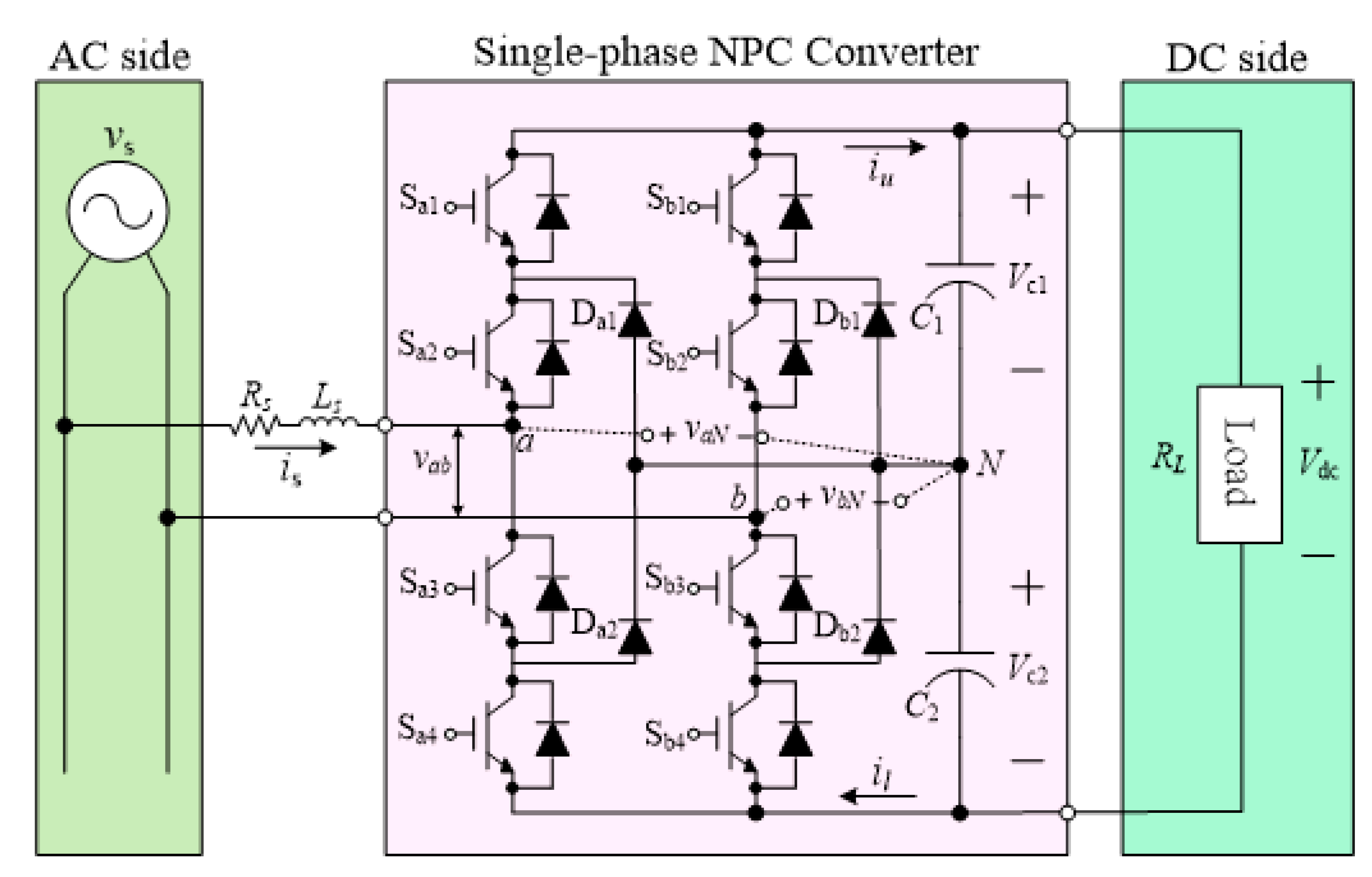

2. Single-Phase Three-Level NPC Converter and Model Predictive Control Method

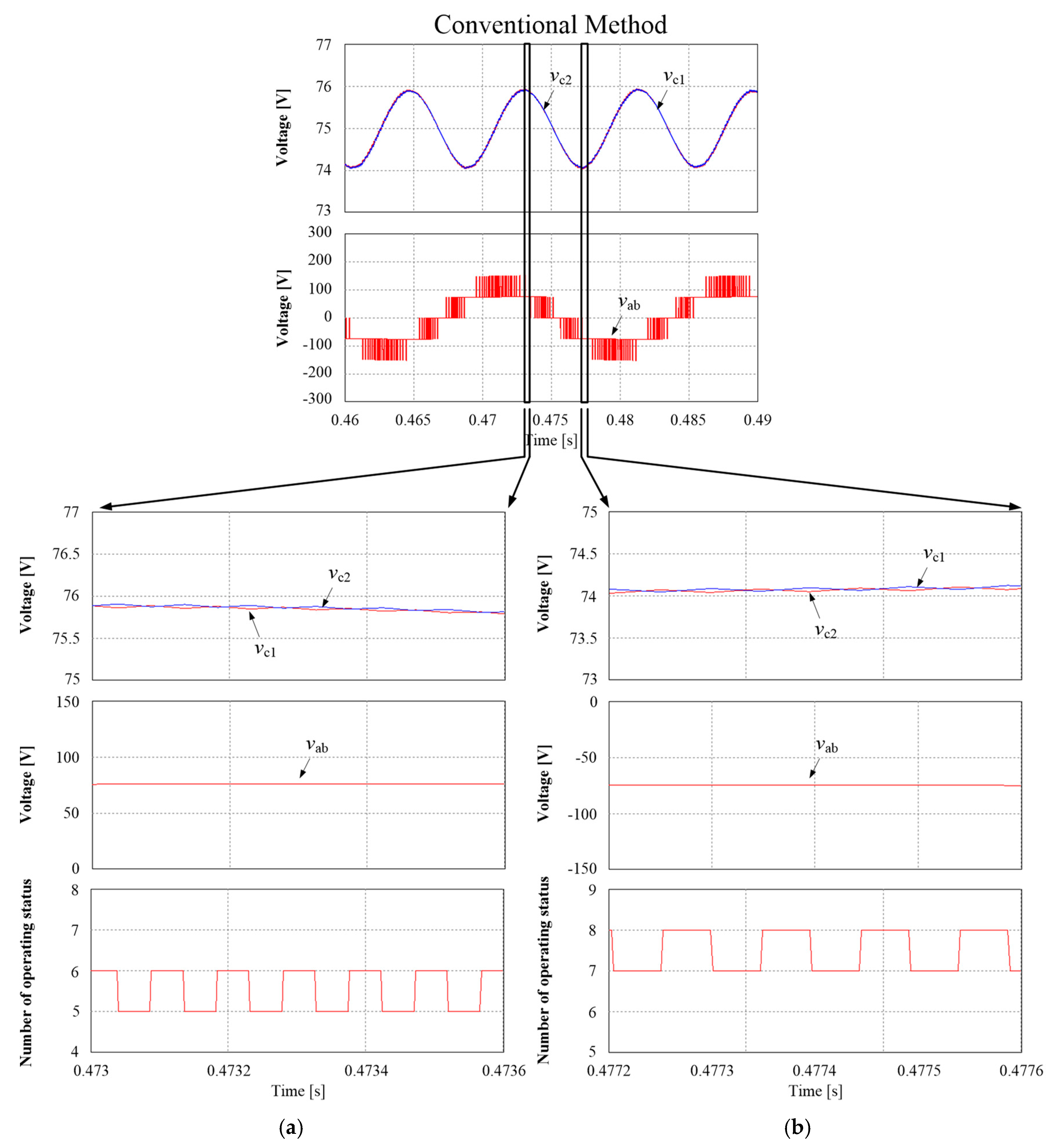

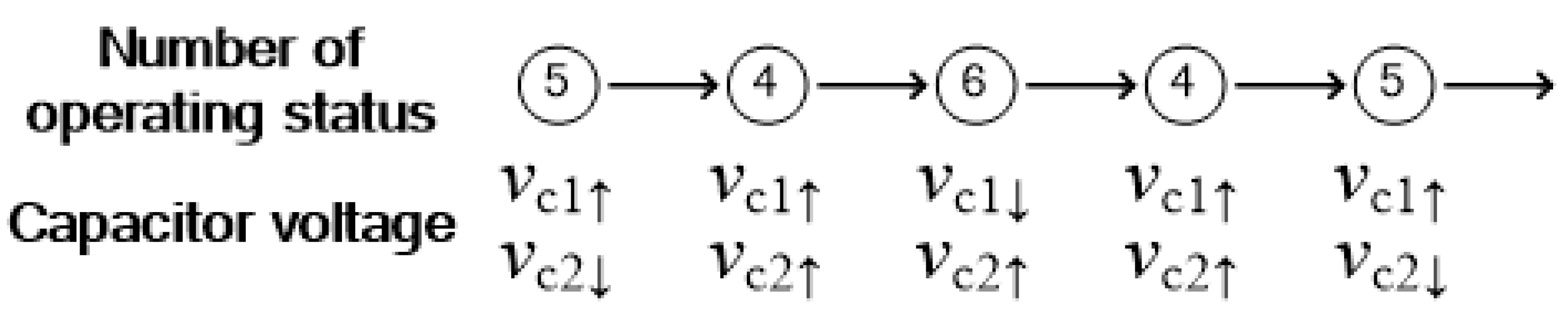

3. Proposed MPC Method Based on Voltage Tolerance Band

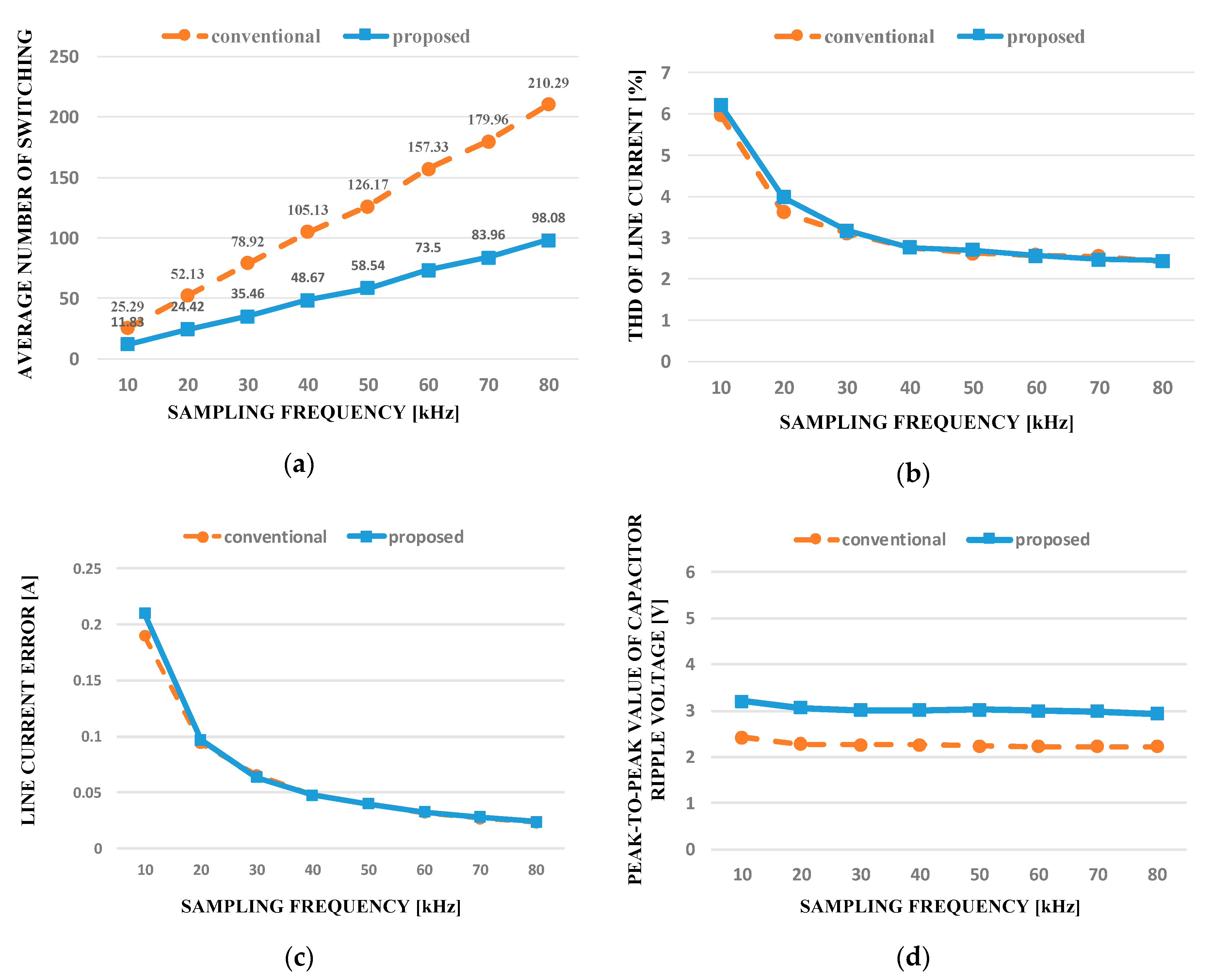

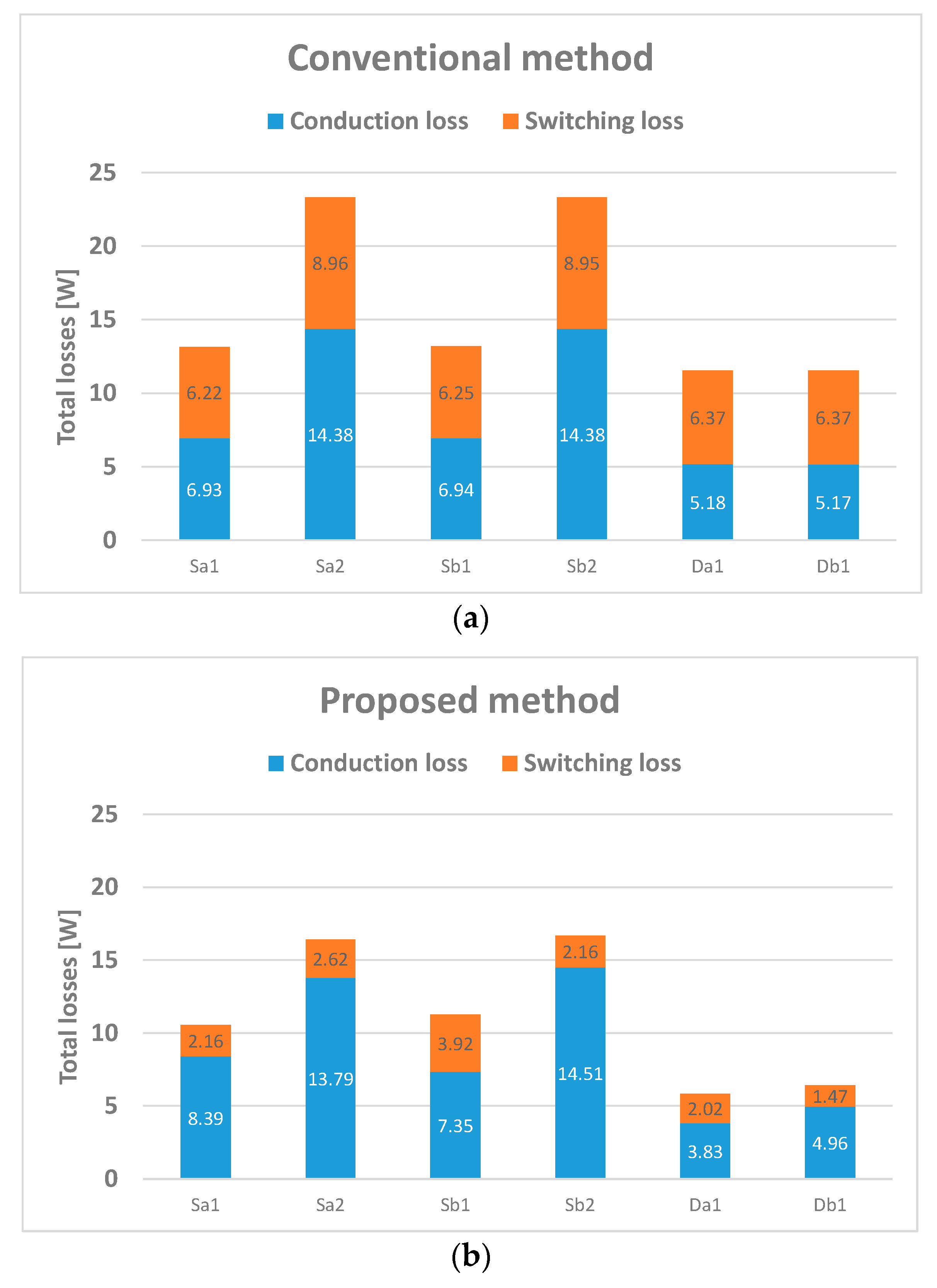

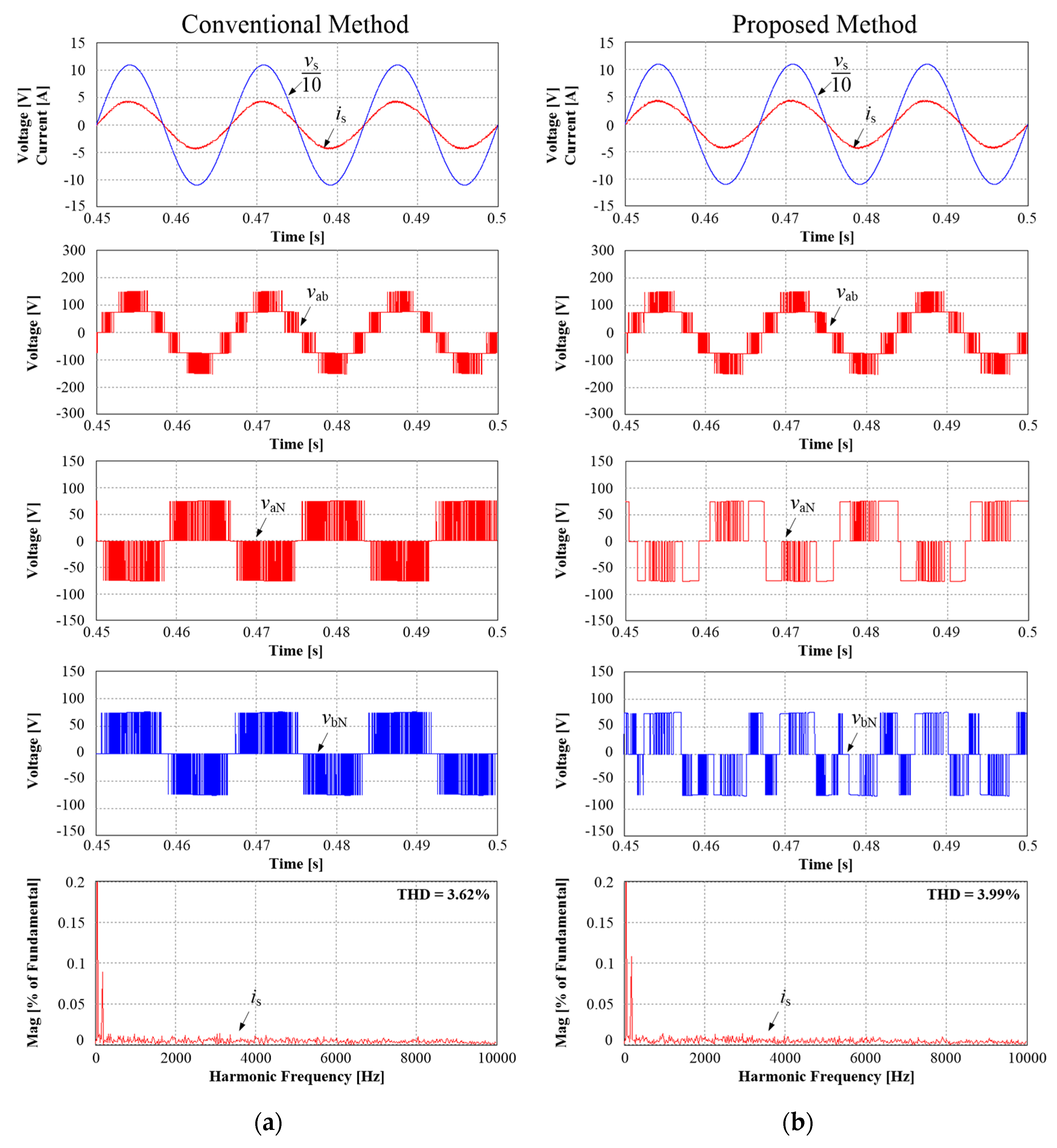

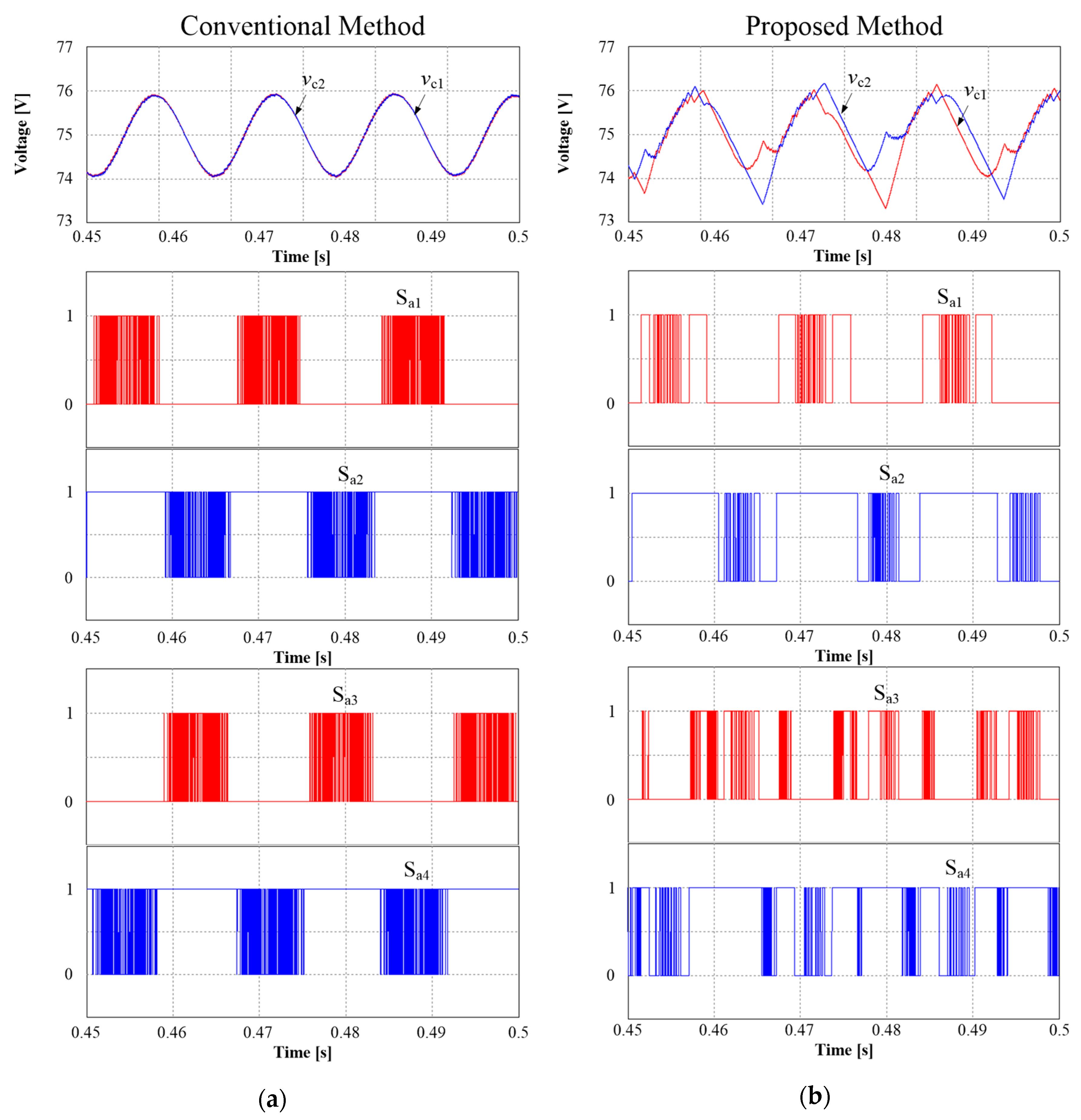

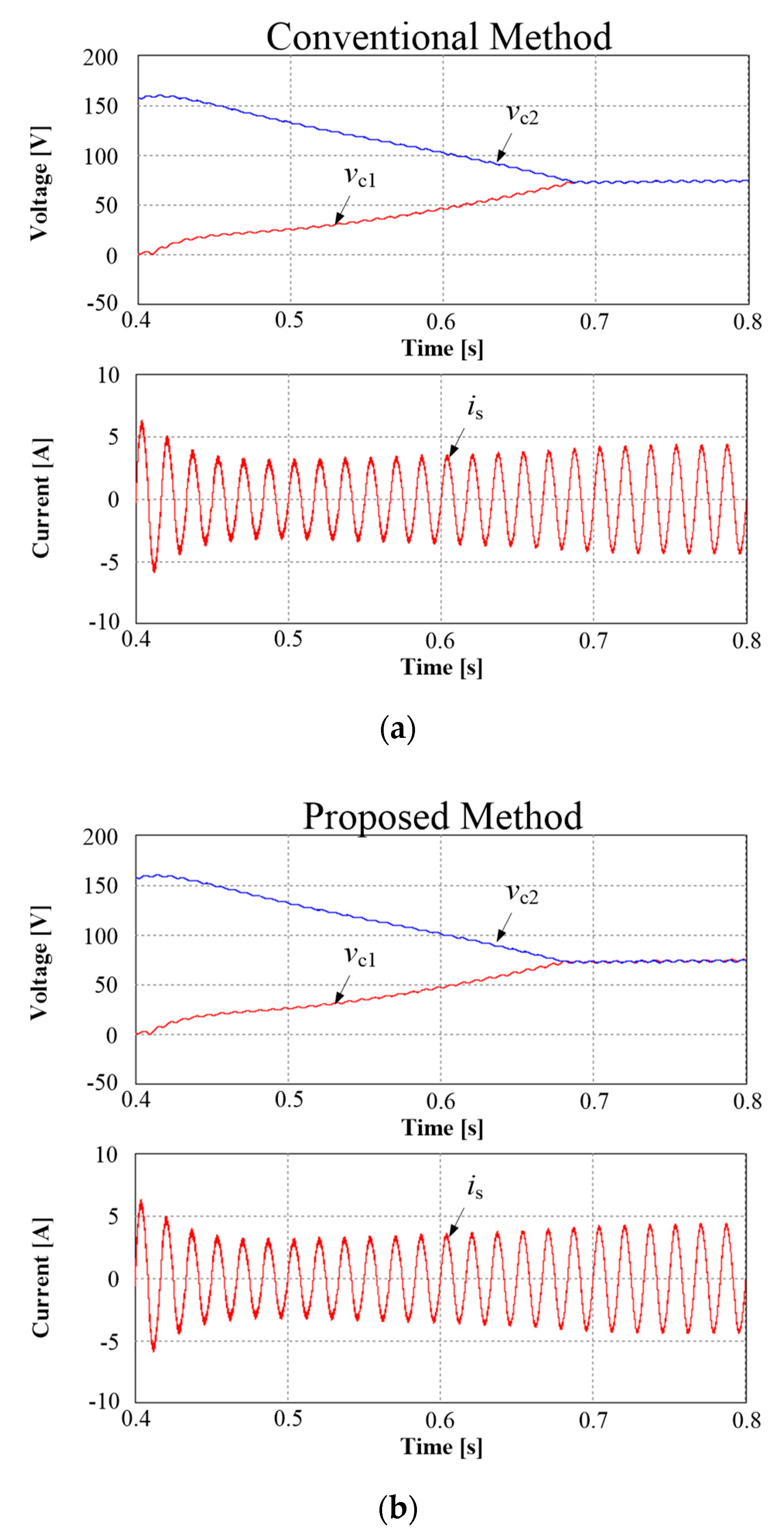

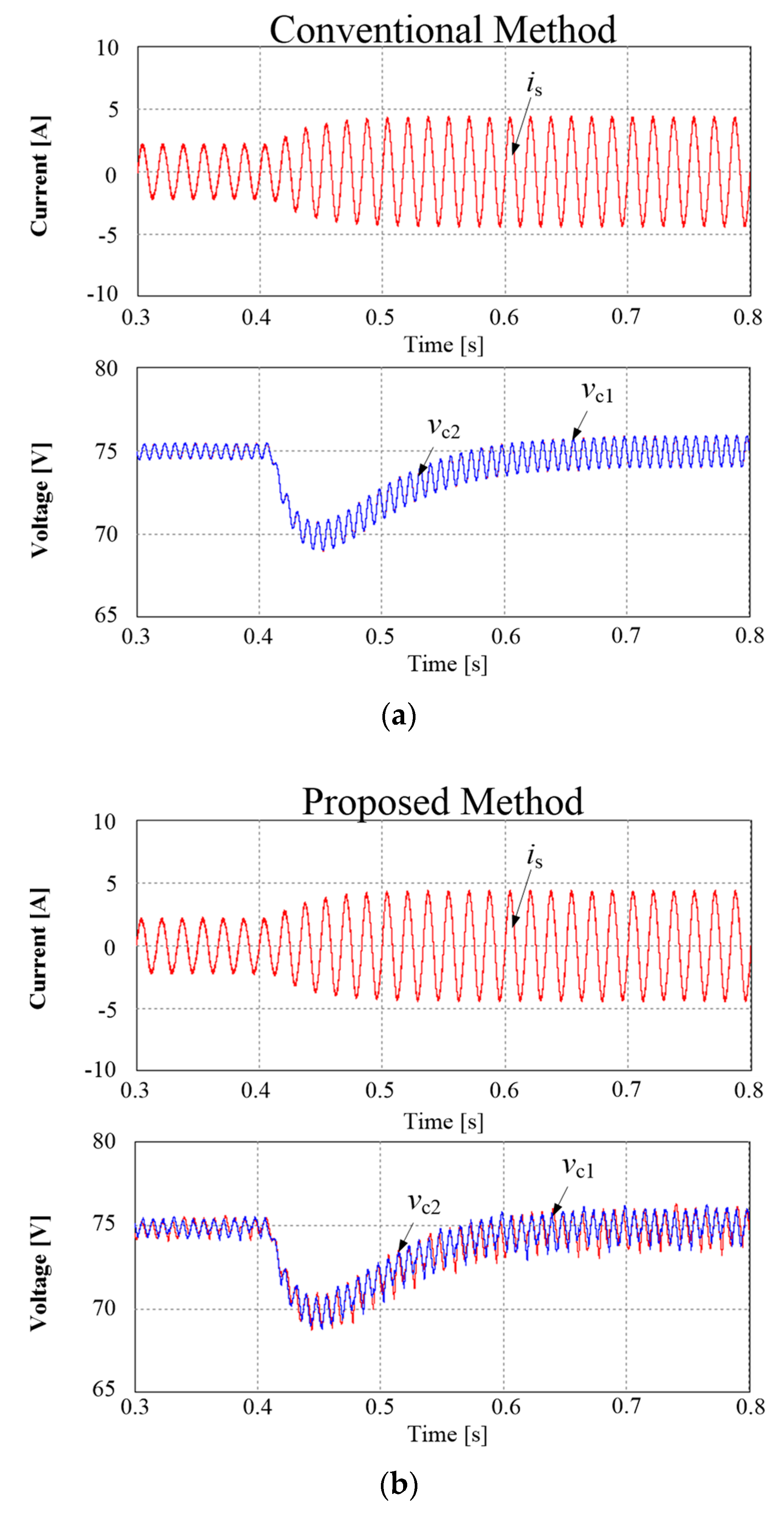

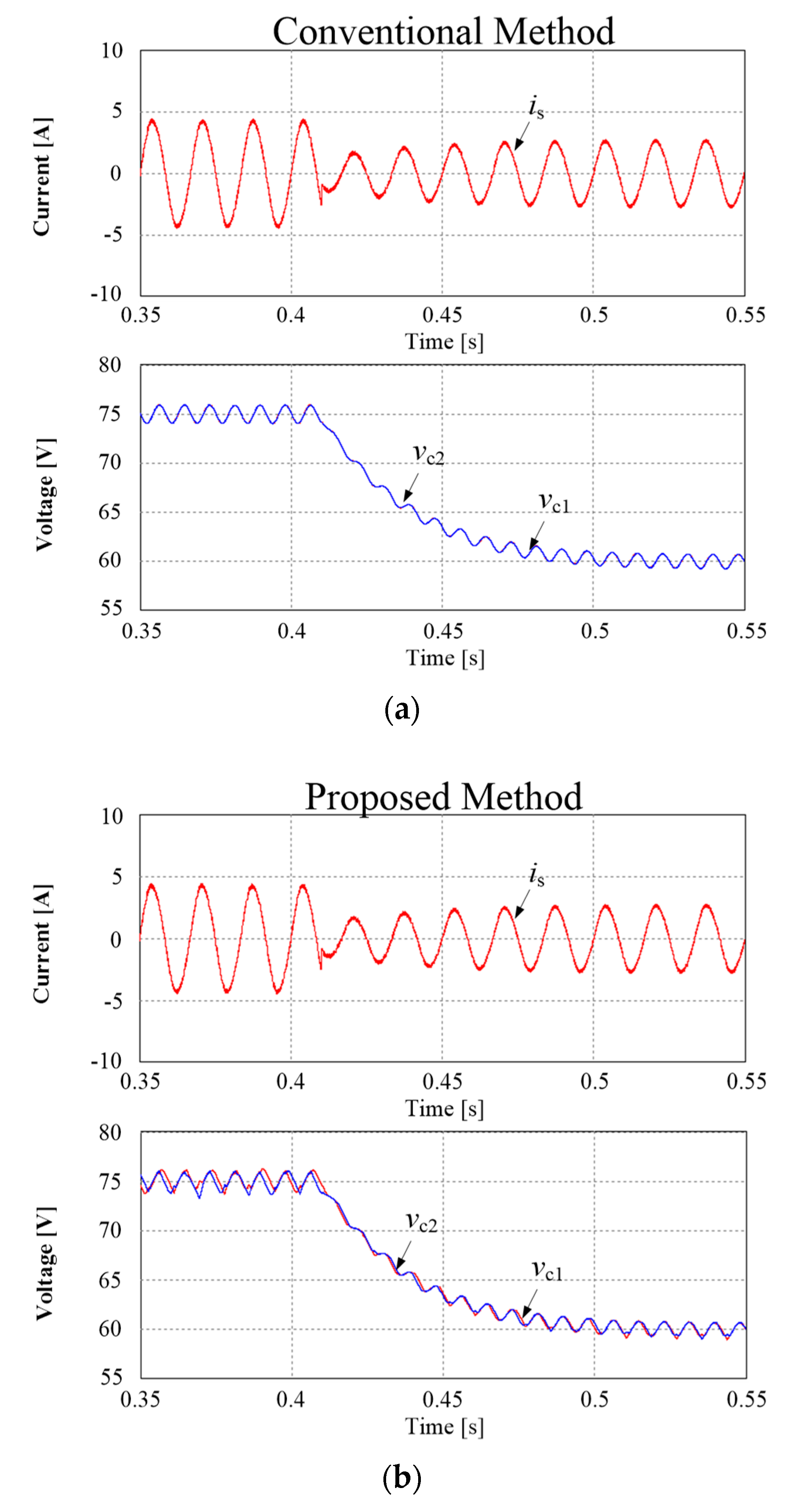

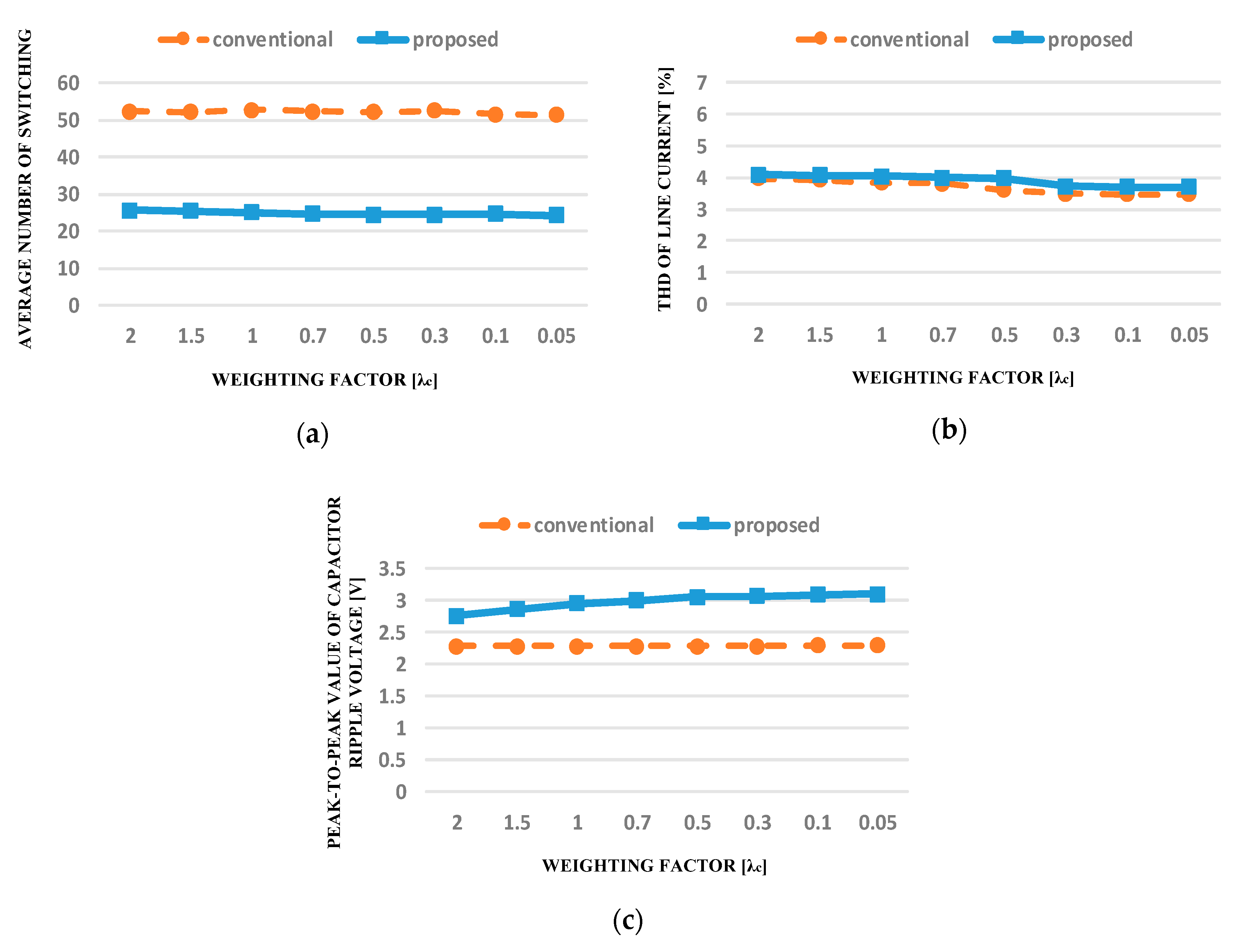

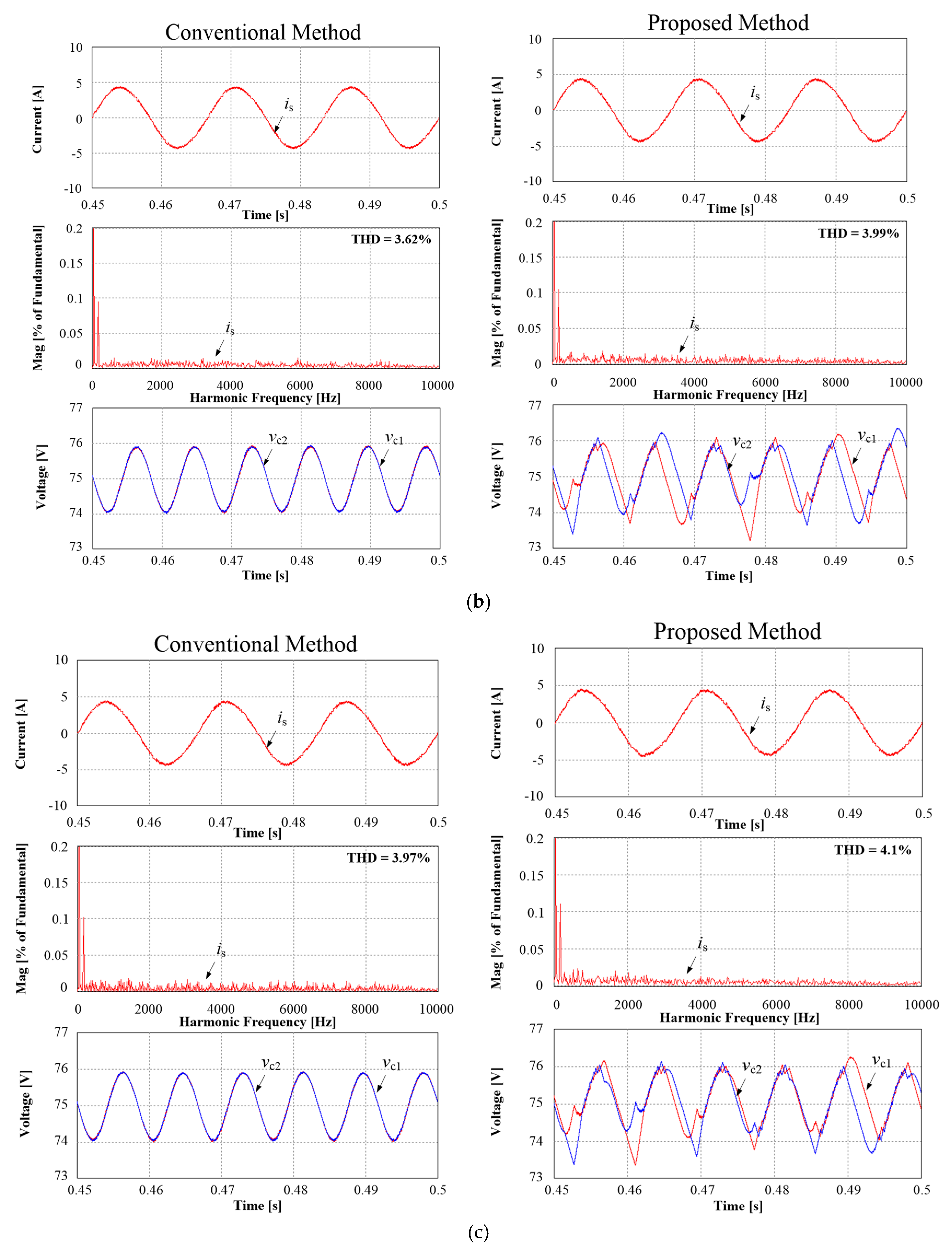

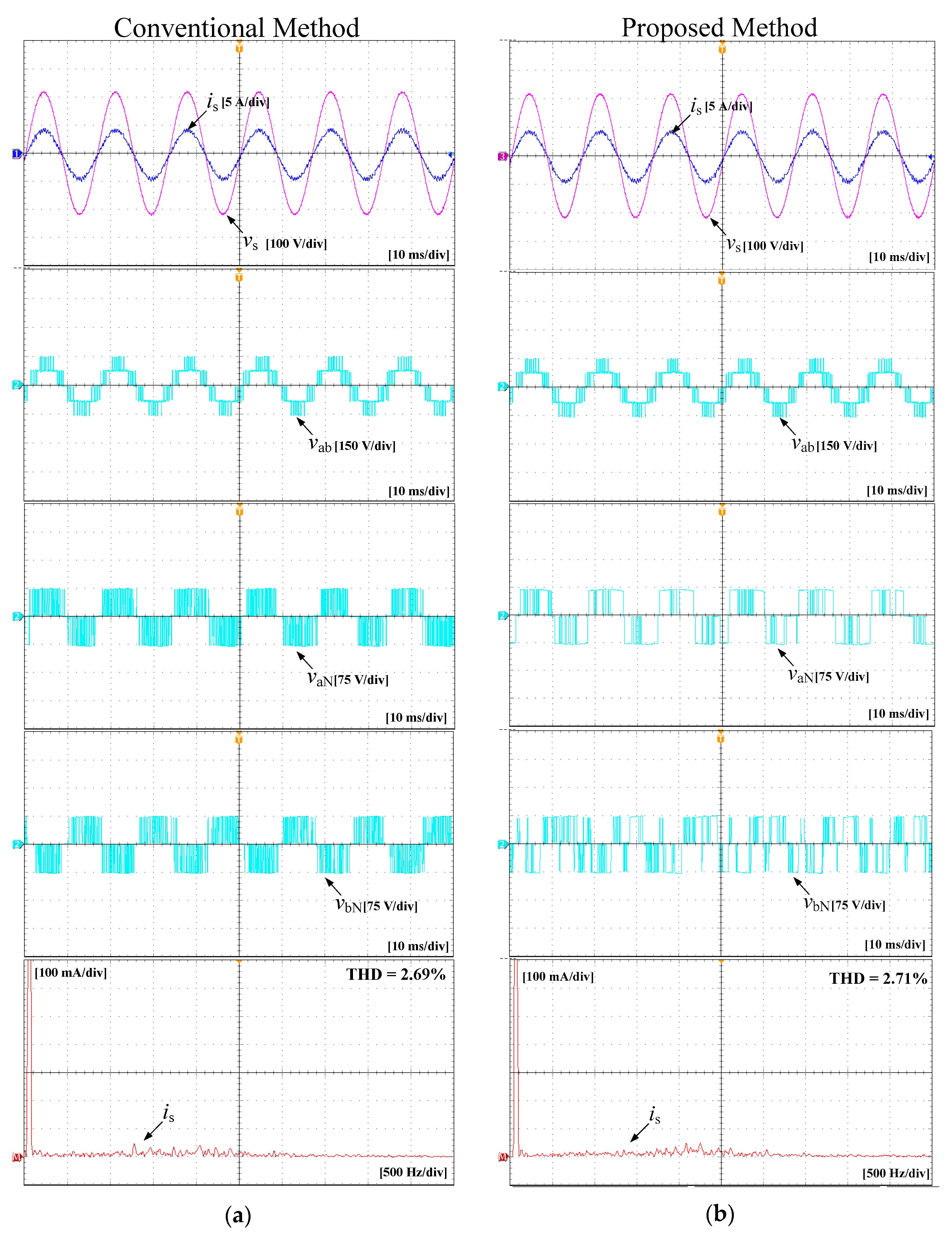

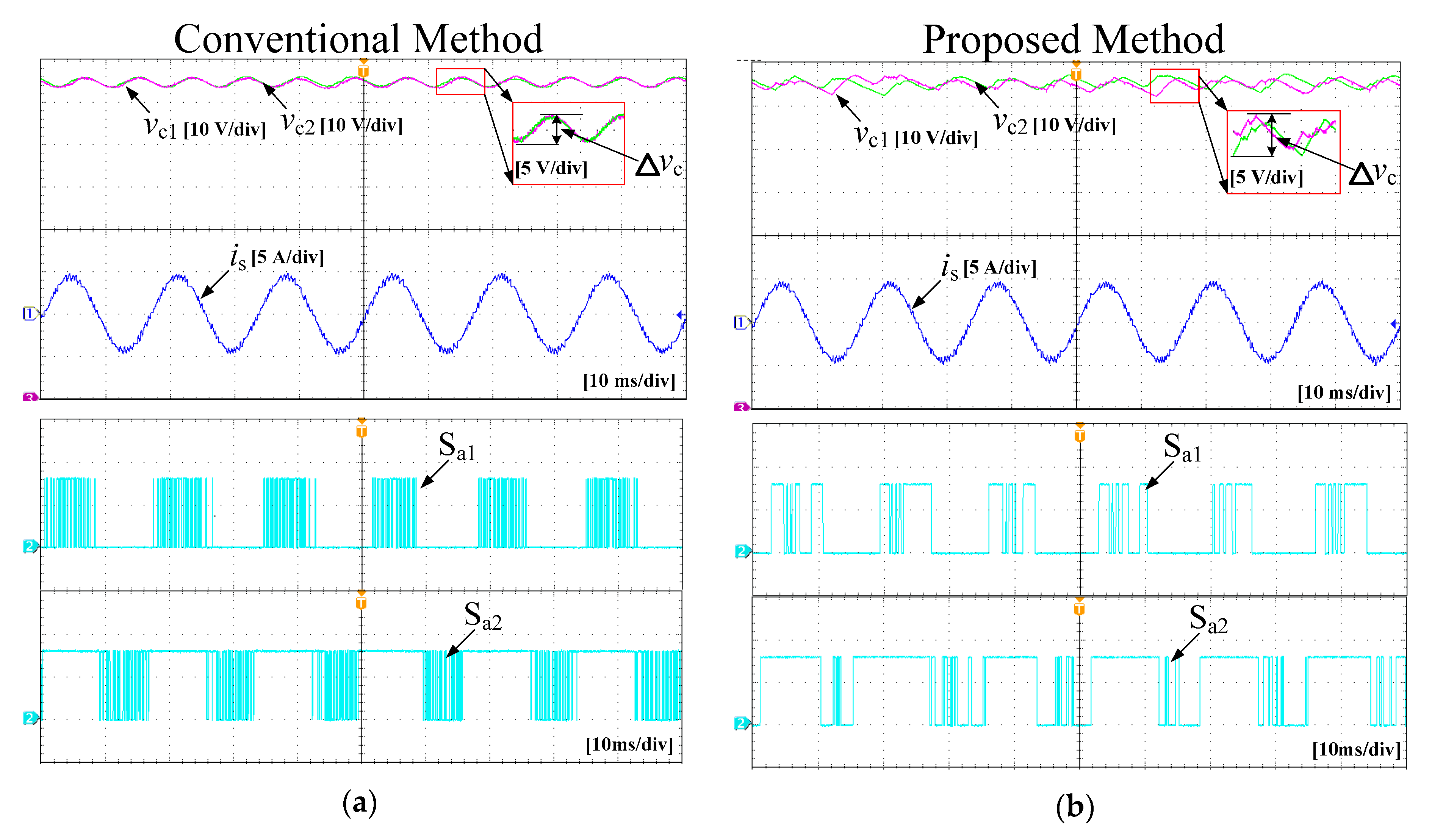

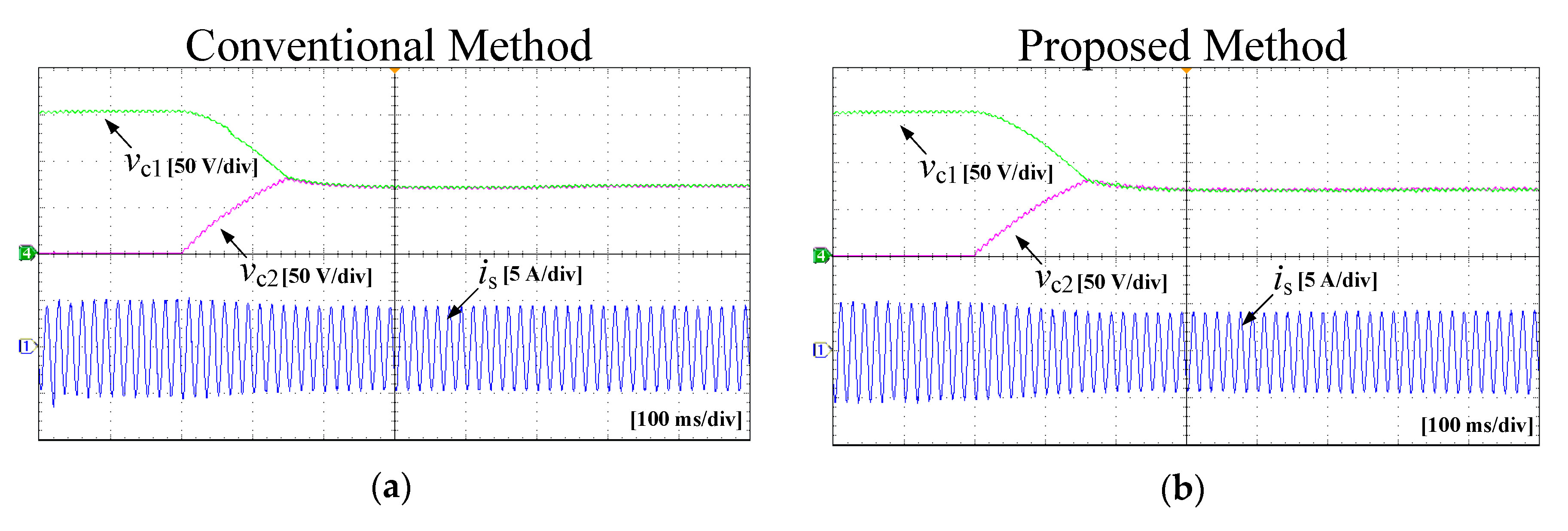

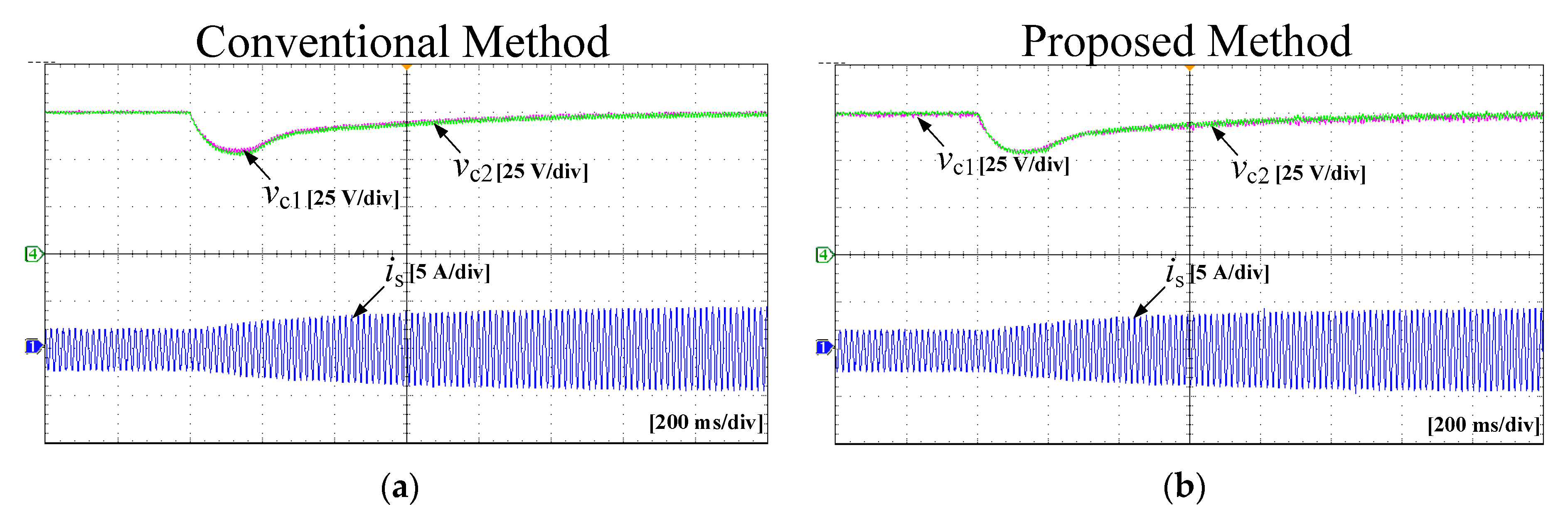

4. Simulation and Experimental Results

5. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

Nomenclature

| Abbreviations | |

| EMI | Electromagnetic interference |

| NPC | Neutral point clamped |

| CBPWM | Carrier-based pulse width modulation |

| PI | Proportional and integral |

| NP | Neutral point |

| MPC | Model predictive control |

| THD | Total harmonic distortion |

| IGBT | Insulated gate bipolar transistor |

| Variables | |

| Sa | Operating status of a-phase |

| Sb | Operating status of b-phase |

| va | Source voltage |

| ia | Source current |

| Reference source current | |

| Input resistance | |

| Input inductance | |

| Line-to-line source voltage | |

| Phase voltage of a-phase | |

| Phase voltage of b-phase | |

| Output capacitance in upper capacitor | |

| Output capacitance in lower capacitor | |

| Current of upper dc-bus bar | |

| Current of lower dc-bus bar | |

| Output load resistance | |

| Output dc voltage | |

| g | Cost function |

| Weighting factor | |

| Sampling period | |

References

- Portillo, R.; Prats, M.M.; Leon, J.I.; Sanchez, J.A.; Carrasco, J.M.; Galvan, E.; Franquelo, L.G. Modeling strategy for back-to-back three-level converters applied to high-power wind turbines. IEEE Trans. Ind. Electron. 2006, 53, 1483–1491. [Google Scholar] [CrossRef]

- Alepuz, S.; Busquets-Monge, S.; Bordonau, J.; Gago, J.; Gonzalez, D.; Balcells, J. Interfacing renewable energy sources to the utility grid using a three-level inverter. IEEE Trans. Ind. Electron. 2006, 53, 1504–1511. [Google Scholar] [CrossRef]

- Stala, R. Application of balancing circuit for DC-link voltages balance in a single-phase diode-clamped inverter with two three-level legs. IEEE Trans. Ind. Electron. 2011, 58, 4185–4195. [Google Scholar] [CrossRef]

- Song, W.; Feng, X.; Smedley, K. A carrier-based PWM strategy with the offset voltage injection for single-phase three-level neutral-point-clamped converters. IEEE Trans. Power Electron. 2013, 28, 1083–1095. [Google Scholar] [CrossRef]

- Choi, U.-M.; Lee, H.-H.; Lee, K.-B. Simple neutral-point voltage control for three-level inverters using a discontinuous pulse width modulation. IEEE Trans. Energy Convers. 2013, 28, 434–443. [Google Scholar] [CrossRef]

- Song, W.; Wang, S.; Xiong, C.; Ge, X.; Feng, X. Single-phase three-level space vector pulse width modulation algorithm for grid-side railway tractionconverter and its relationship of carrier-based pulse width modulation. IET Electr. Syst. Transp. 2014, 14, 78–87. [Google Scholar] [CrossRef]

- Freitas, I.S.D.; Bandeira, M.M.; Barros, L.D.M.; Jacobina, C.B.; Santos, E.C.D.; Salvadori, F.; Silva, S.A.D. A carrier-based PWM technique for capacitor voltage balancing of single-phase three-level neutral-point-clamped converters. IEEE Trans. Ind. Appl. 2015, 51, 3227–3235. [Google Scholar] [CrossRef]

- Habibullah, M.; Lu, D.D.; Xiao, D.; Fletcher, J.E.; Rahman, M.F. Predictive torque control of induction motor sensorless drive fed by a 3L-NPC inverter. IEEE Trans. Ind. Inf. 2017, 13, 60–70. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B. Predictive control of a three-level boost converter and an NPC inverter for high-power PMSG-based medium voltage wind energy conversion systems. IEEE Trans. Power Electron. 2014, 29, 5308–5322. [Google Scholar] [CrossRef]

- Acuna, P.; Moran, L.; Rivera, M.; Aguilera, R.; Burgos, R.; Agelidis, V.G. A single-objective predictive control method for a multivariable single-phase three-level NPC converter-based active power filter. IEEE Trans. Ind. Electron. 2015, 62, 4598–4607. [Google Scholar] [CrossRef]

- Song, W.; Ma, J.; Zhou, L.; Feng, X. Deadbeat predictive power control of single-phase three-level neutral-point-clamped converters using space-vector modulation for electric railway traction. IEEE Trans. Power Electron. 2016, 31, 1083–1095. [Google Scholar] [CrossRef]

- Acuna, P.; Aguilera, R.P.; Ghias, A.M.Y.M.; Rivera, M.; Baier, C.R.; Agelidis, V.G. Cascade-free model predictive control for single-phase grid-connected power converters. IEEE Trans. Ind. Electron. 2017, 64, 721–732. [Google Scholar] [CrossRef]

- Deng, Y.; Li, J.; Shin, K.H.; Viitanen, T.; Saeedifard, M.; Harley, R.G. Improved modulation scheme for loss balancing of three-level active NPC converters. IEEE Trans. Power Electron. 2017, 32, 2521–2532. [Google Scholar] [CrossRef]

- Jing, X.; He, J.; Demerdash, N.A.O. Loss balancing SVPWM for active NPC converters. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014. [Google Scholar]

- Pulikanti, S.; Dahidah, M.S.A.; Agelidis, V. Voltage balancing control of three-level active NPC converter using SHE-PWM. IEEE Trans. Power Deliv. 2011, 26, 258–267. [Google Scholar] [CrossRef]

- Bruckner, T.; Bernet, S.; Guldner, H. The active NPC converter and its loss-balancing control. IEEE Trans. Ind. Electron. 2005, 52, 855–868. [Google Scholar] [CrossRef]

- Floricau, D.; Gateau, G.; Leredde, A.; Teodorescu, R. The efficiency of three-level active NPC converter for different PWM strategies. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009. [Google Scholar]

- Bruckner, T.; Bernet, S.; Steimer, P. Feedforward loss control of three-level active NPC converters. IEEE Trans. Ind. Appl. 2007, 43, 1588–1596. [Google Scholar] [CrossRef]

- Brückner, T.; Bernet, S. Loss balancing in three-level voltage source inverters applying active NPC switches. In Proceedings of the IEEE Power Electronics Specialists Conference (PESC), Vancouver, BC, Canada, 17–21 June 2001; pp. 1135–1140. [Google Scholar]

- Ma, L.; Kerekes, T.; Rodriguez, P.; Jin, X.; Teodorescu, R.; Liserre, M. A new PWM strategy for grid-connected half-bridge active NPC converters with losses distribution balancing mechanism. IEEE Trans. Power Electron. 2015, 30, 5331–5340. [Google Scholar] [CrossRef]

- Jiao, Y.; Lee, F.C. New modulation scheme for three-level active neutral-point-clamped converter with loss and stress reduction. IEEE Trans. Ind. Electron. 2015, 62, 5468–5479. [Google Scholar] [CrossRef]

- Habibullah, M.; Lu, D.D.; Xiao, D.; Rahman, M.F. Finite-state predictive torque control of induction motor supplied from a three-level NPC voltage source inverter. IEEE Trans. Power Electron. 2017, 32, 479–489. [Google Scholar] [CrossRef]

- Vargas, R.; Ammann, U.; Rodriguez, J. Predictive approach to increase efficiency and reduce switching losses on matrix converters. IEEE Trans. Power Electron. 2009, 24, 894–902. [Google Scholar] [CrossRef]

- Vargas, R.; Rodriguez, J.; Rojas, C.A.; Rivera, M. Predictive control of an induction machine fed by a matrix converter with increased efficiency and reduced common-mode voltage. IEEE Trans. Energy Convers. 2014, 29, 473–485. [Google Scholar]

- Vatani, M.; Bahrani, B.; Saeedifard, M.; Hovd, M. Indirect finite control set model predictive control of modular multilevel converters. IEEE Trans. Smart Grid 2015, 6, 1520–1529. [Google Scholar] [CrossRef]

- Kwak, S.; Park, J. Switching strategy based on model predictive control of VSI to obtain high efficiency and balanced loss distribution. IEEE Trans. Power Electron. 2014, 29, 4551–4567. [Google Scholar] [CrossRef]

- Kwak, S.; Park, J. Predictive control method with future zero-sequence voltage to reduce switching losses in three-phase voltage source inverters. IEEE Trans. Power Electron. 2015, 30, 1558–1566. [Google Scholar] [CrossRef]

- Kukrer, O. Discrete-time current control of voltage-fed three-phase PWM inverters. IEEE Trans. Power Electron. 1996, 11, 260–269. [Google Scholar] [CrossRef]

- Hildetirand, F.B. Introduction to Numerical Analysis; McGraw-Hill: New York, NY, USA, 1956. [Google Scholar]

- Venkatraman, K.; Selvan, M.P.; Moorthi, S. Predictive current control of distribution static compensator for load compensation in distribution system. IET Gener. Transm. Distrib. 2016, 10, 2410–2423. [Google Scholar] [CrossRef]

- Kumar, C.; Mishra, M.K. Operation and control of an improved performance interactive DSTATCOM. IEEE Trans. Ind. Electron. 2015, 62, 6024–6034. [Google Scholar] [CrossRef]

| # | Operating Status | Phase Switching State | Converter input Voltage | Capacitor Voltage | |||||

|---|---|---|---|---|---|---|---|---|---|

| Sa | Sb | Sa1 | Sa2 | Sb1 | Sb2 | vab | vc1 | vc2 | |

| 1 | 0 | 0 | OFF | ON | OFF | ON | 0 | - | - |

| 2 | 1 | 1 | ON | ON | ON | ON | 0 | - | - |

| 3 | −1 | −1 | OFF | OFF | OFF | OFF | 0 | - | - |

| 4 | 1 | −1 | ON | ON | OFF | OFF | Vdc | ↑ | ↑ |

| 5 | 1 | 0 | ON | ON | OFF | ON | Vdc/2 | ↑ | ↓ |

| 6 | 0 | −1 | OFF | ON | OFF | OFF | Vdc/2 | ↓ | ↑ |

| 7 | 0 | 1 | OFF | ON | ON | ON | −Vdc/2 | ↑ | ↓ |

| 8 | −1 | 0 | OFF | OFF | OFF | ON | −Vdc/2 | ↓ | ↑ |

| 9 | −1 | 1 | OFF | OFF | ON | ON | −Vdc | ↓ | ↓ |

| Current Operating Status | Next Possible Operating Status | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (Sa,Sb) | (0,0) | (0,0) | (0,1) | (1,0) | (−1,0) | (0,−1) | (1,−1) | (−1,1) | (1,1) | (−1,−1) |

| number of commutations | 0 | 1 | 1 | 1 | 1 | 2 | 2 | 2 | 2 | |

| (Sa,Sb) | (1.1) | (1,1) | (1,0) | (0,1) | (−1,1) | (0,0) | (1,−1) | (0,−1) | (−1,0) | (−1,−1) |

| number of commutations | 0 | 1 | 1 | 2 | 2 | 2 | 3 | 3 | 4 | |

| (Sa,Sb) | (−1.−1) | (−1,−1) | (−1,0) | (0,−1) | (−1,1) | (0,0) | (1,−1) | (0,1) | (1,0) | (1,1) |

| number of commutations | 0 | 1 | 1 | 2 | 2 | 2 | 3 | 3 | 4 | |

| (Sa,Sb) | (1.−1) | (1,−1) | (0,−1) | (1,0) | (−1,−1) | (0,0) | (1,1) | (−1,0) | (0,1) | (−1,1) |

| number of commutations | 0 | 1 | 1 | 2 | 2 | 2 | 3 | 3 | 4 | |

| (Sa,Sb) | (1.0) | (1,0) | (1,1) | (1,−1) | (0,0) | (0,1) | (0,−1) | (−1,0) | (−1,1) | (−1,−1) |

| number of commutations | 0 | 1 | 1 | 1 | 2 | 2 | 2 | 3 | 3 | |

| (Sa,Sb) | (0.−1) | (0,−1) | (1,−1) | (−1,−1) | (0,0) | (0,1) | (1,0) | (−1,0) | (−1,1) | (1,1) |

| number of commutations | 0 | 1 | 1 | 1 | 2 | 2 | 2 | 3 | 3 | |

| (Sa,Sb) | (0.1) | (0,1) | (1,1) | (−1,1) | (0,0) | (0,−1) | (1,0) | (−1,0) | (1,−1) | (−1,−1) |

| number of commutations | 0 | 1 | 1 | 1 | 2 | 2 | 2 | 3 | 3 | |

| (Sa,Sb) | (−1.0) | (−1,0) | (−1,1) | (−1,−1) | (0,0) | (0,1) | (0,−1) | (1,0) | (1,−1) | (1,1) |

| number of commutations | 0 | 1 | 1 | 1 | 2 | 2 | 2 | 3 | 3 | |

| (Sa,Sb) | (−1.1) | (−1,1) | (0,1) | (−1,0) | (−1,−1) | (0,0) | (1,1) | (1,0) | (0,−1) | (1,−1) |

| number of commutations | 0 | 1 | 1 | 2 | 2 | 2 | 3 | 3 | 4 | |

| Current Operating Status | Next Possible Operating Status |

|---|---|

| (0,0) | (0,0) (0,1) (1,0) (−1,0) (0,−1) |

| (1,1) | (1,1) (1,0) (0,1) |

| (−1,−1) | (−1,−1) (−1,0) (0,−1) |

| (1,−1) | (1,−1) (0,−1) (1,0) |

| (1,0) | (1,0) (1,1) (1,−1) (0,0) |

| (0,−1) | (0,−1) (1,−1) (−1,−1) (0,0) |

| (0,1) | (0,1) (1,1) (−1,1) (0,0) |

| (−1,0) | (−1,0) (−1,1) (−1,−1) (0,0) |

| (−1,1) | (−1,1) (0,1) (−1,0) |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jun, E.-S.; Kwak, S. A Highly Efficient Single-Phase Three-Level Neutral Point Clamped (NPC) Converter Based on Predictive Control with Reduced Number of Commutations. Energies 2018, 11, 3524. https://doi.org/10.3390/en11123524

Jun E-S, Kwak S. A Highly Efficient Single-Phase Three-Level Neutral Point Clamped (NPC) Converter Based on Predictive Control with Reduced Number of Commutations. Energies. 2018; 11(12):3524. https://doi.org/10.3390/en11123524

Chicago/Turabian StyleJun, Eun-Su, and Sangshin Kwak. 2018. "A Highly Efficient Single-Phase Three-Level Neutral Point Clamped (NPC) Converter Based on Predictive Control with Reduced Number of Commutations" Energies 11, no. 12: 3524. https://doi.org/10.3390/en11123524

APA StyleJun, E.-S., & Kwak, S. (2018). A Highly Efficient Single-Phase Three-Level Neutral Point Clamped (NPC) Converter Based on Predictive Control with Reduced Number of Commutations. Energies, 11(12), 3524. https://doi.org/10.3390/en11123524