Analysis to Input Current Zero Crossing Distortion of Bridgeless Rectifier Operating under Different Power Factors

Abstract

:1. Introduction

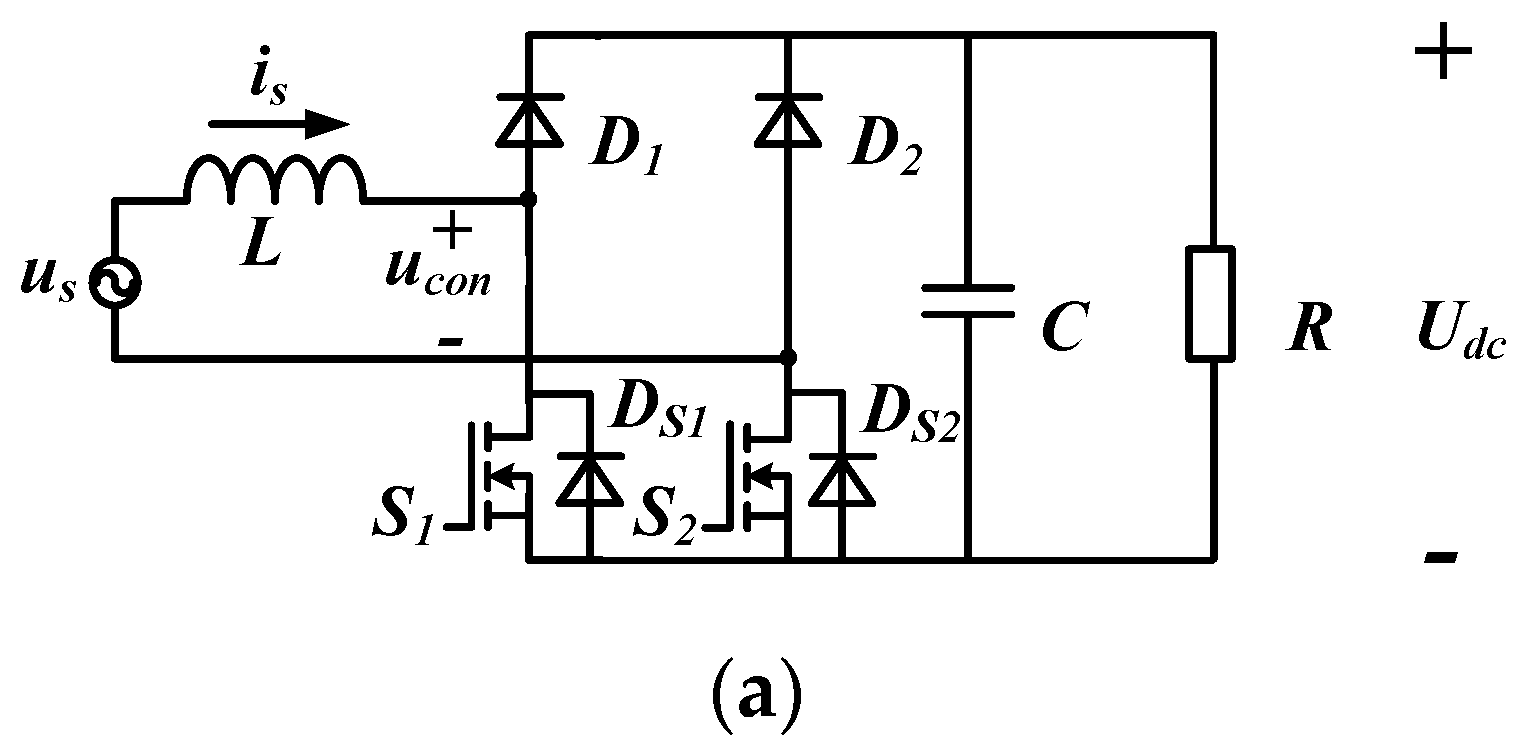

2. Operating Principle and Driving Modes of Switches

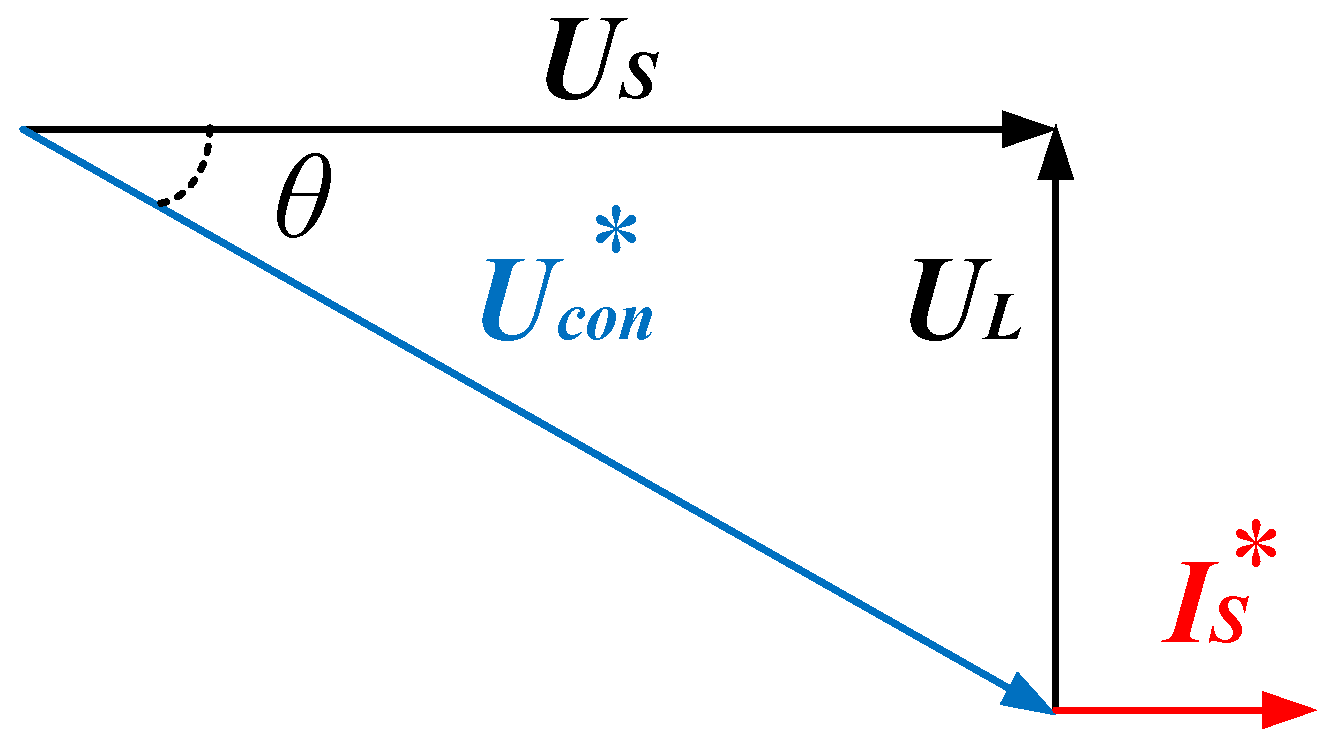

2.1. Effective Operation Mode and Mathematical Model

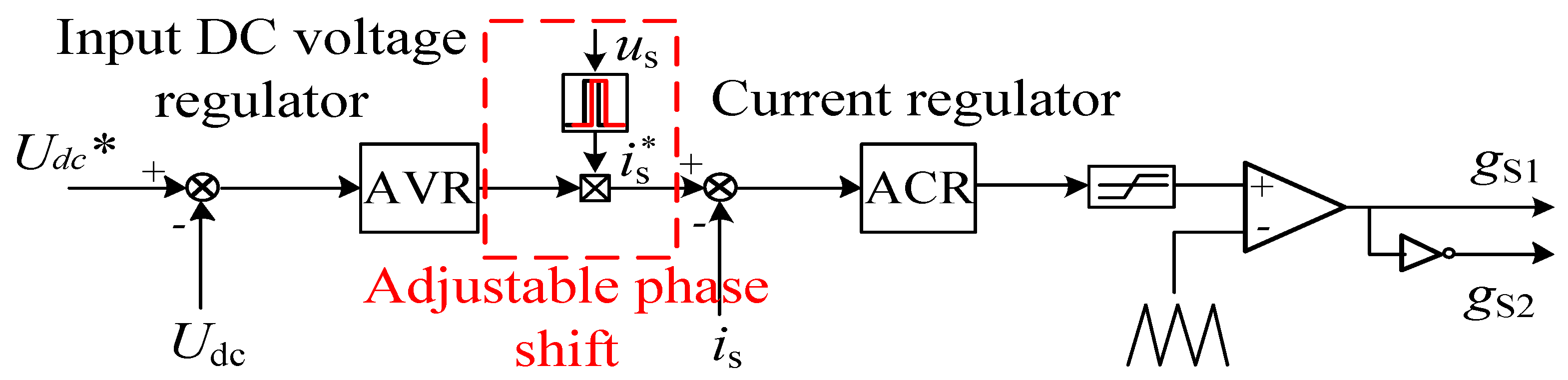

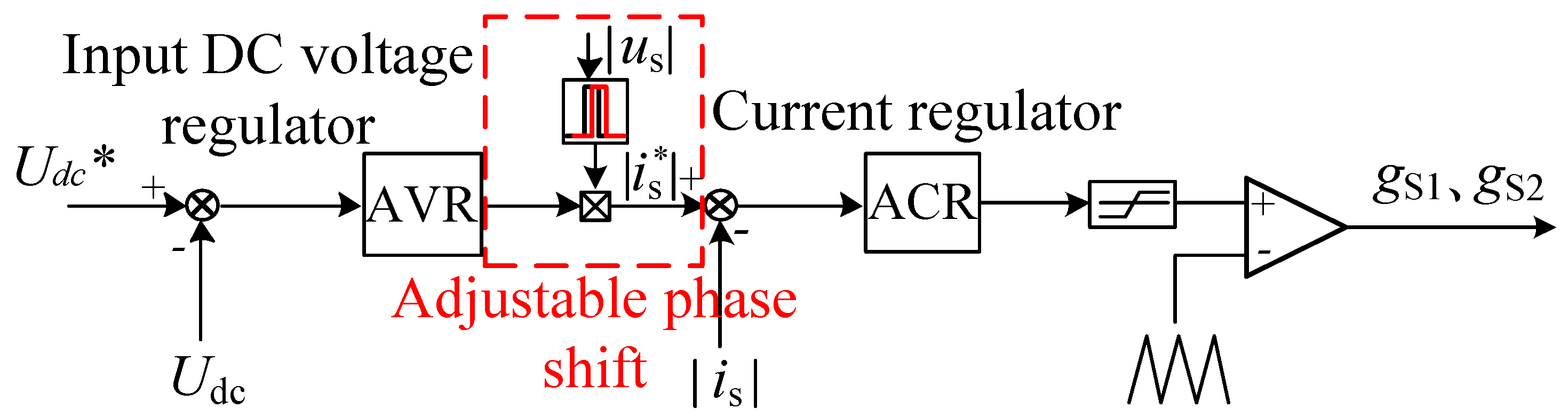

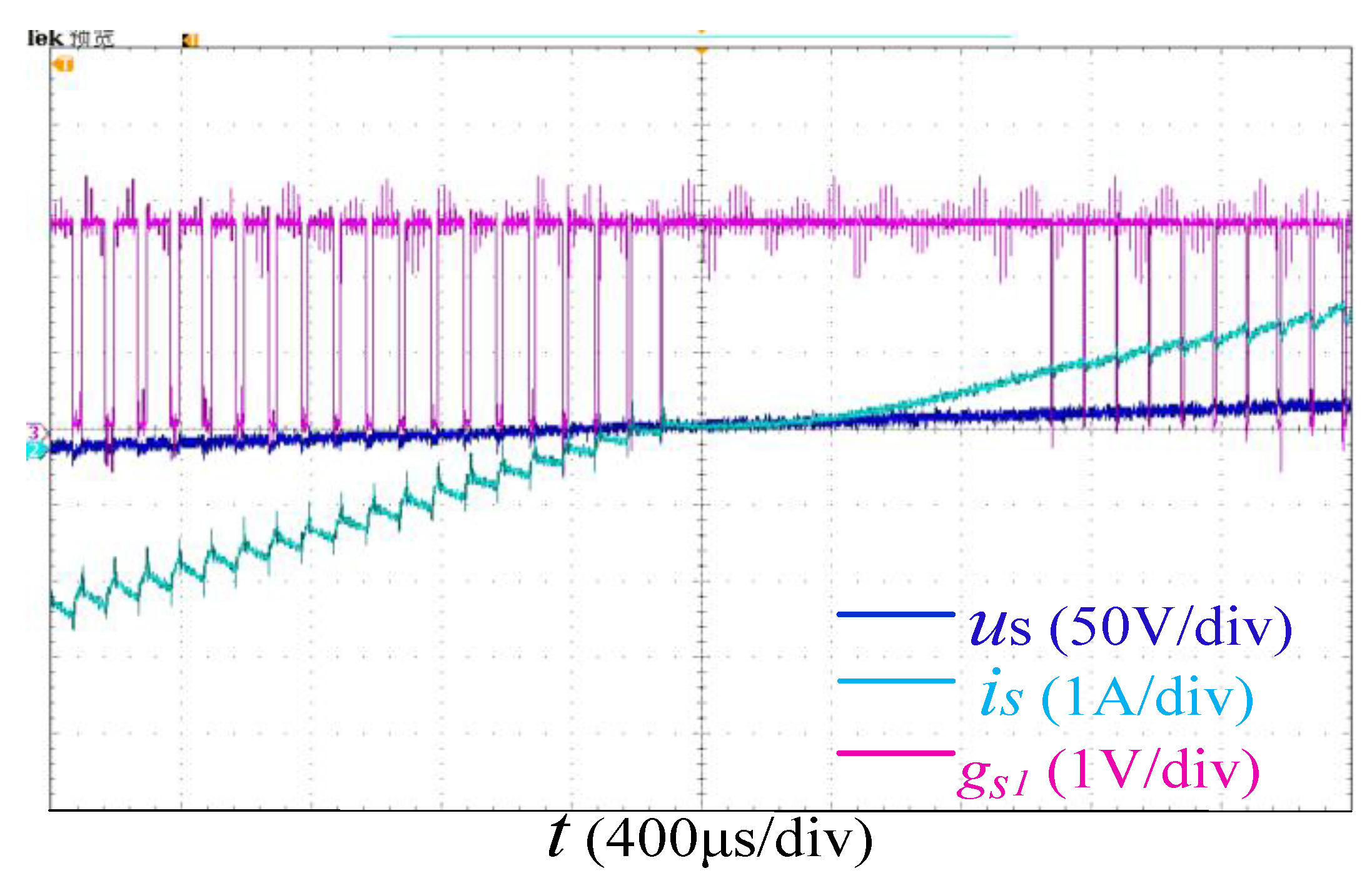

2.2. Driving Mode of Two Switches

3. Analysis of Input Current Zero-Crossing Distortion

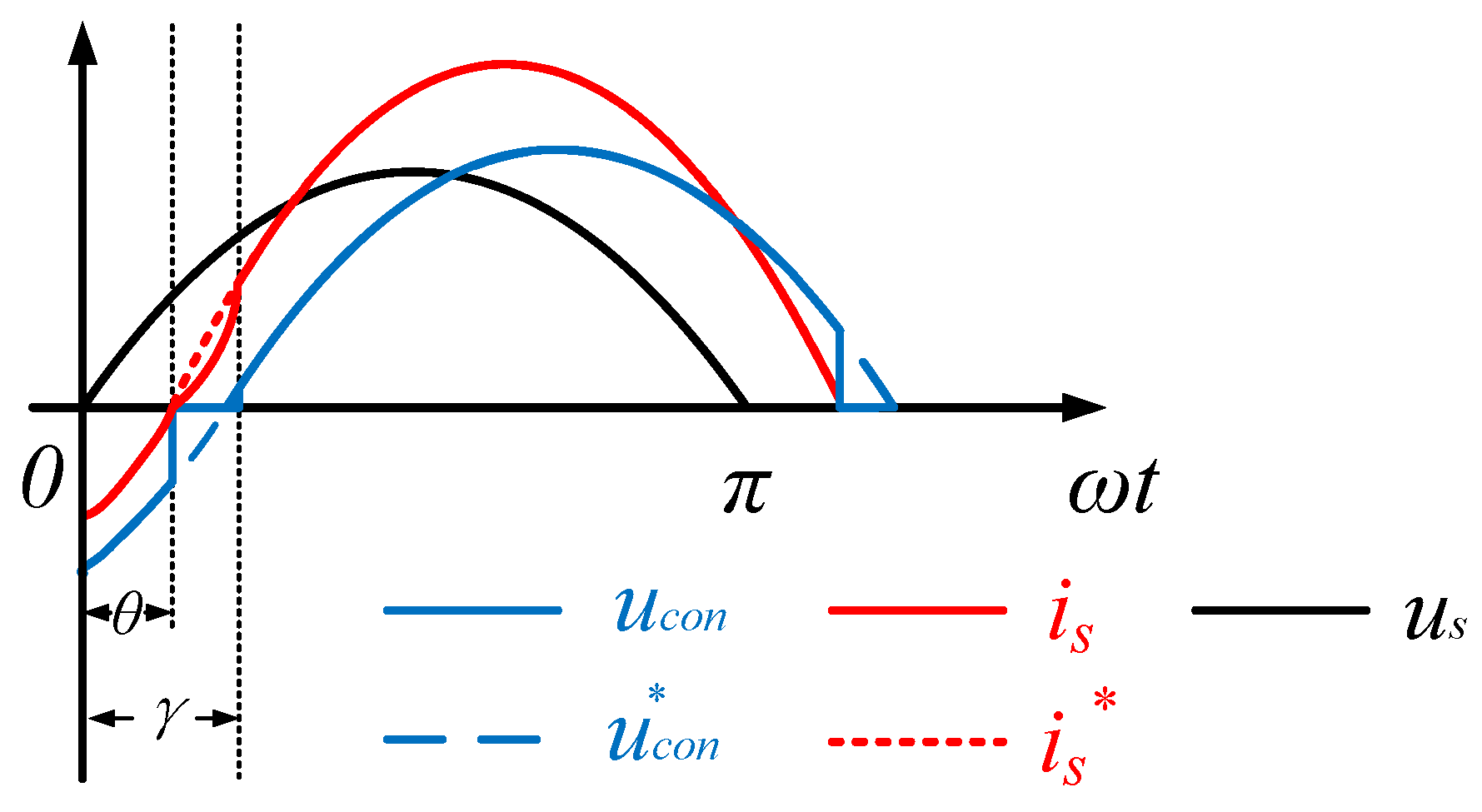

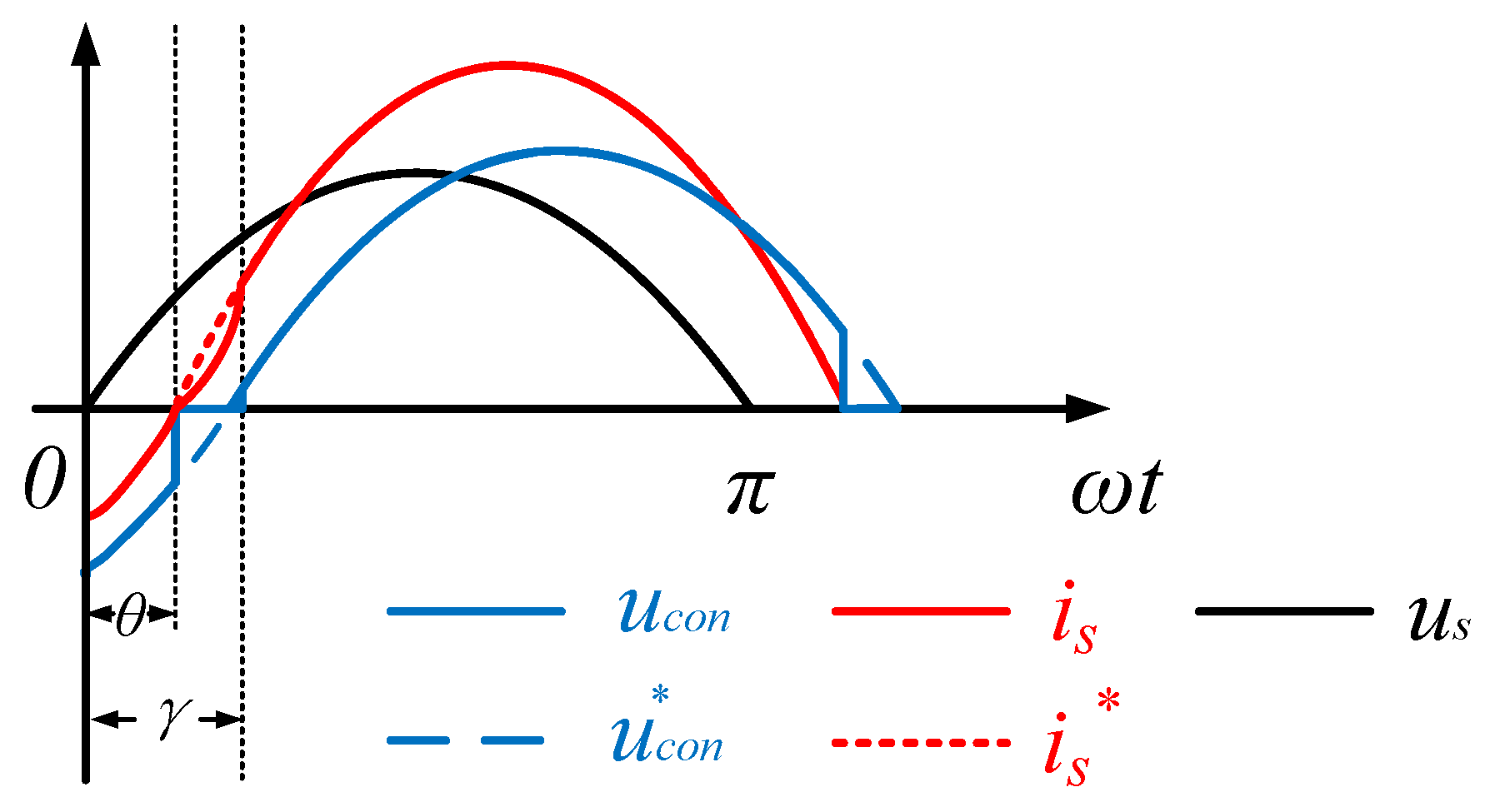

3.1. Theory for Input Current Zero-Crossing Distortion

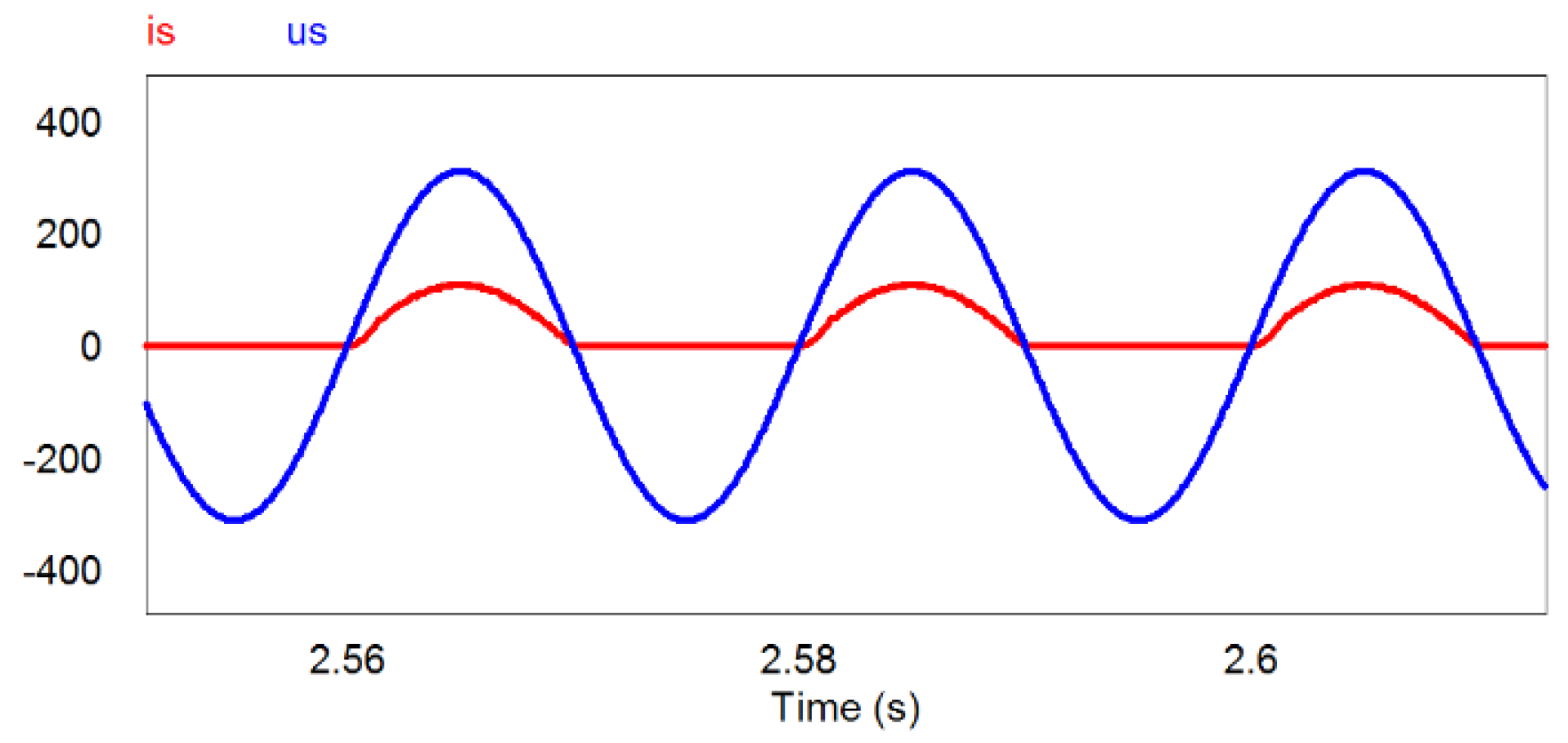

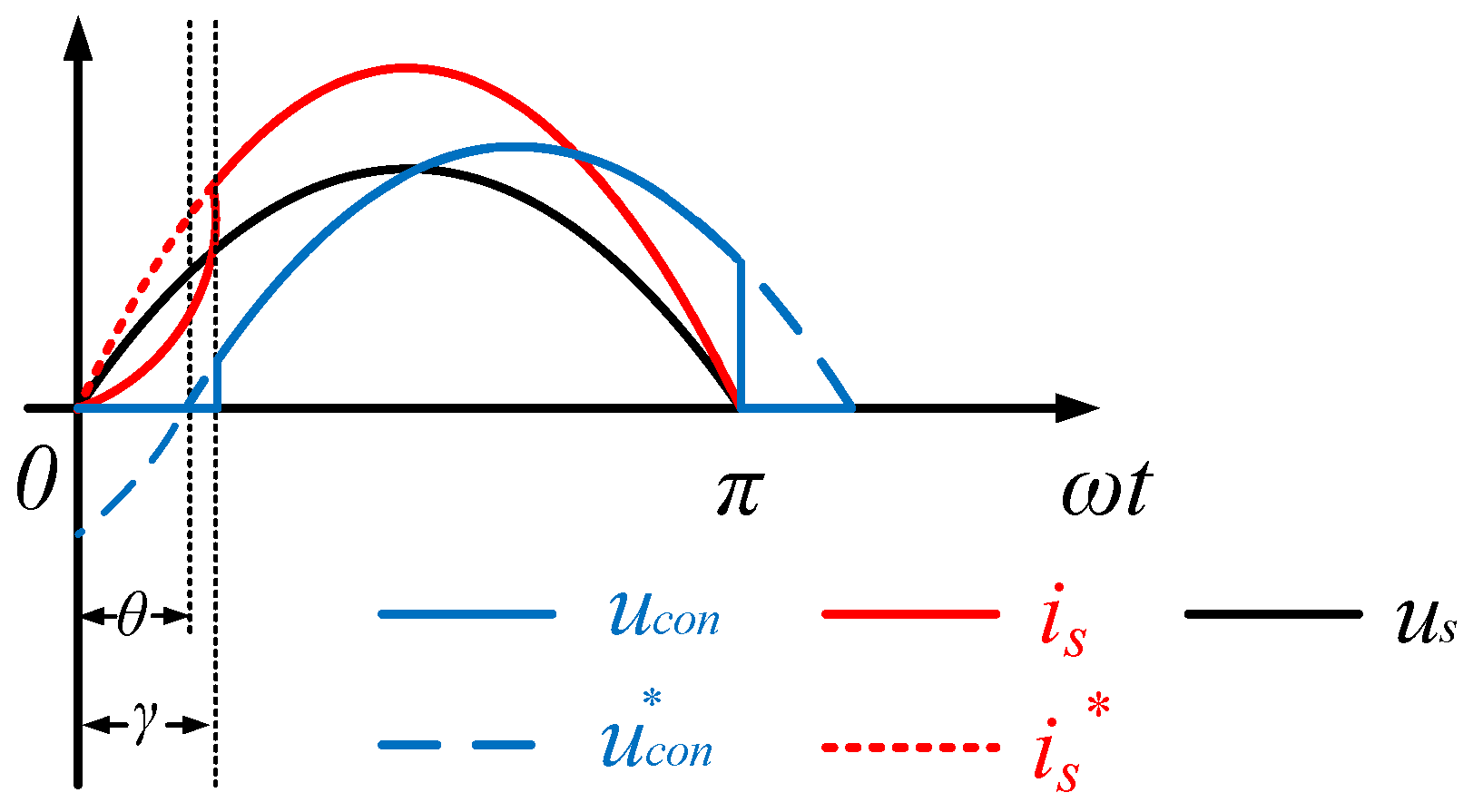

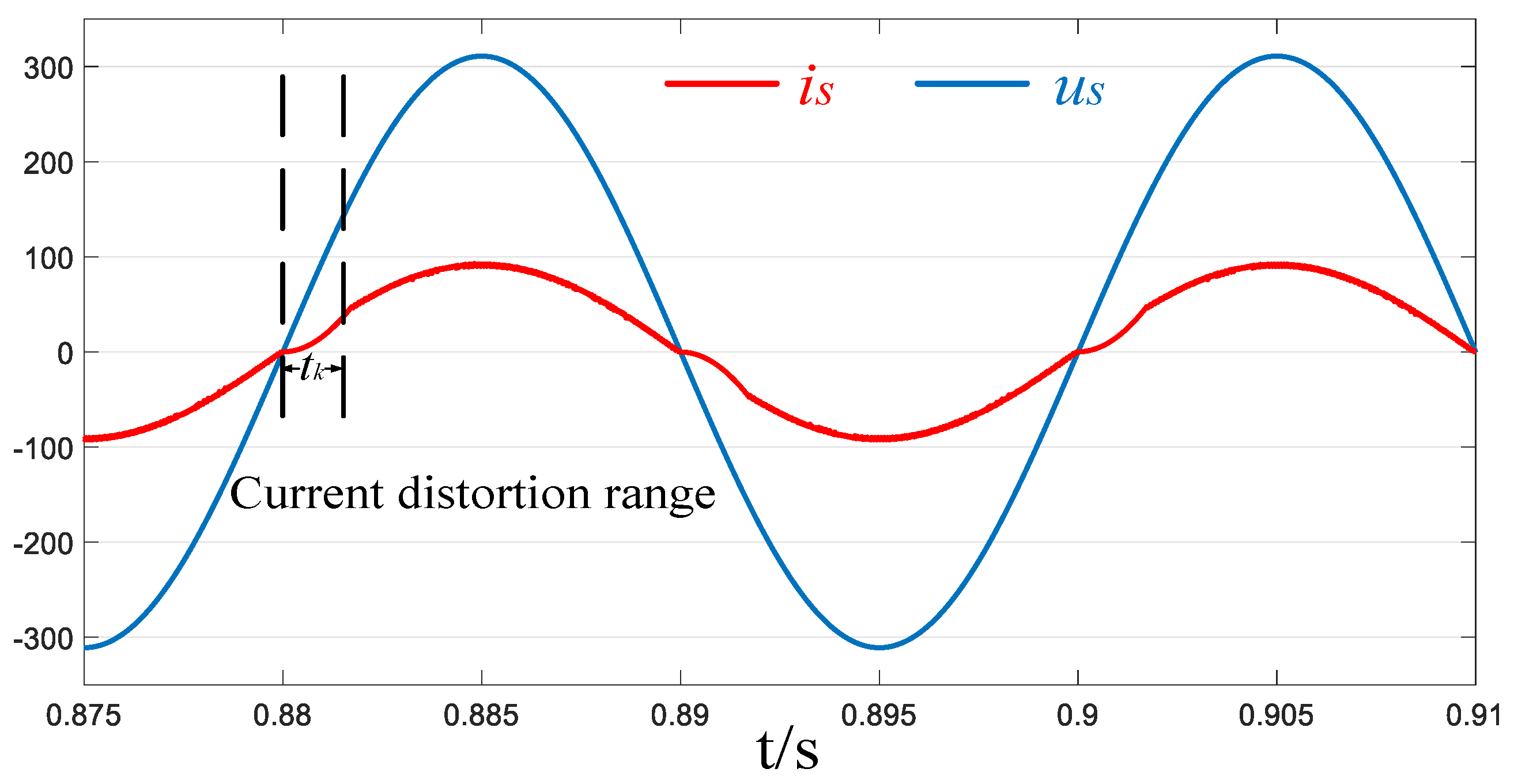

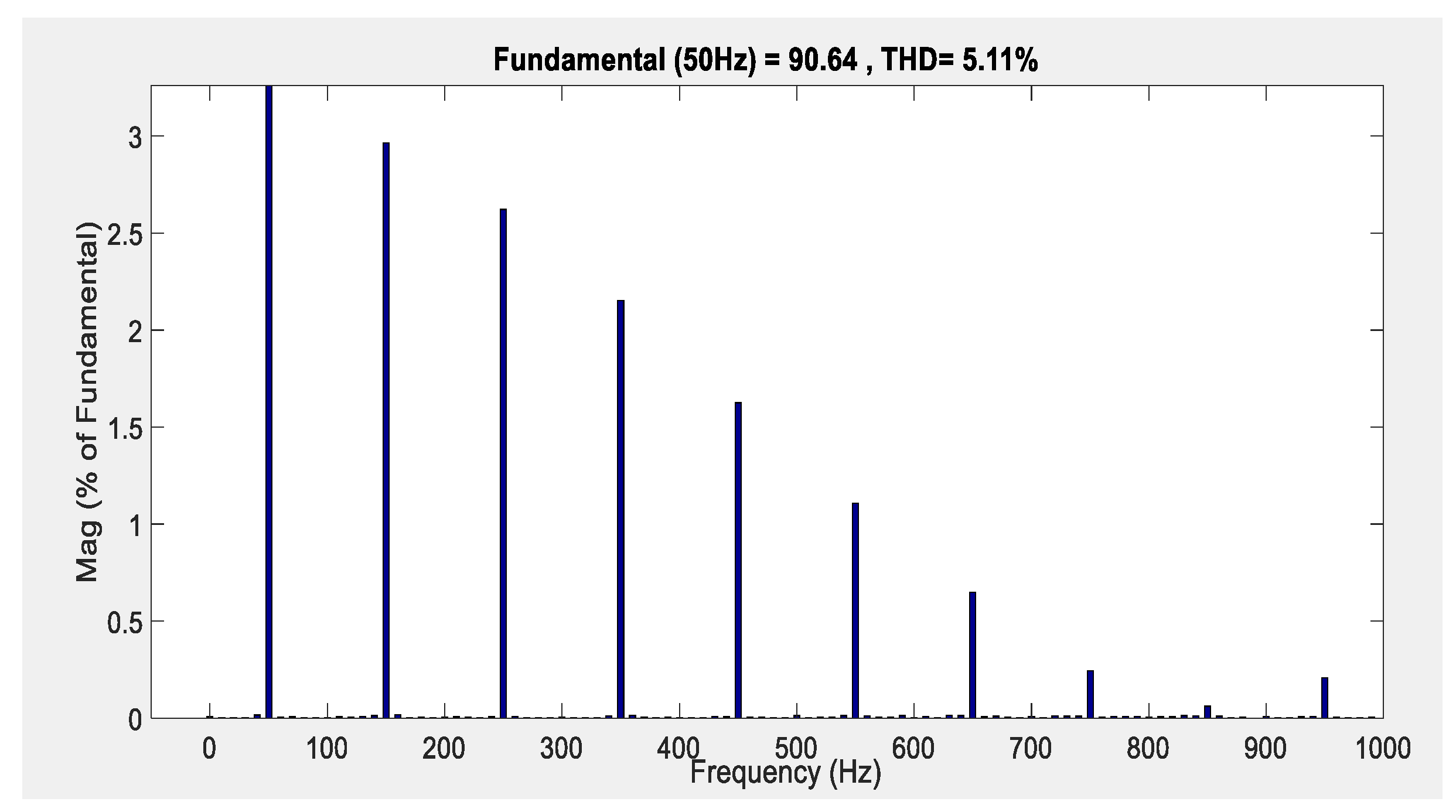

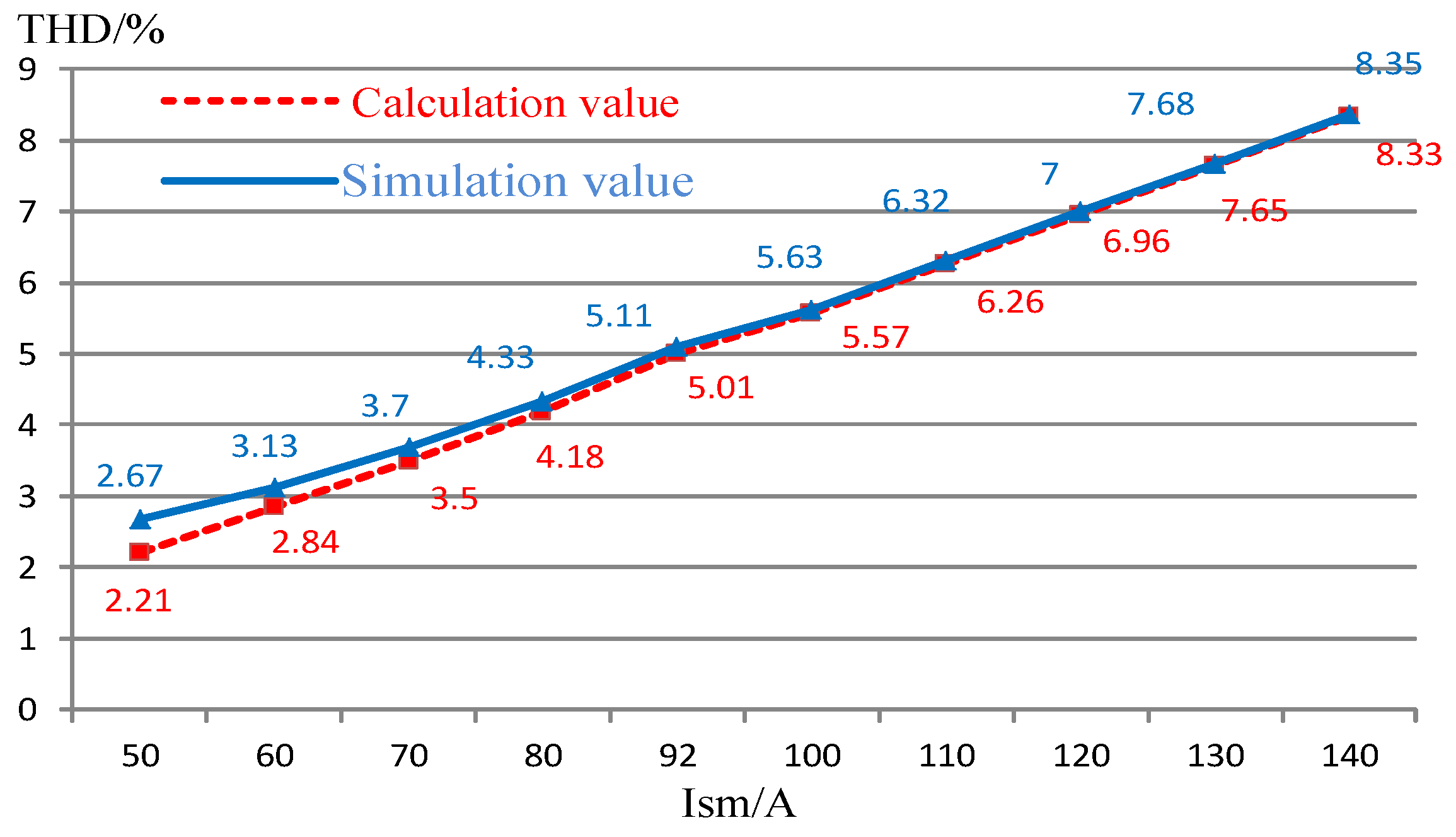

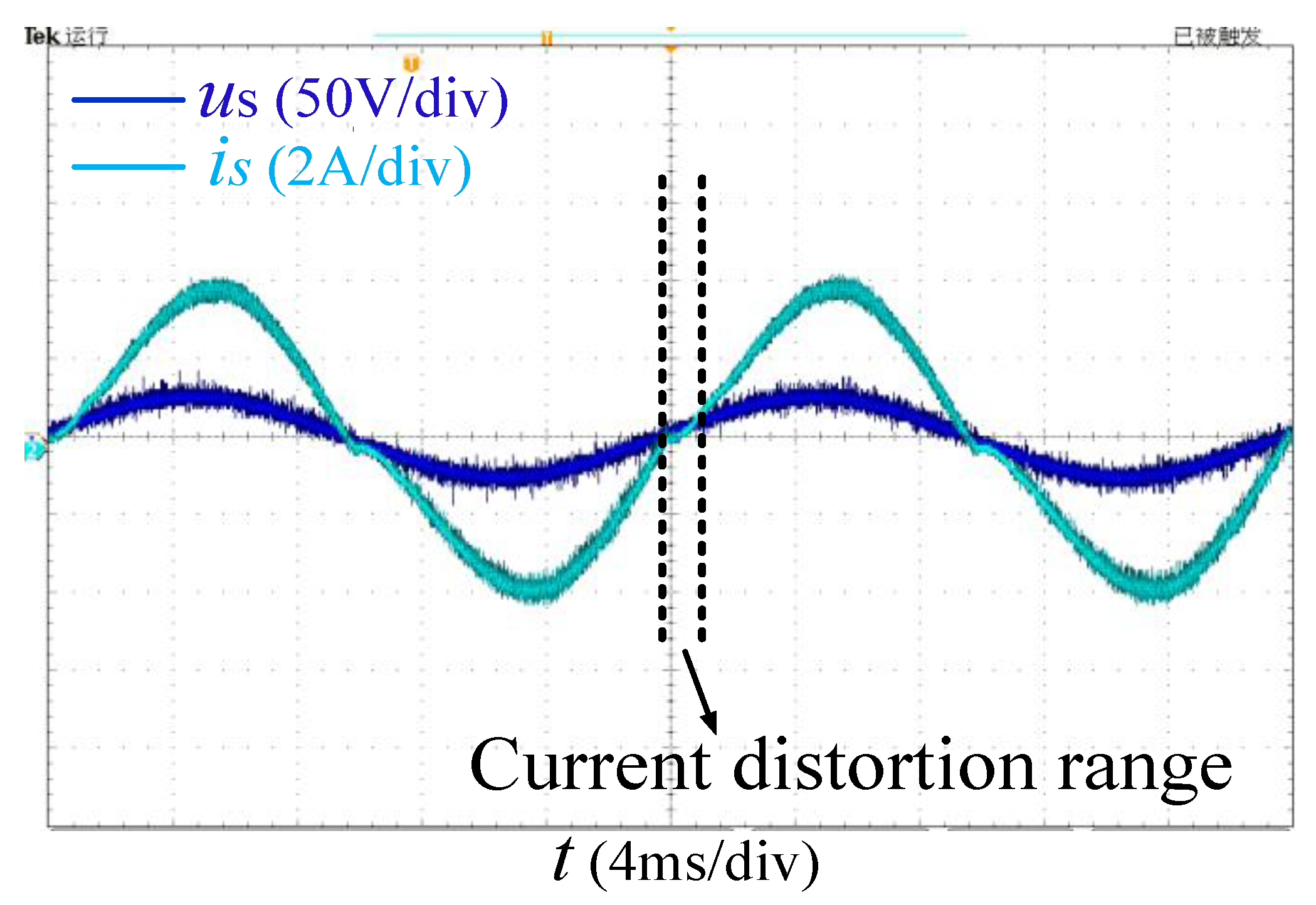

3.2. Distortion Characteristics of Input Current under Unity Power Factor

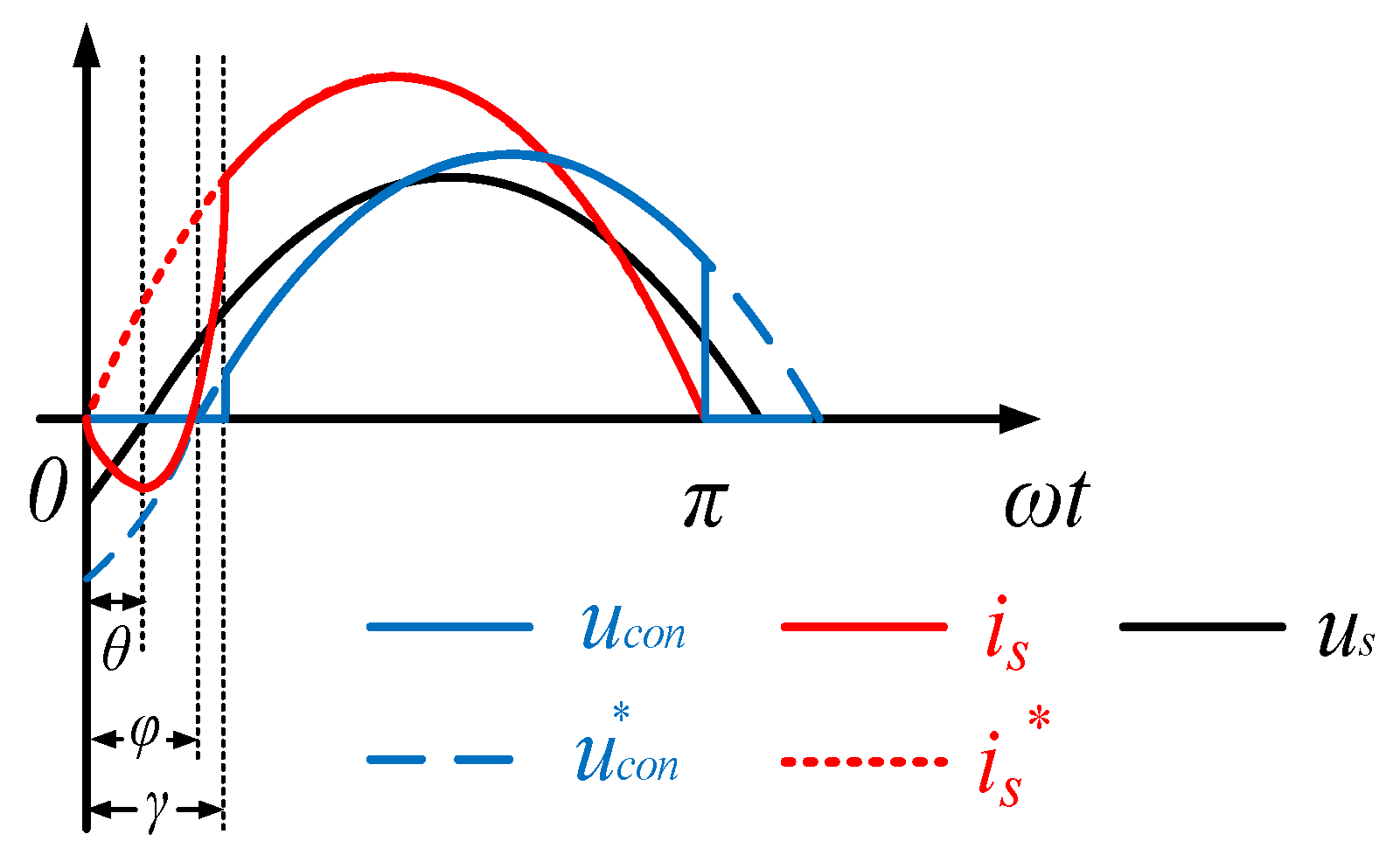

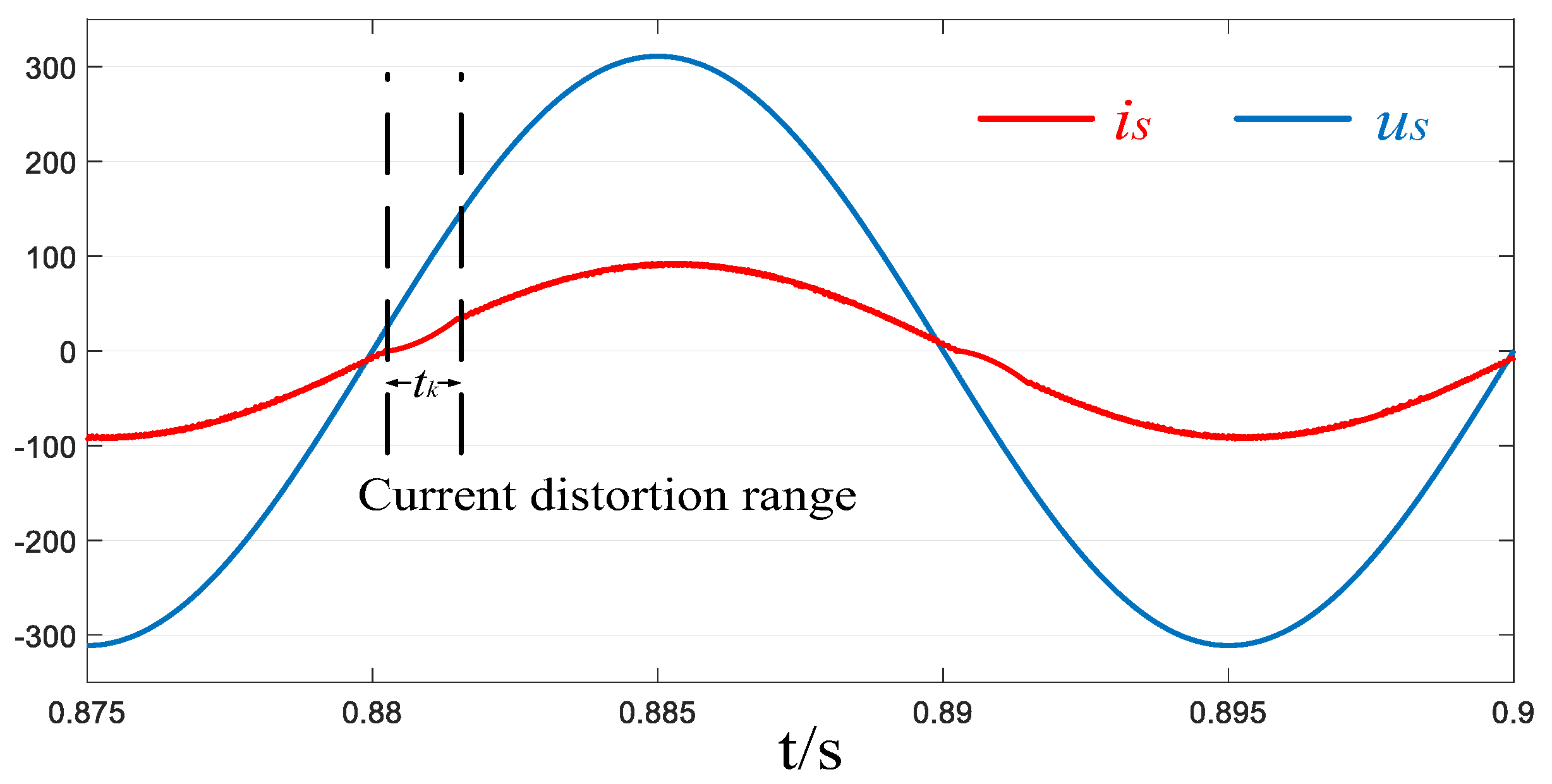

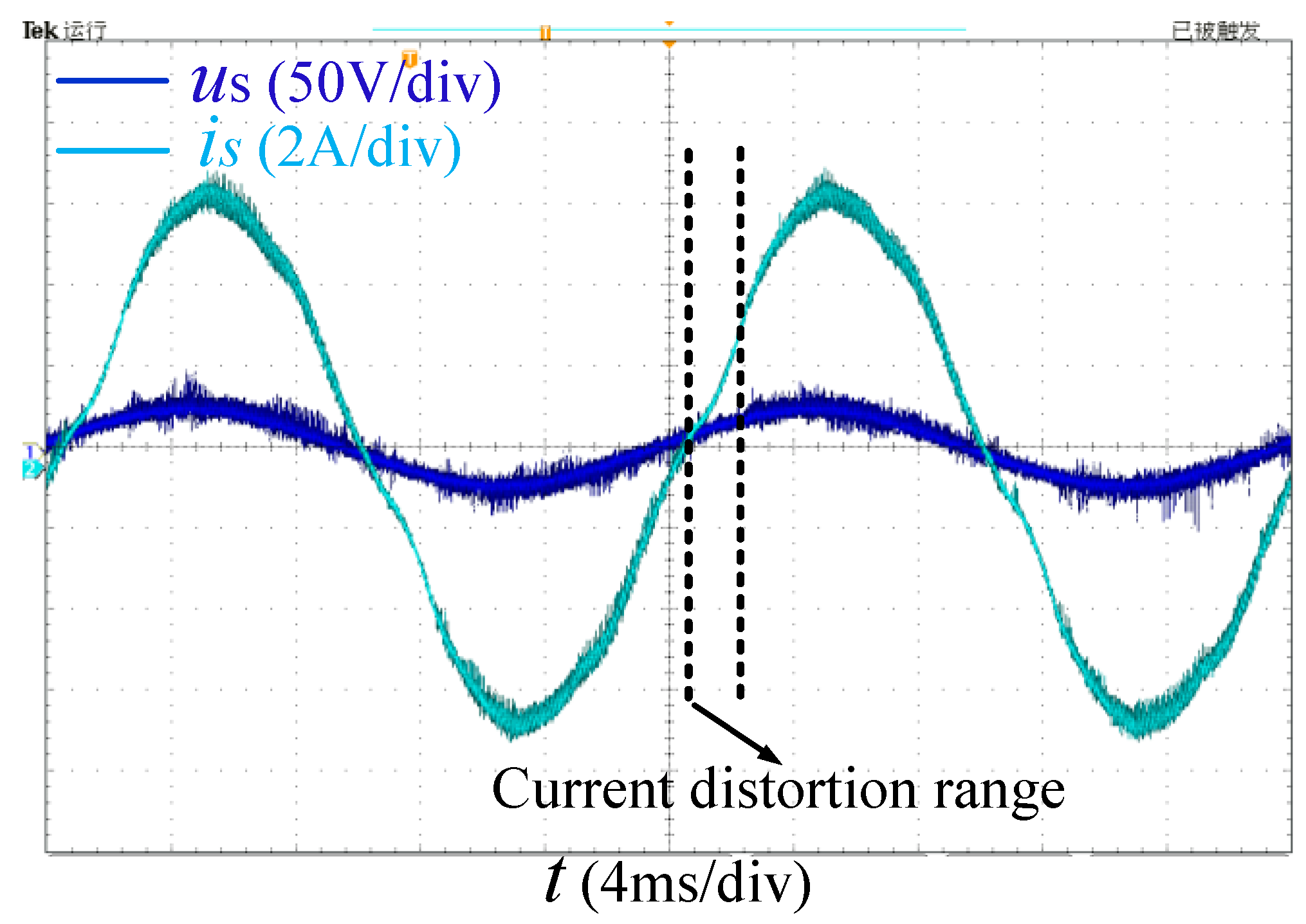

3.3. Distortion Characteristics of Input Current under Leading Power Factor

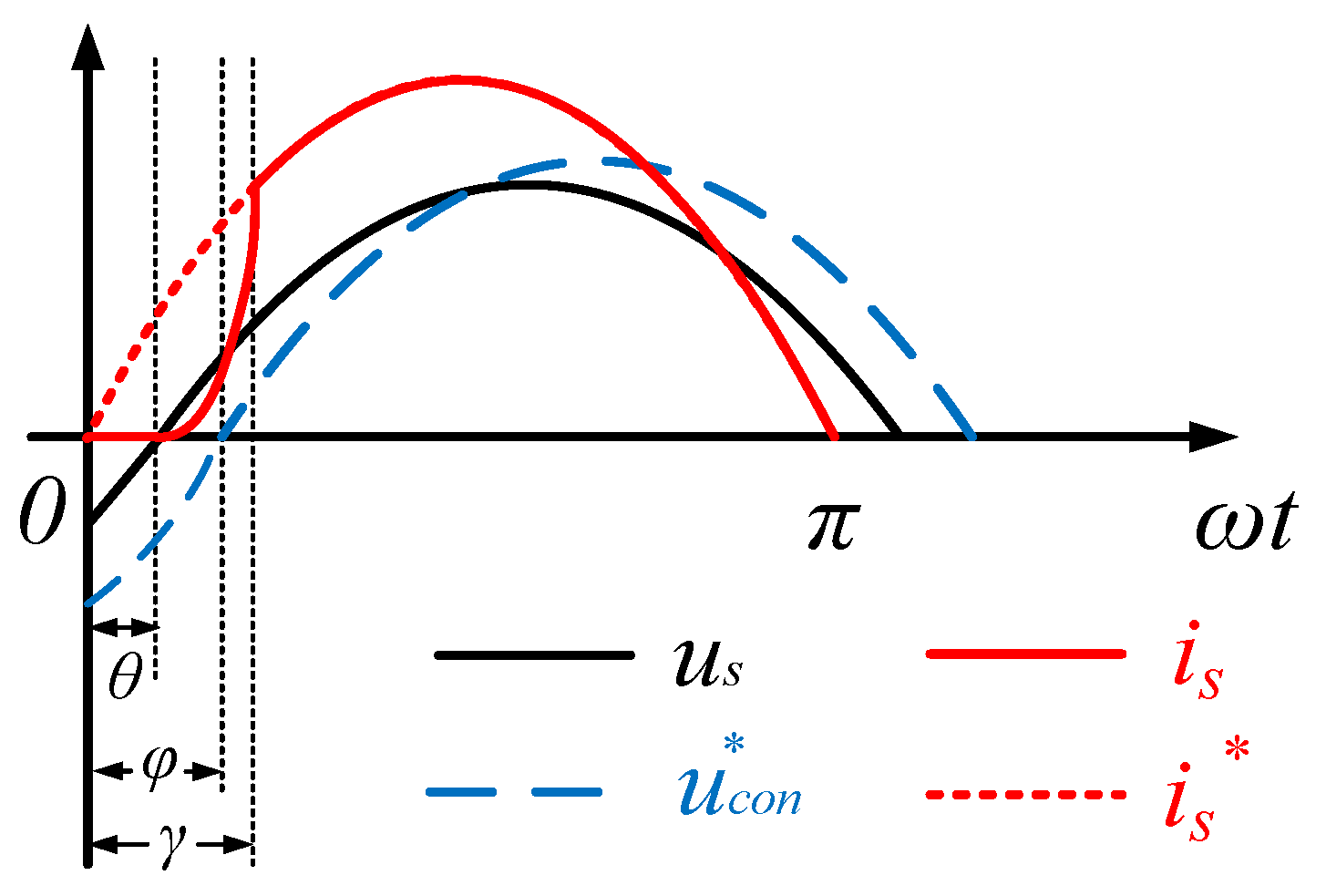

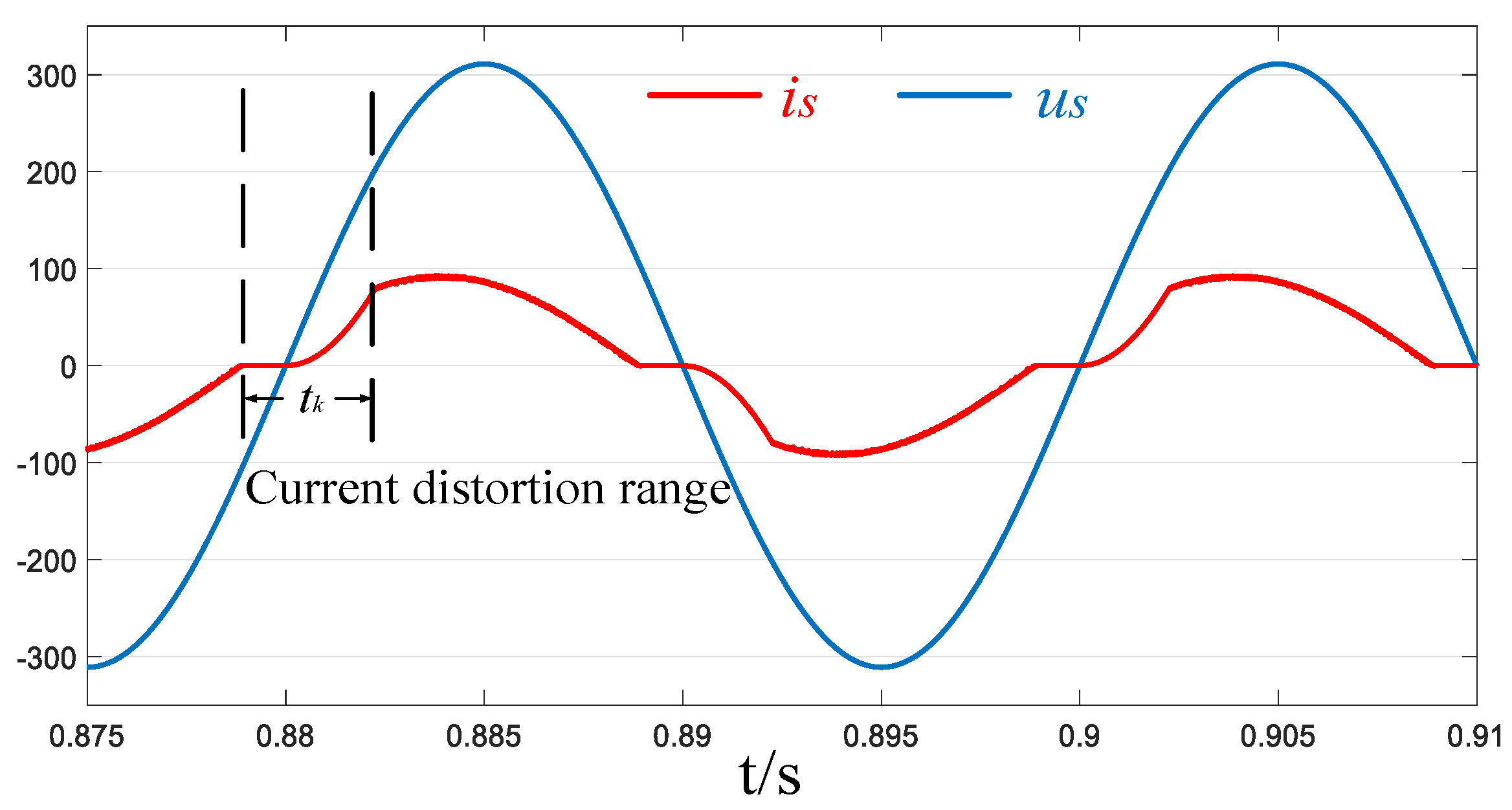

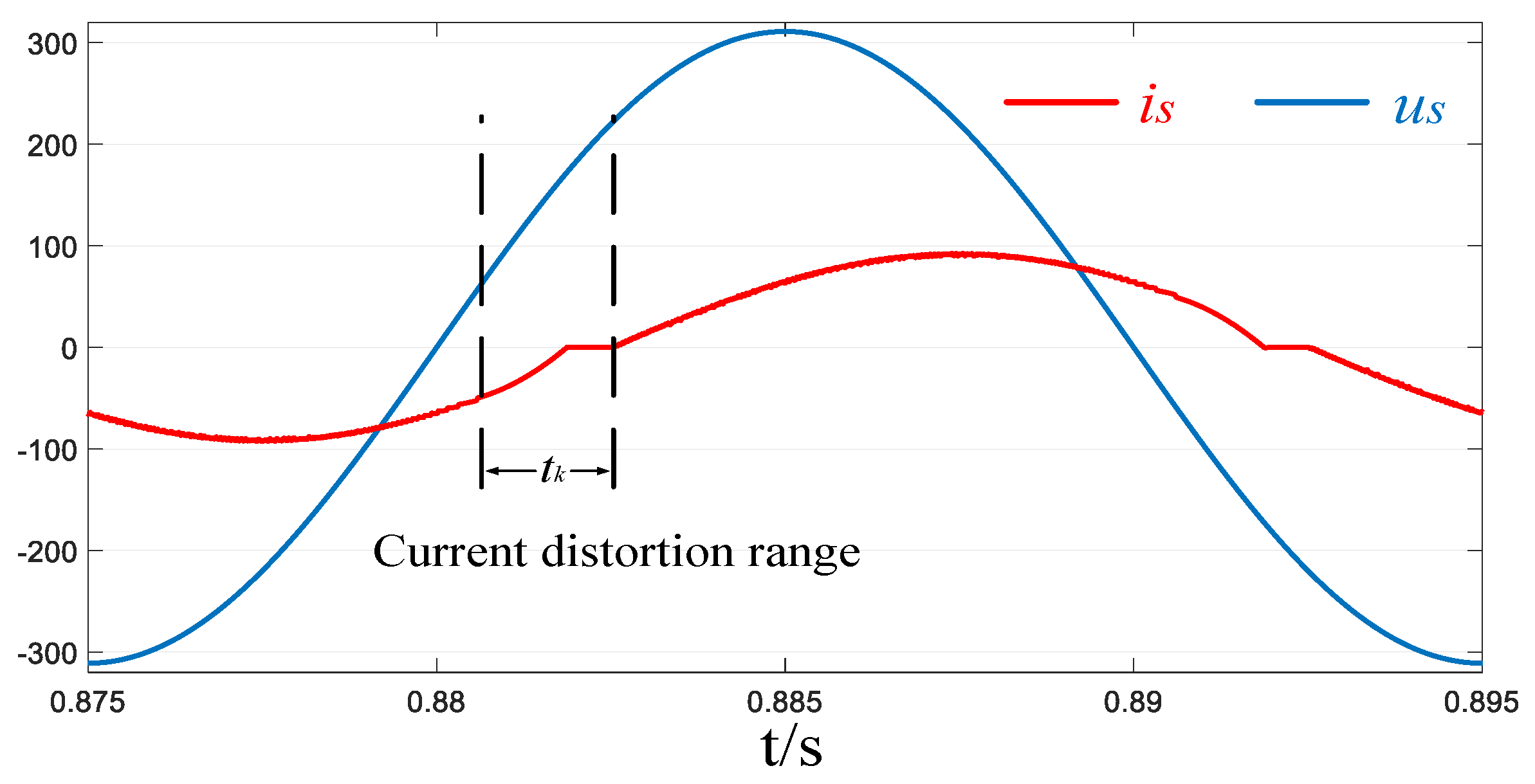

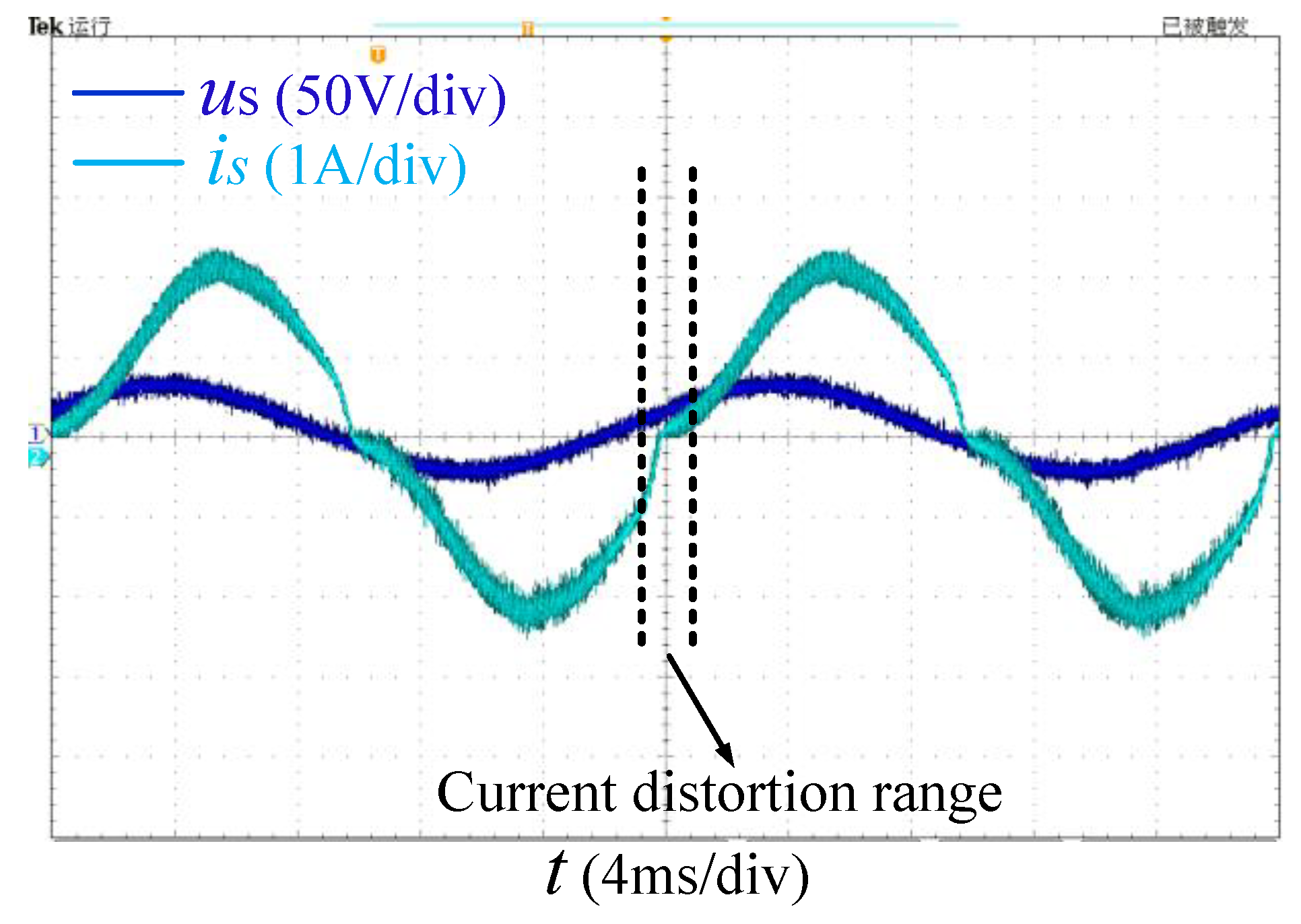

3.4. Distortion Characteristics of Input Current under Lagging Power Factor

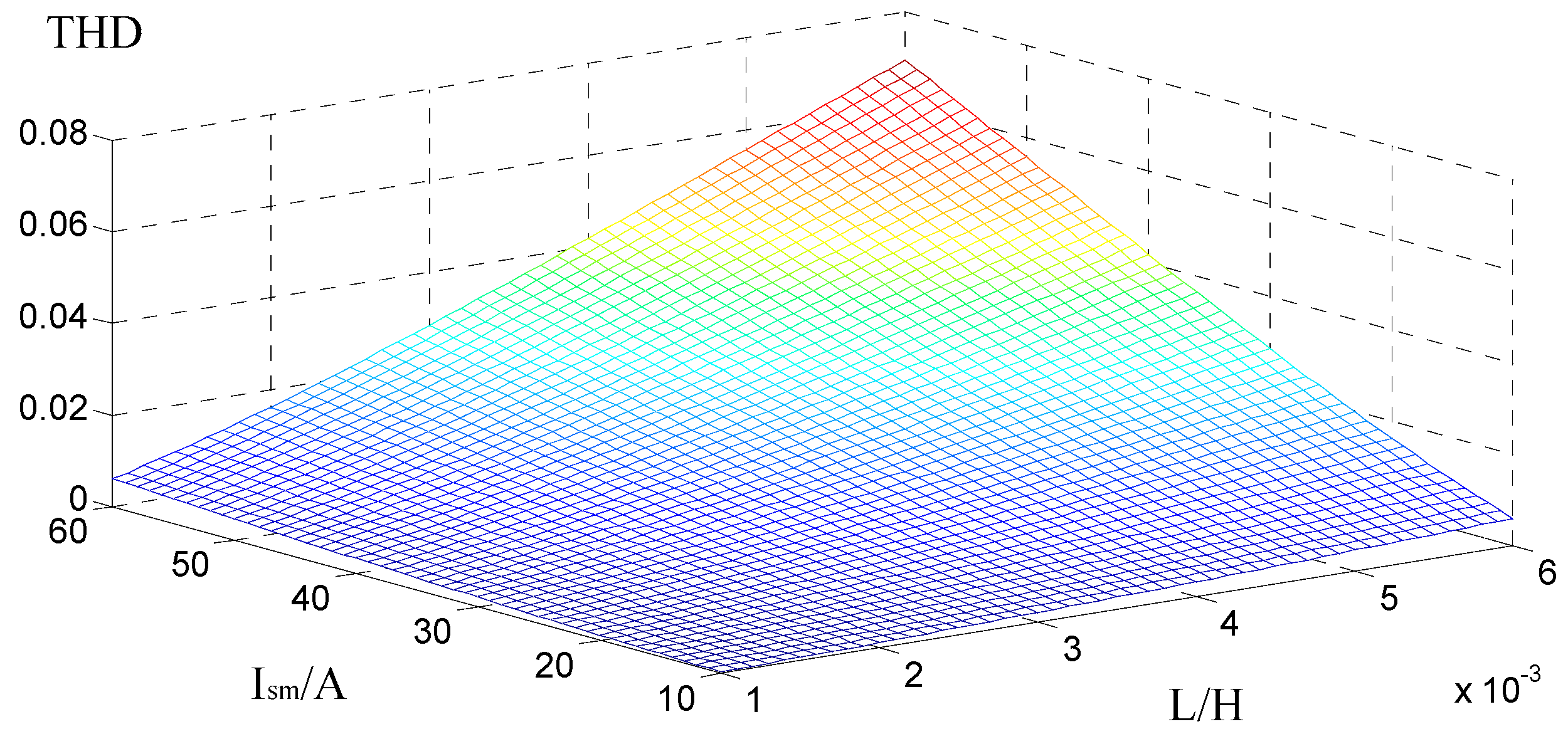

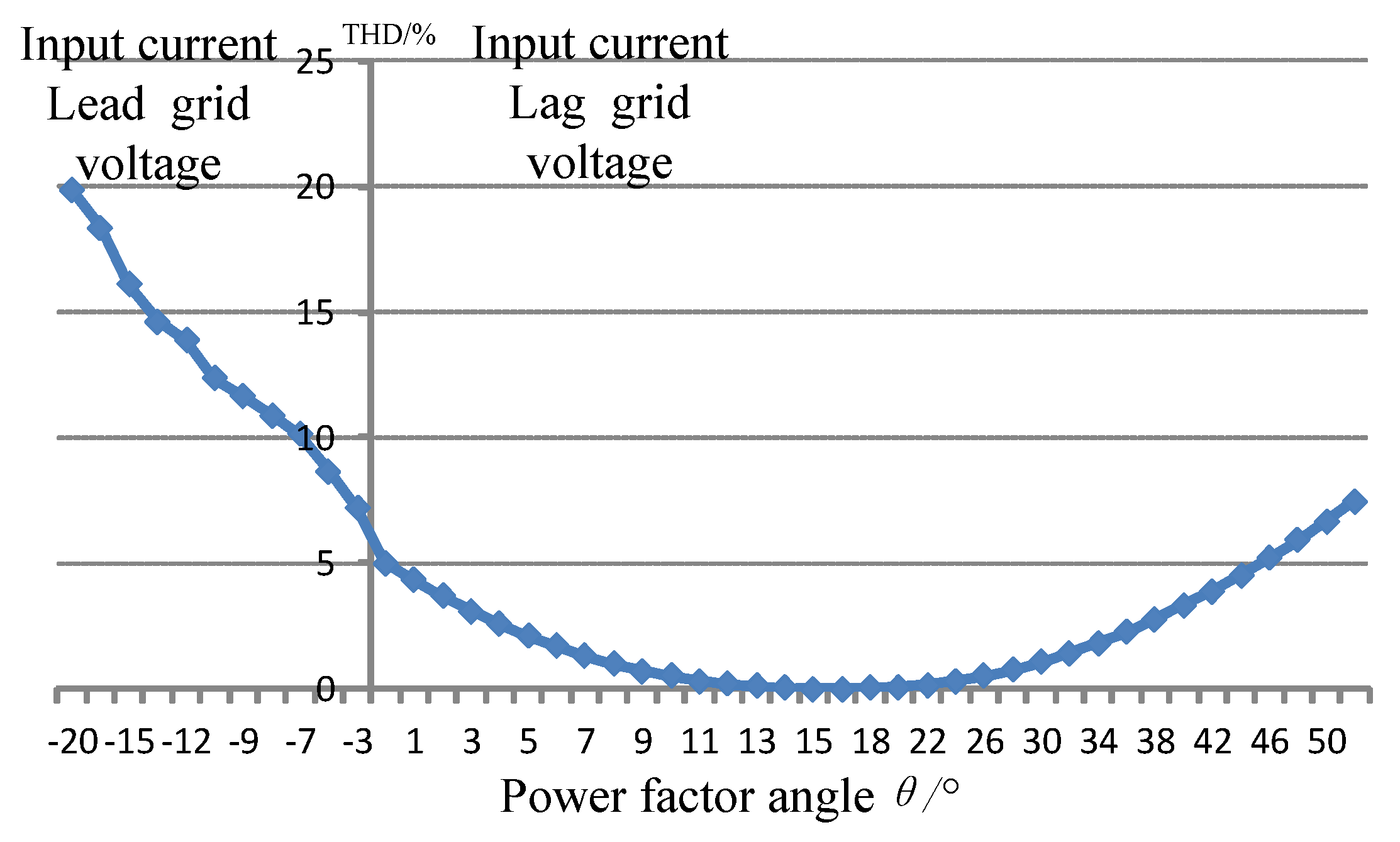

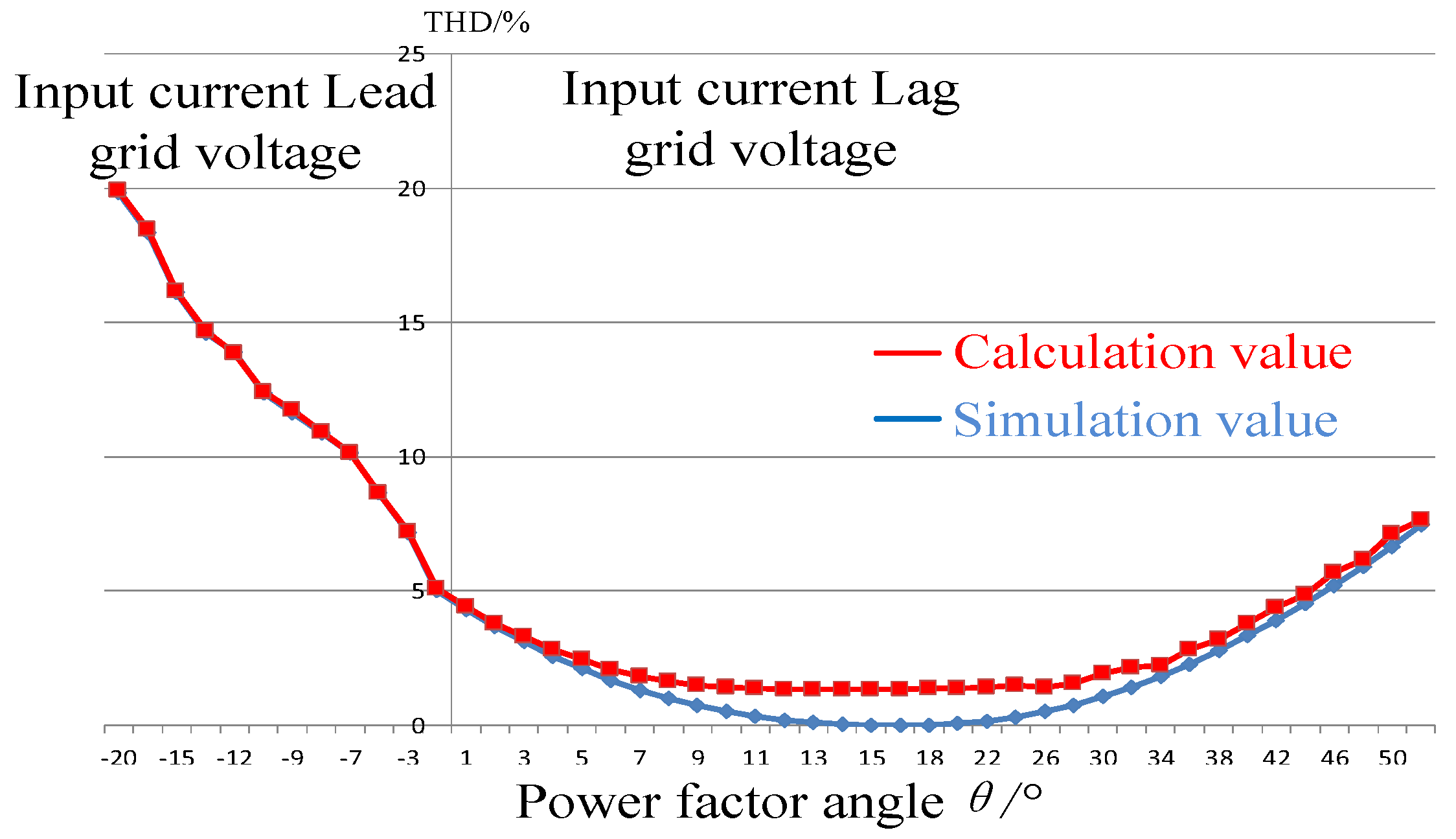

4. Constrain of Input Current on Filter Inductance, Input Current Amplitude, and Power Factor Angel Based on THD

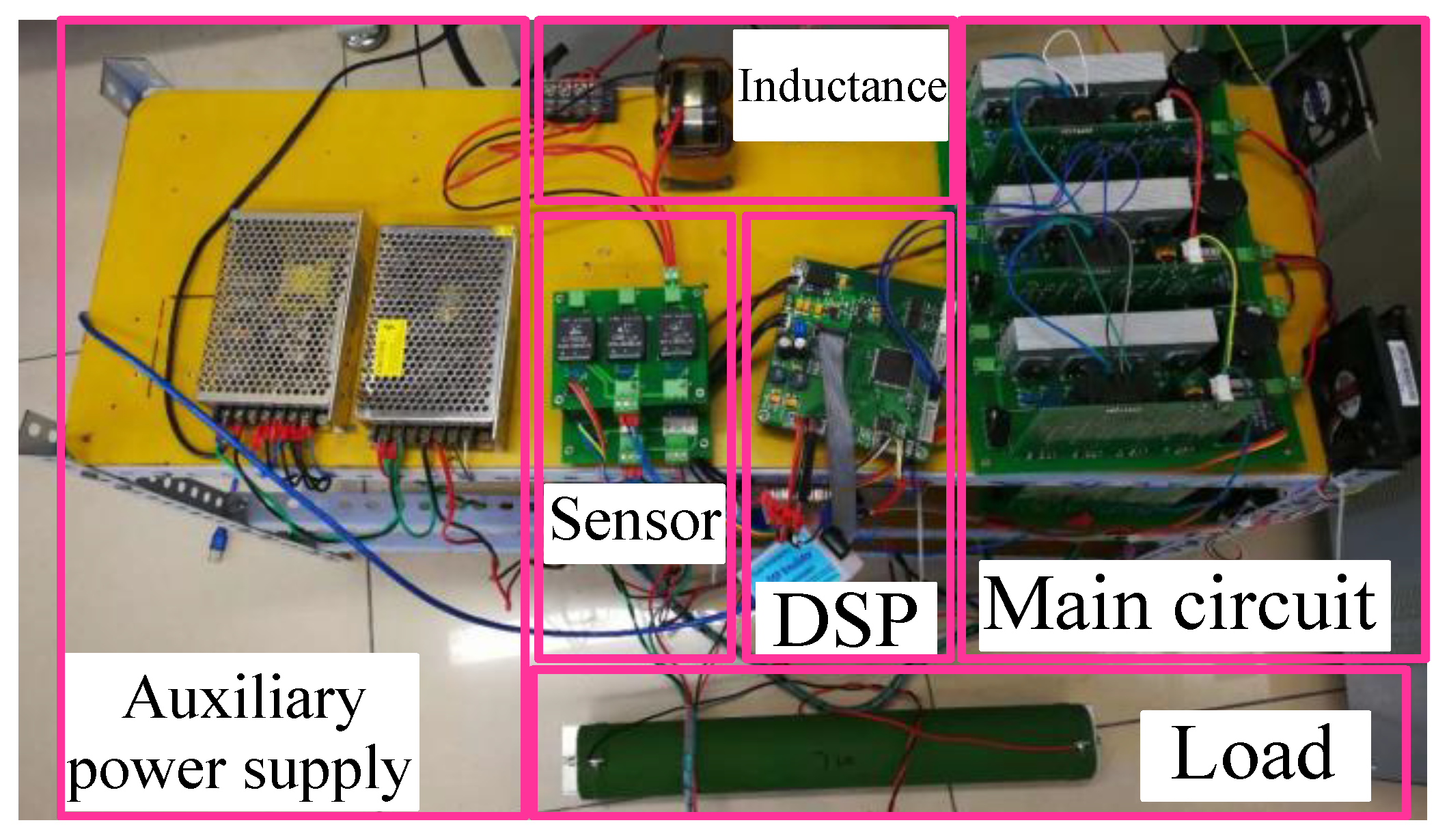

5. Simulation and Experimental Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Hamad, M.S.; Masoud, M.I.; Williams, B.W. Medium-Voltage 12-Pulse Converter: Output Voltage Harmonic Compensation Using a Series APF. IEEE Trans. Ind. Electron. 2014, 61, 43–52. [Google Scholar] [CrossRef]

- Sun, X. Study of a Novel Equivalent Model and a Long-Feeder Simulator-Based Active Power Filter in a Closed-Loop Distribution Feeder. IEEE Trans. Ind. Electron. 2016, 63, 2702–2712. [Google Scholar] [CrossRef]

- Lam, C.S.; Wang, L.S.; Ho, I.; Wong, M.C. Adaptive Thyristor-Controlled LC-Hybrid Active Power Filter for Reactive Power and Current Harmonics Compensation with Switching Loss Reduction. IEEE Trans. Ind. Electron. 2017, 32, 7577–7590. [Google Scholar] [CrossRef]

- Huber, L.; Jang, Y.; Jovanovic, M.M. Performance Evaluation of Bridgeless PFC Boost Rectifiers. IEEE Trans. Power Electron. 2008, 23, 1381–1390. [Google Scholar] [CrossRef]

- Liu, L.; Li, H.; Xue, Y.; Liu, W. Reactive Power Compensation and Optimization Strategy for Grid-Interactive Cascaded Photovoltaic Systems. IEEE Trans. Power Electron. 2015, 30, 188–202. [Google Scholar] [CrossRef]

- Singh, M.; Khadkikar, V.; Chandra, A.; Varma, R.K. Grid interconnection of renewable energy sources at the distribution level with power quality improvement features. IEEE Trans. Power Deliv. 2011, 26, 307–315. [Google Scholar] [CrossRef]

- Kisacikoglu, M.C.; Ozpineci, B.; Tolbert, L.M. EV/PHEV bidirectional charger assessment for V2G reactive power operation. IEEE Trans. Power Electron. 2013, 28, 5717–5727. [Google Scholar] [CrossRef]

- Wang, C.; Zhuang, Y.; Jiao, J.; Zhang, H.; Wang, C.; Cheng, H. Topologies and Control Strategies of Cascaded Bridgeless Multilevel Rectifiers. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 432–444. [Google Scholar] [CrossRef]

- Ma, H.; Lai, J.; Zheng, C.; Sun, P. A High-Efficiency Quasi-Single-Stage Bridgeless Electrolytic Capacitor-Free High-Power AC–DC Driver for Supplying Multiple LED Strings in Parallel. IEEE Trans. Power Electron. 2016, 8, 5825–5836. [Google Scholar] [CrossRef]

- Park, S.M.; Park, S.Y. Versatile unidirectional AC-DC converter with harmonic current and reactive power compensation for smart grid applications. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 2163–2170. [Google Scholar]

- Fardoun, A.; Ismail, E.; Al-Saffar, M.; Sabzali, A. A Bridgeless Resonant Pseudoboost PFC Rectifier. IEEE Trans. Power Electron. 2014, 11, 5949–5960. [Google Scholar] [CrossRef]

- Zhao, B.; Abramovitz, A.; Smedley, K. Family of Bridgeless Buck-Boost PFC Rectifiers. IEEE Trans. Power Electron. 2015, 30, 6524–6527. [Google Scholar] [CrossRef]

- Lin, X.; Wang, F. New Bridgeless Buck PFC Converter with Improved Input Current and Power Factor. IEEE Trans. Ind. Electron. 2018, 10, 7730–7740. [Google Scholar] [CrossRef]

- Liu, Y.; Sun, Y.; Su, M. A Control Method for Bridgeless Cuk/Sepic PFC Rectifier to Achieve Power Decoupling. IEEE Trans. Ind. Electron. 2017, 9, 7272–7276. [Google Scholar] [CrossRef]

- Jian, J.; Cong, W. The research of new cascade bridgeless multi-level rectifier. In Proceedings of the 2014 International Power Electronics and Application Conference and Exposition, Shanghai, China, 5–8 December 2014; pp. 1513–1518. [Google Scholar]

- Chang, W.; Cong, W.; Wang, K.; Hong, C.; Liang, Y. New control algorithm of bridgeless PFC. Adv. Technol. Electr. Eng. Energy 2015, 34, 18–23. [Google Scholar]

- Park, S.M.; Park, S.Y. Versatile control of unidirectional AC–DC boost converters for power quality mitigation. IEEE Trans. Power Electron. 2015, 30, 4738–4749. [Google Scholar] [CrossRef]

- Kotsopoulos, A.; Heskes, P.J.M.; Jansen, M.J. Zero-crossing distortion in grid-connected PV inverters. IEEE Trans. Ind. Electron. 2005, 52, 558–565. [Google Scholar] [CrossRef]

- Wu, F.; Sun, B.; Zhao, K.; Sun, L. Analysis and Solution of Current Zero-Crossing Distortion with Unipolar Hysteresis Current Control in Grid-Connected Inverter. IEEE Trans. Ind. Electron. 2013, 60, 4450–4457. [Google Scholar] [CrossRef]

| Mode I | Mode II | Mode III | Mode IV |

|---|---|---|---|

| is > 0 | is < 0 | ||

| ucon = Udc | ucon = 0 | ucon = −Udc | ucon = 0 |

| D1, DS2 conductivity | S1, DS2 conductivity | D2, DS1 conductivity | S2, DS1 conductivity |

| Parameters | Value |

|---|---|

| Input voltage (RMS) | 220 V |

| Source voltage frequency | 50 Hz |

| Input current (RMS) | 65 A |

| Input inductance | 3 mH |

| Switching frequency | 5 kHz |

| Load side capacitance | 4700 uF |

| DC-link resistance | 0.09 Ω |

| DC-link voltage | 400 V |

| Parameter | Value |

|---|---|

| Input voltage (RMS) | 24 V |

| Source voltage frequency | 50 Hz |

| Input current (RMS) | 1.37 A |

| Input inductance | 5 mH |

| Switching frequency | 5 kHz |

| Load side capacitance | 2200 uF |

| DC-link resistance | 50 Ω |

| DC-link voltage | 40 V |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, J.; Liu, Y.; Zhuang, Y.; Wang, C. Analysis to Input Current Zero Crossing Distortion of Bridgeless Rectifier Operating under Different Power Factors. Energies 2018, 11, 2447. https://doi.org/10.3390/en11092447

Liu J, Liu Y, Zhuang Y, Wang C. Analysis to Input Current Zero Crossing Distortion of Bridgeless Rectifier Operating under Different Power Factors. Energies. 2018; 11(9):2447. https://doi.org/10.3390/en11092447

Chicago/Turabian StyleLiu, Jinqi, Yizhou Liu, Yuan Zhuang, and Cong Wang. 2018. "Analysis to Input Current Zero Crossing Distortion of Bridgeless Rectifier Operating under Different Power Factors" Energies 11, no. 9: 2447. https://doi.org/10.3390/en11092447

APA StyleLiu, J., Liu, Y., Zhuang, Y., & Wang, C. (2018). Analysis to Input Current Zero Crossing Distortion of Bridgeless Rectifier Operating under Different Power Factors. Energies, 11(9), 2447. https://doi.org/10.3390/en11092447