PLL-Less Three-Phase Four-Wire SAPF with STF-dq0 Technique for Harmonics Mitigation under Distorted Supply Voltage and Unbalanced Load Conditions

Abstract

1. Introduction

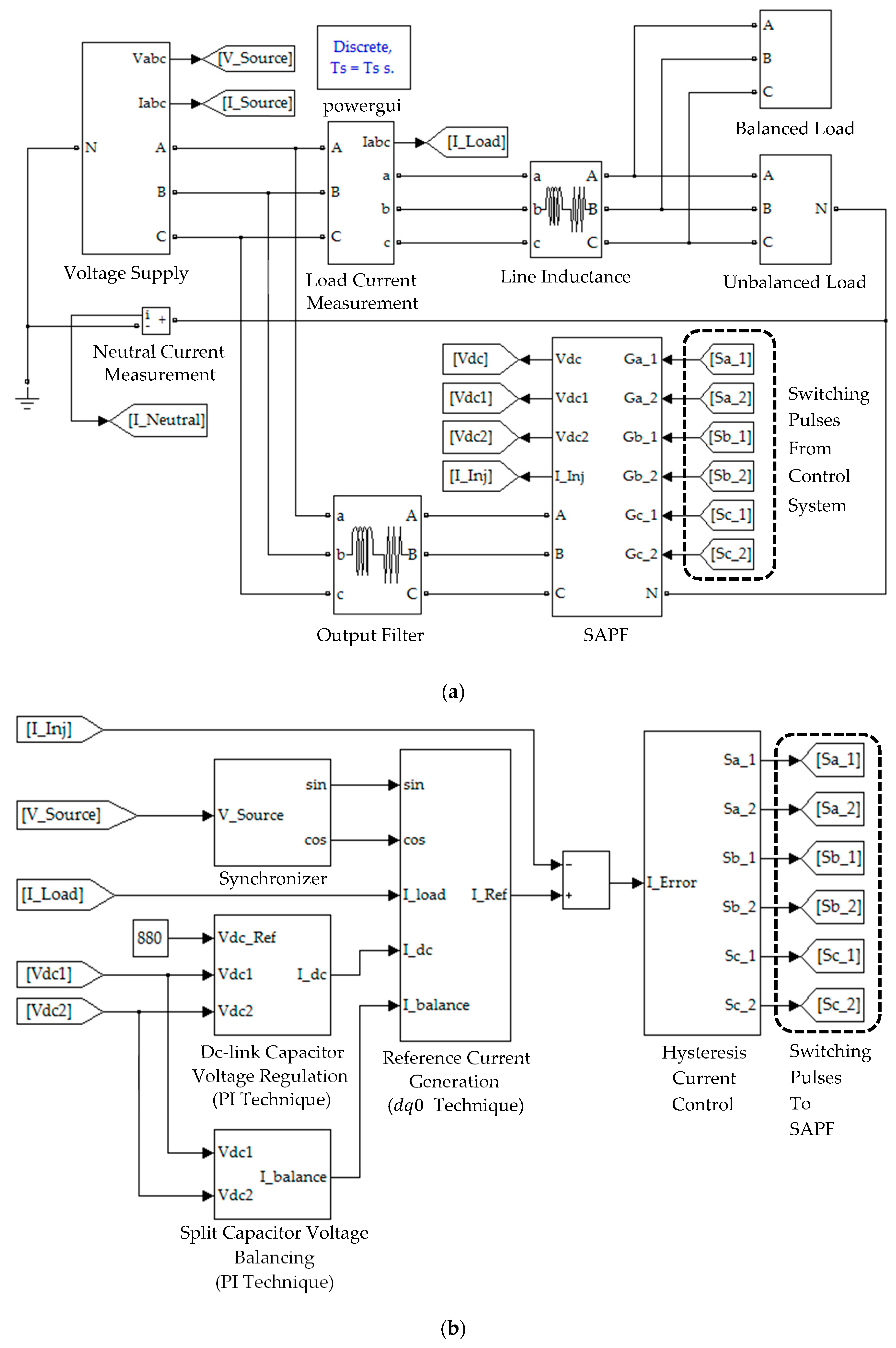

2. Three-Phase Three-Leg Four-Wire Shunt Active Power Filter: Arrangement of Power Circuits and Control Strategies

3. Working Principle of the Standard dq0 Technique

4. Working Principle the Proposed STF-dq0 Technique

5. Results and Discussion

5.1. Sinusoidal-Balanced Source Voltage (Scenario A)

5.2. Non-Sinusoidal-Balanced Source Voltage (Scenario B)

5.3. Sinusoidal-Unbalanced Source Voltage (Scenario C)

5.4. Non-Sinusoidal-Unbalanced Source Voltage (Scenario D)

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kale, M.; Ozdemir, E. A new hysteresis band current control technique for a shunt active filter. Turk. J. Electr. Eng. Comput. Sci. 2015, 23, 654–665. [Google Scholar] [CrossRef]

- Ucar, M.; Ozdemir, E. Control of a 3-phase 4-leg active power filter under non-ideal mains voltage condition. Electr. Power Syst. Res. 2008, 78, 58–73. [Google Scholar] [CrossRef]

- Escobar, G.; Valdez, A.A.; Torres-Olguin, R.E.; Martinez-Montejano, M.F. A model-based controller for a three-phase four-wire shunt active filter with compensation of the neutral line current. IEEE Trans. Power Electron. 2007, 22, 2261–2270. [Google Scholar] [CrossRef]

- Bhattacharya, A.; Chakraborty, C.; Bhattacharya, S. Shunt compensation—Reviewing traditional methods of reference current generation. IEEE Ind. Electron. Mag. 2009, 3, 38–49. [Google Scholar] [CrossRef]

- Green, T.C.; Marks, J.H. Control techniques for active power filters. IEE Proc. Electr. Power Appl. 2005, 152, 369–381. [Google Scholar] [CrossRef]

- Kale, M.; Ozdemir, E. An adaptive hysteresis band current controller for shunt active power filter. Electr. Power Syst. Res. 2005, 73, 113–119. [Google Scholar] [CrossRef]

- Mikkili, S.; Panda, A.K. Instantaneous active and reactive power and current strategies for current harmonics cancellation in 3-ph 4-wire SHAF with both PI and fuzzy controllers. Energy Power Eng. 2011, 3, 285–298. [Google Scholar] [CrossRef]

- Eskandarian, N.; Beromi, Y.A.; Farhangi, S. Improvement of dynamic behavior of shunt active power filter using fuzzy instantaneous power theory. J. Power Electron. 2014, 14, 1303–1313. [Google Scholar] [CrossRef]

- Rodriguez, P.; Pou, J.; Bergas, J.; Candela, J.I.; Burgos, R.P.; Boroyevich, D. Decoupled double synchronous reference frame PLL for power converters control. IEEE Trans. Power Electron. 2007, 22, 584–592. [Google Scholar] [CrossRef]

- Campanhol, L.B.G.; Silva, S.A.O.; Goedtel, A. Application of shunt active power filter for harmonic reduction and reactive power compensation in three-phase four-wire systems. IET Power Electron. 2014, 7, 2825–2836. [Google Scholar] [CrossRef]

- Ucar, M.; Ozdemir, S.; Ozdemir, E. A unified series-parallel active filter system for nonperiodic disturbances. Turk. J. Electr. Eng. Comput. Sci. 2011, 19, 575–596. [Google Scholar]

- Senini, S.; Wolfs, P.J. Analysis and design of a multiple-loop control system for a hybrid active filter. IEEE Trans. Ind. Electron. 2002, 49, 1283–1292. [Google Scholar] [CrossRef]

- Hoon, Y.; Radzi, M.A.M.; Hassan, M.K.; Mailah, N.F. Three-phase three-level shunt active power filter with simplified synchronous reference frame. In Proceedings of the IEEE Industrial Electronics and Applications Conference, Kota Kinabalu, Sabah, Malaysia, 20–22 November 2016; pp. 1–6. [Google Scholar]

- Monfared, M.; Golestan, S.; Guerrero, J.M. A new synchronous reference frame-based method for single-phase shunt active power filters. J. Power Electron. 2013, 13, 692–700. [Google Scholar] [CrossRef]

- Jain, N.; Gupta, A. Comparison between two compensation current control methods of shunt active power filter. Int. J. Eng. Res. Gen. Sci. 2014, 2, 603–615. [Google Scholar]

- Abdulsalam, M.; Poure, P.; Karimi, S.; Saadate, S. New digital reference current generation for shunt active power filter under distorted voltage conditions. Electr. Power Syst. Res. 2009, 79, 759–765. [Google Scholar] [CrossRef]

- Biricik, S.; Redif, S.; Özerdem, Ö.C.; Khadem, S.K.; Basu, M. Real-time control of shunt active power filter under distorted grid voltage and unbalanced load condition using self-tuning filter. IET Power Electron. 2014, 7, 1895–1905. [Google Scholar] [CrossRef]

- Djazia, K.; Krim, F.; Chaoui, A.; Sarra, M. Active power filtering using the zdpc method under unbalanced and distorted grid voltage conditions. Energies 2015, 8, 1584–1605. [Google Scholar] [CrossRef]

- Jain, S.K.; Agrawal, P.; Gupta, H.O. Design simulation and experimental investigations, on a shunt active power filter for harmonics, and reactive power compensation. Electr. Power Compon. Syst. 2003, 31, 671–692. [Google Scholar] [CrossRef]

- Krim, F. Parameters estimation of shunt active filter for power quality improvement. In Proceedings of the 5th International Power Engineering and Optimization Conference (PEOCO), Shah Alam, Selangor, Malaysia, 6–7 June 2011; pp. 306–311. [Google Scholar]

- Jain, S.K.; Agrawal, P.; Gupta, H.O. Fuzzy logic controlled shunt active power filter for power quality improvement. IEE Proc. Electr. Power Appl. 2002, 149, 317–328. [Google Scholar] [CrossRef]

- Institute of Electrical and Electronics Engineers (IEEE). IEEE recommended practice and requirement for harmonic control in electric power systems. In IEEE Std 519-2014 (Revision of IEEE Std 519-1992); IEEE: Piscataway, NJ, USA, 2014; pp. 1–29. [Google Scholar]

| Nonlinear Load | Load Descriptions | |

|---|---|---|

| Load 1: Unbalanced single-phase load | Phase | Uncontrolled single-phase rectifier feeding a parallel connected 80 Ω resistor and 1500 μF capacitor |

| Phase | Uncontrolled single-phase rectifier feeding a series connected 20 Ω resistor and 50 mH inductor | |

| Phase | Uncontrolled single-phase rectifier feeding a parallel connected 60 Ω resistor and 1000 μF capacitor | |

| Load 2: Unbalanced single-phase load and balanced three-phase load connected in parallel (refer Figure 4a) | Phase | Uncontrolled single-phase rectifier feeding a series connected 30 Ω resistor and 30 mH inductor |

| Phase | Uncontrolled single-phase rectifier feeding a parallel connected 80 Ω resistor and 1500 μF capacitor | |

| Phase | Uncontrolled single-phase rectifier feeding a series connected 20 Ω resistor and 50 mH inductor | |

| Uncontrolled three-phase rectifier feeding a series connected 50 Ω resistor and 100 mH inductor | ||

| Performance Parameter | Load 1 | Load 2 | ||||

|---|---|---|---|---|---|---|

| Phase | Phase | Phase | Phase | Phase | Phase | |

| Before connecting SAPF | ||||||

| THD value (%) | 118.27 | 25.99 | 114.73 | 13.46 | 45.53 | 14.73 |

| Phase difference (°) | 9.80 | 15.60 | 7.50 | 8.50 | 6.80 | 10.90 |

| Power factor | 0.636 | 0.932 | 0.651 | 0.980 | 0.903 | 0.971 |

| After connecting SAPF with the proposed STF-dq0 technique | ||||||

| THD value (%) | 2.97 | 2.81 | 2.81 | 0.98 | 0.96 | 1.03 |

| Phase difference (°) | 0.70 | 0.30 | 0.40 | 0.00 | 0.20 | 0.20 |

| Power factor | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 |

| After connecting SAPF with the standard dq0 technique | ||||||

| THD value (%) | 2.93 | 2.78 | 2.92 | 1.02 | 0.97 | 1.01 |

| Phase difference (°) | 0.80 | 0.10 | 0.60 | 0.00 | 0.10 | 0.20 |

| Power factor | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 |

| Performance Parameter | Load 1 | Load 2 | ||||

|---|---|---|---|---|---|---|

| Phase | Phase | Phase | Phase | Phase | Phase | |

| Before connecting SAPF | ||||||

| THD value (%) | 123.98 | 35.29 | 120.11 | 15.63 | 46.21 | 20.71 |

| Phase difference (°) | 10.10 | 10.40 | 8.20 | 11.10 | 12.10 | 11.80 |

| Power factor | 0.618 | 0.927 | 0.633 | 0.969 | 0.887 | 0.958 |

| After connecting SAPF with the proposed STF-dq0 technique | ||||||

| THD value (%) | 2.91 | 2.90 | 2.73 | 0.92 | 0.95 | 0.98 |

| Phase difference (°) | 0.80 | 0.20 | 0.30 | 0.10 | 0.20 | 0.20 |

| Power factor | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 |

| After connecting SAPF with the standard dq0 technique | ||||||

| THD value (%) | 8.56 | 8.08 | 7.41 | 6.75 | 6.92 | 7.33 |

| Phase difference (°) | 0.80 | 0.10 | 0.50 | 0.10 | 0.20 | 0.10 |

| Power factor | 0.996 | 0.997 | 0.997 | 0.997 | 0.997 | 0.997 |

| Performance Parameter | Load 1 | Load 2 | ||||

|---|---|---|---|---|---|---|

| Phase | Phase | Phase | Phase | Phase | Phase | |

| Before connecting SAPF | ||||||

| THD value (%) | 118.27 | 25.99 | 114.73 | 12.84 | 45.09 | 13.77 |

| Phase difference (°) | 9.80 | 15.60 | 7.50 | 9.90 | 7.40 | 9.40 |

| Power factor | 0.636 | 0.932 | 0.651 | 0.977 | 0.904 | 0.977 |

| After connecting SAPF with the proposed STF-dq0 technique | ||||||

| THD value (%) | 2.86 | 2.79 | 2.89 | 1.11 | 1.09 | 1.17 |

| Phase difference (°) | 0.30 | 0.20 | 0.50 | 0.30 | 0.40 | 0.20 |

| Power factor | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 |

| After connecting SAPF with the standard dq0 technique | ||||||

| THD value (%) | 5.20 | 5.09 | 5.72 | 3.24 | 2.97 | 3.13 |

| Phase difference (°) | 0.30 | 0.10 | 0.30 | 0.90 | 0.10 | 0.90 |

| Power factor | 0.998 | 0.998 | 0.998 | 0.999 | 0.999 | 0.999 |

| Performance Parameter | Load 1 | Load 2 | ||||

|---|---|---|---|---|---|---|

| Phase | Phase | Phase | Phase | Phase | Phase | |

| Before connecting SAPF | ||||||

| THD value (%) | 116.53 | 33.38 | 121.45 | 19.78 | 49.10 | 13.89 |

| Phase difference (°) | 10.40 | 11.40 | 8.40 | 8.70 | 11.90 | 8.20 |

| Power factor | 0.640 | 0.929 | 0.628 | 0.969 | 0.878 | 0.980 |

| After connecting SAPF with the proposed STF-dq0 technique | ||||||

| THD value (%) | 2.97 | 2.60 | 2.91 | 1.09 | 1.07 | 1.12 |

| Phase difference (°) | 0.40 | 0.10 | 0.50 | 0.20 | 0.50 | 0.20 |

| Power factor | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 | 0.999 |

| After connecting SAPF with the standard dq0 technique | ||||||

| THD value (%) | 8.64 | 5.87 | 5.74 | 6.85 | 5.14 | 5.04 |

| Phase difference (°) | 0.20 | 0.50 | 0.70 | 0.40 | 0.40 | 1.30 |

| Power factor | 0.996 | 0.998 | 0.998 | 0.997 | 0.998 | 0.998 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hoon, Y.; Mohd Radzi, M.A. PLL-Less Three-Phase Four-Wire SAPF with STF-dq0 Technique for Harmonics Mitigation under Distorted Supply Voltage and Unbalanced Load Conditions. Energies 2018, 11, 2143. https://doi.org/10.3390/en11082143

Hoon Y, Mohd Radzi MA. PLL-Less Three-Phase Four-Wire SAPF with STF-dq0 Technique for Harmonics Mitigation under Distorted Supply Voltage and Unbalanced Load Conditions. Energies. 2018; 11(8):2143. https://doi.org/10.3390/en11082143

Chicago/Turabian StyleHoon, Yap, and Mohd Amran Mohd Radzi. 2018. "PLL-Less Three-Phase Four-Wire SAPF with STF-dq0 Technique for Harmonics Mitigation under Distorted Supply Voltage and Unbalanced Load Conditions" Energies 11, no. 8: 2143. https://doi.org/10.3390/en11082143

APA StyleHoon, Y., & Mohd Radzi, M. A. (2018). PLL-Less Three-Phase Four-Wire SAPF with STF-dq0 Technique for Harmonics Mitigation under Distorted Supply Voltage and Unbalanced Load Conditions. Energies, 11(8), 2143. https://doi.org/10.3390/en11082143