HIL Co-Simulation of Finite Set-Model Predictive Control Using FPGA for a Three-Phase VSI System

Abstract

:1. Introduction

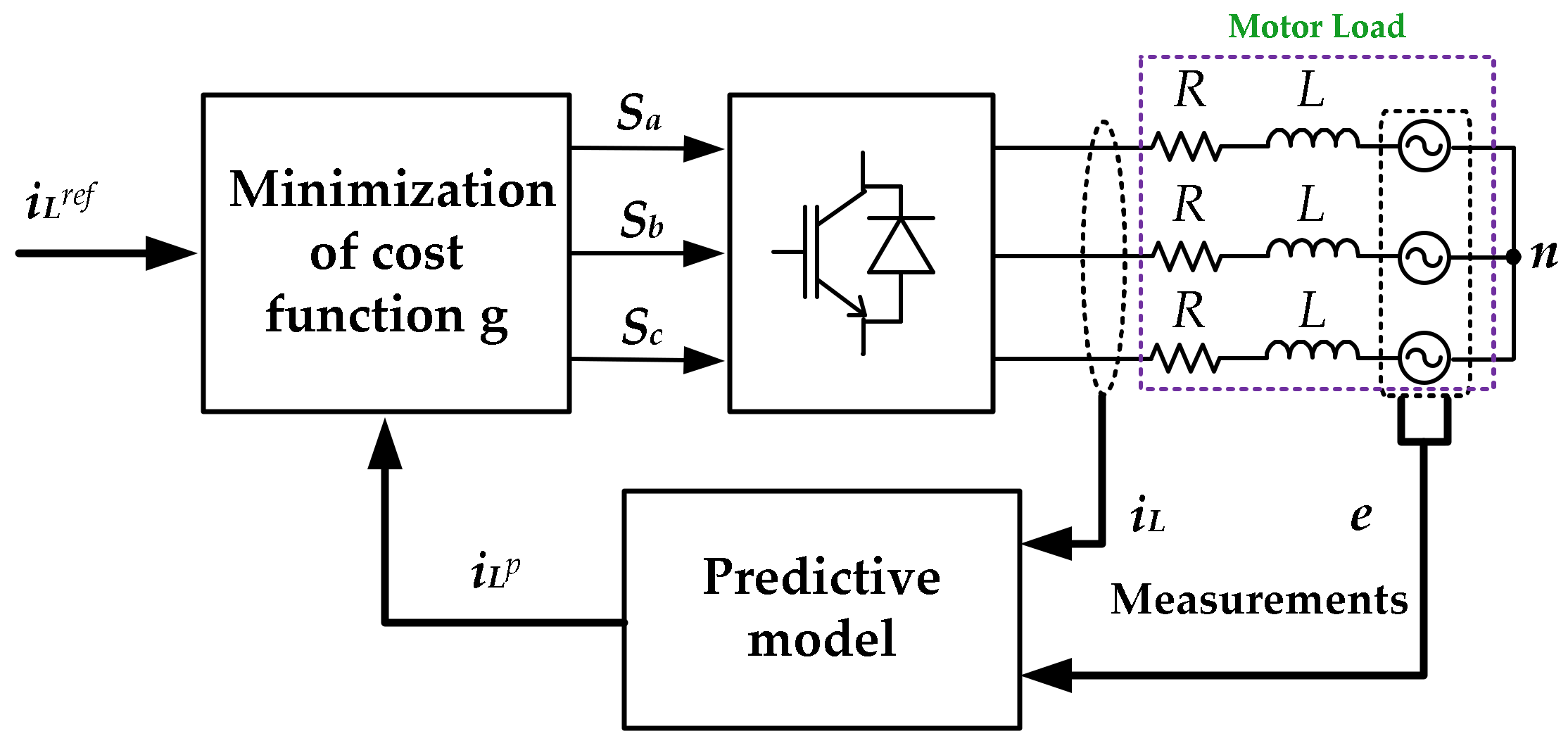

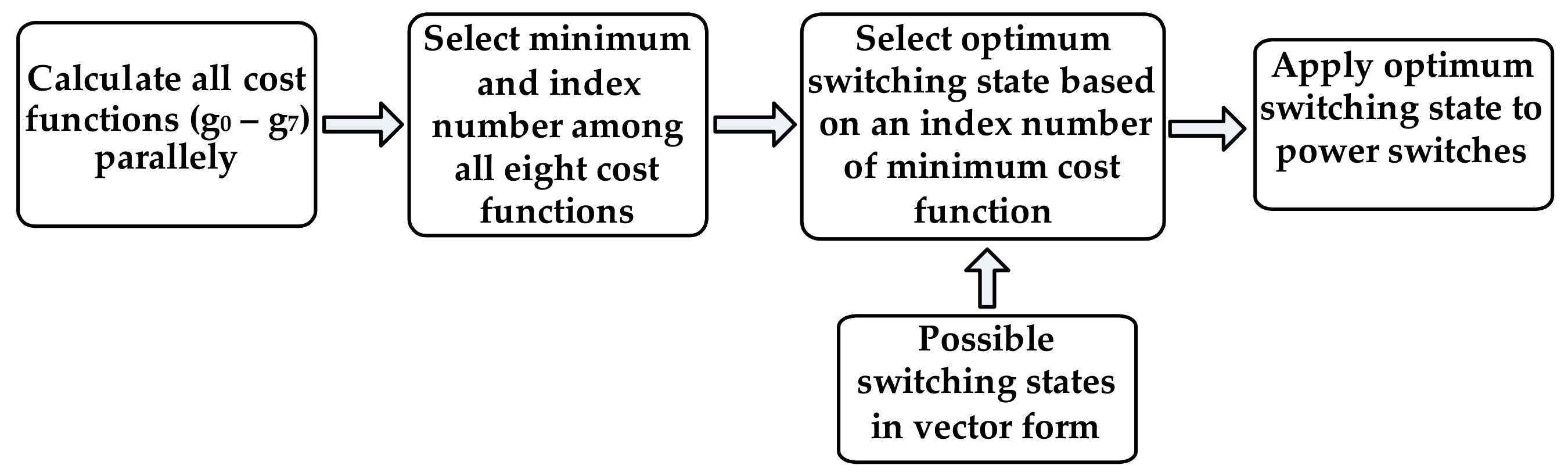

2. FS-MPC

2.1. Inverter System

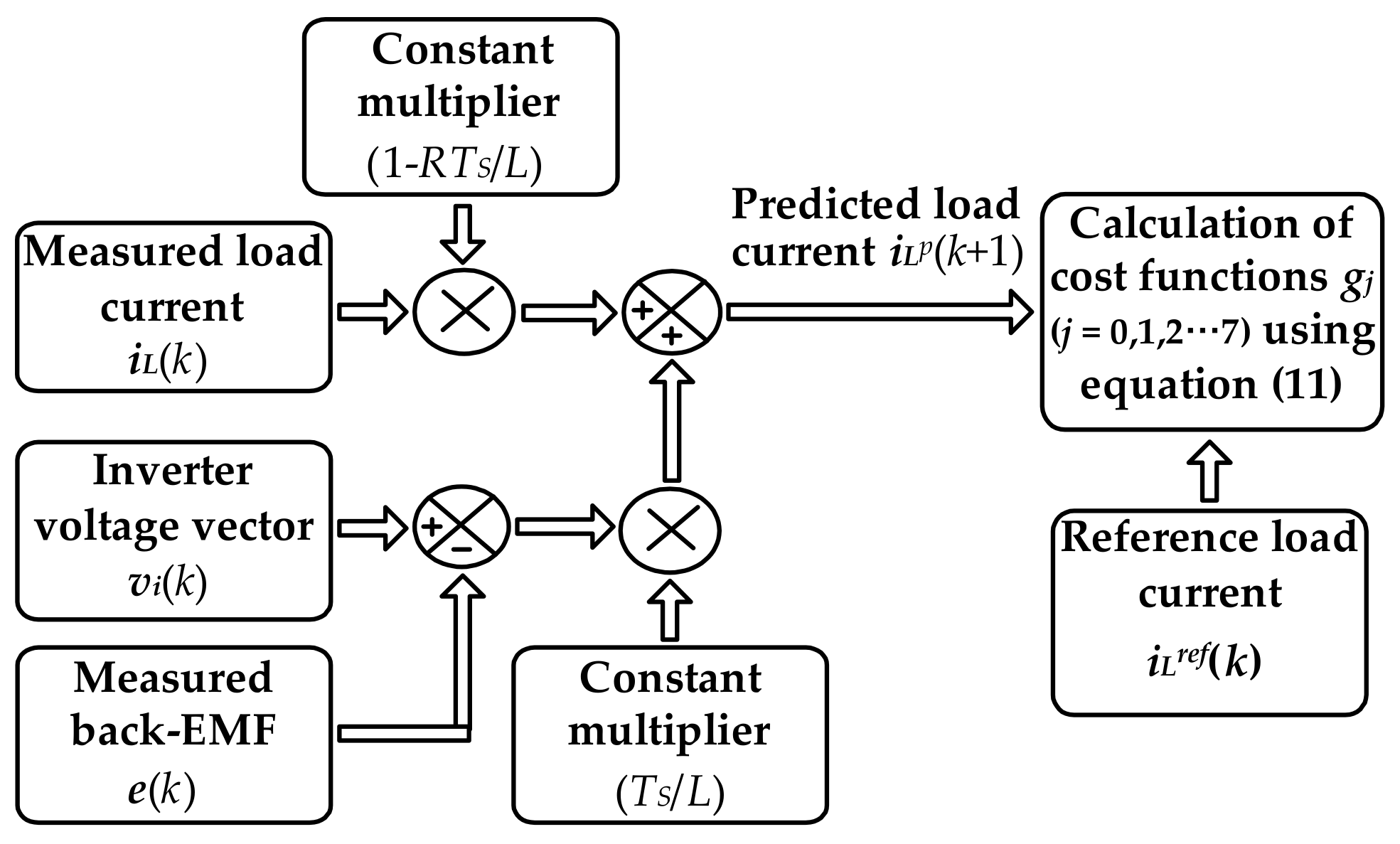

2.2. Predictive Model

2.3. Cost Function

- The value of reference current iLref(k) is obtained from an outer control loop at the sampling instant k.

- The load current iL(k) and the back-EMF voltage e(k) are measured at the sampling instant k.

- The discrete-time model of the load (Equation (10)) is used to predict the future value of the load current iLp(k + 1) in the next sampling instant k + 1 for each of the possible switching states of the inverter.

- Then, the cost function is evaluated for all the predicted load currents, which is a function of the reference current iref(k) and the predicted load current iLp(k + 1).

- The switching state which minimizes the cost function is selected and applied to the inverter in the next sampling interval.

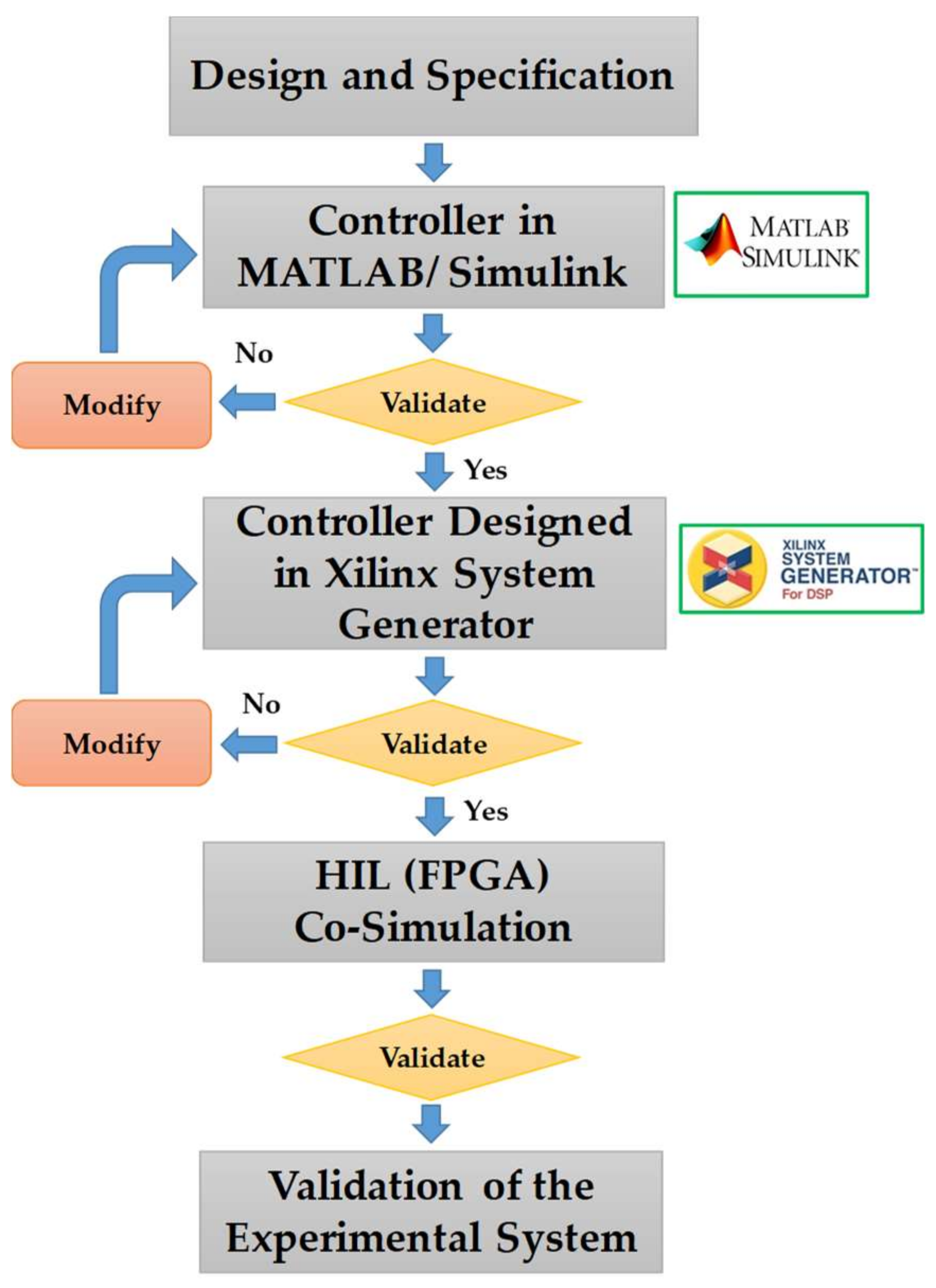

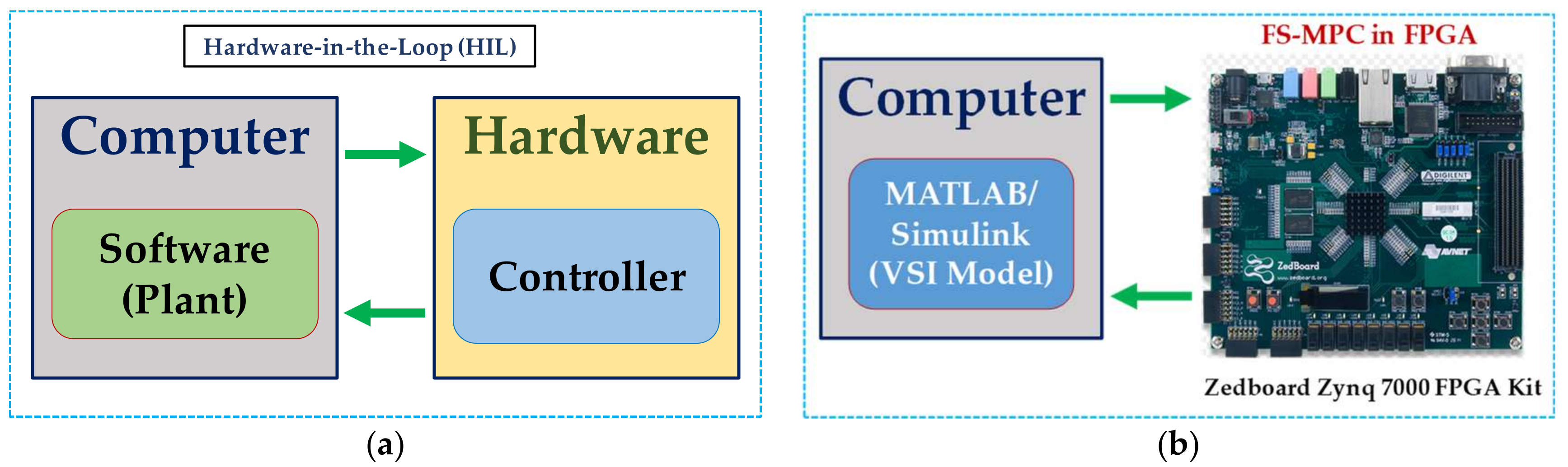

3. HIL Co-Simulation

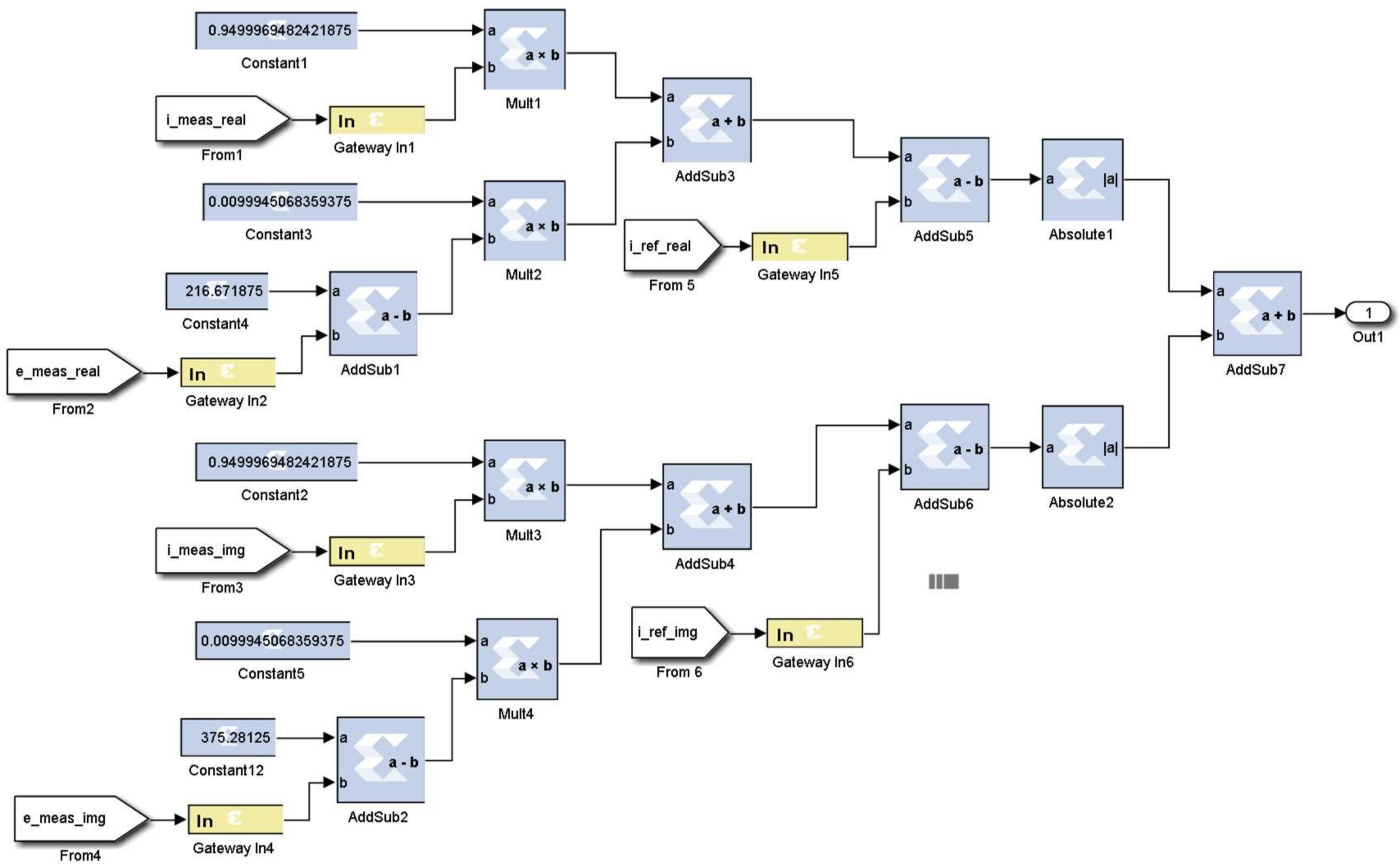

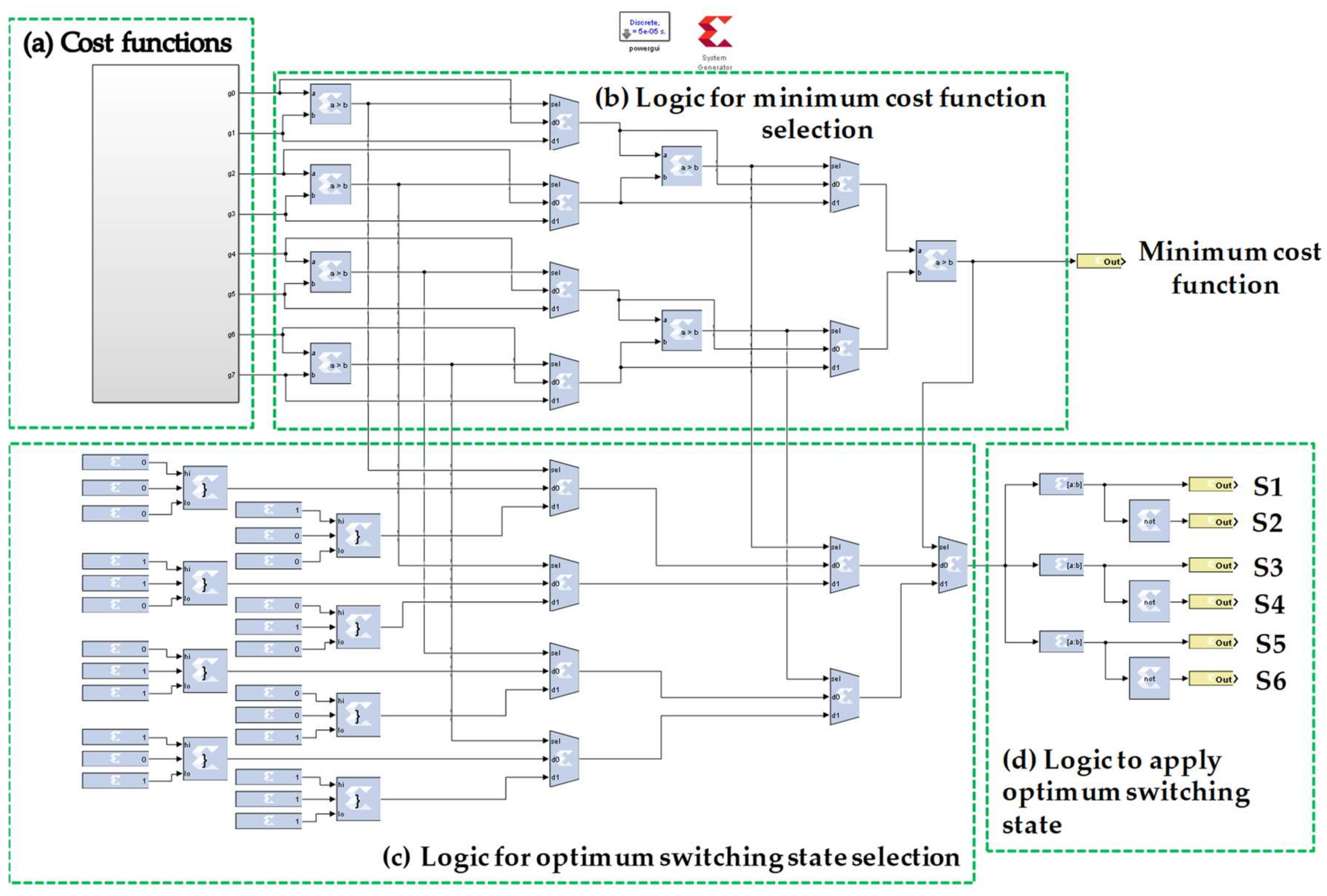

3.1. Modelling of the FS-MPC in XSG

3.1.1. Computation of the Cost Function

3.1.2. Selection of Optimum Switching Signals

3.2. Co-simulation

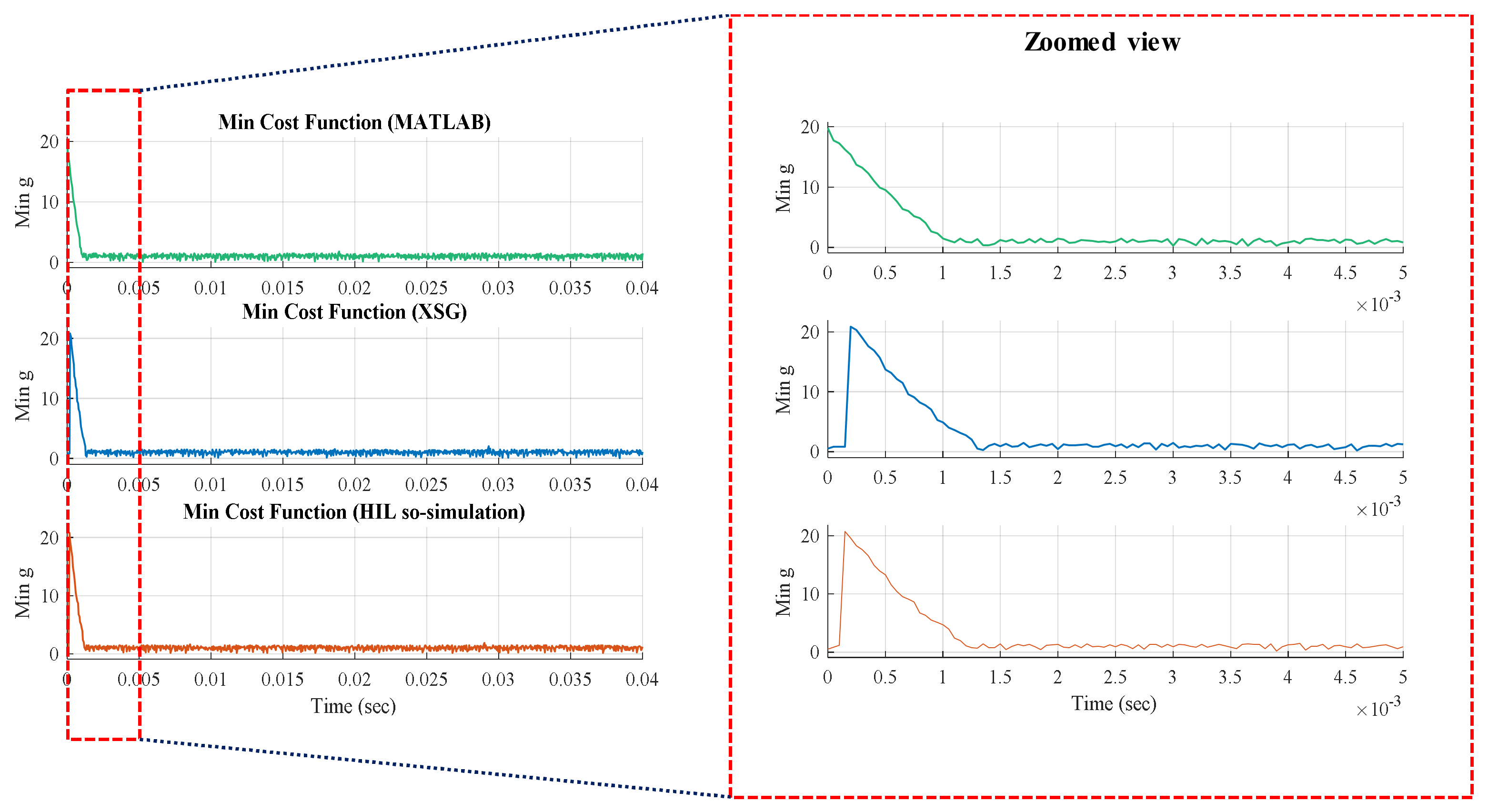

4. Results and Discussion

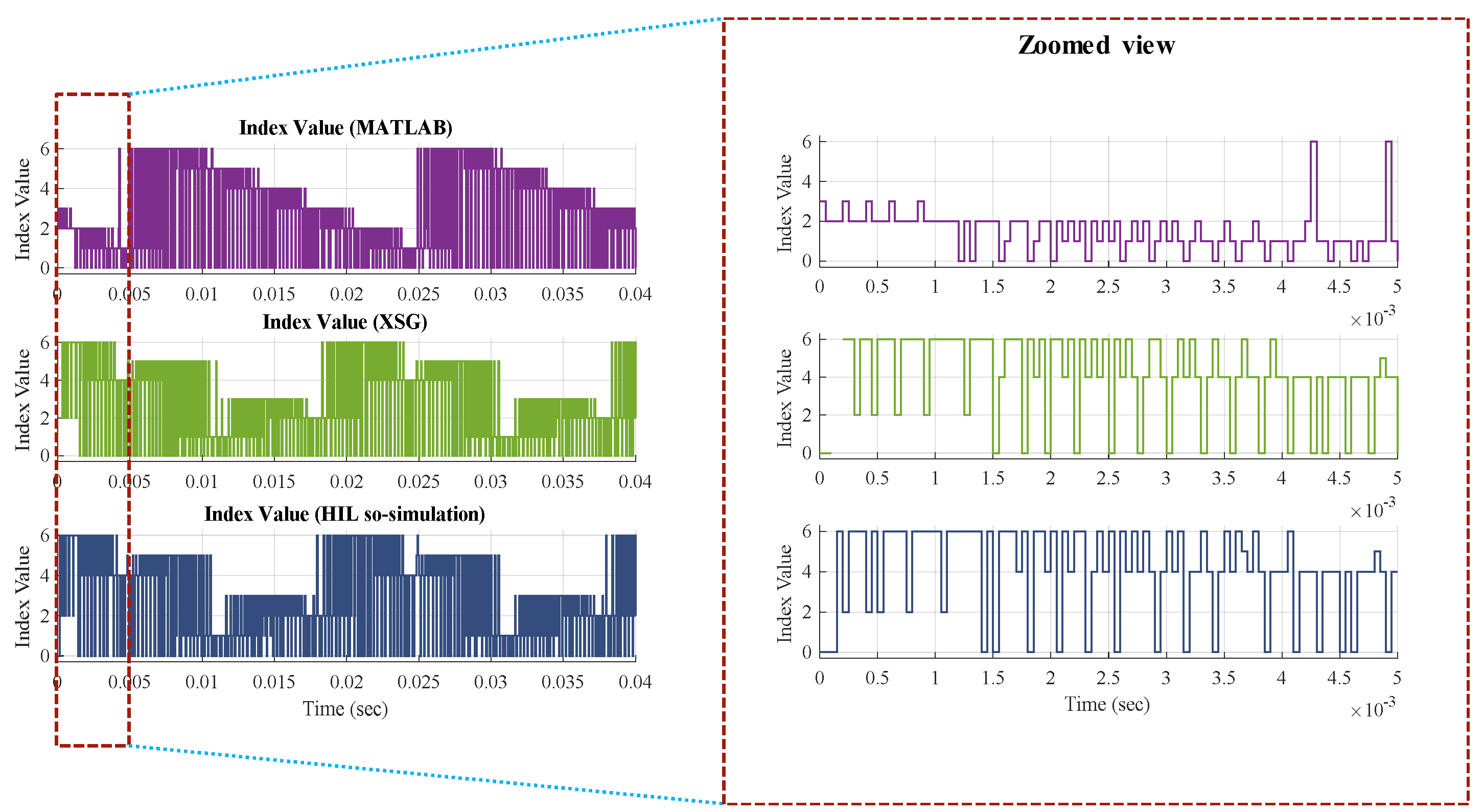

4.1. Intermediate Response

4.2. Sampling Time

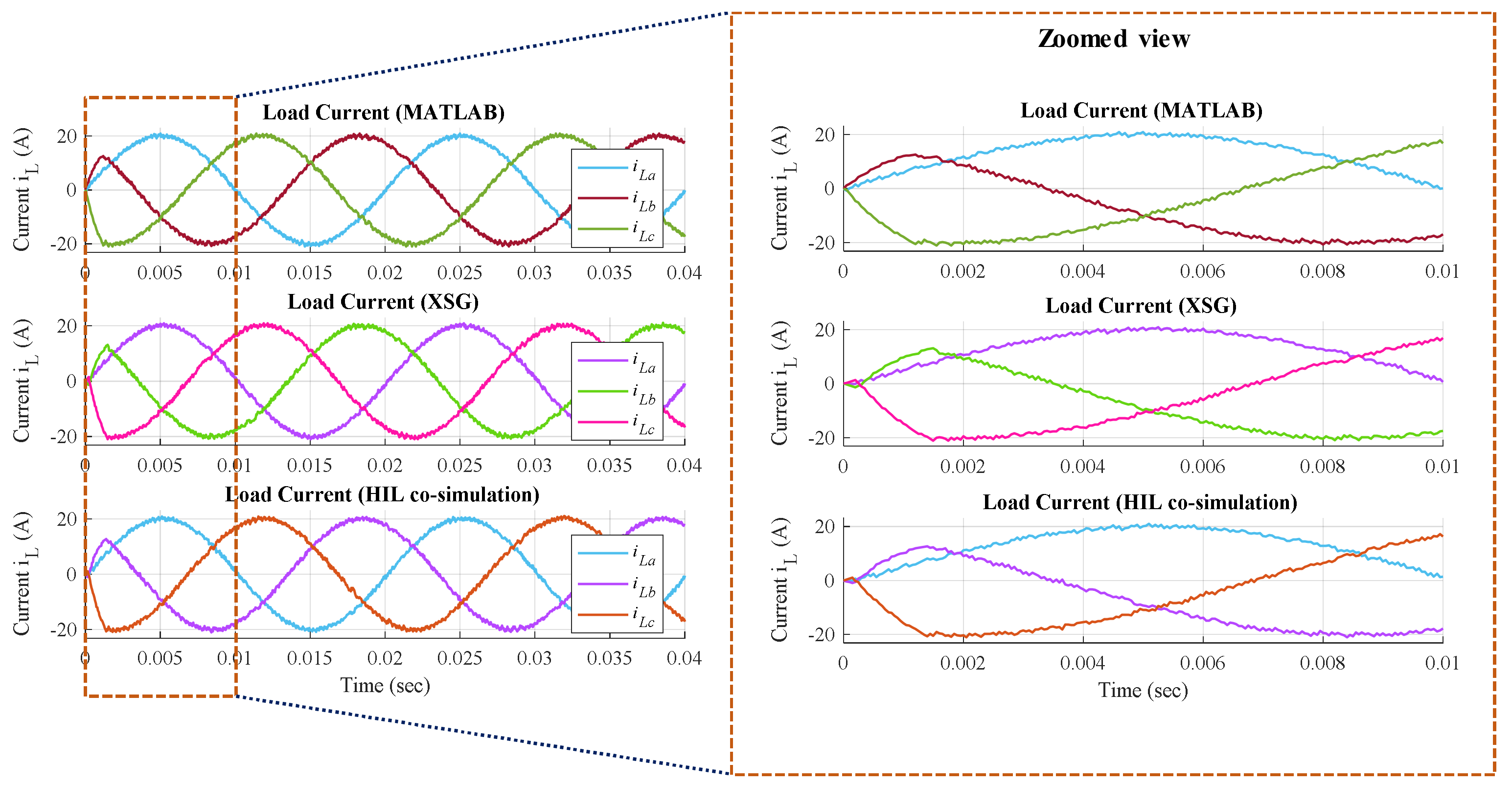

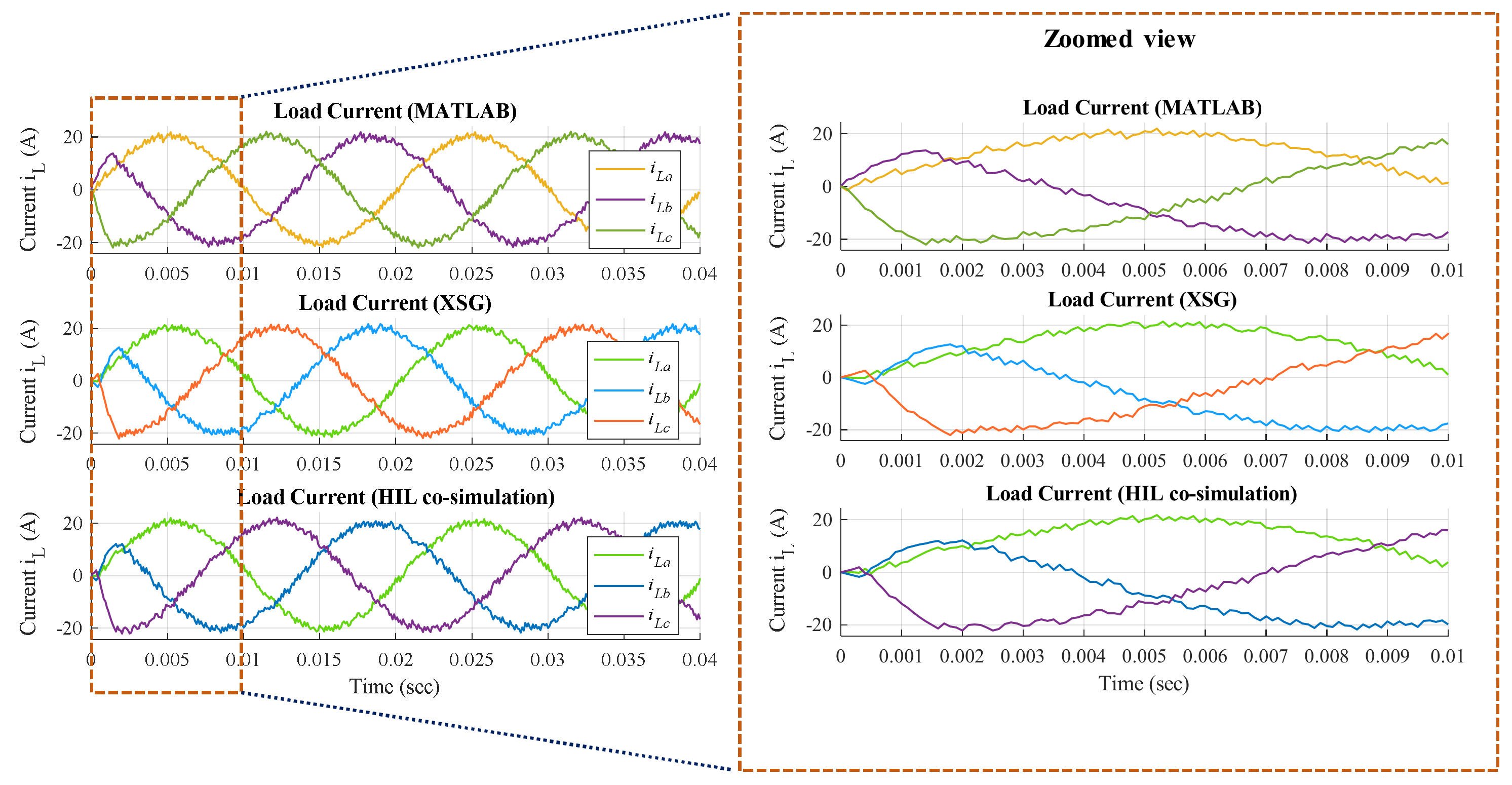

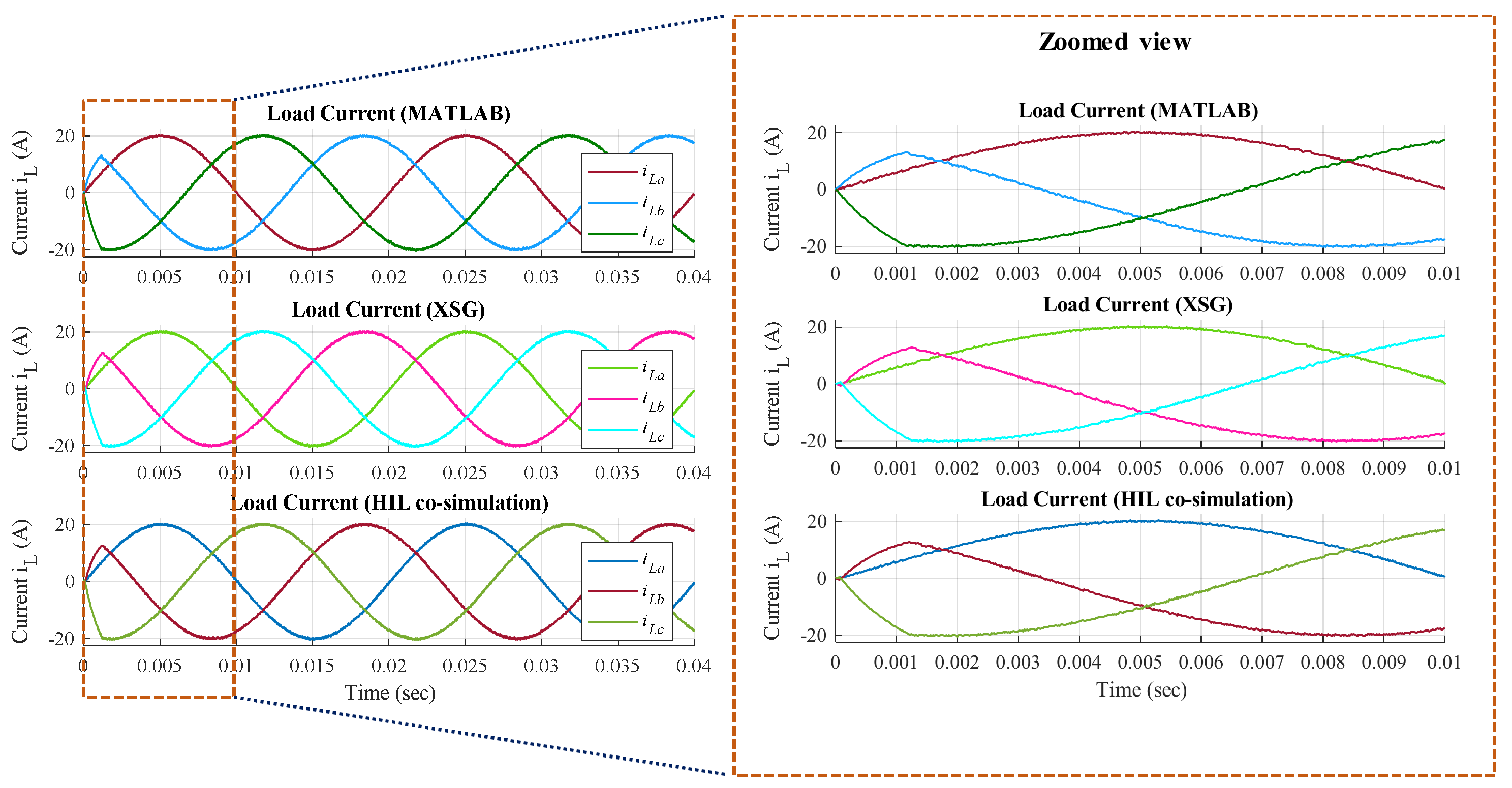

4.3. Tracking Performance

5. Conclusions

Author Contributions

Conflicts of Interest

References

- Bak, Y.; Lee, J.-S.; Lee, K.-B. Low-voltage ride-through control strategy for a grid-connected energy storage system. Appl. Sci. 2018, 8, 57. [Google Scholar] [CrossRef]

- Tahir, S.; Wang, J.; Baloch, M.H.; Kaloi, G.S. Digital control techniques based on voltage source inverters in renewable energy applications: A Review. Electronics 2018, 7, 18. [Google Scholar] [CrossRef]

- Smadi, I.A.; Albatran, S.; Ahmad, H.J. On the performance optimization of two-level three-phase grid-feeding voltage-source inverters. Energies 2018, 11, 400. [Google Scholar] [CrossRef]

- Kazmierkowski, M.P.; Krishnan, R.; Blaabjerg, F. Control in Power Electronics, 1st ed.; Academic Press: New York, NY, USA, 2002. [Google Scholar]

- Mohan, M.N.; Undeland, T.M.; Robbins, W.P. Power Electronics: Converters, Applications, and Design, 2nd ed.; Wiley: New York, NY, USA, 1995. [Google Scholar]

- Kazmierkowski, M.P.; Malesani, L. Current control techniques for three-phase voltage-source PWM converters: A survey. IEEE Trans. Ind. Electron. 1998, 45, 691–703. [Google Scholar] [CrossRef]

- Brod, D.M.; Novotny, D.M. Current control of VSI-PWM inverters. IEEE Trans. Ind. Appl. IA-21, 562–570. [CrossRef]

- Holtz, J. Pulse width modulation-a survey. IEEE Trans. Ind. Electron. 1992, 39, 410–420. [Google Scholar] [CrossRef]

- Ho, C.N.M.; Cheung, V.S.P.; Chung, H.S.H. Constant-frequency hysteresis current control of grid-connected VSI without bandwidth control. IEEE Trans. Power Electron. 2009, 24, 2484–2495. [Google Scholar] [CrossRef]

- Geyer, T. A comparison of control and modulation schemes for medium-voltage drives: Emerging predictive control concepts versus PWM-based schemes. IEEE Trans. Ind. Appl. 2011, 47, 1380–1389. [Google Scholar] [CrossRef]

- Cortes, P.; Kazmierkowski, M.P.; Kennel, R.M.; Quevedo, D.E.; Rodriguez, J. Predictive control in power electronics and drives. IEEE Trans. Ind. Electron. 2008, 55, 4312–4324. [Google Scholar] [CrossRef]

- Kouro, S.; Cortes, P.; Vargas, R.; Ammann, U.; Rodriguez, J. Model predictive control—A simple and powerful method to control power converters. IEEE Trans. Ind. Electron. 2009, 56, 1826–1838. [Google Scholar] [CrossRef]

- Rodríguez, J.; Cortes, P. Predictive Control of Power Converters and Electrical Drives, 1st ed.; Wiley-IEEE Press: New York, NY, USA, 2012. [Google Scholar]

- Vazquez, S.; Rodriguez, J.; Rivera, M.; Franquelo, L.G.; Norambuena, M. Model predictive control for power converters and drives: Advances and trends. IEEE Trans. Ind. Electron. 2017, 64, 935–947. [Google Scholar] [CrossRef]

- Rodríguez, J.; Pontt, J.; Cortés, P.; Vargas, R. Predictive control of a three-phase neutral point clamped inverter. In Proceedings of the Power Electronics Specialists Conference, Recife, Brazil, 12–16 June 2005. [Google Scholar]

- Rodríguez, J.; Kazmierkowski, M.P.; Espinoza, J.R.; Zanchetta, P.; Abu-Rub, H.; Young, H.A.; Rojas, C.A. State of the art of finite control set model predictive control in power electronics. IEEE Trans. Ind. Inf. 2013, 9, 1003–1016. [Google Scholar] [CrossRef]

- Cortes, P.; Rodriguez, J.; Antoniewicz, P.; Kazmierkowski, M. Direct power control of an AFE using predictive control. IEEE Trans. Power Electron. 2008, 23, 2516–2523. [Google Scholar] [CrossRef]

- Perez, M.A.; Cortes, P.; Rodriguez, J. Predictive control algorithm technique for multilevel asymmetric cascaded H-bridge inverters. IEEE Trans. Ind. Electron. 2008, 55, 4354–4361. [Google Scholar] [CrossRef]

- Cortes, P.; Wilson, A.; Kouro, S.; Rodriguez, J.; Abu-Rub, H. Model predictive control of multilevel cascaded H-bridge inverters. IEEE Trans. Ind. Electron. 2010, 57, 2691–2699. [Google Scholar] [CrossRef]

- Lezana, P.; Aguilera, R.P.; Quevedo, D.E. Model predictive control of an asymmetric flying capacitor converter. IEEE Trans. Ind. Electron. 2009, 56, 1839–1846. [Google Scholar] [CrossRef]

- Rivera, M.; Rojas, C.A.; Rodriguez, J.; Wheeler, P.; Wu, B.; Espinoza, J.R. Predictive current control with input filter resonance mitigation for a direct matrix converter. IEEE Trans. Power Electron. 2011, 26, 2794–2803. [Google Scholar] [CrossRef]

- Rodríguez, J.; Pontt, J.; Silva, C.; Correa, P.; Lezana, P.; Cortés, P.; Ammann, U. Predictive current control of a voltage source inverter. IEEE Trans. Ind. Electron. 2007, 54, 495–503. [Google Scholar] [CrossRef]

- Kouro, S.; Perez, M.A.; Rodriguez, J.; Llor, A.M.; Young, H.A. Model predictive control: MPC’s role in the evolution of power electronics. IEEE Ind. Electron. Mag. 2014, 8, 16–31. [Google Scholar] [CrossRef]

- Vazquez, S.; Leon, J.I.; Franquelo, L.G.; Rodriguez, J.; Young, H.A.; Marquez, A.; Zanchetta, P. Model predictive control: A review of its applications in power electronics. IEEE Ind. Electron. Mag. 2015, 9, 8–21. [Google Scholar] [CrossRef] [Green Version]

- Xia, C.; Liu, T.; Shi, T.; Song, Z. A simplified finite-control-set model-predictive control for power converters. IEEE Trans. Ind. Inf. 2014, 10, 991–1002. [Google Scholar]

- Cortes, P.; Ortiz, G.; Yuz, J.; Rodríguez, J.; Vazquez, S.; Franquelo, L. Model predictive control of an inverter with output LC filter for UPS applications. IEEE Trans. Ind. Electron. 2009, 56, 1875–1883. [Google Scholar] [CrossRef]

- Naouar, M.W.; Naassani, A.A.; Monmasson, E.; Slama-Belkhodja, I. FPGA-based predictive current controller for synchronous machine speed drive. IEEE Trans. Power Electron. 2008, 23, 2115–2126. [Google Scholar] [CrossRef]

- Sanchez, P.M.; Machado, O.; Peña, E.J.B.; Rodríguez, F.J.; Meca, F.J. FPGA-based implementation of a predictive current controller for power converters. IEEE Trans. Ind. Inf. 2013, 9, 1312–1321. [Google Scholar] [CrossRef]

- Selvamuthukumaran, R.; Gupta, R. Rapid prototyping of power electronics converters for photovoltaic system application using Xilinx System Generator. IET Power Electron. 2014, 7, 2269–2278. [Google Scholar] [CrossRef]

- Monti, A.; Santi, E.; Dougal, R.A.; Riva, M. Rapid prototyping of digital controls for power electronics. IEEE Trans. Power Electron. 2003, 18, 915–923. [Google Scholar] [CrossRef]

- Mekhilef, S.; Masaoud, A. Xilinx FPGA based multilevel PWM single phase inverter. In Proceedings of the IEEE International Conference on Industrial Technology, Mumbai, India, 15–17 December 2006. [Google Scholar]

- Vivado Design Suite User Guide: Model-Based DSP Design Using System Generator. Available online: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2017_2/ug897-vivado-sysgen-user.pdf (accessed on 7 June 2017).

- Vivado Design Suite Tutorial: Model-Based DSP Design Using System Generator. Available online: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2017_2/ug948-vivado-sysgen-tutorial.pdf (accessed on 7 June 2017).

- Vivado Design Suite User Guide: Release Notes, Installation, and Licensing. Available online: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2017_1/ug973-vivado-release-notes-install-license.pdf (accessed on 20 April 2017).

| Leg a, Sa | Leg b, Sb | Leg c, Sc |

|---|---|---|

| S1 ON, 1 | S3 ON, 1 | S5 ON, 1 |

| S2 OFF, 0 | S4 OFF, 0 | S6 OFF, 0 |

| S1 OFF, 0 | S3 OFF, 0 | S5 OFF, 0 |

| S2 ON, 1 | S4 ON, 1 | S6 ON, 1 |

| vi | [Sa Sb Sc] | [vreal vimg] |

|---|---|---|

| v0 | [0 0 0] | [0, 0] |

| v1 | [1 0 0] | [2Vdc/3, 0] |

| v2 | [0 1 0] | [−Vdc/3, √3 Vdc/3] |

| v3 | [1 1 0] | [Vdc/3, √3Vdc/3] |

| v4 | [0 0 1] | [−Vdc/3, −√3Vdc/3] |

| v5 | [1 0 1] | [Vdc/3, −√3Vdc/3] |

| v6 | [0 1 1] | [−2Vdc/3, 0] |

| v7 | [1 1 1] | [0, 0] |

| Description | Parameter | Value |

|---|---|---|

| DC supply voltage | Vdc | 650 V |

| Load resistor | R | 10 Ω |

| Load inductor | L | 10 mH |

| Sinusoidal back-EMF | e | 100 V |

| Frequency | f | 50 Hz |

| Sampling period | TS | 50 µs |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Singh, V.K.; Tripathi, R.N.; Hanamoto, T. HIL Co-Simulation of Finite Set-Model Predictive Control Using FPGA for a Three-Phase VSI System. Energies 2018, 11, 909. https://doi.org/10.3390/en11040909

Singh VK, Tripathi RN, Hanamoto T. HIL Co-Simulation of Finite Set-Model Predictive Control Using FPGA for a Three-Phase VSI System. Energies. 2018; 11(4):909. https://doi.org/10.3390/en11040909

Chicago/Turabian StyleSingh, Vijay Kumar, Ravi Nath Tripathi, and Tsuyoshi Hanamoto. 2018. "HIL Co-Simulation of Finite Set-Model Predictive Control Using FPGA for a Three-Phase VSI System" Energies 11, no. 4: 909. https://doi.org/10.3390/en11040909

APA StyleSingh, V. K., Tripathi, R. N., & Hanamoto, T. (2018). HIL Co-Simulation of Finite Set-Model Predictive Control Using FPGA for a Three-Phase VSI System. Energies, 11(4), 909. https://doi.org/10.3390/en11040909