1. Introduction

Renewable energy sources are becoming increasingly important for electricity generation, since non-renewable energy sources such as fossil fuels are facing serious problems, e.g., pollutions, uncertain future of fossil-fuel prices, being unsustainable and CO

2 emissions [

1]. Among these alternative energy sources, solar energy has been identified as being clean and easily available [

2]. However, DC power produced by PV modules is not compatible with standard electrical appliances operating with AC power. In order to be compatible with the standard AC electrical appliances, various inverter topologies are proposed and employed to convert the DC electricity to the AC form [

1]. Among these topologies, multilevel inverters have been receiving much attention, the most popular of them being cascaded multilevel inverter topologies [

3,

4], diode-clamped multilevel inverter topologies [

5,

6] and flying-capacitor multilevel inverter topologies [

7,

8]. A comparative analysis of the three topologies demonstrates that the cascaded topology is simple and uses the least components. Also, the cascaded topology is ideally suited for solar PV systems, where isolated input DC sources are available. Therefore, the cascaded topology is considered as the most suitable for solar PV systems in all multilevel topologies.

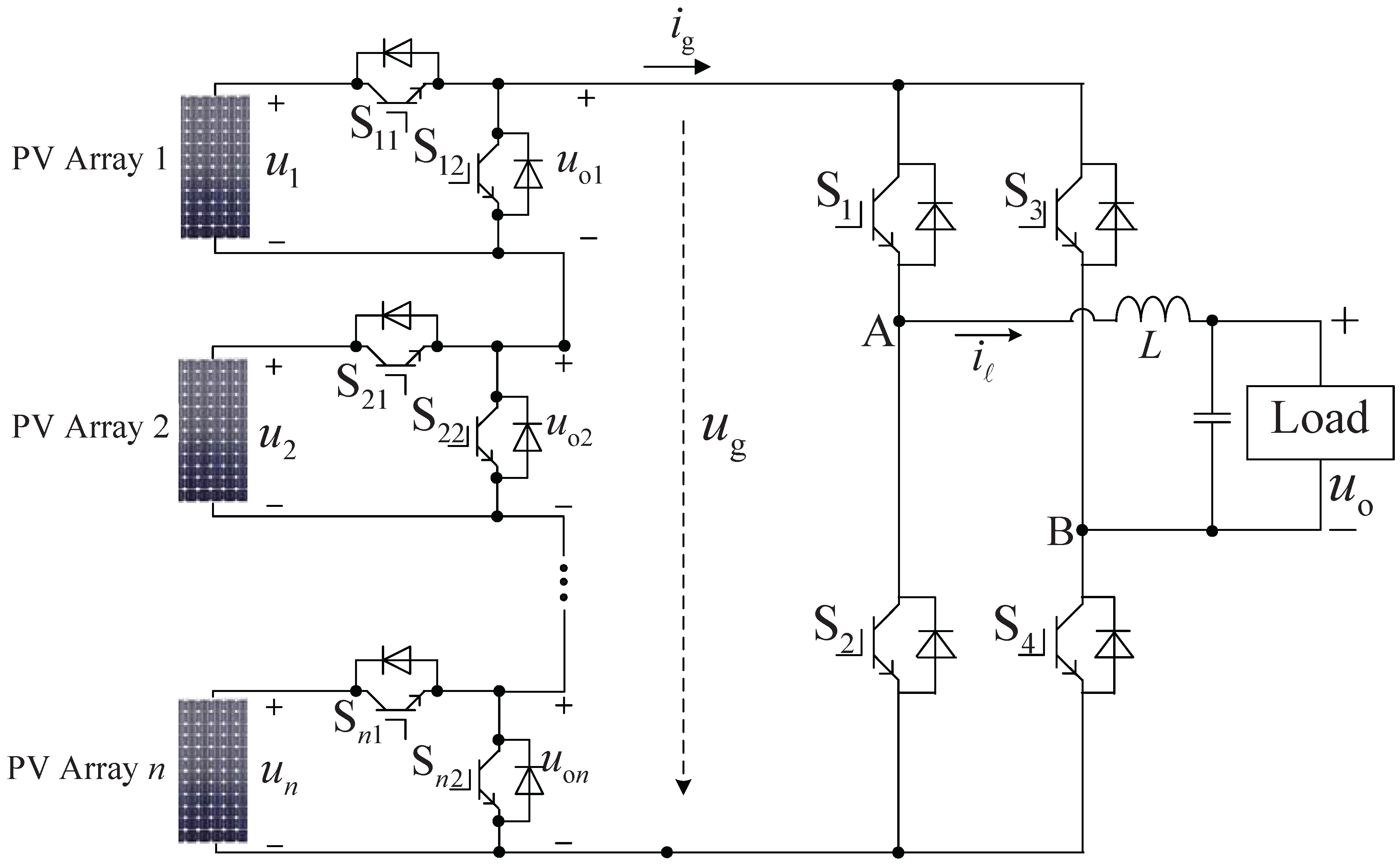

Figure 1 displays the block diagram of a standalone solar PV system using a cascaded half-bridge multilevel inverter [

9]. Compared with the typical cascaded H-bridge (CHB) multilevel topology, the cascaded half-bridge multilevel topology reduces nearly half the number of required switches. Recently, a cascaded switched-diode topology has been proposed [

10,

11]. The comparison with cascaded half-bridge multilevel topology illustrates that more voltage levels are produced with fewer required switches. However, under a case of resistance-inductance (R-L) loads, high voltage spikes occur at the base of the stepped output voltage due to the lack of a path for reverse load currents, which tend to deteriorate power quality [

12].

Basic modulations techniques for cascaded multilevel topologies are rooted on the fundamental frequency switching [

9], sinusoidal pulse width modulation (PWM) [

13,

14], and space vector PWM (SV-PWM) [

15]. However, in solar PV systems, DC sources of a multilevel inverter topology are supplied by PV modules, as shown in

Figure 1, which brings about a series of problems:

Power imbalance: the power of a PV array supplied to each cascaded unit of the multilevel inverter may be different, introduced by cloud shading, different irradiance levels and ambient temperatures.

DC supply with fluctuations: the DC supply from a PV array is always with fluctuation caused by variety of external factors, such as illumination change, shadow, ambient temperature and etc. More specifically, following variations in a certain range of irradiance level will lead to the instability of the voltage, which manifests as low frequency pulsation.

Load variations: with the constant expansion of application fields, loads of an inverter are becoming more and more diversified. Abrupt load variations happen regularly.

The existence of these problems cause distortions or bring lots of low harmonics to the output voltages of the cascaded multilevel inverters using basic modulation techniques, which leads great hazards to electrical equipment. In recent years, some nonlinear control methods, e.g., hysteresis control, sliding mode control, fuzzy logic control and so on, have been attempted in multilevel inverters. As presented in [

16], the advantages of using various accessible DC voltage levels have been fully exploited by using the hysteresis control. Sliding-mode control (SMC), as presented in [

17], provides fast dynamic responses. However, the variable switching frequency and nonzero steady-state error are the drawbacks of these methods. Then in [

18], a fuzzy logic control has been proposed. The dynamic behaviours are improved by considering moving cloud obfuscating the PV arrays.

Among the problems in solar PV systems, the power imbalance can be classified into two categories: (1) the inter-phase power imbalance, which occurs when each phase generates different amount of power; and (2) the inter-bridge power imbalance, which happens when each bridge in the same phase generates different amounts of power [

19]. A three-phase system focus more on the interphase power imbalance because three-phase unbalanced currents result in wasted power. New control methods [

19,

20] or converter topology [

21] have been proposed to deal with the interphase power imbalance problem of CHB converters in PV systems. In contrast, the interbridge power imbalance gets more attention in single-phase systems. A continuous time-domain power balancing control algorithm was presented to solve the interbridge imbalance of a single-phase CHB converter [

22]. However, this method can improve but not completely suppress fluctuations of the DC supply of the multilevel inverter. Thus, the problem of DC supply with fluctuations in PV application has not been solved. A CPS one-cycle control method was proposed for multilevel inverters. While its inhibitory capability to the interbridge power imbalance and variations of input voltage is satisfactory, the inhibitory capability to load changes is still poor [

12].

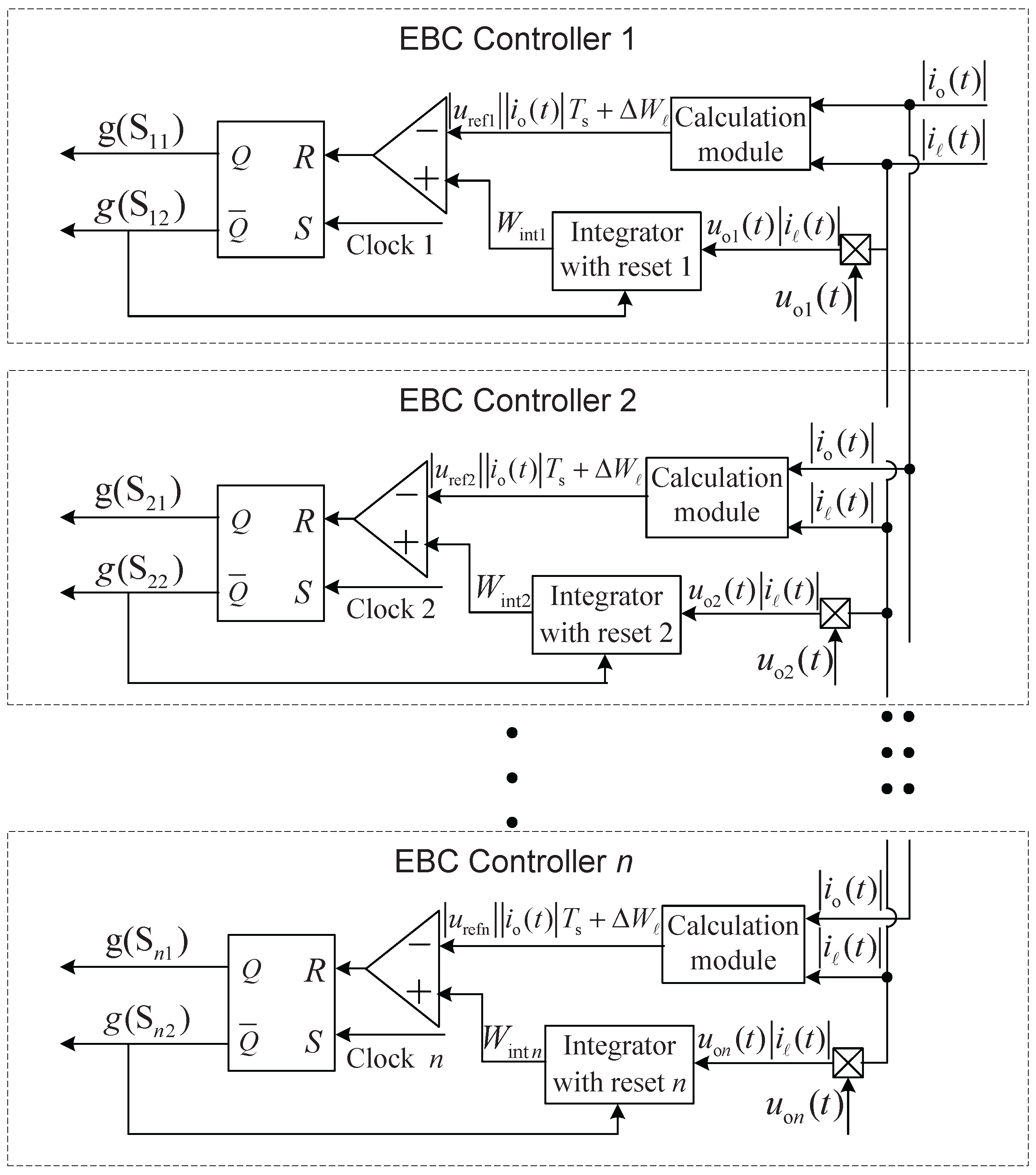

The objective of this paper is to verify the ability of the proposed CPS EBC method to deal with the problems of a multilevel inverter in standalone solar PV applications. The basic structure of this paper is as follows.

Section 2 introduces the cascaded half-bridge topology. The derivation of the control equation, the design and implementation of the proposed CPS EBC method are illustrated in

Section 3.

Section 4 presents the simulation and experimental results. Final conclusions are given in

Section 5.

2. Topology of the Cascaded Half-Bridge Multilevel Topology

Figure 1 displays the cascaded half-bridge topology for standalone solar PV applications. The topology is divided into two stages. The first stage is cascaded by

n half-bridge converters. The cascaded unit, e.g., unit 1, as shown in

Figure 1, contains a DC source supplied from a PV array, the DC voltage of which is equal to

, switches

and

. The output of the unit 1

have two values, which are

when switch

conducts and

is off, and when switch

is off and

is turned on, the value of

is 0. For states of switches

,

,

,

, ⋯,

,

,

, the output voltage of the first stage

obtains

different values, as listed in

Table 1, the maximum of them is given as follows:

From

Table 1, it can be observed that the first stage generates a positive output voltage. For generating both positive and negative values, the second stage, which is a full-bridge inverter, is required.

Table 2 lists the obtained output voltage

under different switch states. Through the judgement of the positive or the negative sign of a reference voltage

, both the positive and negative halves of

are achieved.

Under the symmetric case, that is, all the DC sources are equal to

, the total number of required switches

against the output voltage levels

are shown as follows,

Compared with the CHB multilevel topology (

), the cascaded half-bridge multilevel topology reduces nearly half the number of required switches. However, in designing such a multilevel topology, it should be noted that the switches of the full-bridge converter

, ⋯,

have to withstand the total voltage of all cascaded units, while the switches of the first stage

,

, ⋯,

,

only withstand a fraction of the total voltage of all cascaded units. This indicates that the four switches in the full-bridge cell of the second stage are with a high capability of the voltage rating, which makes the total voltage rating increase and leads to the limitation of the high voltage applications. Thus, the cascaded half-bridge multilevel topology is more suitable for medium voltage (

or

) applications [

23].

4. Simulation and Experimental Results

When designing solar PV fed inverters, the estimation of PV characteristics and maximum power point tracking (MPPT) control are one focus for solar PV modelling, meanwhile another way to simulate PV arrays employs a DC power supply with variable output voltage. Concerning stand-alone PV systems, the extraction of energy from PV arrays depends on the load demand [

18,

25]. In this research, on the premise of guaranteeing the installed output power of PV arrays, each PV array is only simulated by a

V-

I characteristic with an open-circuit voltage that is equal to

. It should be noticed that the PV modelling method employed in this research cannot represent the PV arrays controlled by a MPPT algorithm. At first, a five-level and nine-level two-stage half-bridge multilevel inverter with a switching frequency of 2,500

are set up. The parameters are

,

,

,

,

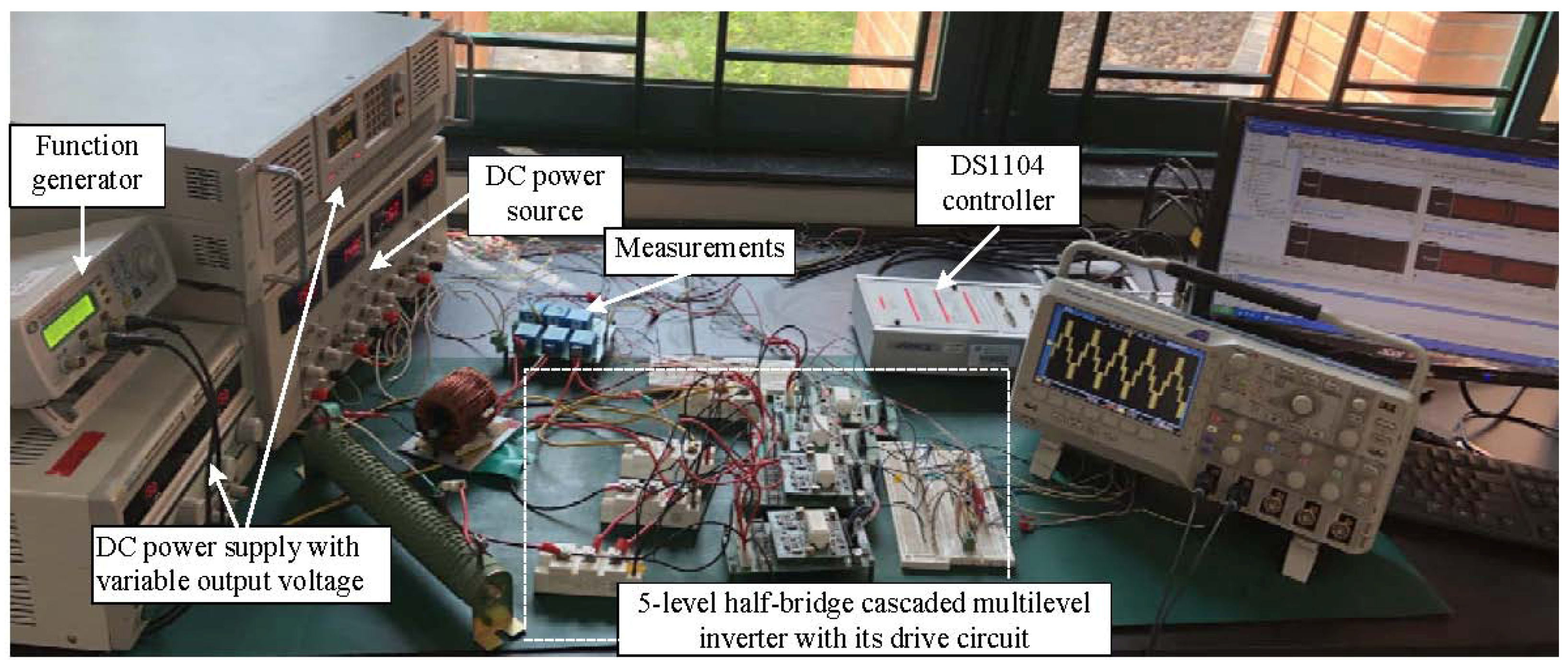

. Then a five-level experimental prototype, the parameters of which are identical with that of the simulation model, is built. In the experimental prototype shown in

Figure 4, the voltage and current are sampled by the measurement, which is made up of HALL voltage sensors CHV-25P/100 (Measurement range: 0–

; Measurement accuracy:

) and HALL current sensors CHB-25NP/6 A (Measurement range: 0–

; Measurement accuracy:

), respectively. The gate drivers of the IGBT are configured on SKYPER 32R (SEMIKRON, Nuremberg, Germany), which are powered with the DC power source (

). In the experiment, PV arrays are emulated by DC power with variable output voltage and a function generators. The function generator TFG1900B (Suin Instuments, Nanjing, China) is connected in series with the DC power, which generate fluctuations (here is the low frequency ripples) to simulate the variations in irradiance and temperature of PV array outputs. The overall control strategy is implemented on a DS1104 (dSPACE company, Padbourne, Germany) system, where the proposed CPS EBC controller was programmed for the five-level half-bridge cascaded multilevel inverter.

To reveal the limitations of the conventional controller for solar PV applications, a carrier phase-shifted sinusoidal pulse width modulation (CPS SPWM) controller is configured. Although in recent years some nonlinear control methods have been attempted for controlling multilevel inverters, the CPS SPWM controller based on the sinusoidal PWM is still the most typical modulation strategy in cascade multilevel converter applications, as the CPS SPWM has the advantages of low-switching technique, balancing switching loads and good harmonic characteristics. The comparative studies demonstrate the ability to suppress DC source fluctuations and the improved dynamic responses to load variations using the CPS EBC. A comparison is made with the CPS SPWM because it is most frequently used for controlling cascaded multilevel inverters.

4.1. The Operation of CPS EBC

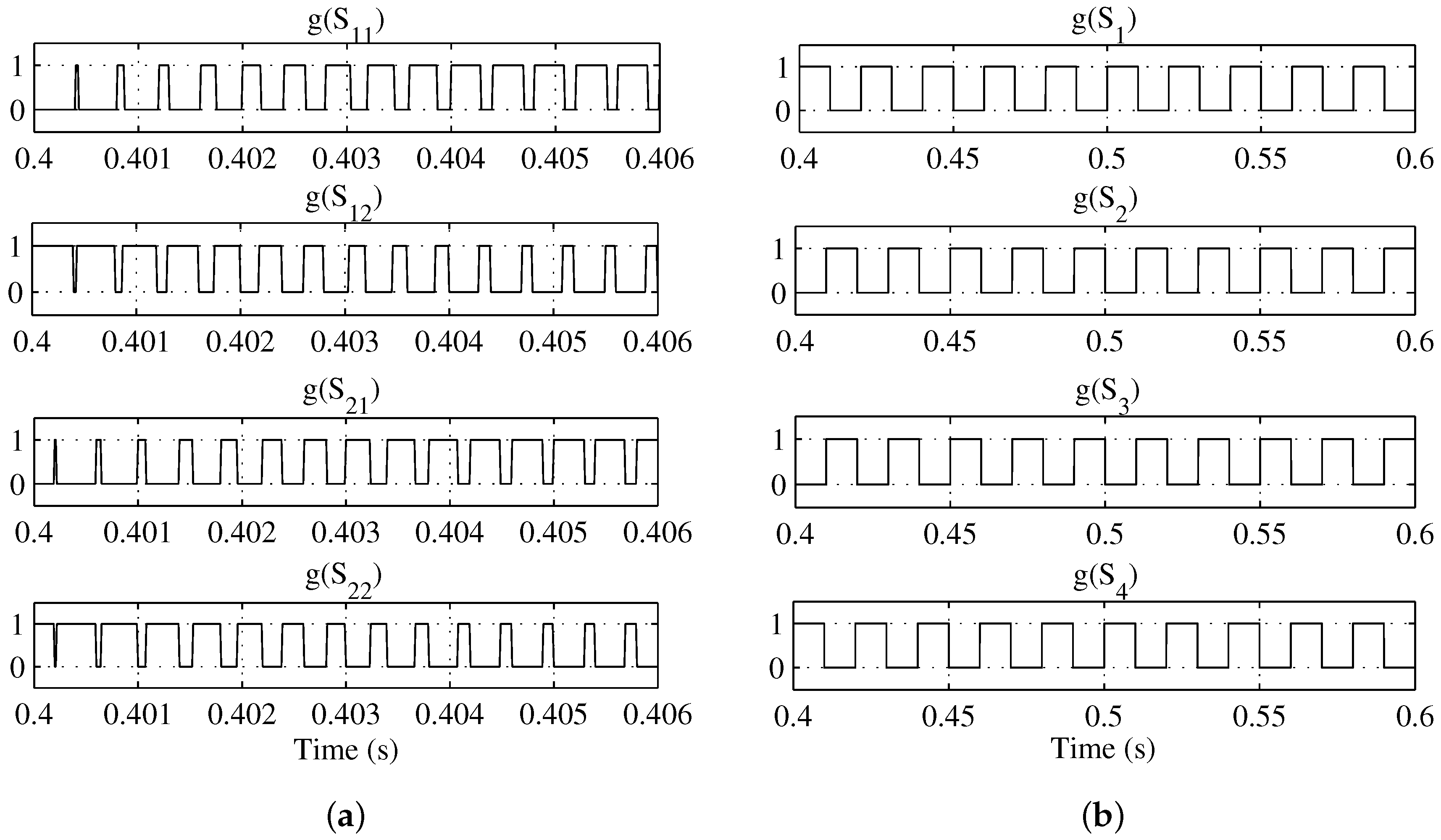

Figure 5 shows the gate signals of the cascaded half-bridge multilevel inverter. From

Figure 5a, it can be seen that when

is on,

is off; When

is turned off,

is on. The gate signals of the second stage are shown in

Figure 5b.

and

are on-state when

. In this switching state,

. When

,

and

are turned off and

and

are turned on. In this switching state,

for the negative half cycle. By judging the sign of

, both the positive and negative halves of output voltage are obtained.

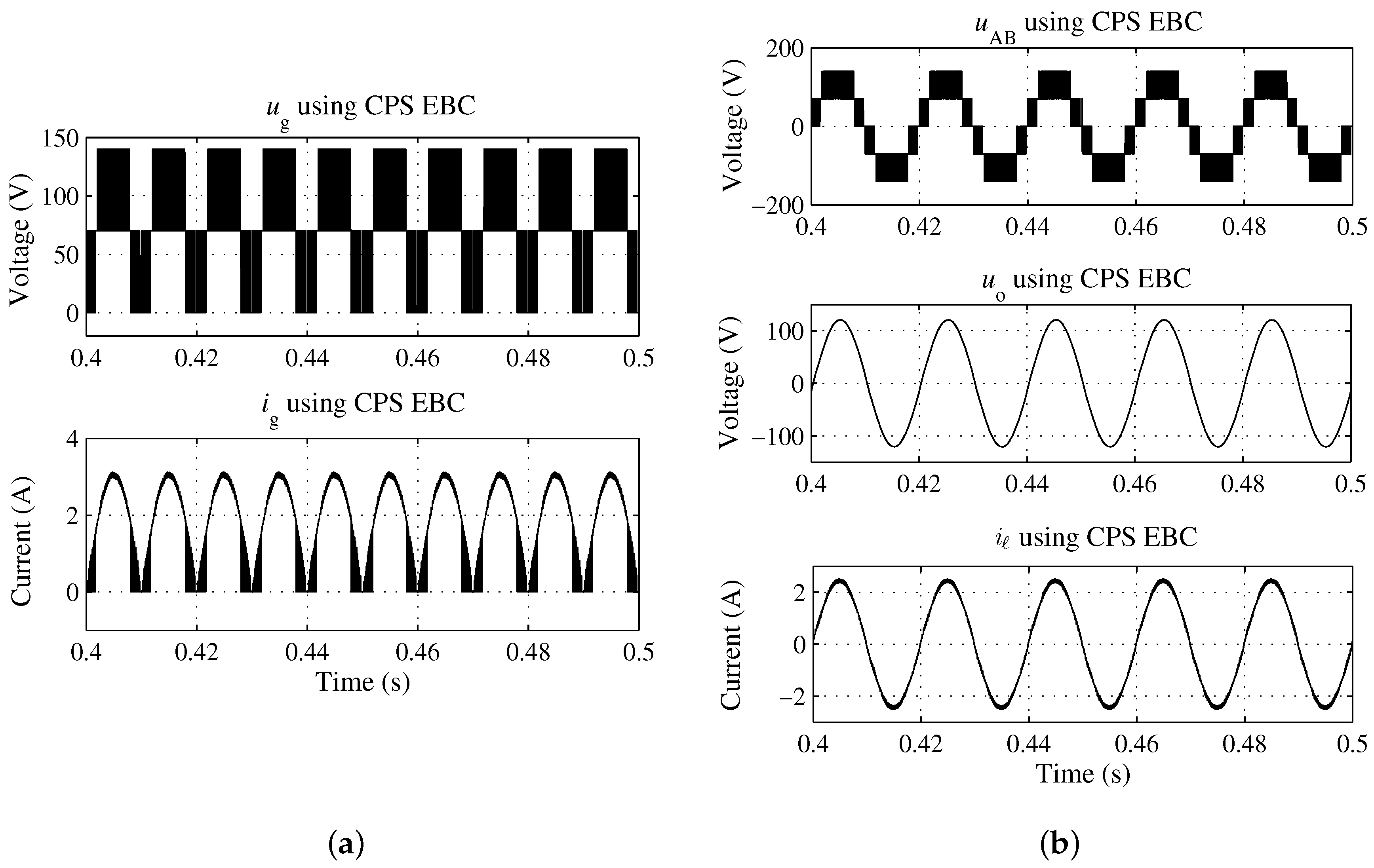

As shown in

Figure 6a, the output of the first stage

, which is the sum of the output voltage of all the cascaded units, has positive and zero values. The output current

of the first stage is also positive. The voltage between points A and B

, the output voltage

and the inductor current

of the multilevel inverter are shown in

Figure 6b. From the waveforms in the figure, it can be seen that

is a staircase waveform with a frequency of

and an amplitude of

. After the

filter,

and

are almost sinusoidal waveforms.

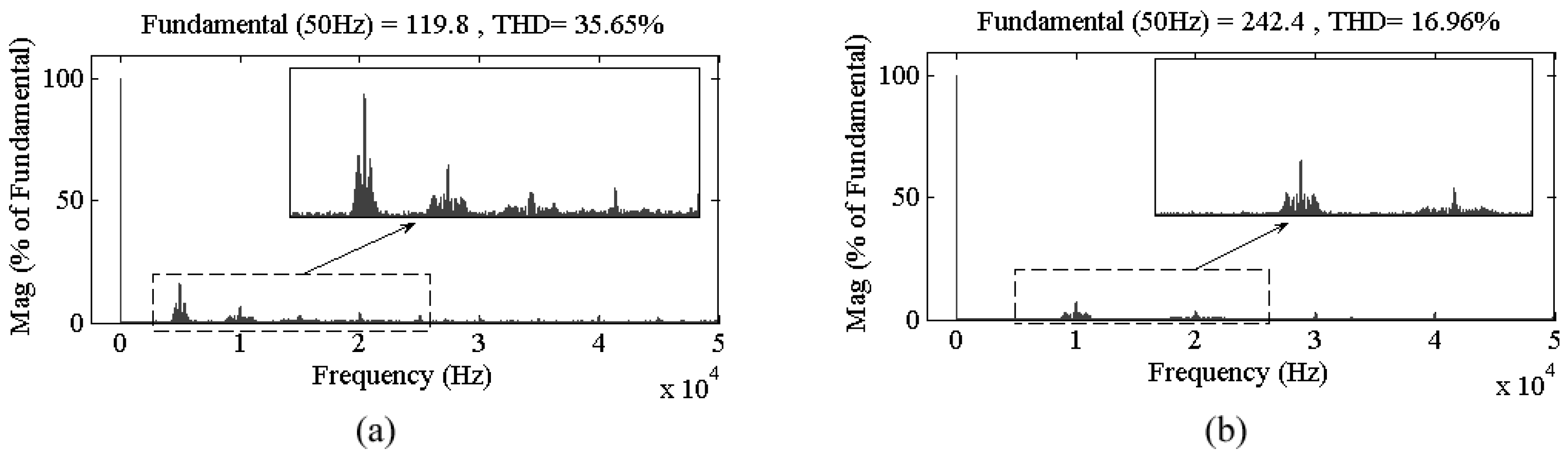

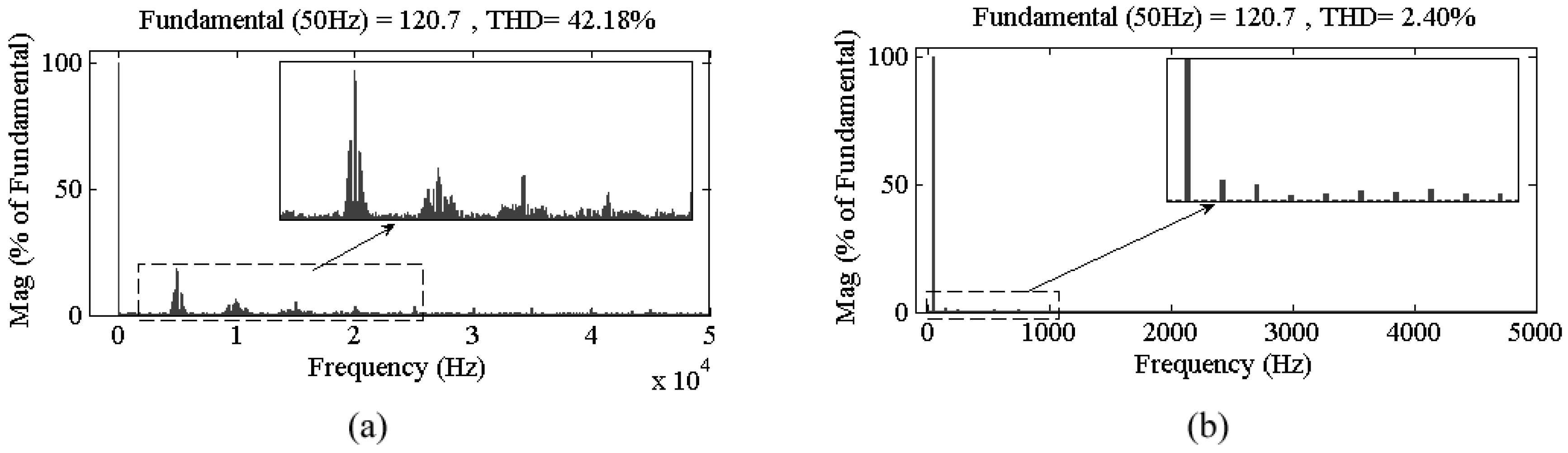

Figure 7a demonstrates that the total harmonic distortion (THD) of

of the five-level simulation prototype is 35.65% and the frequencies that the main harmonics focus on is multiples of 5000

(5000

10,000

15,000

), where 5,000

is twice of the switching frequency (2500

).

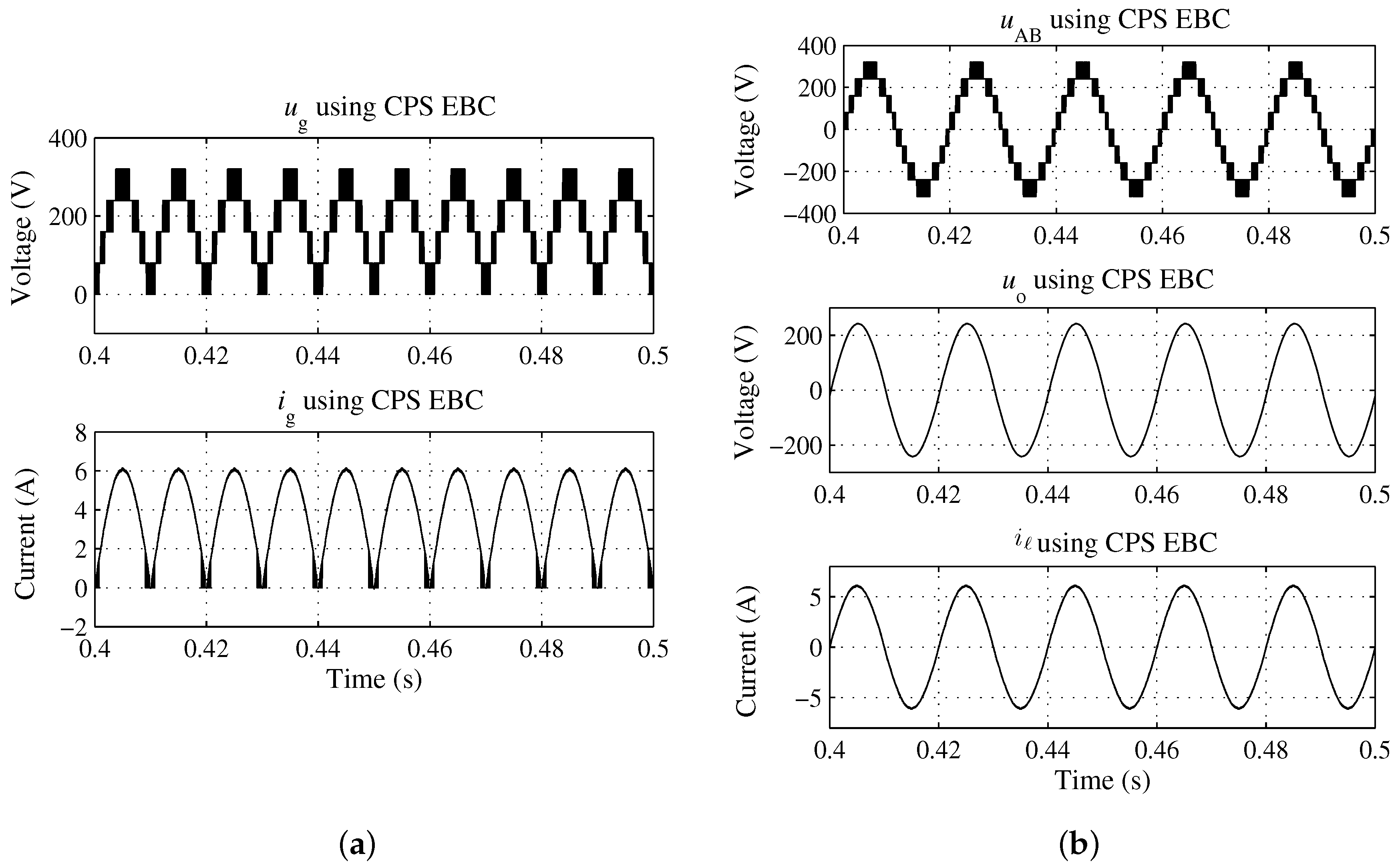

Figure 8 illustrates the simulation results of the operation of a nine-level multilevel topology. It is observed from

Figure 8a that

and

have zero and positive values.

Figure 8b shows the waveforms of

,

and

of the nine-level multilevel topology. The waveforms in the figure demonstrate that

is a staircase waveform with a frequency of

and an amplitude of

. After the

filter,

and

are almost sinusoidal waveforms. The THD of

of the nine-level multilevel inverter is 16.96%, as shown in

Figure 7b. The frequencies that the main harmonics focus on is multiples of 10,000 Hz (10,000 Hz, 20,000 Hz, 30,000 Hz,…), where 10,000 Hz is four times of the switching frequency 2500 Hz. The comparison with THD of

of the five-level prototype, the THD is reduced and the frequencies that the main harmonics focus on move backward, which reduces the designing standards of the output filter.

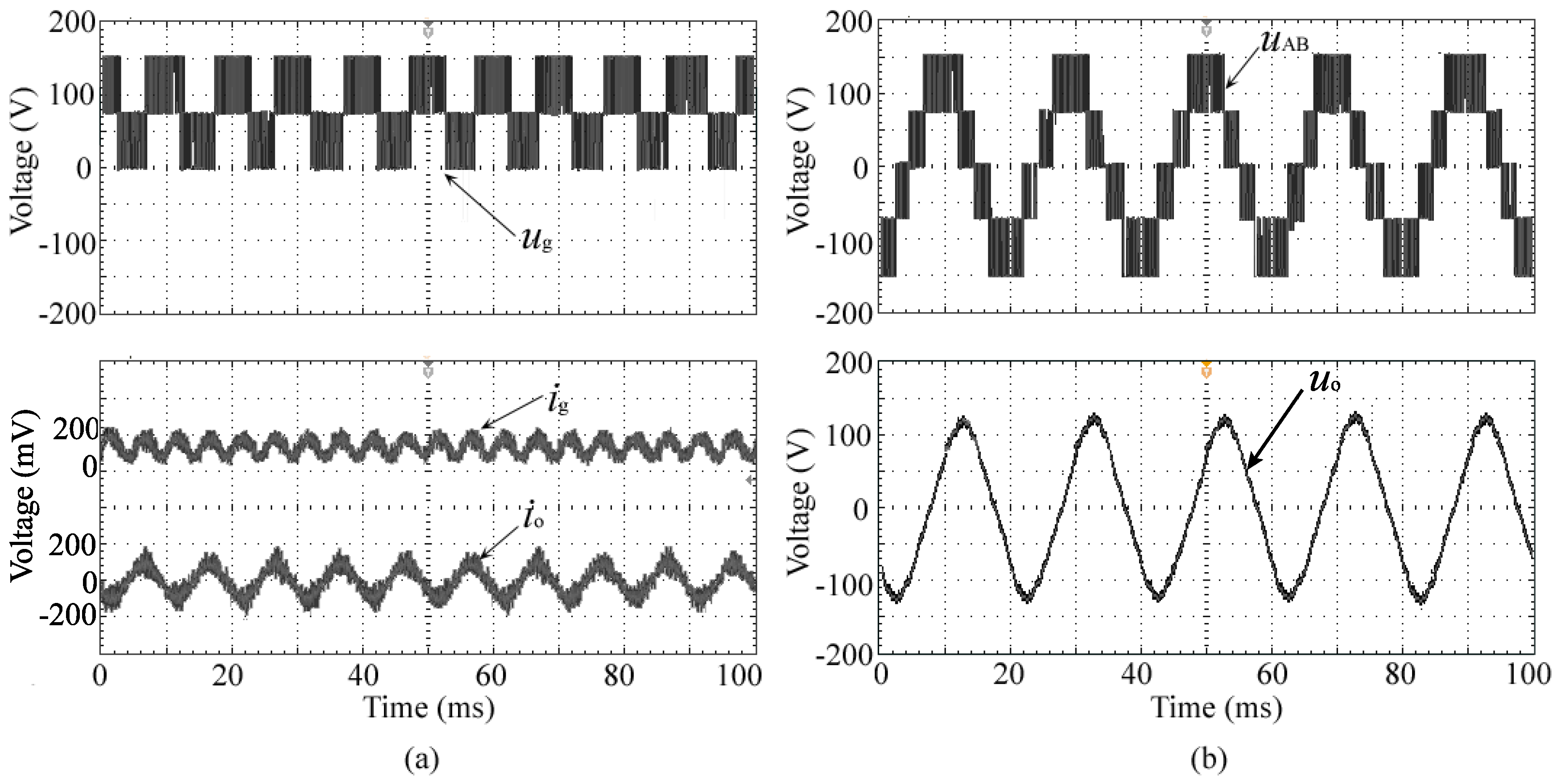

The experimental results of the five-level prototype using the CPS EBC are shown in

Figure 9 and

Figure 10. The figures illustrate that the results are consistent with the simulation results in

Figure 6.

and

of the first stage are positive.

is a five-level staircase waveform. The THD of

is 42.18% and the frequencies that the main harmonics focus on is (5000 Hz, 10,000 Hz, 15,000 Hz, …) , as shown in

Figure 10a. After the

filter,

and

are sinusoidal waveforms. The THD of

is 2.40%, as shown in

Figure 10b.

The above simulation and experimental results verify the feasibility of the CPS EBC method for the cascaded half-bridge multilevel inverter in standalone solar PV applications.

4.2. The Suppression Ability of the CPS EBC against Interbridge Power Imbalance in DC Sources

To evaluate the ability of the CPS EBC to suppress the power imbalance of the PV arrays, DC sources (

) are designed by different DC voltages. The simulation and experimental results are demonstrated in

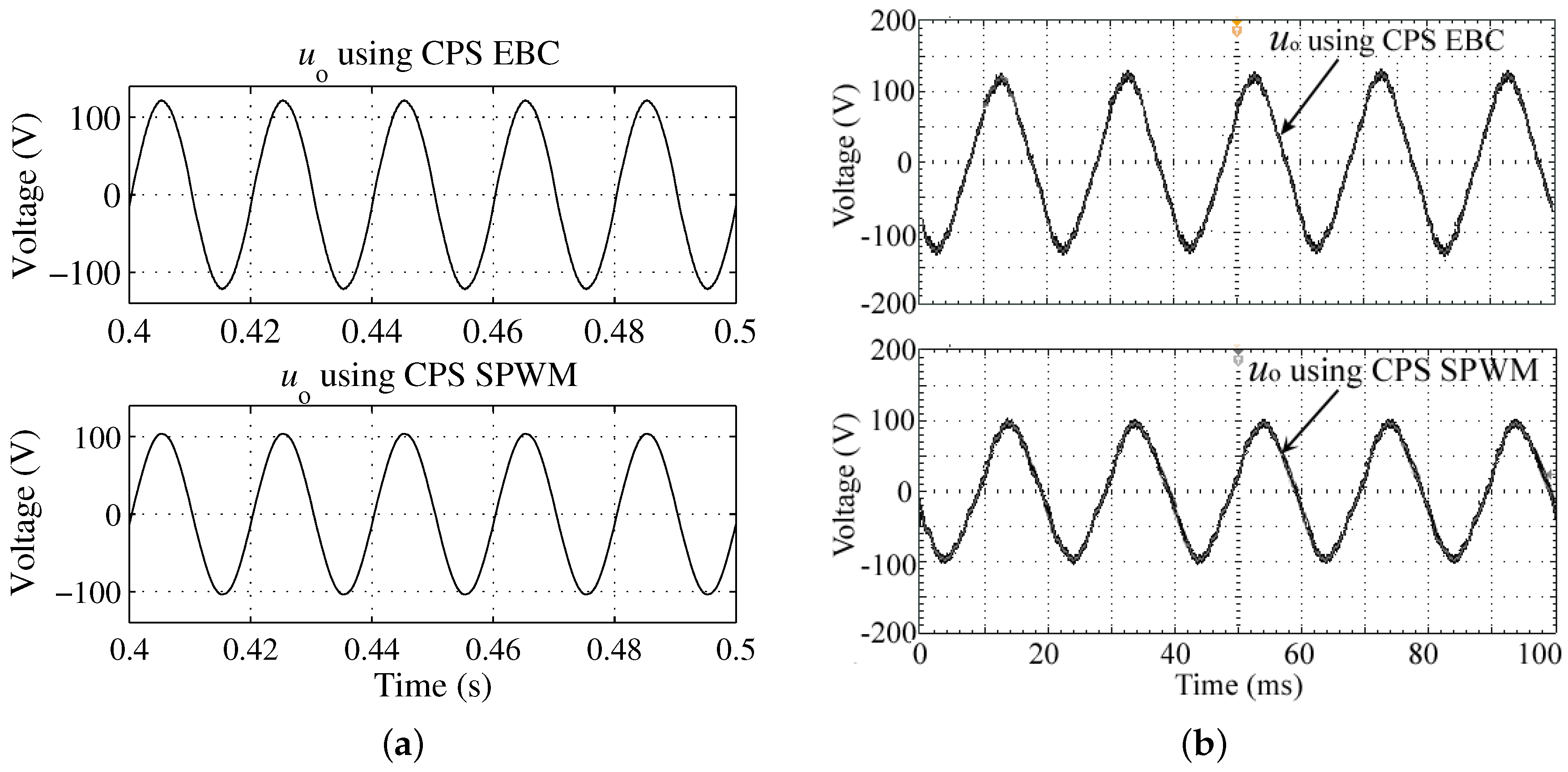

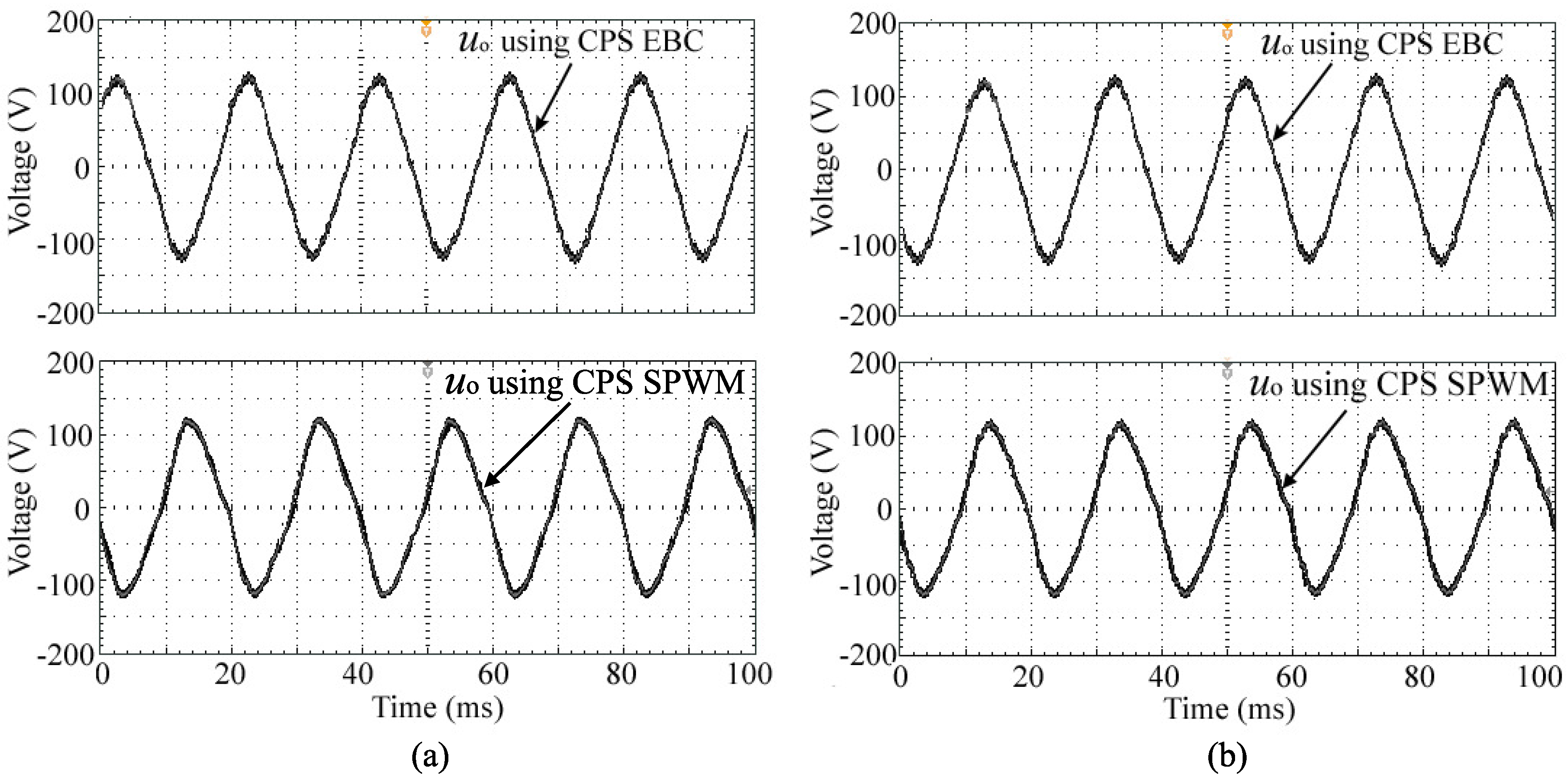

Figure 11.

Figure 11a shows the simulation results under power imbalance (under the obfuscation of cloud shadowing, the PV unit 1 (

) is with a voltage drop

). The comparison results demonstrate that

using CPS SPWM tracks its reference

with a drop

. In contrast,

using CPS EBC tracks its reference with no voltage drop.

Figure 11b display the experimental results using the CPS EBC and the CPS SPWM under the cases of power imbalance. From the comparisons, it can be observed that the experimental results are consistent with the simulation results in

Figure 11a. Thus the ability of the proposed CPS EBC against the interbridge power imbalance is verified.

4.3. The Suppression Ability of the CPS EBC against Interferences in DC Sources

To evaluate the ability of the CPS EBC to suppress the fluctuations of DC sources, DC sources (

) are designed by DC voltage mixed with low frequency interferences. The simulation and experimental results are demonstrated in

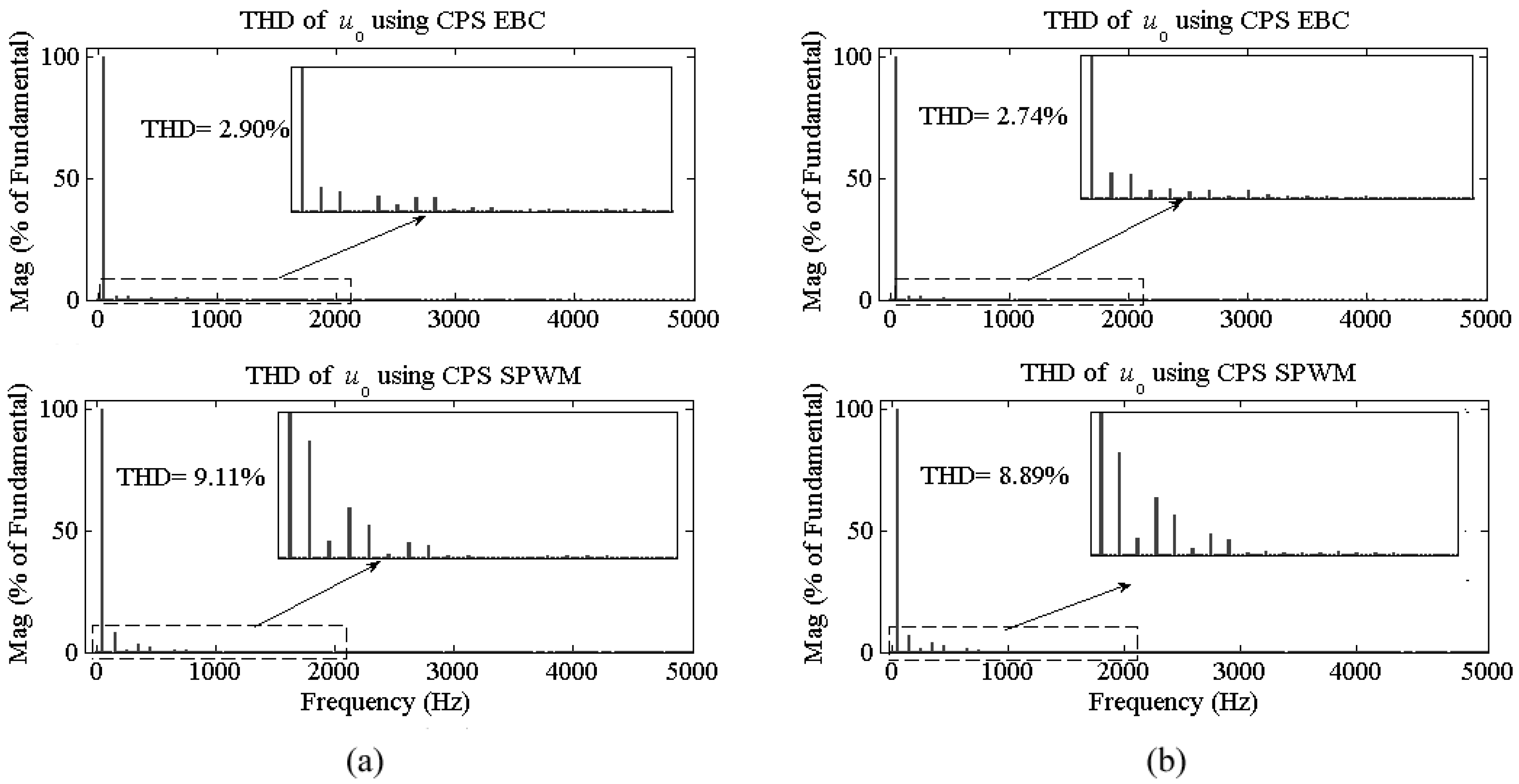

Figure 12,

Figure 13,

Figure 14 and

Figure 15.

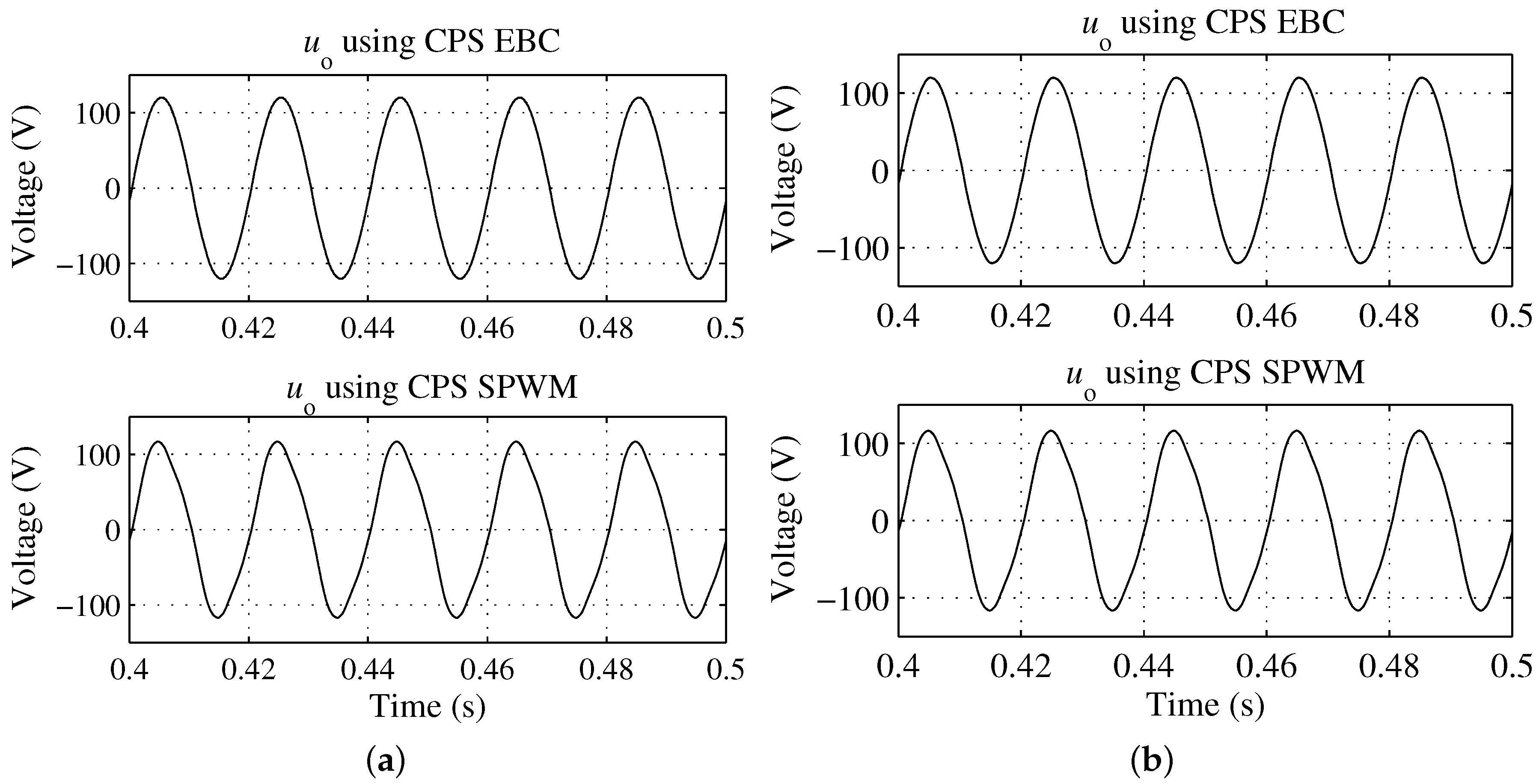

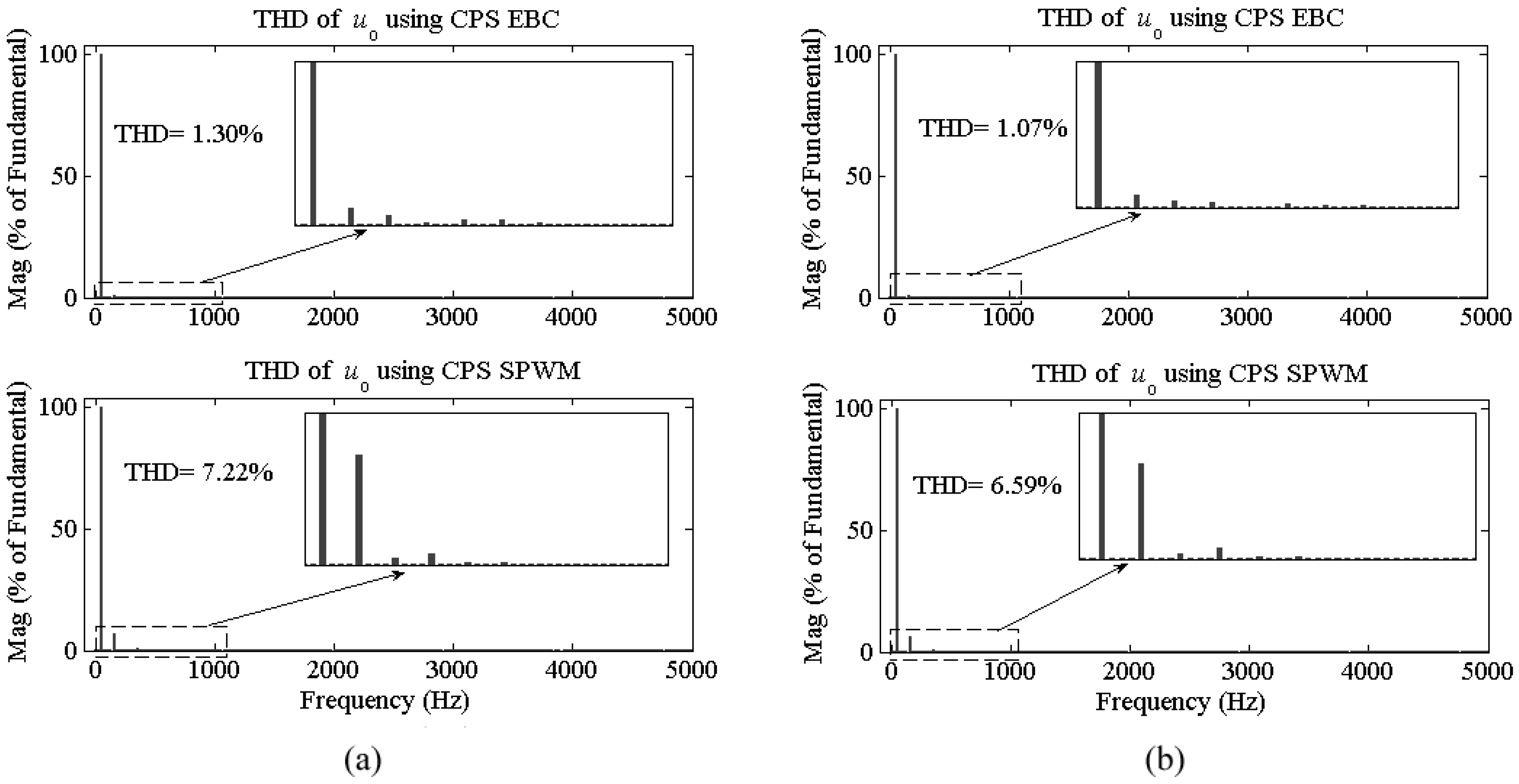

Figure 12a shows the simulation results under unbalance DC voltages (a ripple with a frequency

and an amplitude

is added in

). The comparison results demonstrate that

using CPS SPWM is not a ideal sine wave but with distortions. The FFT analysis in

Figure 13a shows low order harmonic voltages are contained in

. In comparison,

using the CPS EBC is kept as a ideal sine wave. No low order harmonic voltages are brought into

, as shown in

Figure 13a. Similarly, under the DC voltages mixed with low frequency ripples (

ripples with an amplitude

are added in

and

, respectively). The comparison results in

Figure 12b illustrate that

using the CPS SPWM distorts due to the low order harmonic voltages. However,

using the CPS EBC, is kept as a ideal sine wave. This can also be observed from the comparison of the FFT analysis in

Figure 13b.

Figure 14 and

Figure 15 display the experimental results using the CPS EBC and the CPS SPWM under the cases of unbalanced DC voltage and DC voltage with fluctuations. From the comparisons, it can be observed that the experimental results are consistent with the simulation results in

Figure 12. All the comparison results of the THD of

under the cases of unbalance DC voltages and DC voltages containing low frequency ripples are summarized in

Table 3. The figures and tables verify that the CPS EBC has strong inhibitions against fluctuations of DC sources.

4.4. The Dynamic Responses of CPS EBC to Load Variations

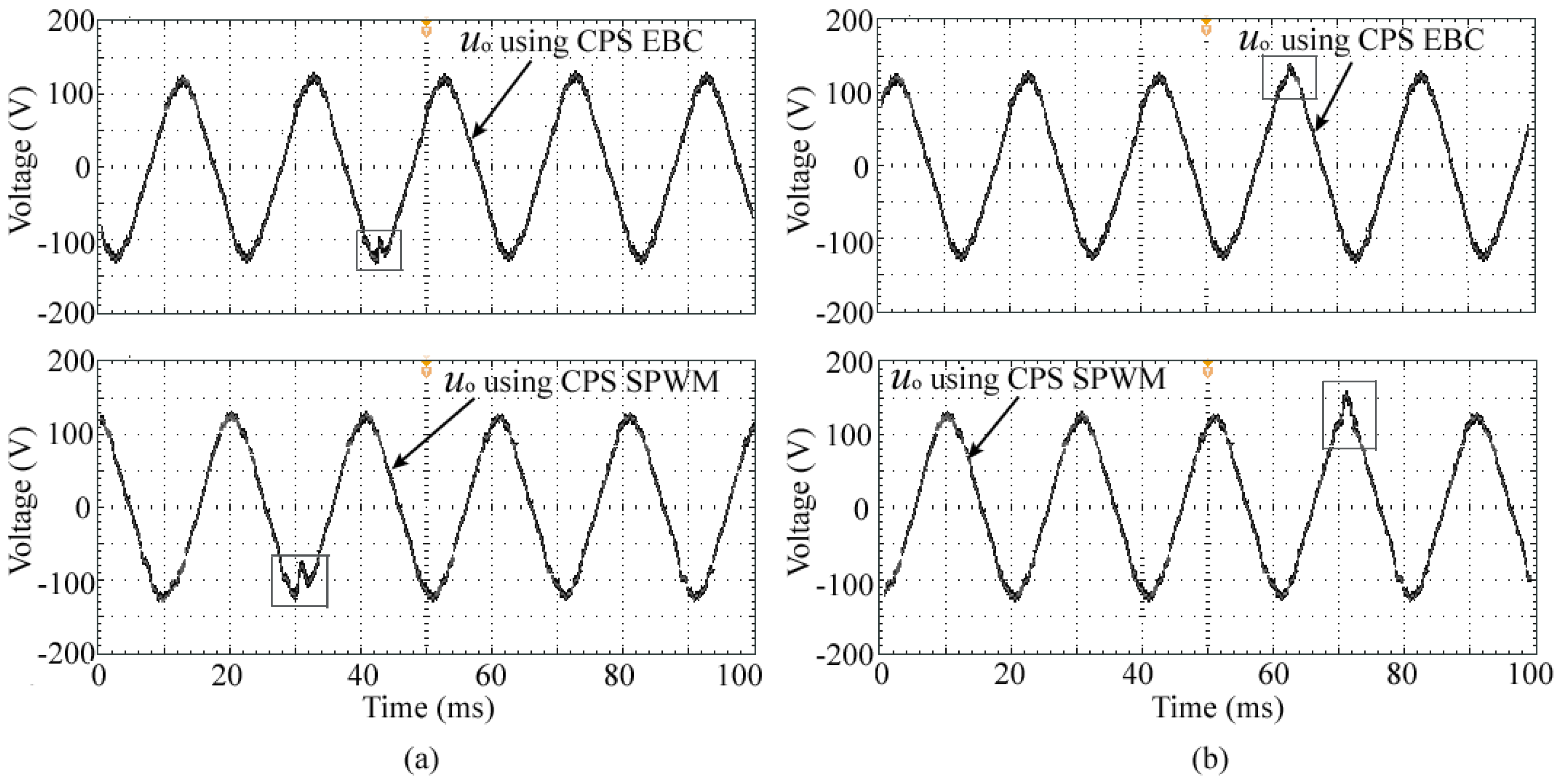

To evaluate the dynamic performances of the proposed CPS EBC, the responses to variations in the load of the converter using the CPS EBC is compared with that of the CPS SPWM.

Figure 16 and

Figure 17 demonstrate the comparison results.

In the simulation and experiment, the load steps from

at

and

at

. The comparison results of the voltage shoot

and the settling time

of the dynamic responses to the load variations are summarized in

Table 4. From the figures and table, it can be observed that, under the load variation,

and

are significantly reduced by using the proposed CPS EBC. For instance, under the load variation from

to

, the simulation results of

is reduced from

(using CPS SPWM) to

(using CPS EBC) and

is reduced from

(using CPS SPWM) to

(using CPS EBC).

Thus, the improved dynamic responses to load variations of the CPS EBC method are verified from the above simulation and experimental results.