Design of a Board-Level Integrated Multi-Channel Radio Frequency Source for the Transportable 40Ca+ Ion Optical Clock

Abstract

1. Introduction

2. Design of Integrated RF Source

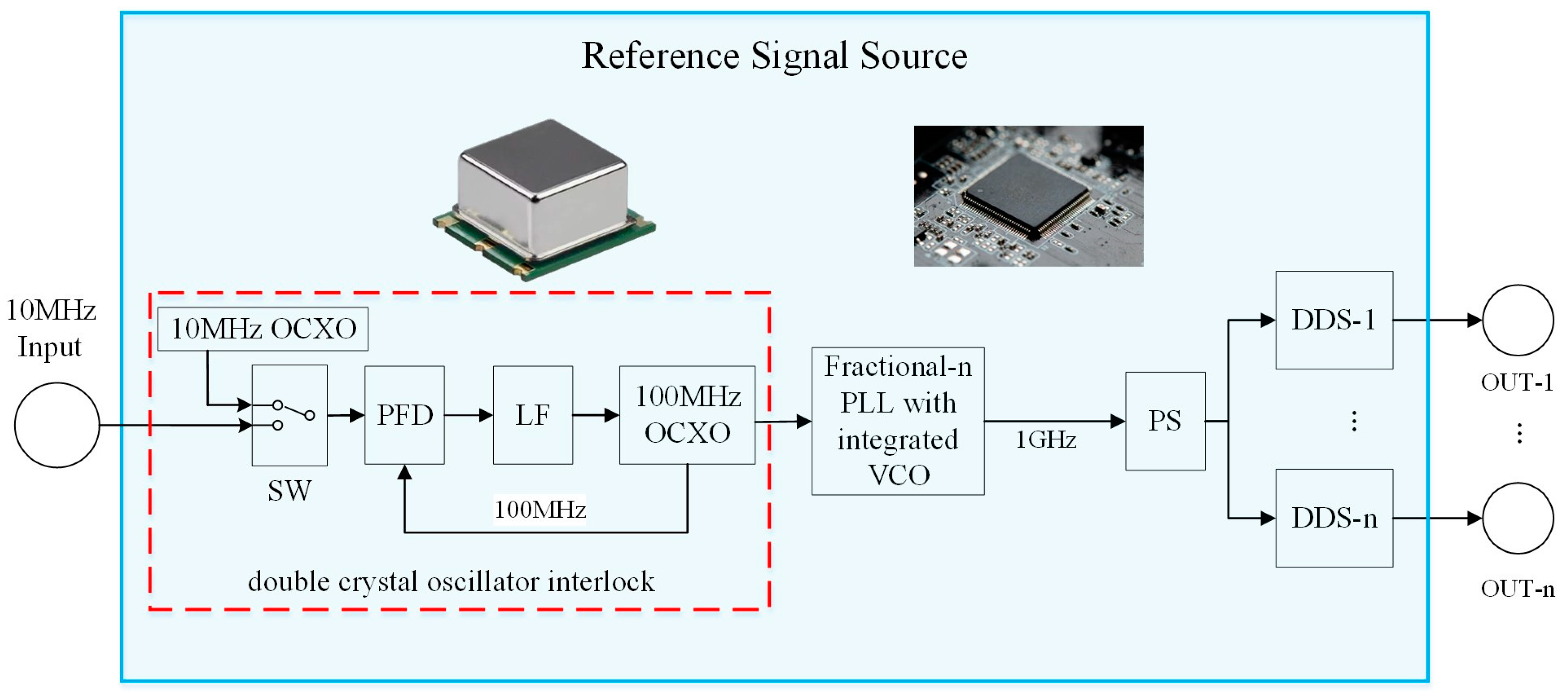

2.1. RF Signal Source

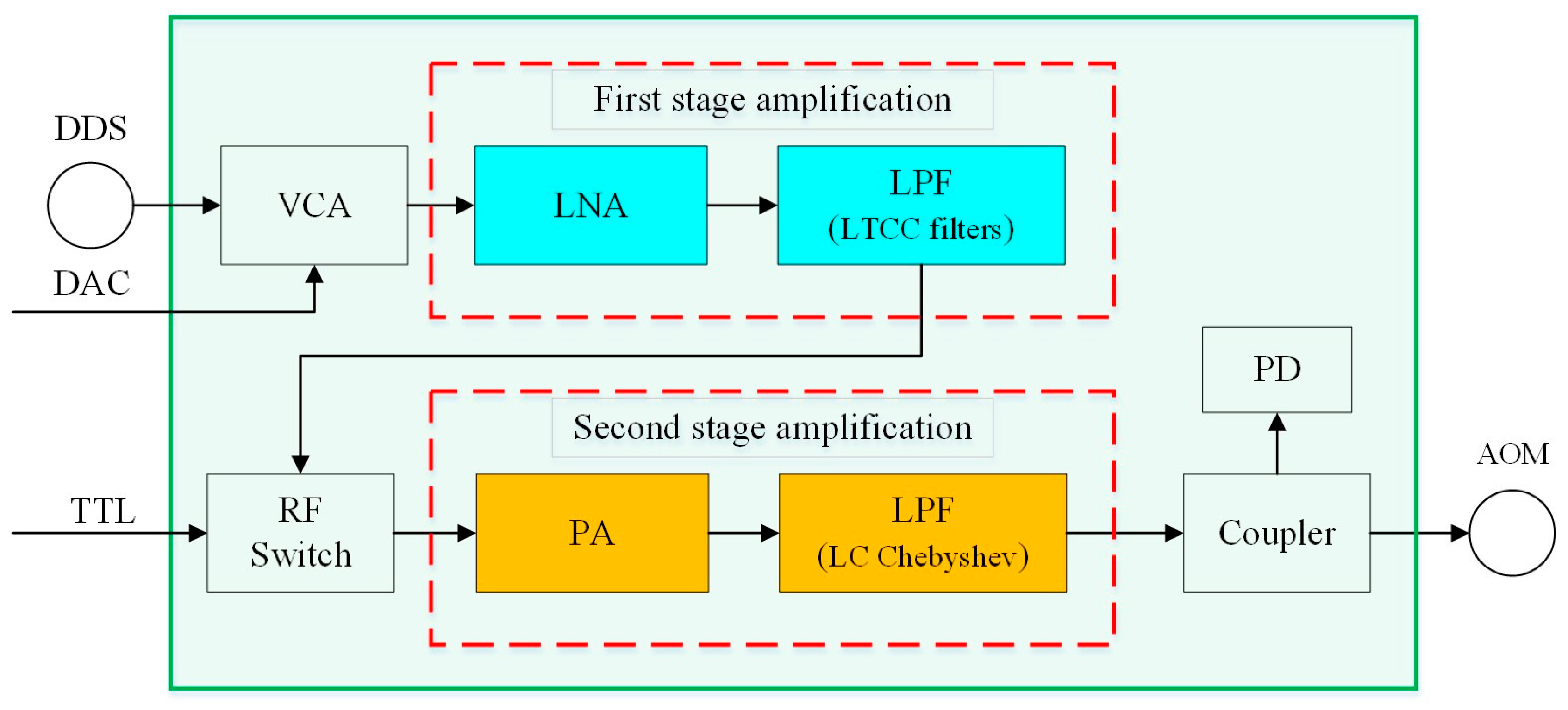

2.2. Power Amplification Circuit

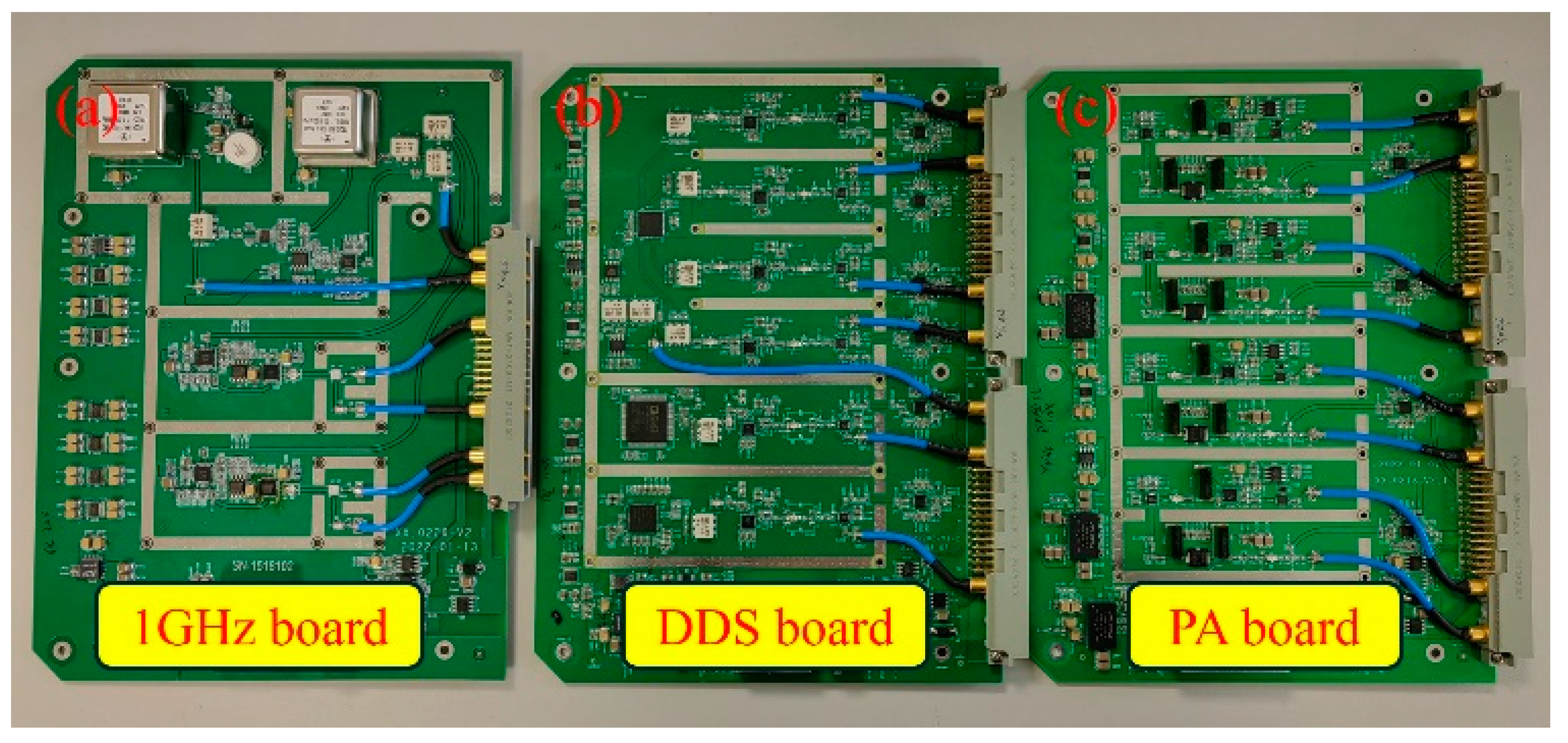

2.3. Design Result

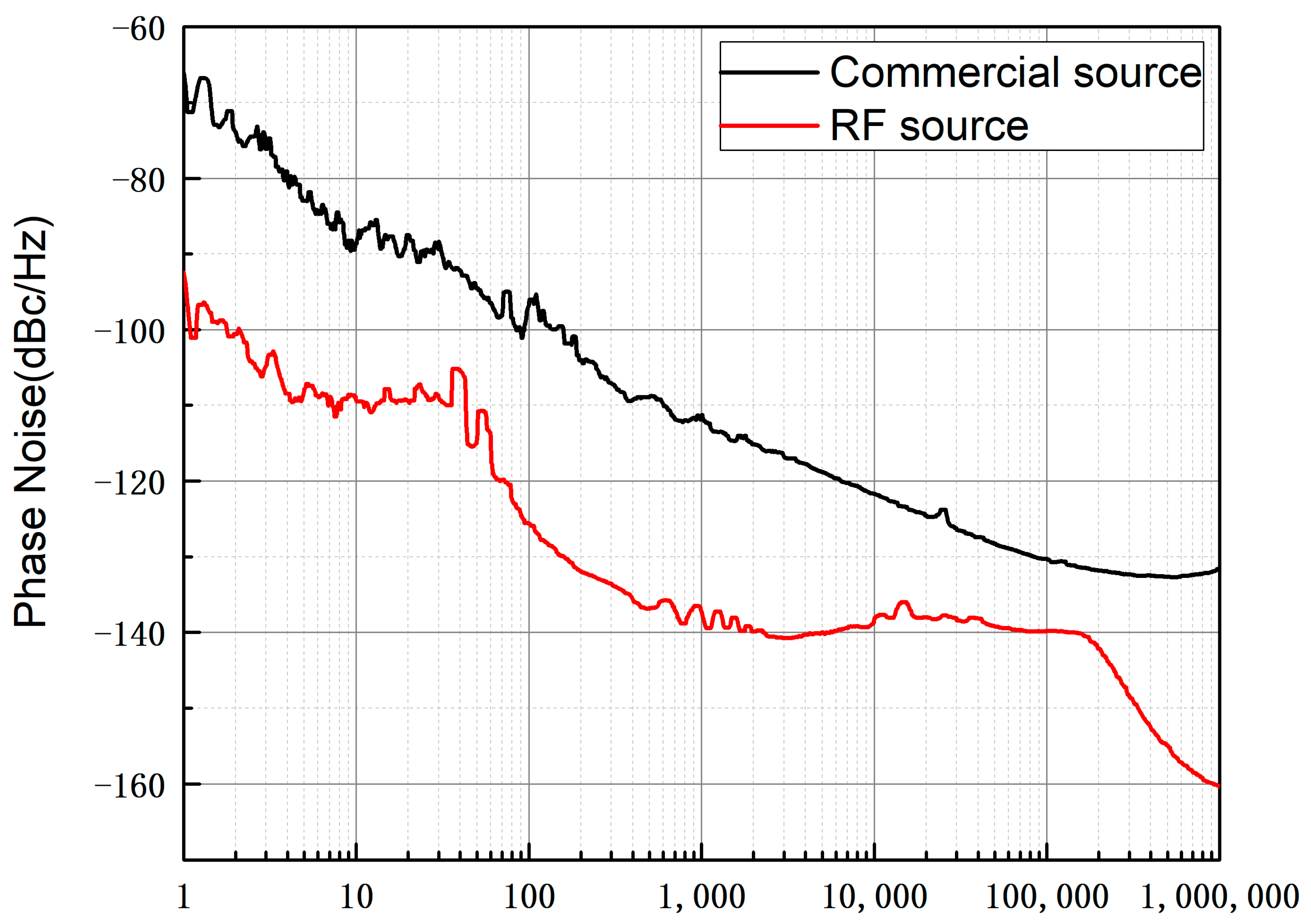

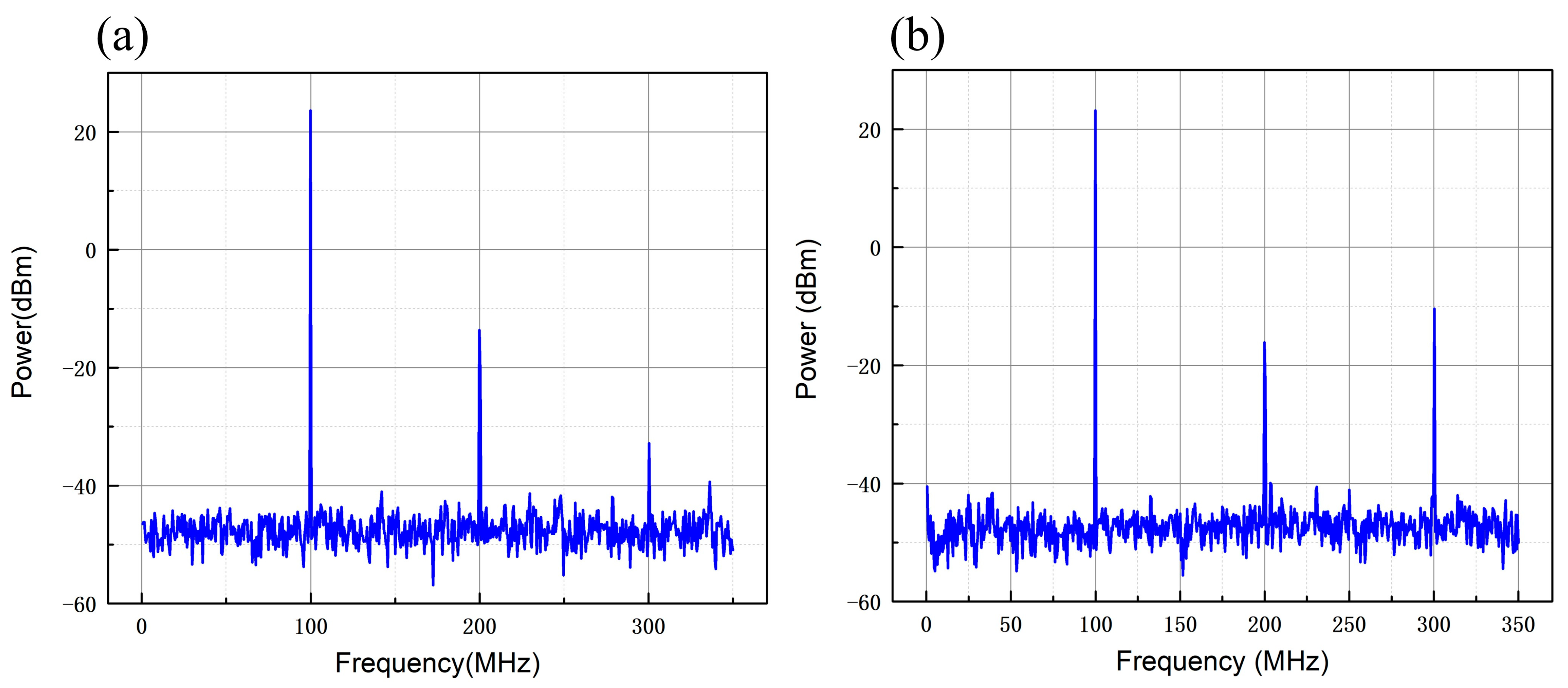

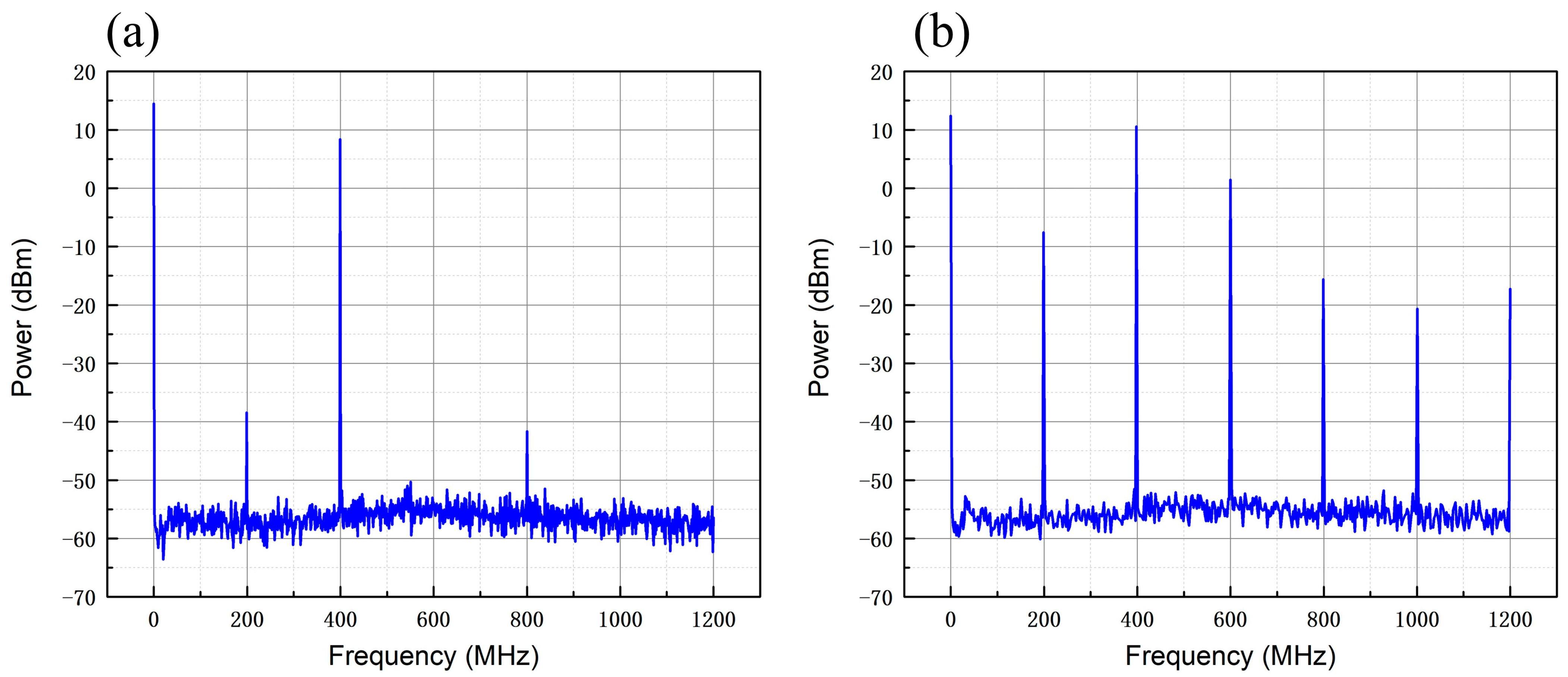

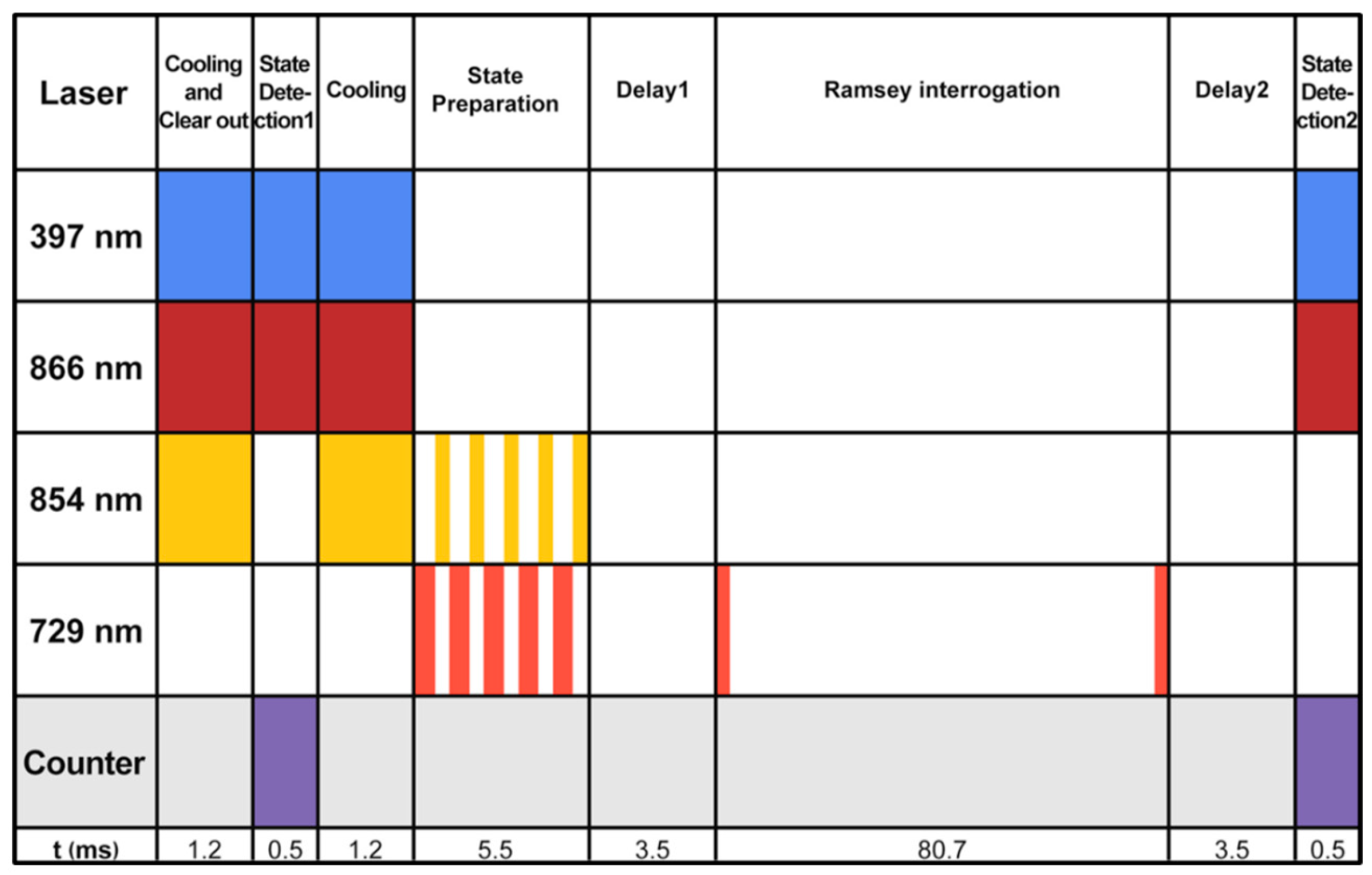

3. Experimental Results and Analysis

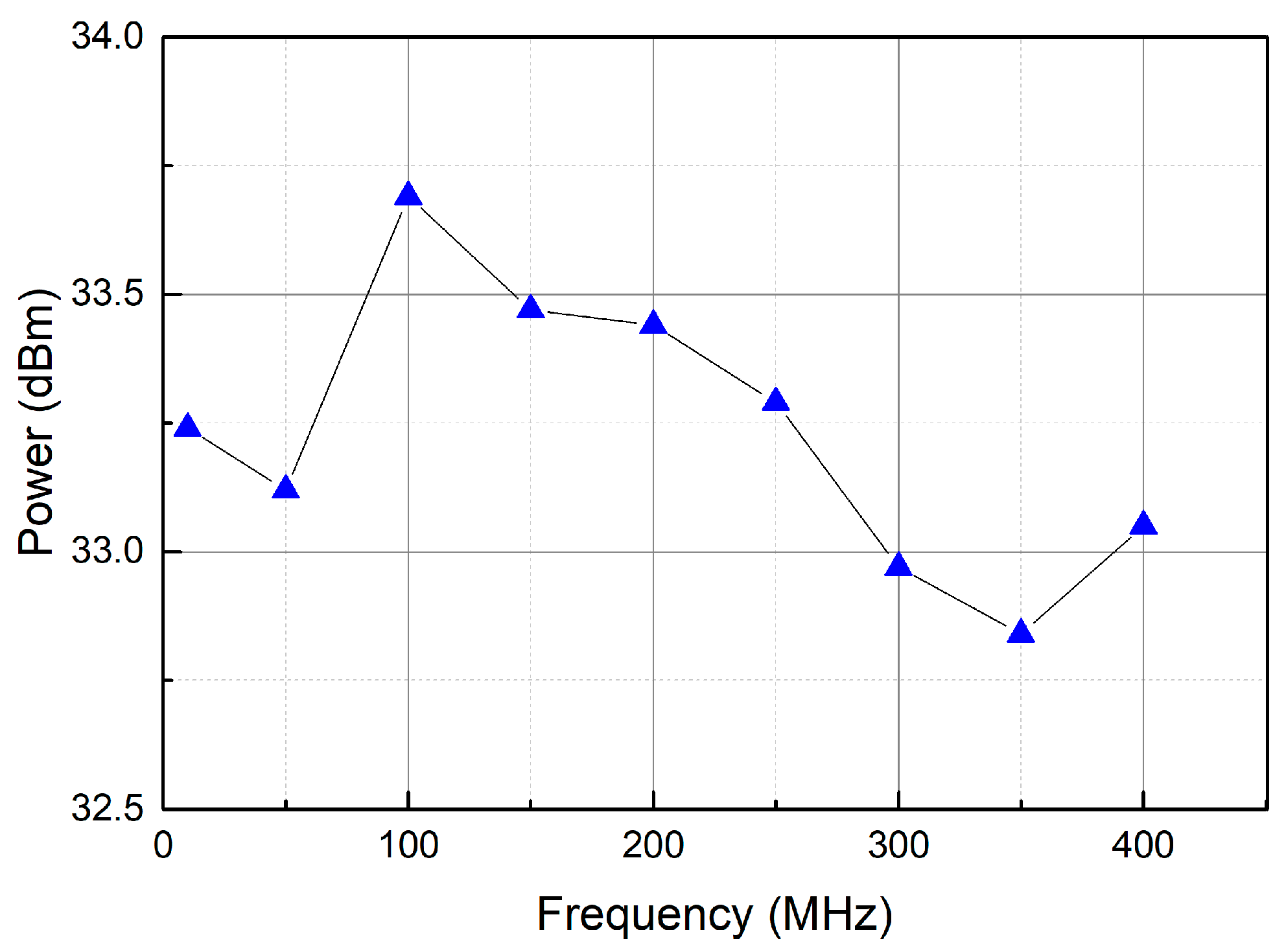

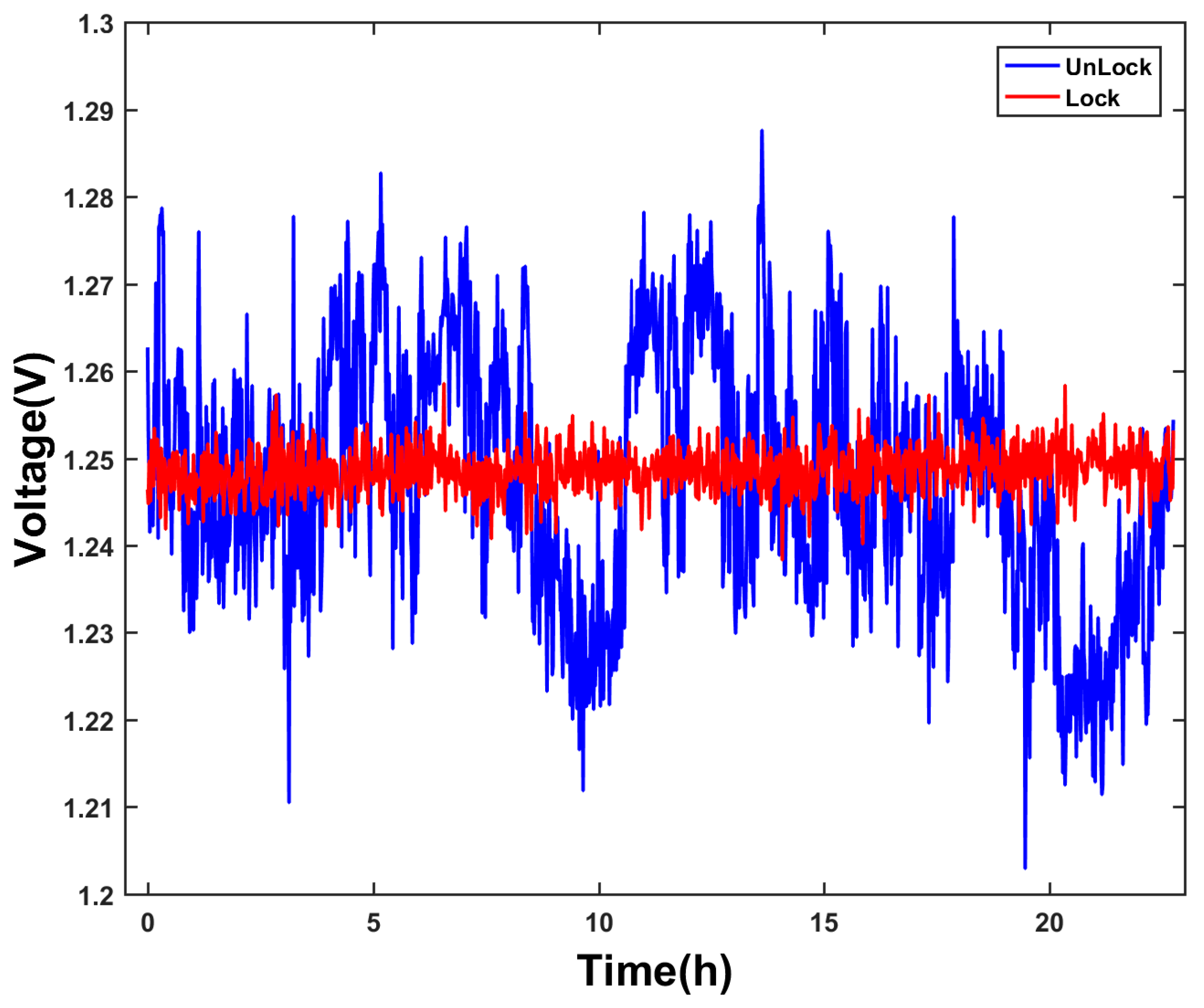

3.1. 729 nm Clock Laser Power Stability Test

3.2. 729 nm Clock Laser Timing Control Test

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Monroe, C.; Meekhof, D.M.; King, B.E.; Jefferts, S.R.; Itano, W.M.; Wineland, D.J.; Gould, P. Resolved-sideband Raman cooling of a bound atom to the 3D zero-point energy. Phys. Rev. Lett. 1995, 75, 4011–4014. [Google Scholar] [CrossRef]

- Li, J.J.; Zhang, F.F.; Wang, Z.M.; Xu, Y.C.; Liu, X.C.; Zong, N.; Zhang, S.J.; Xu, F.L.; Yang, F.; Yuan, L.; et al. High-energy single-frequency 167 nm deep-ultraviolet laser. Opt. Lett. 2018, 43, 2563–2566. [Google Scholar] [CrossRef] [PubMed]

- Chang, S.; Kwon, T.Y.; Lee, H.S.; Minogin, V.G. Laser sub-Doppler cooling of atoms in an arbitrarily directed magnetic field. Phys. Rev. A 2002, 66, 043404. [Google Scholar] [CrossRef]

- Larson, D.J.; Bergquist, J.C.; Bollinger, J.J.; Itano, W.M.; Wineland, D.J. Sympathetic cooling of trapped ions: A laser-cooled two-species nonneutral ion plasma. Phys. Rev. Lett. 1986, 57, 70–73. [Google Scholar] [CrossRef]

- Wells, A.L.; Cook, R.J. Simple theory of sideband cooling. Phys. Rev. A 1990, 41, 3916–3923. [Google Scholar] [CrossRef] [PubMed]

- Taichenachev, A.V.; Tumaikin, A.M.; Yudin, V.I.; Hollberg, L. Two-dimensional sideband Raman cooling and Zeeman-state preparation in an optical lattice. Phys. Rev. A 2001, 63, 033402. [Google Scholar] [CrossRef]

- Sun, Y.; Yao, Y.; Hao, Y.; Yu, H.; Jiang, Y.; Ma, L. Laser stabilizing to ytterbium clock transition with Rabi and Ramsey spectroscopy. Chin. Opt. Lett. 2020, 18, 070201. [Google Scholar] [CrossRef]

- Xu, M.; Wu, H.; Liang, Y.; Luo, D.; Wang, P.; Tan, Y.; Shao, C. Weak-Light Phase-Locking Time Delay Interferometry with Optical Frequency Combs. Sensors 2022, 22, 7349. [Google Scholar] [CrossRef] [PubMed]

- Bernard, J.E.; Marmet, L.; Madej, A.A. A laser frequency lock referenced to a single trapped ion. Opt. Commun. 1998, 150, 170–174. [Google Scholar] [CrossRef]

- Kessler, T.; Hagemann, C.; Grebing, C.; Legero, T.; Sterr, U.; Riehle, F.; Martin, M.J.; Chen, L.; Ye, J. A sub-40 mHz linewidth laser based on a silicon single-crystal optical cavity. Nat. Photonics 2011, 6, 687–692. [Google Scholar] [CrossRef]

- Blumroder, U.; Kochert, P.; Frohlich, T.; Kissinger, T.; Ortlepp, I.; Flugge, J.; Bosse, H.; Manske, E. A GPS-Referenced Wavelength Standard for High-Precision Displacement Interferometry at lambda = 633 nm. Sensors 2023, 23, 1734. [Google Scholar] [CrossRef] [PubMed]

- Takamoto, M.; Ushijima, I.; Ohmae, N.; Yahagi, T.; Kokado, K.; Shinkai, H.; Katori, H. Test of general relativity by a pair of transportable optical lattice clocks. Nat. Photonics 2020, 14, 411–415. [Google Scholar] [CrossRef]

- Sanner, C.; Huntemann, N.; Lange, R.; Tamm, C.; Peik, E.; Safronova, M.S.; Porsev, S.G. Optical clock comparison for Lorentz symmetry testing. Nature 2019, 567, 204–208. [Google Scholar] [CrossRef] [PubMed]

- Liu, D.; Wu, L.; Xiong, C.; Bao, L. Geopotential Difference Measurement Using Two Transportable Optical Clocks’ Frequency Comparisons. Remote Sens. 2024, 16, 2462. [Google Scholar] [CrossRef]

- Lisdat, C.; Grosche, G.; Quintin, N.; Shi, C.; Raupach, S.M.; Grebing, C.; Nicolodi, D.; Stefani, F.; Al-Masoudi, A.; Dorscher, S.; et al. A clock network for geodesy and fundamental science. Nat. Commun. 2016, 7, 12443. [Google Scholar] [CrossRef] [PubMed]

- Grotti, J.; Koller, S.; Vogt, S.; Häfner, S.; Sterr, U.; Lisdat, C.; Denker, H.; Voigt, C.; Timmen, L.; Rolland, A.; et al. Geodesy and metrology with a transportable optical clock. Nat. Phys. 2018, 14, 437–441. [Google Scholar] [CrossRef]

- Boldbaatar, E.; Grant, D.; Choy, S.; Zaminpardaz, S.; Holden, L. Evaluating Optical Clock Performance for GNSS Positioning. Sensors 2023, 23, 5998. [Google Scholar] [CrossRef]

- Safronova, M.S.; Porsev, S.G.; Sanner, C.; Ye, J. Two Clock Transitions in Neutral Yb for the Highest Sensitivity to Variations of the Fine-Structure Constant. Phys. Rev. Lett. 2018, 120, 173001. [Google Scholar] [CrossRef]

- Lemke, N.D.; Martin, K.W.; Beard, R.; Stuhl, B.K.; Metcalf, A.J.; Elgin, J.D. Measurement of Optical Rubidium Clock Frequency Spanning 65 Days. Sensors 2022, 22, 1982. [Google Scholar] [CrossRef] [PubMed]

- Riehle, F.; Gill, P.; Arias, F.; Robertsson, L. The CIPM list of recommended frequency standard values: Guidelines and procedures. Metrologia 2018, 55, 188–200. [Google Scholar] [CrossRef]

- Takumi, K.; Akifumi, T.; Daisuke, A.; Akio, K.; Akiko, N.; Kazumoto, H.; Yusuke, H.; Masato, W.; Hajime, I.; Takehiko, T.; et al. Search for Ultralight Dark Matter from Long-Term Frequency Comparisons of Optical and Microwave Atomic Clocks. Phys. Rev. Lett. 2022, 129, 241301. [Google Scholar]

- Huang, Y.; Guan, H.; Liu, P.; Bian, W.; Ma, L.; Liang, K.; Li, T.; Gao, K. Frequency Comparison of Two 40Ca+ Optical Clocks with an Uncertainty at the 10−17 Level. Phys. Rev. Lett. 2016, 116, 013001. [Google Scholar] [CrossRef] [PubMed]

- Cao, J.; Zhang, P.; Shang, J.; Cui, K.; Yuan, J.; Chao, S.; Wang, S.; Shu, H.; Huang, X. A compact, transportable single-ion optical clock with 7.8 × 10−17 systematic uncertainty. Appl. Phys. B 2017, 123, 112. [Google Scholar] [CrossRef]

- Hao, Y.; Hu, R.; Zhang, B.; Zeng, M.; Zhang, H.; Ma, Z.; Huang, Y.; Chen, Q.; Gao, K.; Guan, H. Stability improvement of 40Ca+ optical clock by using a transportable ultra-stable cavity. Opt. Express 2024, 32, 4081–4092. [Google Scholar] [CrossRef] [PubMed]

- Bowler, R.; Warring, U.; Britton, J.W.; Sawyer, B.C.; Amini, J. Arbitrary waveform generator for quantum information processing with trapped ions. Rev. Sci. Instrum. 2013, 84, 033108. [Google Scholar] [CrossRef]

- Beev, N.; Fenske, J.A.; Hannig, S.; Schmidt, P.O. A low-drift, low-noise, multichannel dc voltage source for segmented-electrode Paul traps. Rev. Sci. Instrum. 2017, 88, 054704. [Google Scholar] [CrossRef] [PubMed]

- Qin, X.; Shi, Z.; Xie, Y.; Wang, L.; Rong, X.; Jia, W.; Zhang, W.; Du, J. An integrated device with high performance multi-function generators and time-to-digital convertors. Rev. Sci. Instrum. 2017, 88, 014702. [Google Scholar] [CrossRef]

- Leandro, S.; Kenneth, T.; Neal, W.; Chris, S.; Collin, B.; Sho, U.; Silvia, Z.; Salvatore, M.; Gustavo, C.; Sara, S.; et al. The QICK (Quantum Instrumentation Control Kit): Readout and control for qubits and detectors. Rev. Sci. Instrum. 2022, 93, 044709. [Google Scholar]

- Zhang, B.; Huang, Y.; Zhang, H.; Hao, Y.; Zeng, M.; Guan, H.; Gao, K. Progress on the 40Ca+ ion optical clock. Chin. Phys. B 2020, 29, 74209. [Google Scholar] [CrossRef]

- Zhu, M.D.; Yan, L.; Qin, X.; Zhang, W.Z.; Lin, Y.; Du, J. FPGA based hardware platform for trapped-ion-based multi-level quantum systems. Chin. Phys. B 2023, 32, 090702. [Google Scholar] [CrossRef]

- Shaik Peerla, R.; Dutta, A.; Sahoo, B.D. An Extended Range Divider Technique for Multi-Band PLL. J. Low Power Electron. Appl. 2023, 13, 43. [Google Scholar] [CrossRef]

- Song, Y.J.; Pany, T.; Won, J.H. Theoretical Upper and Lower Limits for Normalized Bandwidth of Digital Phase-Locked Loop in GNSS Receivers. Sensors 2023, 23, 5887. [Google Scholar] [CrossRef]

- Blatnik, A.; Batagelj, B. Wideband Low Phase-Noise Signal Generation Using Coaxial Resonator in Cascaded Phase Locked Loop. Electronics 2024, 13, 1934. [Google Scholar] [CrossRef]

- Farhad, B.; Alireza, G.R.; Samad, S.; Massoud, T. A fast settling frequency synthesizer with switched-bandwidth loop filter. Int. J. Circuit Theory Appl. 2021, 49, 2021–2031. [Google Scholar]

- Sun, L.; Luo, Y.; Deng, Z.; Wang, J.; Liu, B. Novel Power-Efficient Fast-Locking Phase-Locked Loop Based on Adaptive Time-to-Digital Converter-Aided Acceleration Compensation Technology. Electronics 2024, 13, 3586. [Google Scholar] [CrossRef]

- Zhang, B.; Huang, Y.; Hao, Y.; Zhang, H.; Zeng, M.; Guan, H.; Gao, K. Improvement in the stability of a 40Ca+ ion optical clock using the Ramsey method. J. Appl. Phys. 2020, 128, 143105. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, B.; Yang, Y.; Zhang, H.; Hu, R.; Mao, H.; Huang, Y.; Gao, K.; Guan, H. Design of a Board-Level Integrated Multi-Channel Radio Frequency Source for the Transportable 40Ca+ Ion Optical Clock. Sensors 2025, 25, 1044. https://doi.org/10.3390/s25041044

Wang B, Yang Y, Zhang H, Hu R, Mao H, Huang Y, Gao K, Guan H. Design of a Board-Level Integrated Multi-Channel Radio Frequency Source for the Transportable 40Ca+ Ion Optical Clock. Sensors. 2025; 25(4):1044. https://doi.org/10.3390/s25041044

Chicago/Turabian StyleWang, Bin, Yuanhang Yang, Huaqing Zhang, Ruming Hu, Haicen Mao, Yao Huang, Kelin Gao, and Hua Guan. 2025. "Design of a Board-Level Integrated Multi-Channel Radio Frequency Source for the Transportable 40Ca+ Ion Optical Clock" Sensors 25, no. 4: 1044. https://doi.org/10.3390/s25041044

APA StyleWang, B., Yang, Y., Zhang, H., Hu, R., Mao, H., Huang, Y., Gao, K., & Guan, H. (2025). Design of a Board-Level Integrated Multi-Channel Radio Frequency Source for the Transportable 40Ca+ Ion Optical Clock. Sensors, 25(4), 1044. https://doi.org/10.3390/s25041044