An Area-Efficient Readout Circuit for a High-SNR Triple-Gain LOFIC CMOS Image Sensor †

Abstract

1. Introduction

- To mitigate the SNR drop, we propose the triple-gain LOFIC CIS without enlarging the pixel area or degrading motion artifacts.

- We propose a readout circuit that is area-efficient for the triple-gain LOFIC CIS.

- We evaluate a fabricated test chip and estimate the SNR.

Updates from the Conference Proceeding

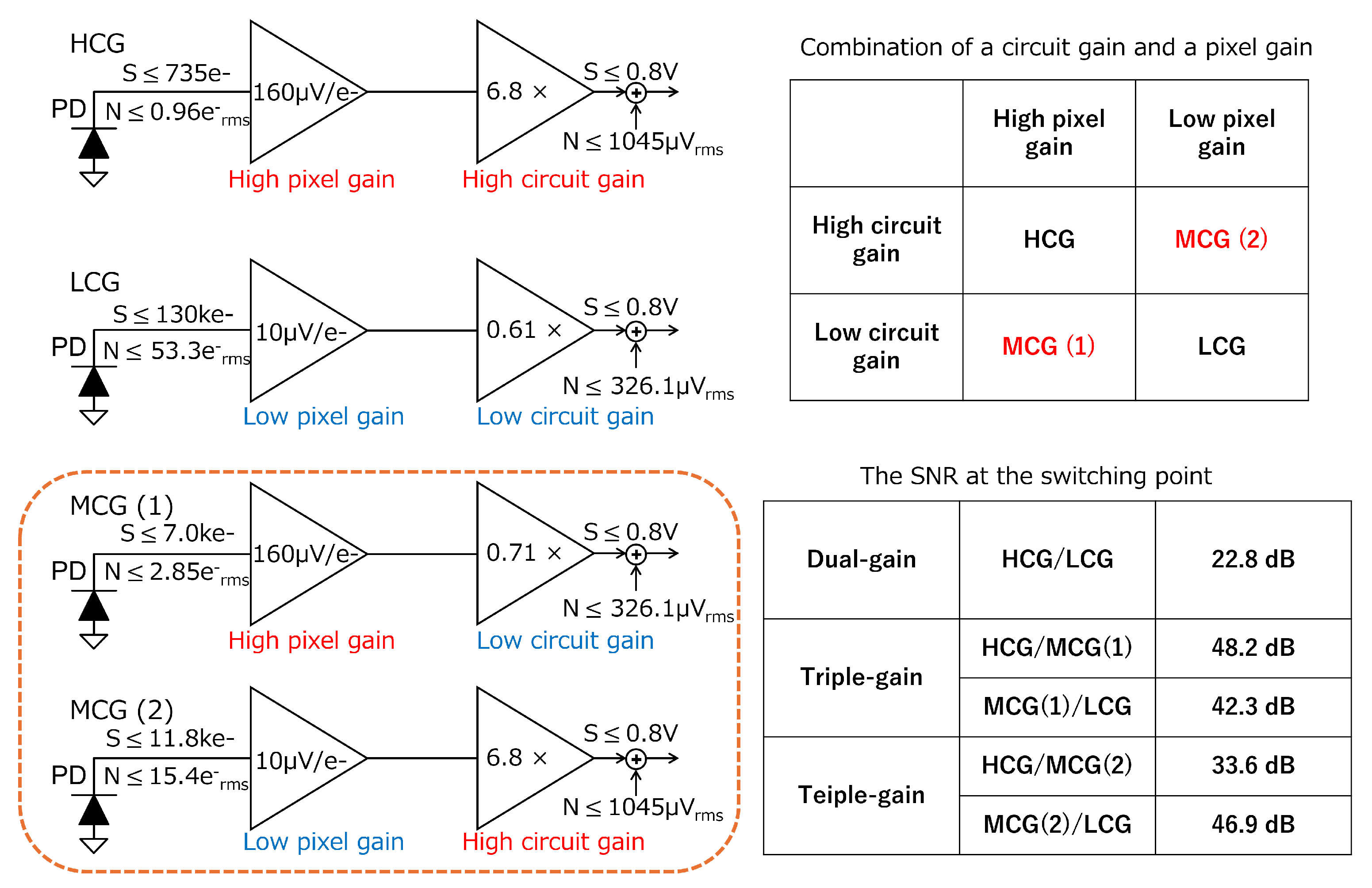

- Pixel- and circuit-gain combination for the MCG signal (Section 2.1, Figure 1).

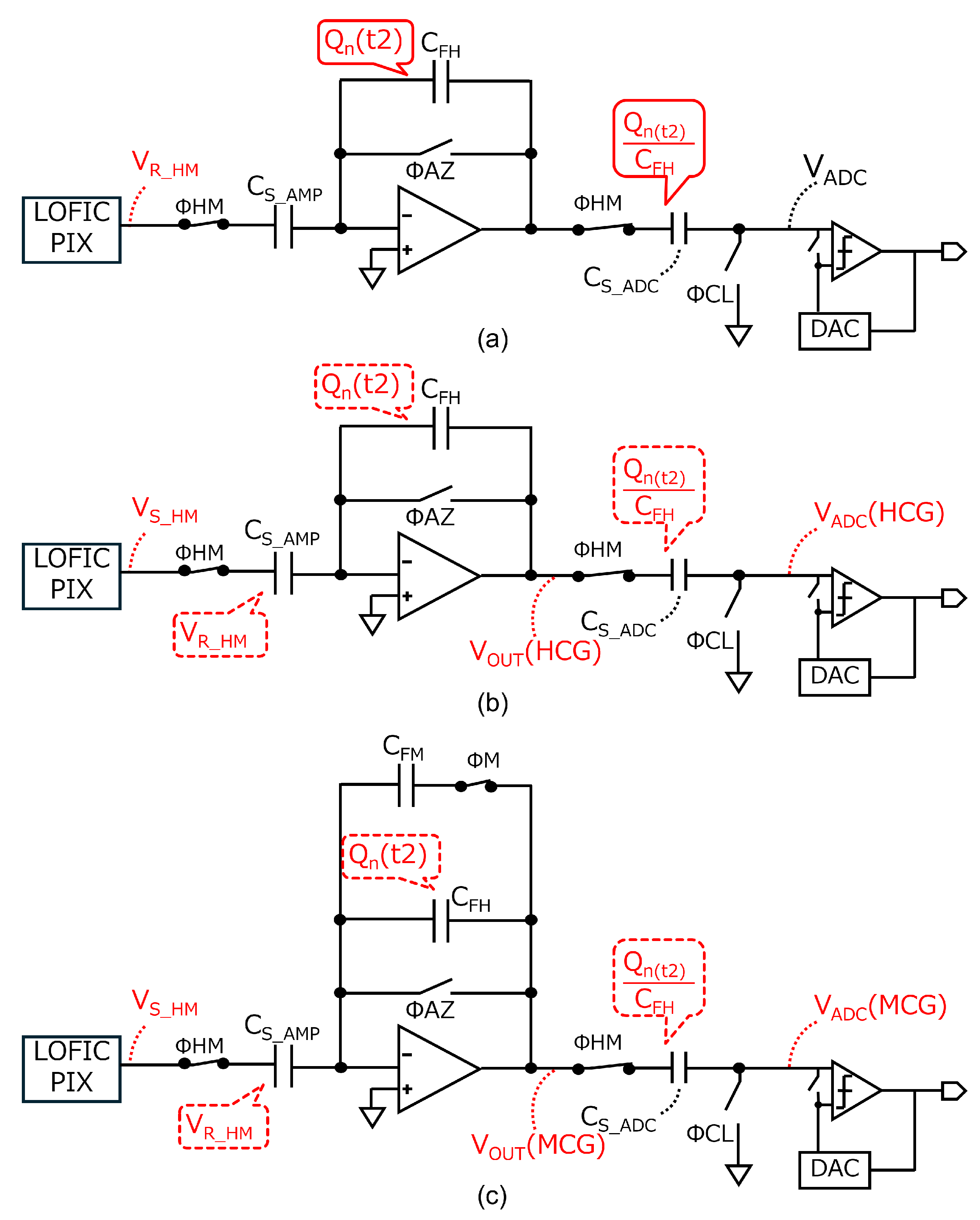

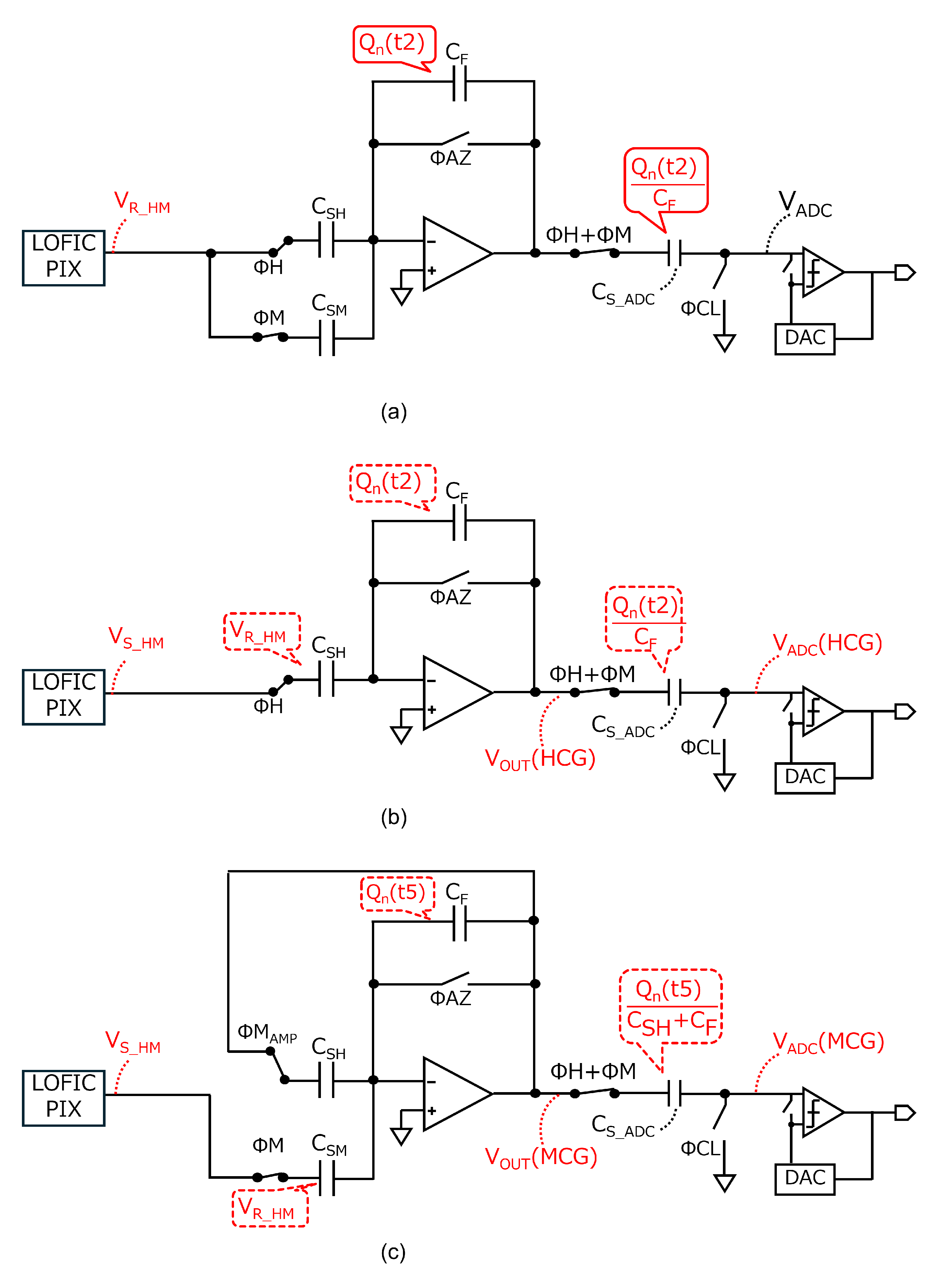

- Details of the baseline circuit and comparison with the proposed readout circuit (Section 3.1, Figure 3).

- Noise analysis of baseline circuit and proposed readout circuit (Figure 4 and Figure 6).

- A discussion of this study and a comparison with other works (Section 4).

2. Concept-Level Design

2.1. Pixel- and Circuit-Gain Combination for the MCG Signal

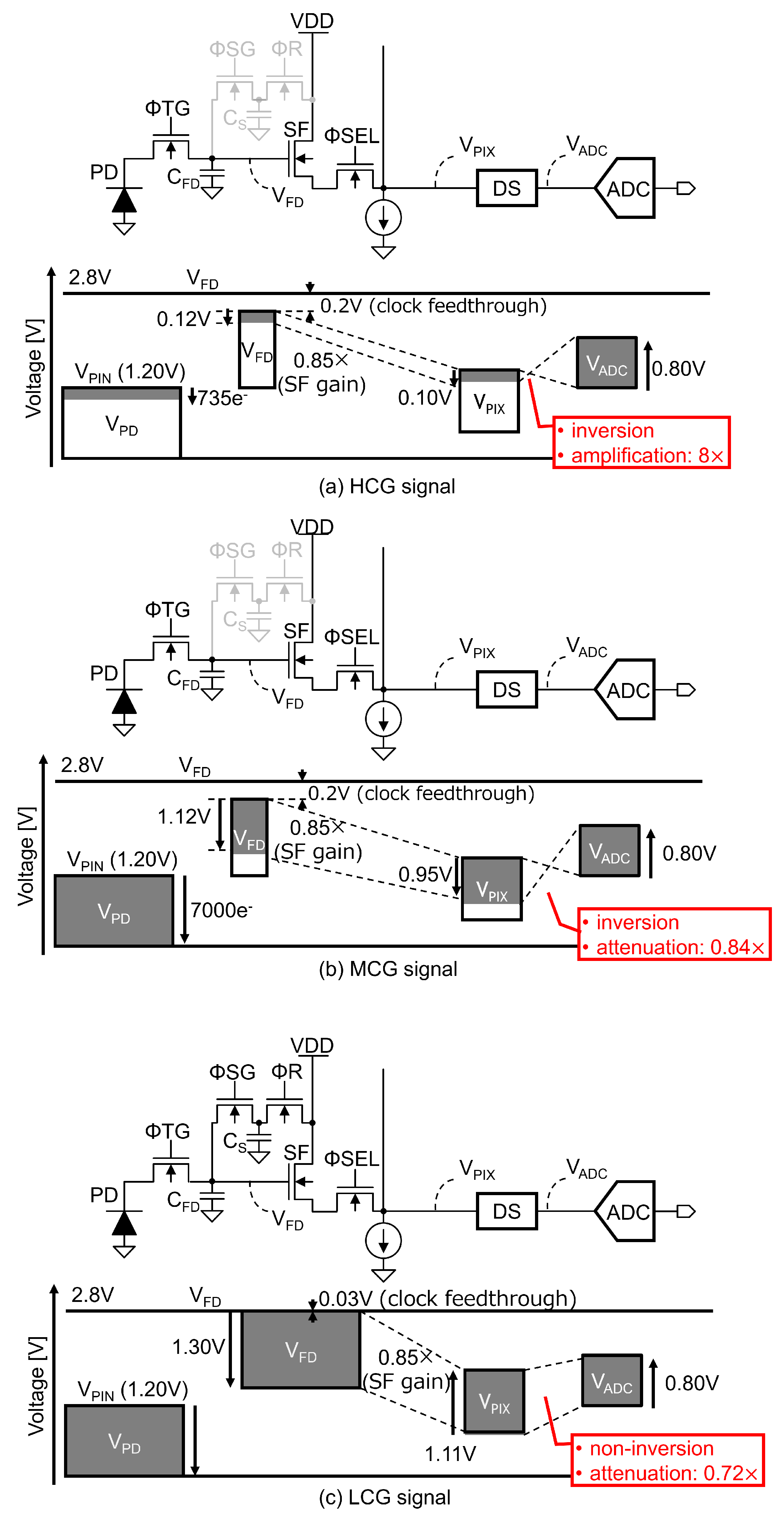

2.2. Voltage-Level Diagram

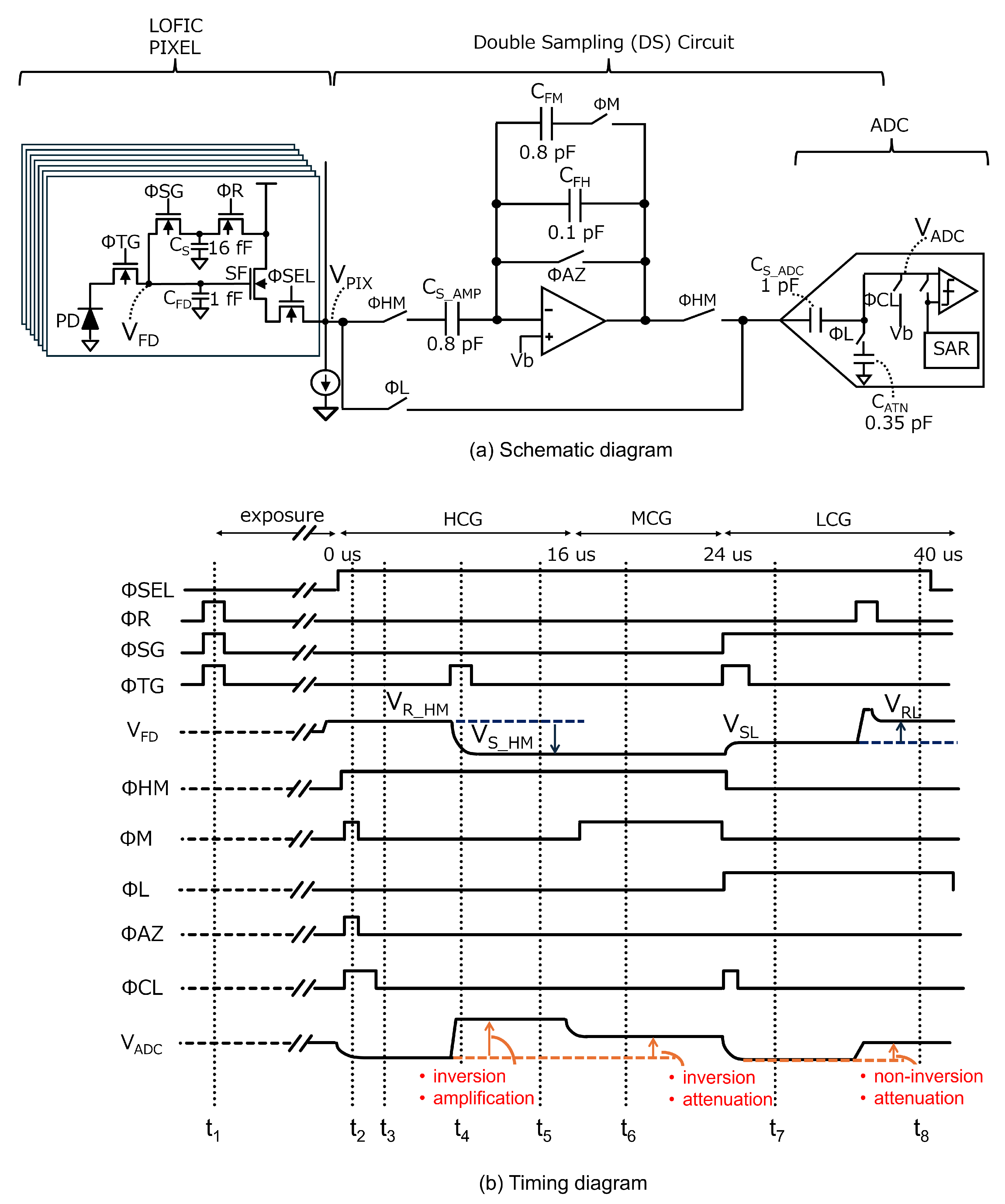

3. Proposed Readout Circuit for a Triple-Gain LOFIC CIS

3.1. Baseline Readout Circuit

3.2. Proposed Circuit

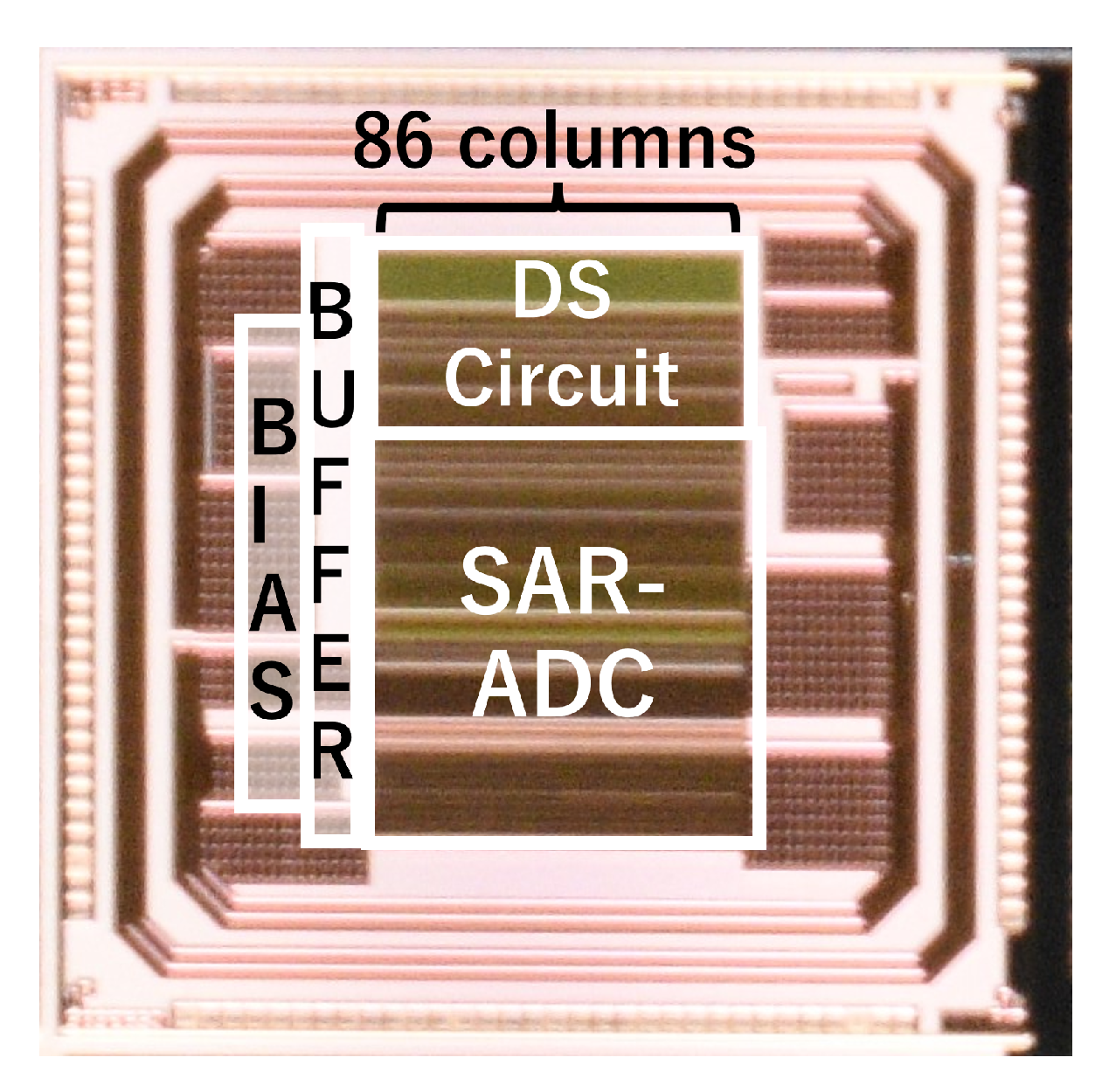

4. Fabrication and Evaluation of a Test Chip

Discussion

5. Summary

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Scheffer, D.; Dierickx, B.; Meynants, G. Random addressable 2048/spl times/2048 active pixel image sensor. IEEE Trans. Electron Devices 1997, 44, 1716–1720. [Google Scholar] [CrossRef]

- de Moraes Cruz, C.A.; de Lima Monteiro, D.W.; Souza, A.K.P.; da Silva, L.L.F.; de Sousa, D.R.; de Oliveira, E.G. Voltage Mode FPN Calibration in the Logarithmic CMOS Imager. IEEE Trans. Electron Devices 2015, 62, 2528–2534. [Google Scholar] [CrossRef]

- Komobuchi, H. 1/4 inch NTSC Format Hyper-D Range IL-CCD. In Proceedings of the 1995 IEEE Workshop on CCDs and AISs. SS-1, Dana Point, CA, USA, 20 April 1995. [Google Scholar]

- Yadid-Pecht, O.; Fossum, E. Wide intrascene dynamic range CMOS APS using dual sampling. IEEE Trans. Electron Devices 1997, 44, 1721–1723. [Google Scholar] [CrossRef]

- Takayanagi, I.; Fukunaga, Y.; Yoshida, T.; Nakamura, J. A four-transistor capacitive feedback reset active pixel and its reset noise reduction capability. In Proceedings of the IEEE Workshop on CCD and AIS, Lake Tahoe, NA, USA, 7–9 June 2001; pp. 118–121. [Google Scholar]

- Mase, M.; Kawahito, S.; Sasaki, M.; Wakamori, Y.; Furuta, M. A wide dynamic range CMOS image sensor with multiple exposure-time signal outputs and 12-bit column-parallel cyclic A/D converters. IEEE J. Solid-State Circuits 2005, 40, 2787–2795. [Google Scholar] [CrossRef]

- Fowler, B.; Liu, C.; Mims, S.; Balicki, J.; Li, W.; Do, H.; Vu, P. Wide dynamic range low light level CMOS image sensor. In Proceedings of the International Image Sensor Workshop, Bergen, Norway, 26–28 June 2009; pp. 1–4. [Google Scholar]

- Huggett, A.; Silsby, C.; Cami, S.; Beck, J. A dual-conversion-gain video sensor with dewarping and overlay on a single chip. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 52–53. [Google Scholar]

- Meynants, G.; Beeckman, G.; Van Wichelen, K.; De Ridder, T.; Koch, M.; Schippers, G.; Bonnifait, M.; Diels, W.; Bogaerts, J. Backside illuminated 84 dB global shutter image sensor. In Proceedings of the International Image Sensor Workshop (IISS), Vaals, The Netherlands, 8–11 June 2015; pp. 220–224. [Google Scholar]

- Miyauchi, K.; Mori, K.; Isozaki, T.; Sawai, Y.; Yasuda, N.; Chien, H.C.; Fu, K.W.C.; Takayanagi, I.; Nakamura, J. 4.0 μm Stacked Voltage Mode Global Shutter Pixels with Single Exposure High Dynamic Range and Phase Detection Auto Focus Capability. ITE Trans. Media Technol. Appl. 2022, 10, 234–242. [Google Scholar] [CrossRef]

- Cremers, B.; Freson, T.; Esquenet, C.; Vroom, W.; Prathipati, A.K.; Okcan, B.; Luypaert, C.; Jiang, H.; Witters, H.; Compiet, J.; et al. A 5MPixel Image Sensor with a 3.45 μm Dual Storage Global Shutter Back-Side Illuminated Pixel with 90 dB DR . In Proceedings of the 2023 International Image Sensors Workshop, Crieff, UK, 21–25 May 2023; pp. 21–25. [Google Scholar]

- Gao, Z.; Park, G.; Fu, L.; Chapinal, G.; Yang, J.; Freson, T.; Qin, Q.; Guo, J.; Zhu, F.; Ding, S.; et al. A 2.2 μm 2-Layer Stacked HDR Voltage Domain Global Shutter CMOS Image Sensor with Dual Conversion Gain and 1.2 e-FPN. In Proceedings of the 2023 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 9–13 December 2023; pp. 1–4. [Google Scholar]

- Chamberlain, S.; Lee, J. A novel wide dynamic range silicon photodetector and linear imaging array. IEEE Trans. Electron Devices 1984, 31, 175–182. [Google Scholar] [CrossRef]

- Sakai, S.; Tashiro, Y.; Kawada, S.; Kuroda, R.; Akahane, N.; Mizobuchi, K.; Sugawa, S. Pixel Scaling in Complementary Metal Oxide Silicon Image Sensor with Lateral Overflow Integration Capacitor. Jpn. J. Appl. Phys. 2010, 49, 04DE03. [Google Scholar] [CrossRef]

- Sakano, Y.; Sakai, S.; Tashiro, Y.; Kato, Y.; Akiyama, K.; Honda, K.; Sato, M.; Sakakibara, M.; Taura, T.; Azami, K.; et al. 224-ke saturation signal global shutter CMOS image sensor with in-pixel pinned storage and lateral overflow integration capacitor. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–9 June 2017; pp. C250–C251. [Google Scholar]

- Takayanagi, I.; Miyauchi, K.; Okura, S.; Mori, K.; Nakamura, J.; Sugawa, S. A 120-ke− Full-Well Capacity 160 μV/e− Conversion Gain 2.8-μm Backside-Illuminated Pixel with a Lateral Overflow Integration Capacitor. Sensors 2019, 19, 5572. [Google Scholar] [CrossRef] [PubMed]

- Shike, H.; Kuroda, R.; Kobayashi, R.; Murata, M.; Fujihara, Y.; Suzuki, M.; Harada, S.; Shibaguchi, T.; Kuriyama, N.; Hatsui, T.; et al. A Global Shutter Wide Dynamic Range Soft X-Ray CMOS Image Sensor with Backside- Illuminated Pinned Photodiode, Two-Stage Lateral Overflow Integration Capacitor, and Voltage Domain Memory Bank. IEEE Trans. Electron Devices 2021, 68, 2056–2063. [Google Scholar] [CrossRef]

- Oikawa, T.; Kuroda, R.; Takahashi, K.; Shiba, Y.; Fujihara, Y.; Shike, H.; Murata, M.; Kuo, C.C.; da Silva, Y.R.S.C.; Goto, T.; et al. A 1000 fps high SNR voltage-domain global shutter CMOS image sensor with two-stage LOFIC for in-situ fluid concentration distribution measurements. In Proceedings of the Proceedings IISW, Virtual, 20–23 September 2021; pp. 258–261. [Google Scholar]

- Oh, M.; Velichko, S.; Johnson, S.; Guidash, M.; Chang, H.C.; Tekleab, D.; Gravelle, B.; Nicholes, S.; Suryadevara, M.; Collins, D.; et al. Automotive 3.0 μm Pixel High Dynamic Range Sensor with LED Flicker Mitigation. Sensors 2020, 20, 1390. [Google Scholar] [CrossRef] [PubMed]

- Fujihara, Y.; Murata, M.; Nakayama, S.; Kuroda, R.; Sugawa, S. An Over 120 dB Single Exposure Wide Dynamic Range CMOS Image Sensor with Two-Stage Lateral Overflow Integration Capacitor. IEEE Trans. Electron Devices 2021, 68, 152–157. [Google Scholar] [CrossRef]

- Velichko, S.; Jasinski, D.; Guidash, M.; Tekleab, D.; Innocent, M.; Perkins, A.; Amanullah, S.; Suryadevara, M.; Silsby, C.; Beck, J. Automotive 3 μm HDR Image Sensor with LFM and Distance Functionality. IEEE Trans. Electron Devices 2022, 69, 2951–2956. [Google Scholar] [CrossRef]

- Takayanagi, I.; Kuroda, R. HDR CMOS Image Sensors for Automotive Applications. IEEE Trans. Electron Devices 2022, 69, 2815–2823. [Google Scholar] [CrossRef]

- Asatsuma, T.; Sakano, Y.; Iida, S.; Takami, M.; Yoshiba, I.; Ohba, N.; Mizuno, H.; Oka, T.; Yamaguchi, K.; Suzuki, A.; et al. Sub-pixel architecture of cmos image sensor achieving over 120 db dynamic range with less motion artifact characteristics. In Proceedings of the 2019 International Image Sensor Workshop, Snowbird, UT, USA, 23–27 June 2019; Volume 1. [Google Scholar]

- Wakashima, S.; Kusuhara, F.; Kuroda, R.; Sugawa, S. A linear response single exposure CMOS image sensor with 0.5e- readout noise and 76ke- full well capacity. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 16–19 June 2015; pp. C88–C89. [Google Scholar] [CrossRef]

- Otani, A.; Ogawa, H.; Miyauchi, K.; Han, S.; Owada, H.; Takayanagi, I.; Okura, S. An Area-Efficient up/down Double-Sampling Circuit for a LOFIC CMOS Image Sensor. Sensors 2023, 23, 4478. [Google Scholar] [CrossRef] [PubMed]

- Otani, A.; Ogawa, H.; Miyauchi, K.; Morikawa, Y.; Owada, H.; Takayanagi, I.; Okura, S. An Area-Efficient Readout Circuit for a High-SNR Triple-Gain LOFIC CMOS Image Sensor. In Proceedings of the 2025 IEEE International Symposium on Circuits and Systems (ISCAS), London, UK, 25–28 May 2025; pp. 1–5. [Google Scholar] [CrossRef]

- Akahane, N.; Adachi, S.; Mizobuchi, K.; Sugawa, S. Optimum Design of Conversion Gain and Full Well Capacity in CMOS Image Sensor with Lateral Overflow Integration Capacitor. IEEE Trans. Electron Devices 2009, 56, 2429–2435. [Google Scholar] [CrossRef]

- Takayanagi, I. A Study on Intra-Scene Single-Exposure High-Dynamic Range CMOS Image Sensor Technologies. Ph.D Thesis, Tohoku University, Sendai, Japan, 2020. [Google Scholar] [CrossRef]

- Fujimoto, Y.; Akada, H.; Ogawa, H.; Iizuka, K.; Miyamoto, M. A switched-capacitor variable gain amplifier for CCD image sensor interface system. In Proceedings of the 28th European Solid-State Circuits Conference, Florence, Italy, 24–26 September 2002; pp. 363–366. [Google Scholar]

- Takahashi, H.; Noda, T.; Matsuda, T.; Watanabe, T.; Shinohara, M.; Endo, T.; Takimoto, S.; Mishima, R.; Nishimura, S.; Sakurai, K.; et al. A 1/2.7-in 2.96 MPixel CMOS Image Sensor with Double CDS Architecture for Full High-Definition Camcorders. IEEE J. Solid-State Circuits 2007, 42, 2960–2967. [Google Scholar] [CrossRef]

- Takayanagi, I.; Yoshimura, N.; Mori, K.; Matsuo, S.; Tanaka, S.; Abe, H.; Yasuda, N.; Ishikawa, K.; Okura, S.; Ohsawa, S.; et al. An Over 90 dB Intra-Scene Single-Exposure Dynamic Range CMOS Image Sensor Using a 3.0 μm Triple-Gain Pixel Fabricated in a Standard BSI Process. Sensors 2018, 18, 203. [Google Scholar] [CrossRef] [PubMed]

- Sakakibara, M.; Oike, Y.; Takatsuka, T.; Kato, A.; Honda, K.; Taura, T.; Machida, T.; Okuno, J.; Ando, A.; Fukuro, T.; et al. An 83dB-dynamic-range single-exposure global-shutter CMOS image sensor with in-pixel dual storage. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 380–382. [Google Scholar] [CrossRef]

| HCG | MCG | LCG | |

|---|---|---|---|

| Measured circuit gain [V/V] | |||

| Estimated total gain [] | 771 | 103 |

| HCG | MCG | LCG | |

|---|---|---|---|

| Measurement [] | |||

| Estimation [] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Otani, A.; Ogawa, H.; Miyauchi, K.; Morikawa, Y.; Owada, H.; Takayanagi, I.; Okura, S. An Area-Efficient Readout Circuit for a High-SNR Triple-Gain LOFIC CMOS Image Sensor. Sensors 2025, 25, 6093. https://doi.org/10.3390/s25196093

Otani A, Ogawa H, Miyauchi K, Morikawa Y, Owada H, Takayanagi I, Okura S. An Area-Efficient Readout Circuit for a High-SNR Triple-Gain LOFIC CMOS Image Sensor. Sensors. 2025; 25(19):6093. https://doi.org/10.3390/s25196093

Chicago/Turabian StyleOtani, Ai, Hiroaki Ogawa, Ken Miyauchi, Yuki Morikawa, Hideki Owada, Isao Takayanagi, and Shunsuke Okura. 2025. "An Area-Efficient Readout Circuit for a High-SNR Triple-Gain LOFIC CMOS Image Sensor" Sensors 25, no. 19: 6093. https://doi.org/10.3390/s25196093

APA StyleOtani, A., Ogawa, H., Miyauchi, K., Morikawa, Y., Owada, H., Takayanagi, I., & Okura, S. (2025). An Area-Efficient Readout Circuit for a High-SNR Triple-Gain LOFIC CMOS Image Sensor. Sensors, 25(19), 6093. https://doi.org/10.3390/s25196093