A Phase-Adjustable Noise-Shaping SAR ADC for Mitigating Parasitic Capacitance Effects from PIP Capacitors

Abstract

1. Introduction

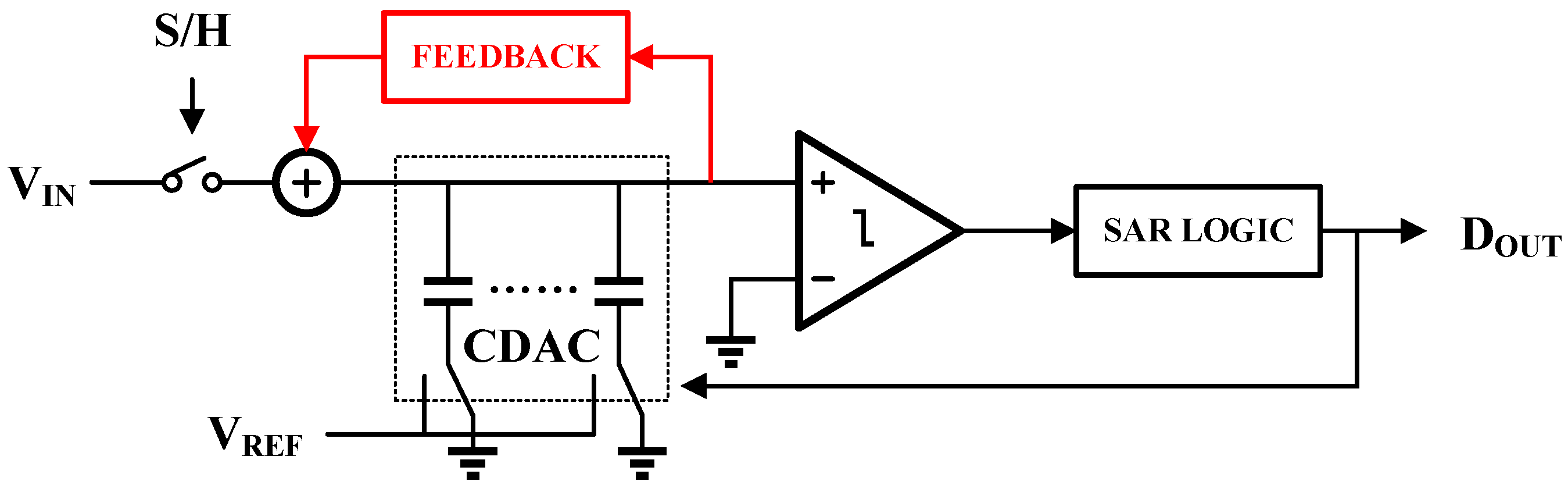

2. Analysis of Parasitic Effects

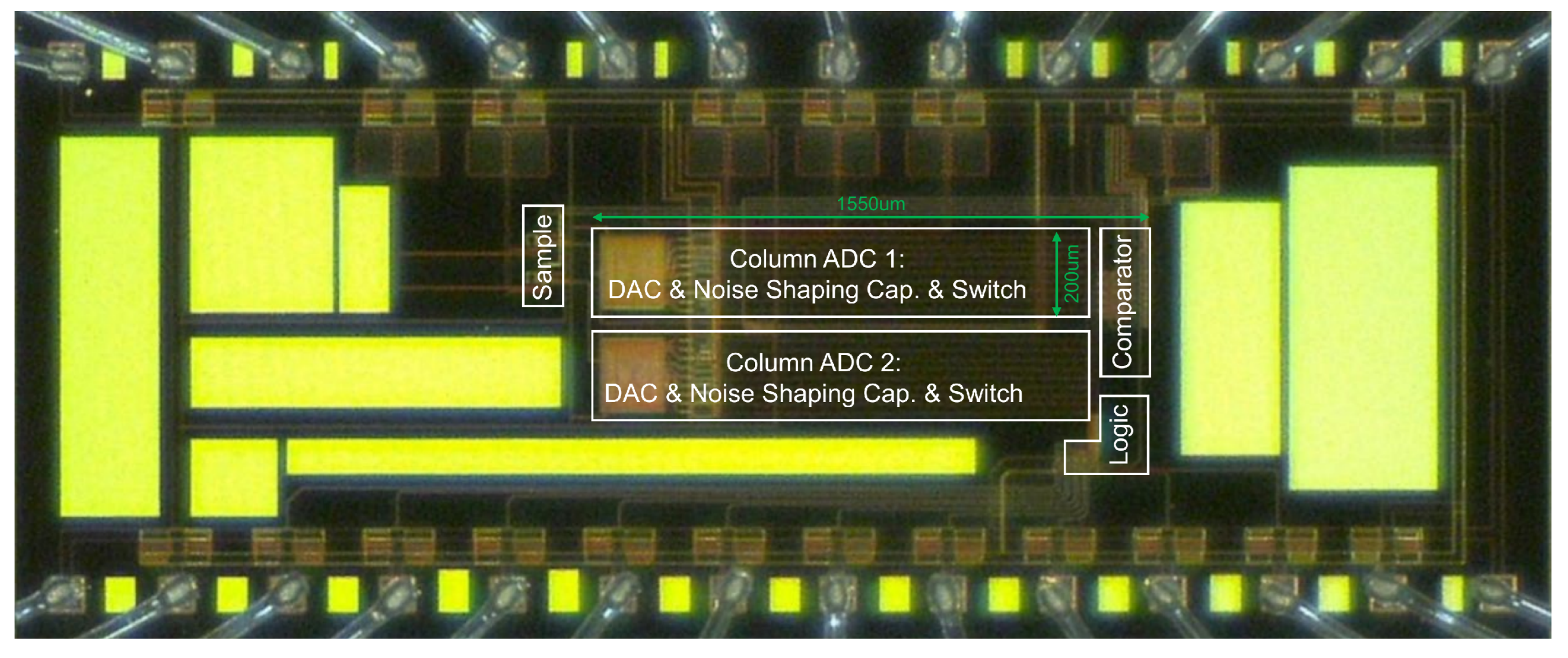

3. Design of a Column ADC Prototype

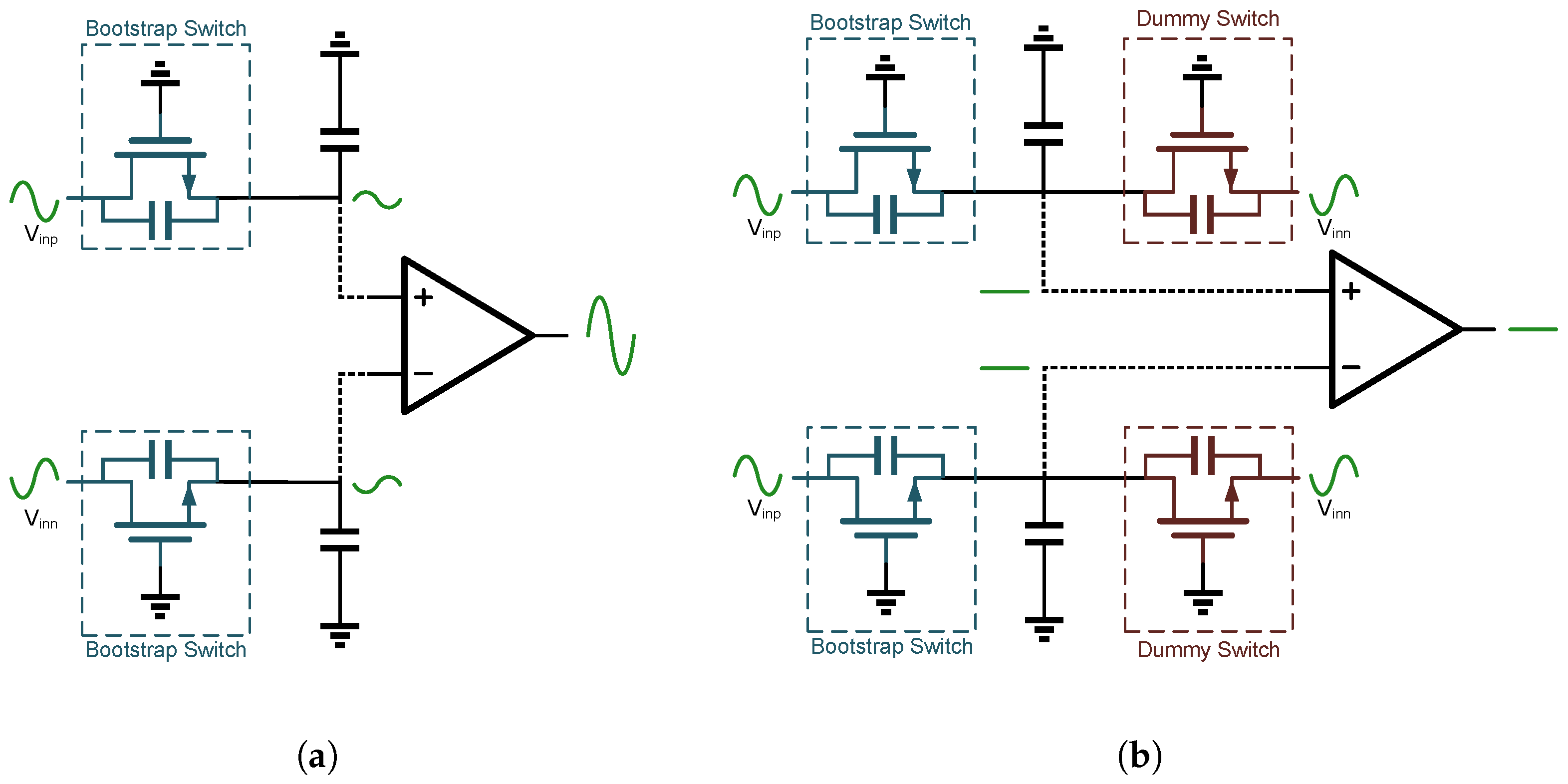

3.1. Bootstrapped Sample Switch

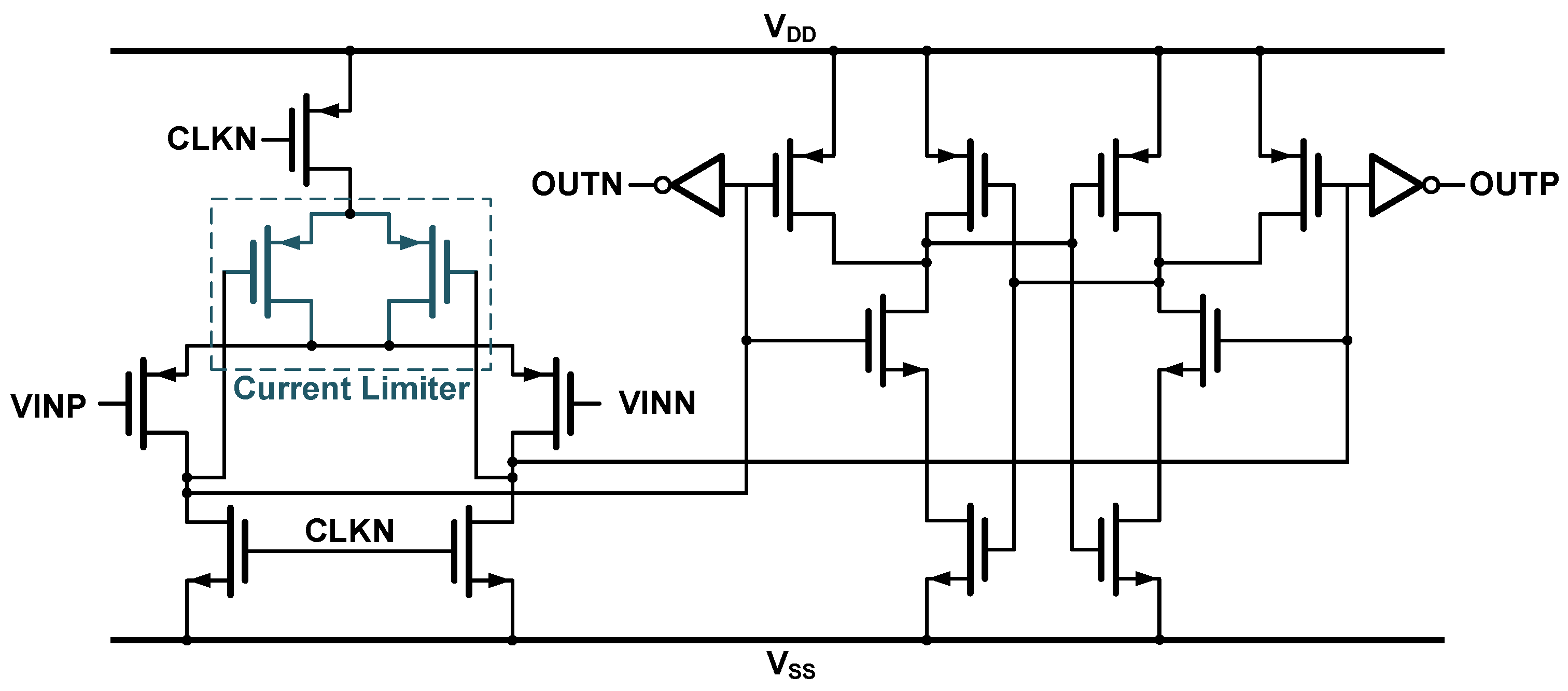

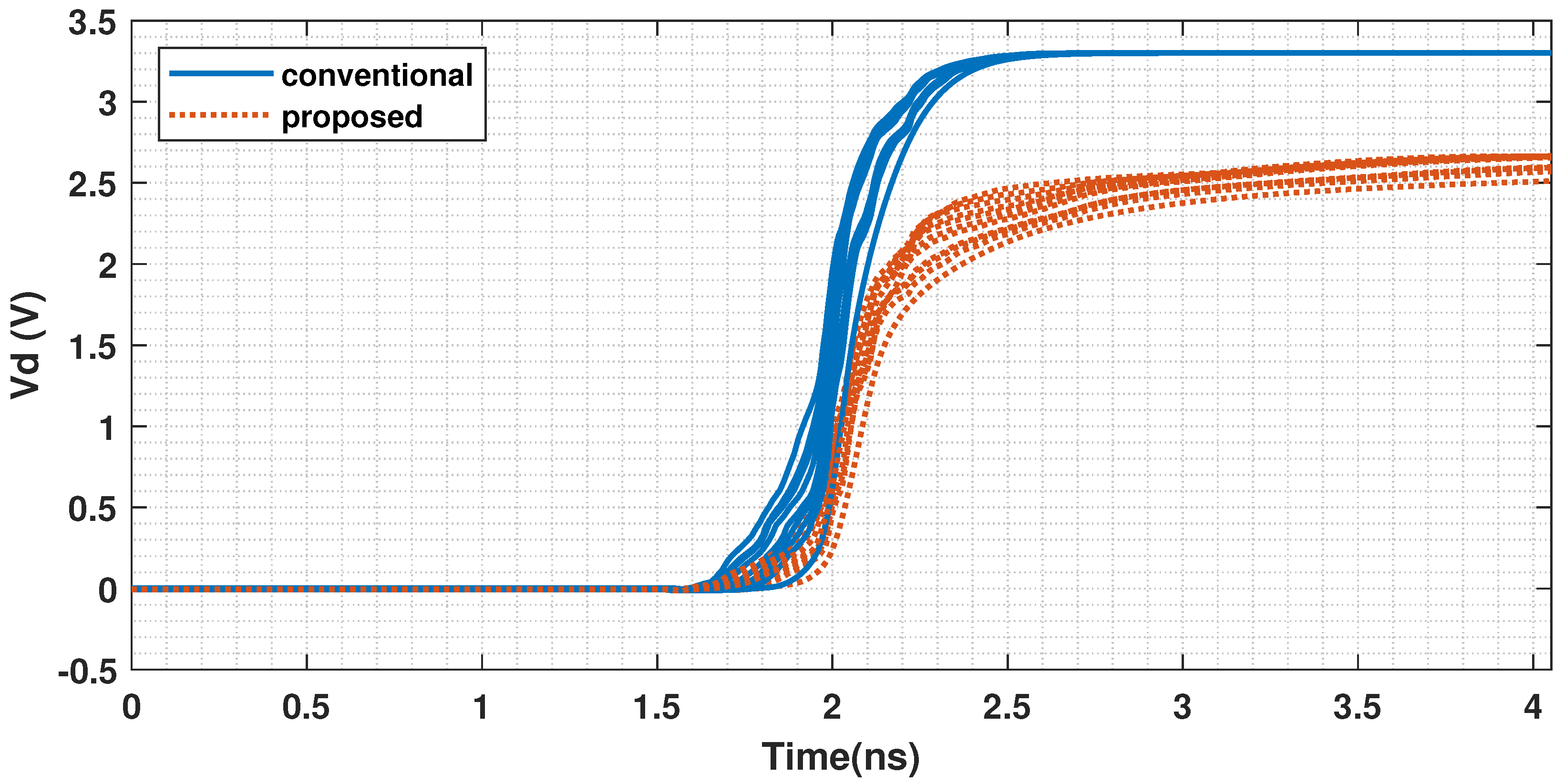

3.2. Comparator

3.3. DAC Architecture

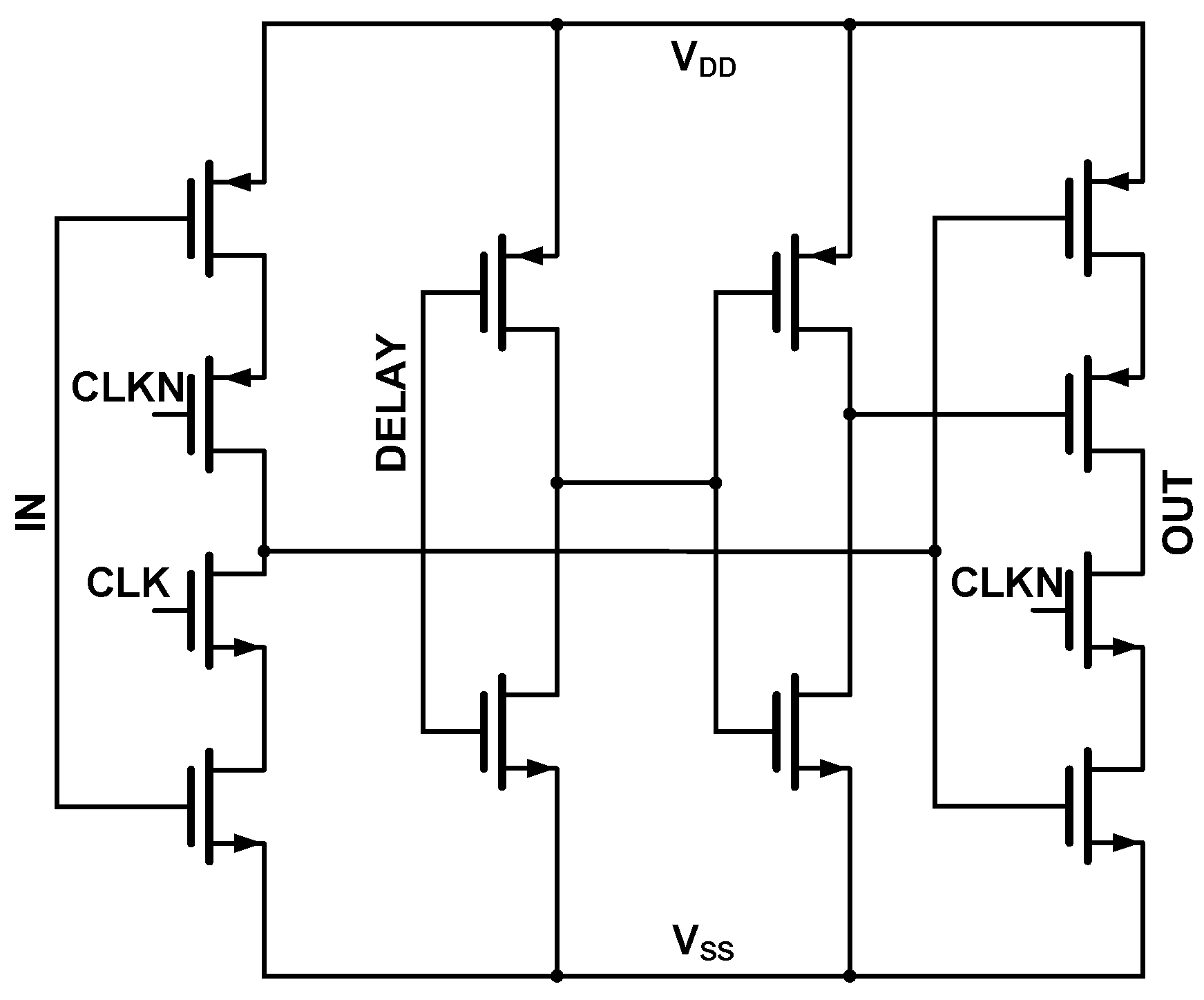

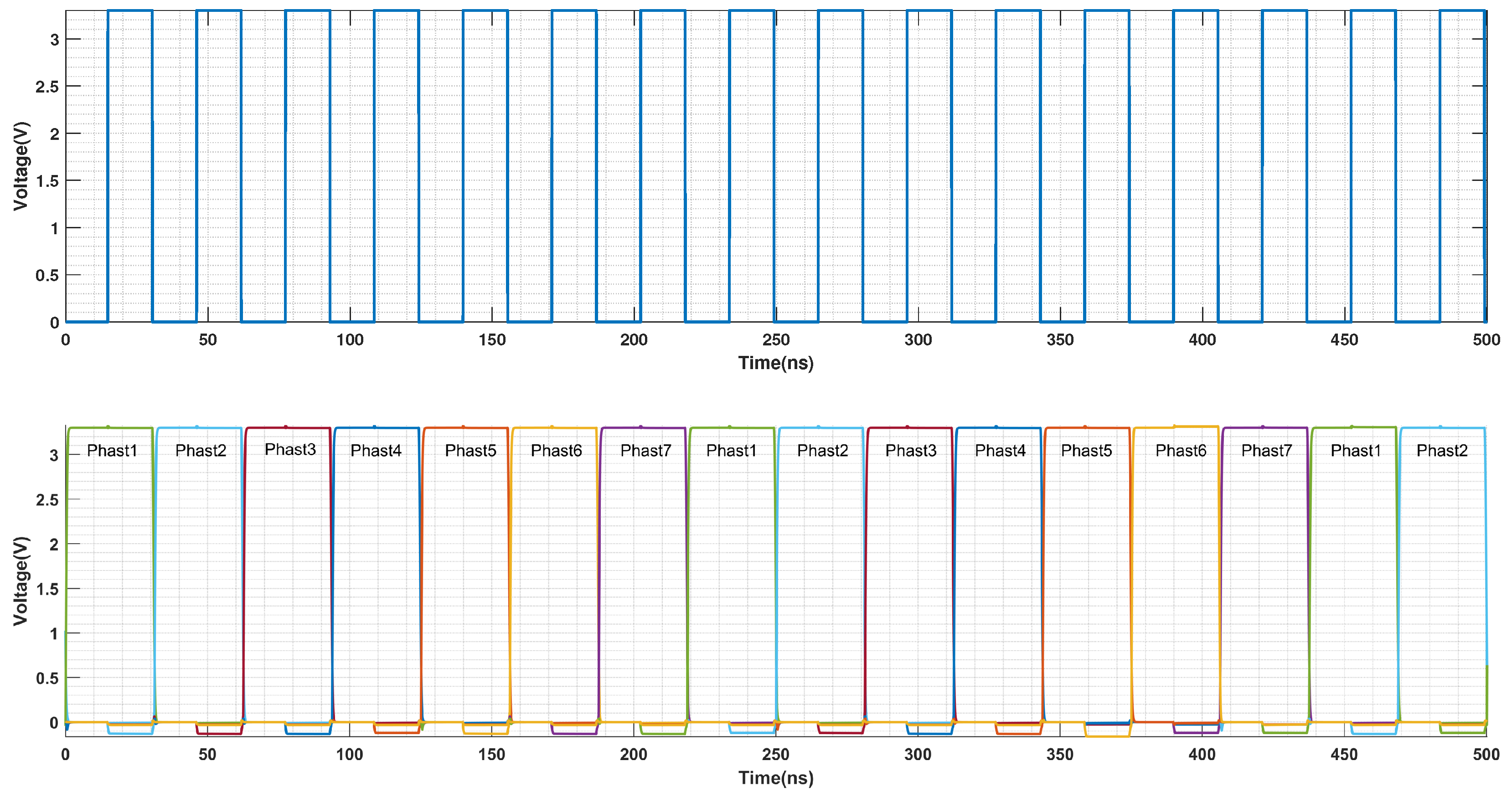

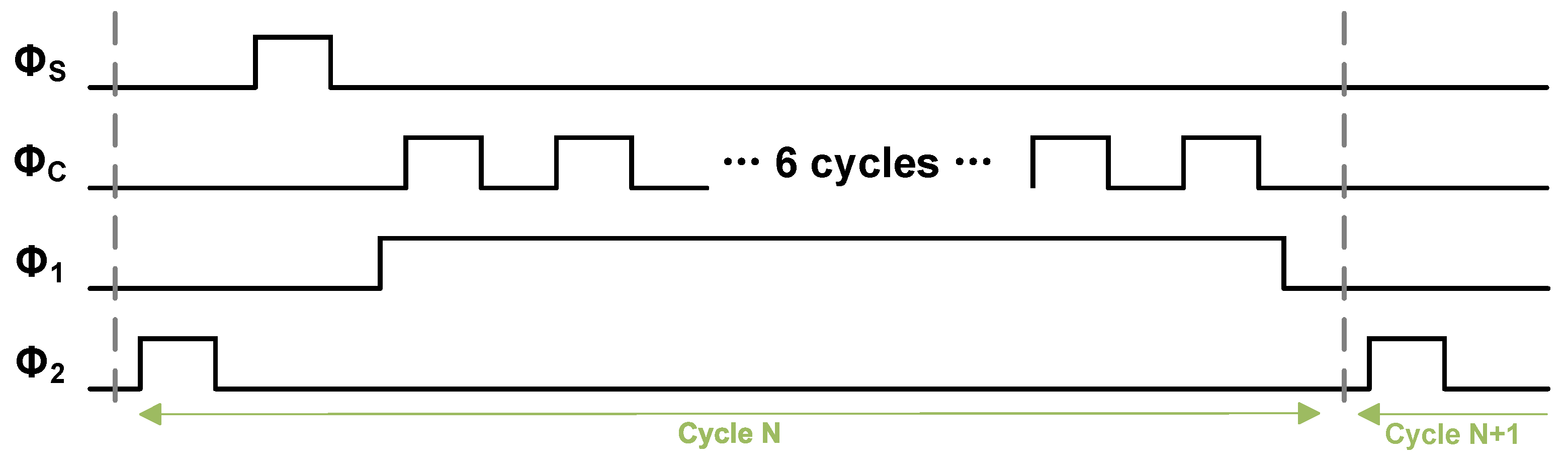

3.4. Phase-Adjustable SAR Logic

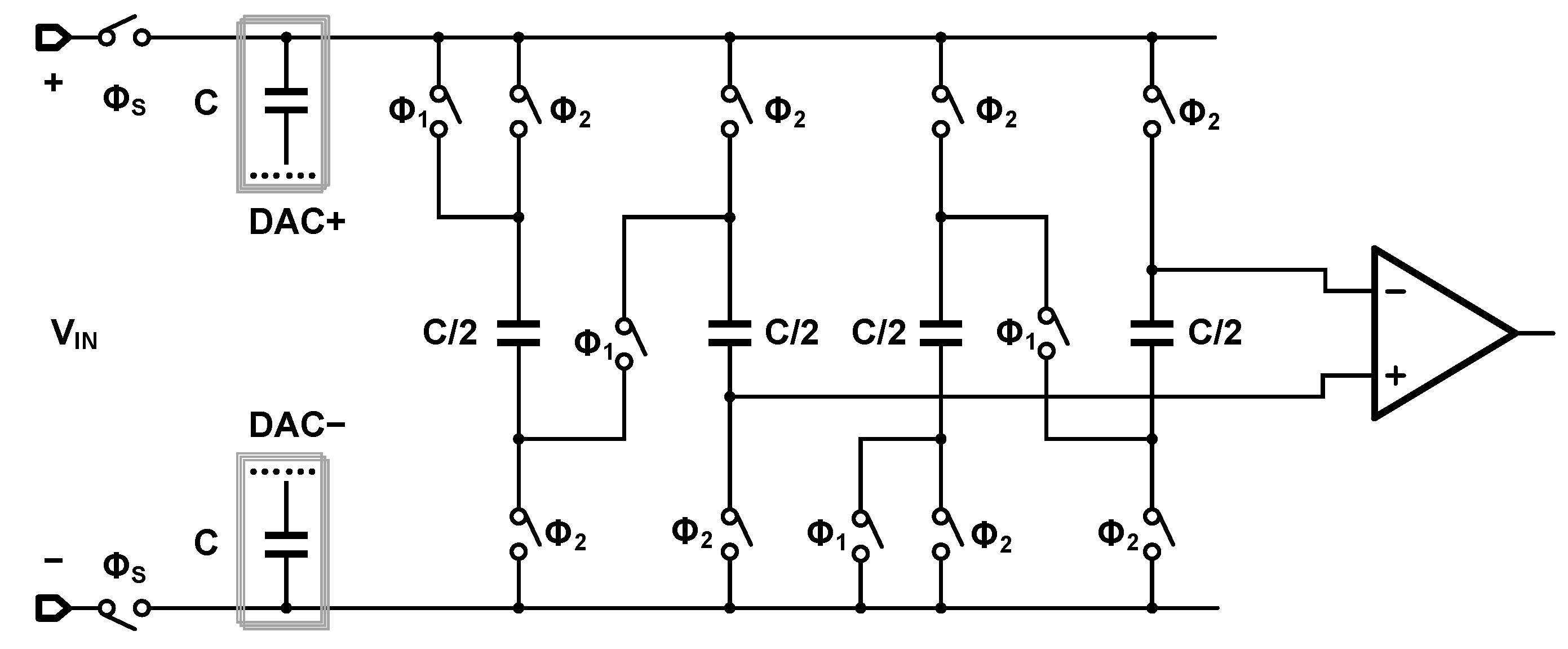

3.5. Noise Shaping Architecture

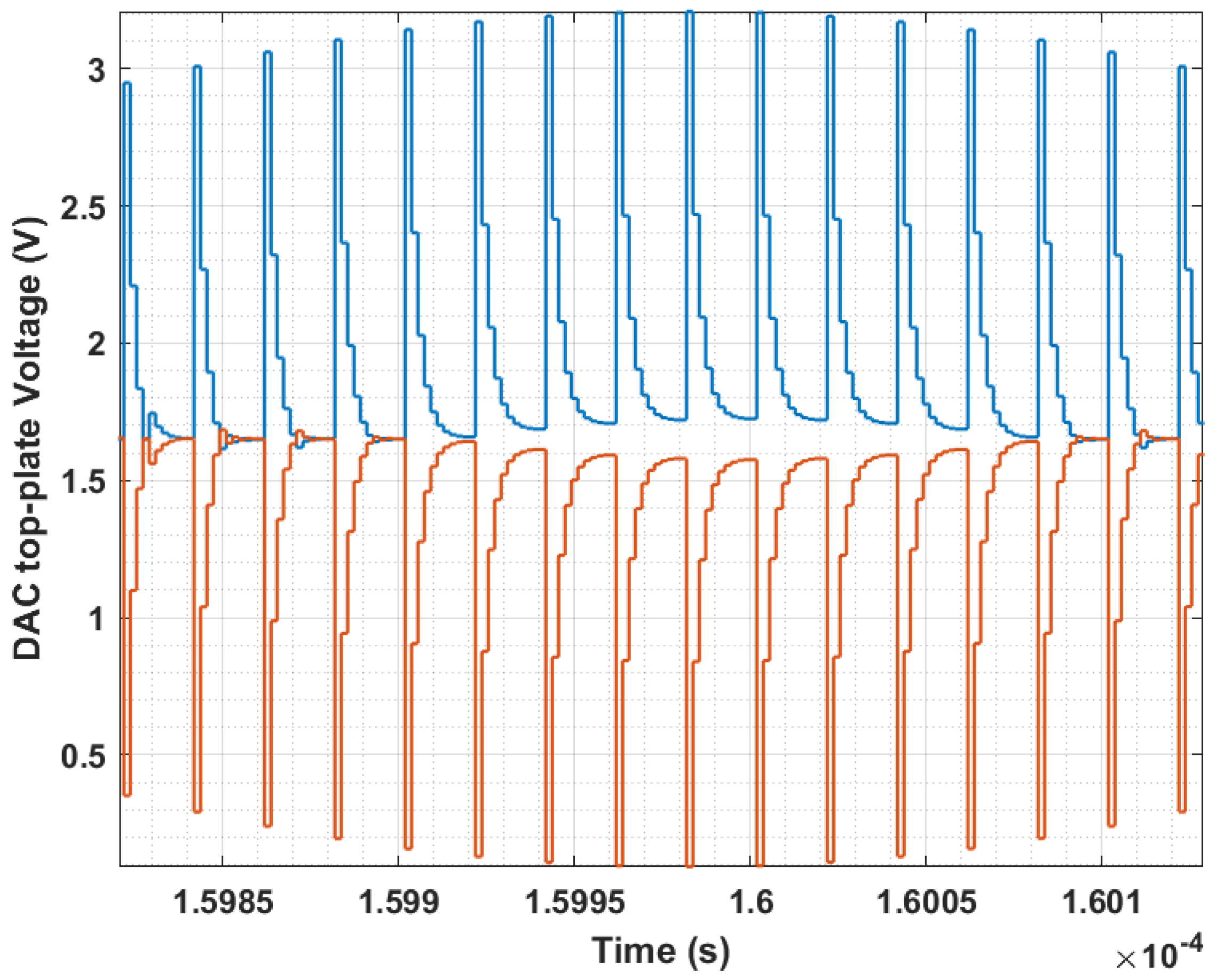

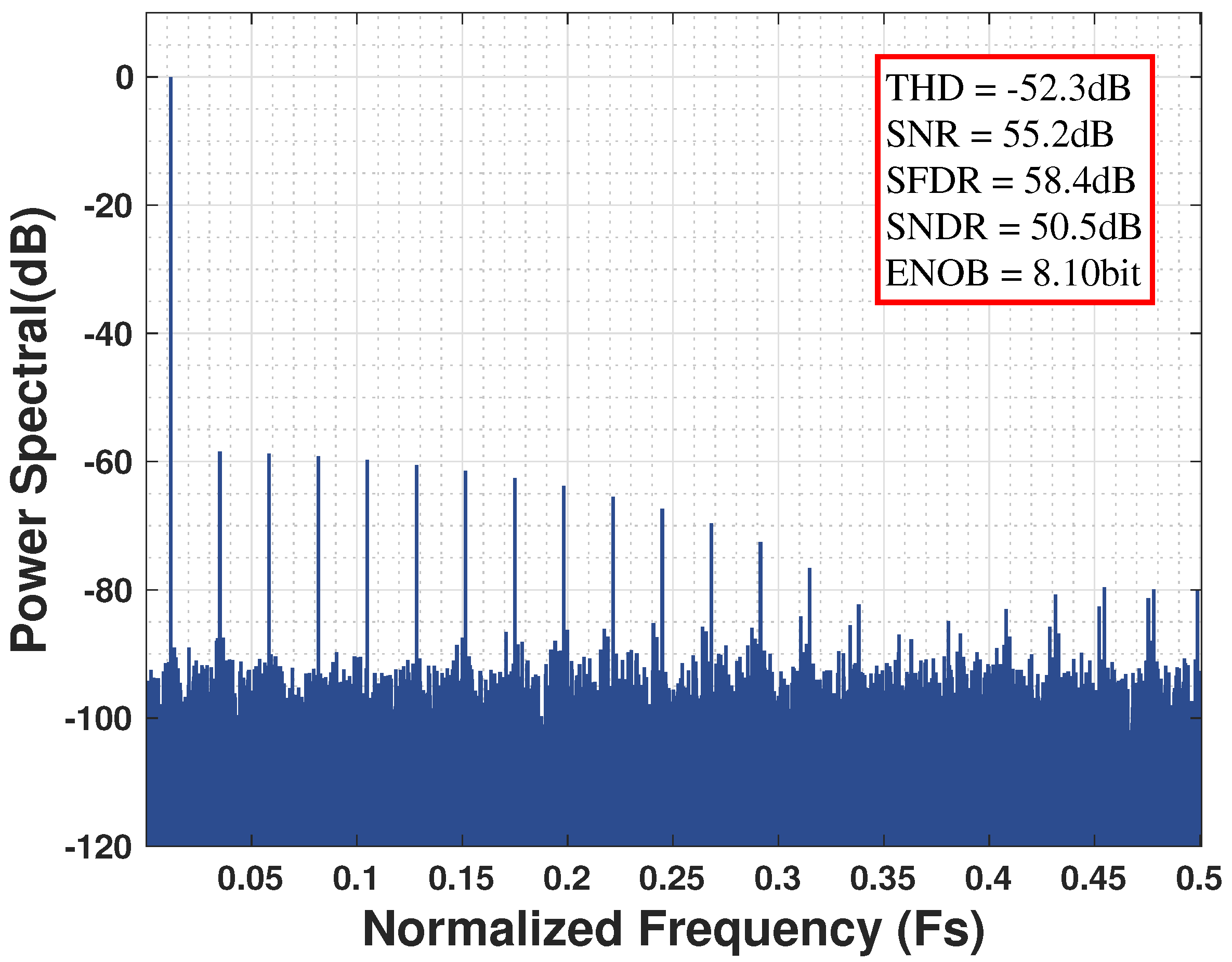

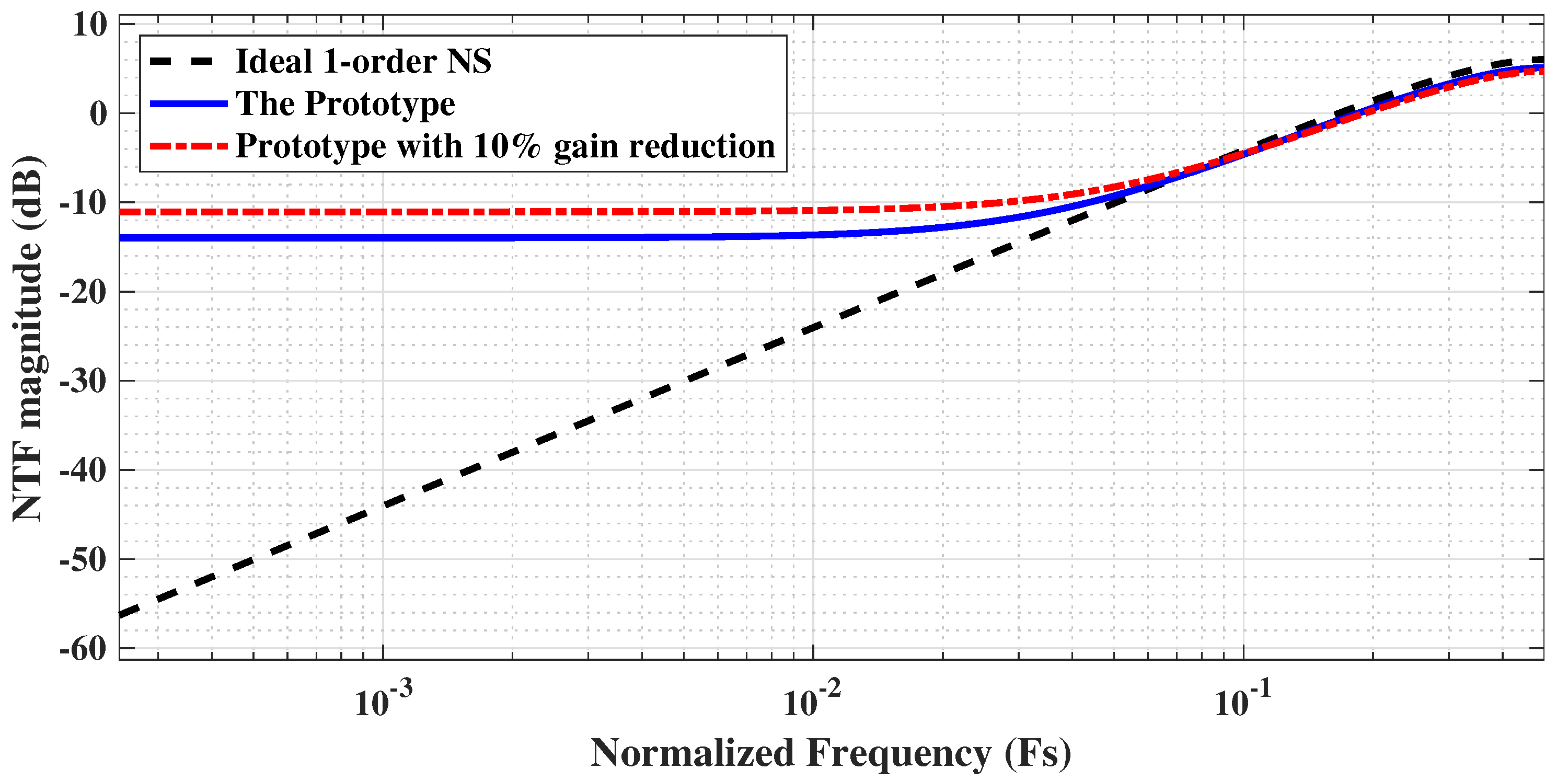

3.6. Prototype Simulation

4. Results and Discussion

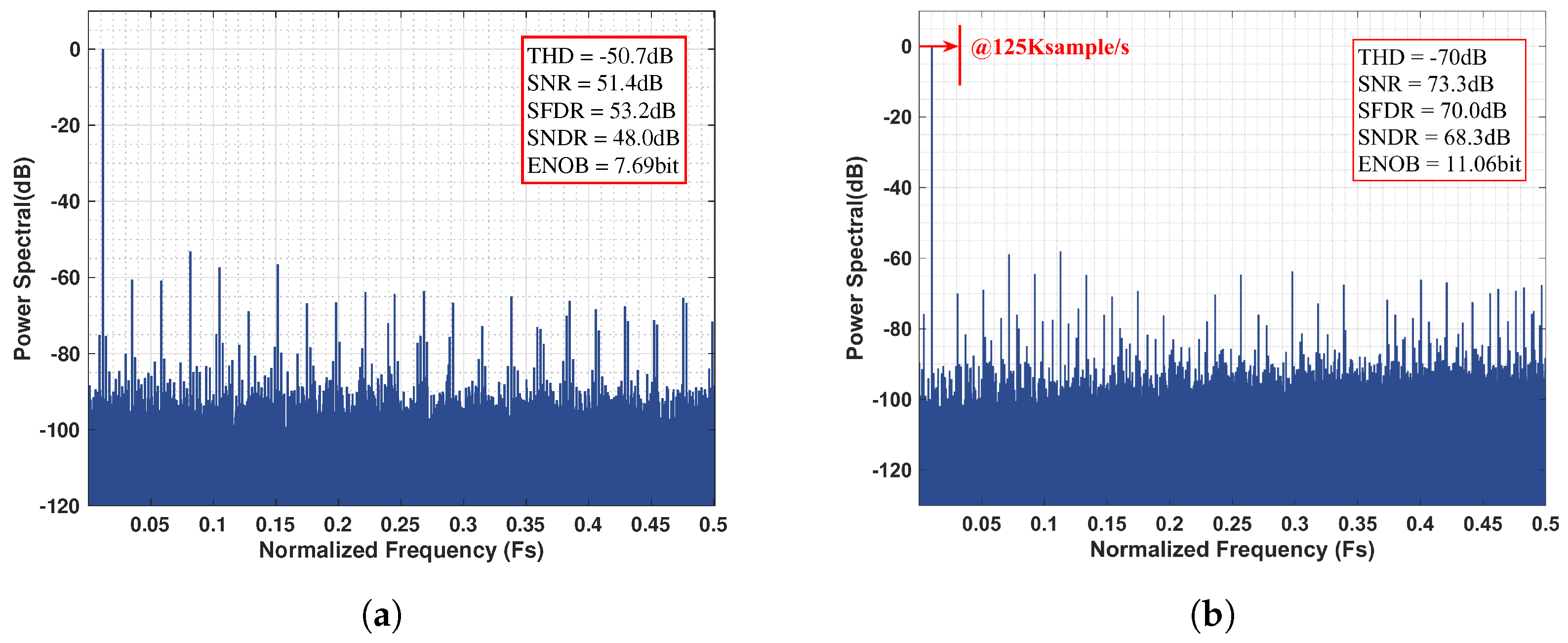

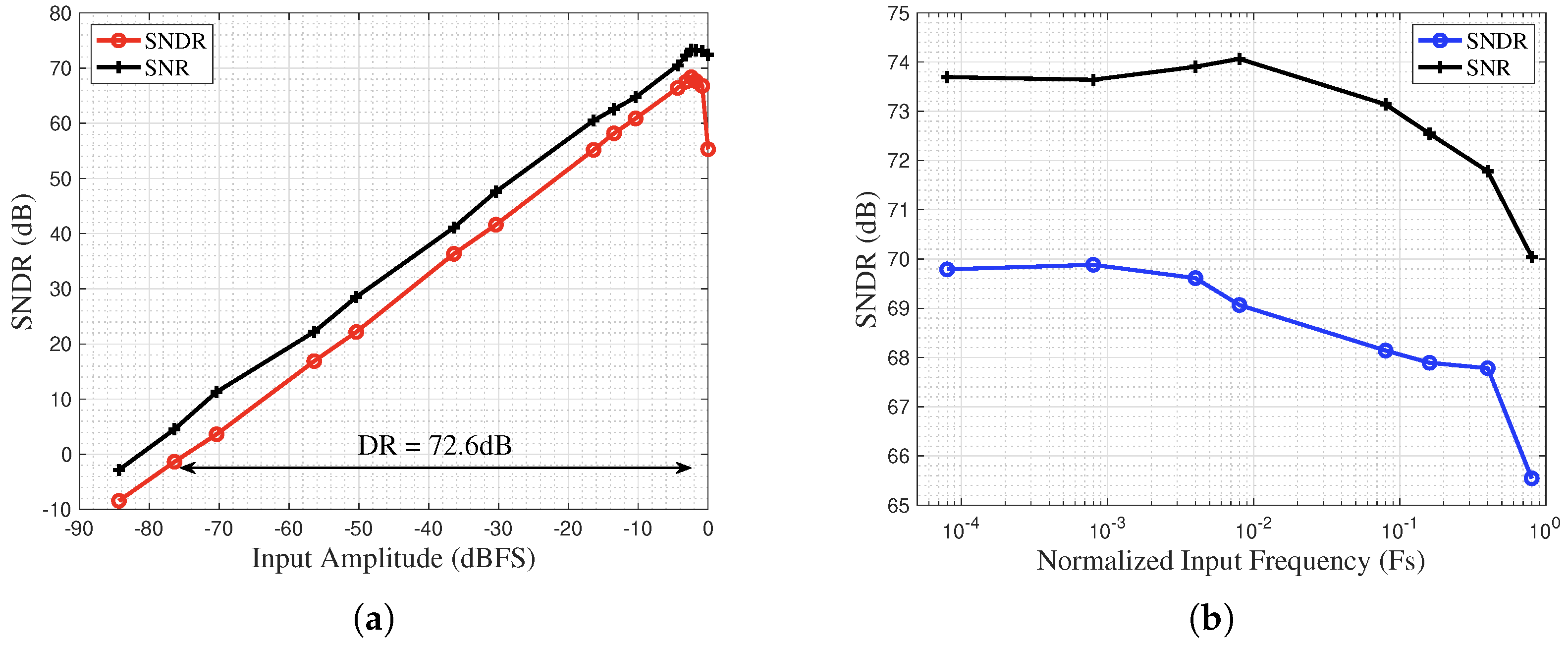

Measurements

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Udoy, M.R.I.; Alam, S.; Islam, M.M.; Jaiswal, A.; Aziz, A. A review of digital pixel sensors. IEEE Access 2025, 13, 8533–8551. [Google Scholar] [CrossRef]

- Lozada, K.E.; Chang, D.J.; Oh, D.R.; Seo, M.J.; Ryu, S.T. SAR-Assisted Energy-Efficient Hybrid ADCs. IEEE Open J. Solid-State Circuits Soc. 2024, 4, 163–175. [Google Scholar] [CrossRef]

- Harpe, P. Low-power SAR ADCs: Basic techniques and trends. IEEE Open J. Solid-State Circuits Soc. 2022, 2, 73–81. [Google Scholar] [CrossRef]

- Tang, X.; Liu, J.; Shen, Y.; Li, S.; Shen, L.; Sanyal, A.; Ragab, K.; Sun, N. Low-power SAR ADC design: Overview and survey of state-of-the-art techniques. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 2249–2262. [Google Scholar] [CrossRef]

- Zhang, Y.; Bonizzoni, E.; Maloberti, F. Mismatch and parasitics limits in capacitors-based SAR ADCs. In Proceedings of the 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, Monaco, 11–14 December 2016; pp. 33–36. [Google Scholar] [CrossRef]

- Ding, Y.X.; Burcea, F.; Habal, H.; Graeb, H.E. PASTEL: Parasitic matching-driven placement and routing of capacitor arrays with generalized ratios in charge-redistribution SAR-ADCs. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2019, 39, 1372–1385. [Google Scholar] [CrossRef]

- Aoki, R.; Wei, J.; Zhao, Y.; Kuwana, A.; Kobayashi, H.; Nakatani, T.; Hatayama, K.; Sato, K.; Ishida, T.; Okamoto, T.; et al. Analysis, Testing and Calibration of Charge Distribution SAR ADC Architecture with Split Capacitor. In Proceedings of the 4th International Conference on Technology and Social Science (ICTSS 2020), Kiryu, Japan, 2–4 December 2020; Kiryu City Performing Art Center: Kiryu, Japan, 2020. [Google Scholar]

- Jie, L.; Tang, X.; Liu, J.; Shen, L.; Li, S.; Sun, N.; Flynn, M.P. An Overview of Noise-Shaping SAR ADC: From Fundamentals to the Frontier. IEEE Open J. Solid-State Circuits Soc. 2021, 1, 149–161. [Google Scholar] [CrossRef]

- Liu, J.; Wang, X.; Gao, Z.; Zhan, M.; Tang, X.; Sun, N. 9.3 A 40kHz-BW 90dB-SNDR Noise-Shaping SAR with 4× Passive Gain and 2nd-Order Mismatch Error Shaping. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 158–160. [Google Scholar] [CrossRef]

- Zou, X.; Liu, J.; Li, Q. Fully passive noise-shaping successive approximation register analog-to-digital converter realizing 2 × gain without capacitor stacking. Electron. Lett. 2023, 59, e12757. [Google Scholar] [CrossRef]

- Fredenburg, J.A.; Flynn, M.P. A 90-ms/s 11-mhz-bandwidth 62-db sndr noise-shaping sar adc. IEEE J. Solid-State Circuits 2012, 47, 2898–2904. [Google Scholar] [CrossRef]

- Boughedda, A.; Pancheri, L.; Parmesan, L.; Gasparini, L.; Quarta, G.; Perenzoni, D.; Perenzoni, M. The Modeling of a Single-Electron Bipolar Avalanche Transistor in 150 nm CMOS. Sensors 2025, 25, 3354. [Google Scholar] [CrossRef]

- Zhang, W.; Xu, X.; Cheng, Z. The Effect of Pixel Design and Operation Conditions on Linear Output Range of 4T CMOS Image Sensors. Sensors 2024, 24, 1841. [Google Scholar] [CrossRef]

- Razavi, B. The Bootstrapped Switch [A Circuit for All Seasons]. IEEE Solid-State Circuits Mag. 2015, 7, 12–15. [Google Scholar] [CrossRef]

- Razavi, B. The StrongARM Latch [A Circuit for All Seasons]. IEEE Solid-State Circuits Mag. 2015, 7, 12–17. [Google Scholar] [CrossRef]

- Liu, Y. The progress of the double-tail dynamic comparators and an improvement design. In Proceedings of the 2021 International Conference on Wireless Communications and Smart Grid (ICWCSG), Hangzhou, China, 13–15 August 2021; pp. 427–434. [Google Scholar] [CrossRef]

- Yang, S.; Li, X.; Tang, M.; Wang, M.; Zhuang, Z. A hybrid switching logic control circuit for SAR ADC. In Proceedings of the International Conference on Electronic Information Technology (EIT 2022), Chengdu, China, 18–20 March 2022; SPIE: Bellingham, WA, USA, 2022; Volume 12254, pp. 37–41. [Google Scholar] [CrossRef]

- Deng, X.; Ma, T.; Luo, P.; Liu, M.; Dong, J. A 10-bit 100-MS/s 1.2-mW Asynchronous SAR ADC with Low-power Dynamic Logic Units in 65nm CMOS. In Proceedings of the 2023 8th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 20–23 October 2023; pp. 463–467. [Google Scholar] [CrossRef]

- Shu, Y.S.; Kuo, L.T.; Lo, T.Y. An oversampling SAR ADC with DAC mismatch error shaping achieving 105 dB SFDR and 101 dB SNDR over 1 kHz BW in 55 nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 2928–2940. [Google Scholar] [CrossRef]

- Chen, Z.; Miyahara, M.; Matsuzawa, A. A 9.35-ENOB, 14.8 fJ/conv.-step fully-passive noise-shaping SAR ADC. IEICE Trans. Electron. 2015, 99, 963–973. [Google Scholar]

- Guo, W.; Sun, N. A 12b-ENOB 61 µW noise-shaping SAR ADC with a passive integrator. In Proceedings of the 42nd European Solid-State Circuits Conference, ESSCIRC 2016, Lausanne, Switzerland, 12–15 September 2016; Volume 2016, pp. 405–408. [Google Scholar] [CrossRef]

- Guo, W.; Zhuang, H.; Sun, N. A 13b-ENOB 173dB-FoM 2nd-order NS SAR ADC with passive integrators. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. C236–C237. [Google Scholar] [CrossRef]

- Lin, M.P.H.; He, Y.-T.; Hsiao, V.W.H.; Chang, R.-G.; Lee, S.-Y. Common-Centroid Capacitor Layout Generation Considering Device Matching and Parasitic Minimization. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2013, 32, 991–1002. [Google Scholar] [CrossRef]

- Zhang, C.; Wang, H. Reduction of Parasitic Capacitance Impact in Low-Power SAR ADC. IEEE Trans. Instrum. Meas. 2012, 61, 587–594. [Google Scholar] [CrossRef]

- Fredenburg, J.; Flynn, M.P. ADC trends and impact on SAR ADC architecture and analysis. In Proceedings of the 2015 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 28–30 September 2015; pp. 1–8. [Google Scholar] [CrossRef]

- Xu, L.; Chen, D. A low cost jitter estimation and ADC spectral testing method. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 2277–2280. [Google Scholar] [CrossRef]

- Zhang, S.; Sun, Q.; Chen, X.; Wang, B.; Li, Y. ADC Clock Jitter Measurement Based on Simple Coherent Sampling Algorithm. J. Physics Conf. Ser. 2022, 2366, 012045. [Google Scholar] [CrossRef]

- Spivak, A.; Belenky, A.; Yadid-Pecht, O. Very Sensitive Low-Noise Active-Reset CMOS Image Sensor with In-Pixel ADC. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 939–943. [Google Scholar] [CrossRef]

- Chen, N.; Zhong, S.; Zou, M.; Zhang, J.; Ji, Z.; Yao, L. A Low-Noise CMOS Image Sensor With Digital Correlated Multiple Sampling. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 84–94. [Google Scholar] [CrossRef]

- Lee, J.; Park, H.; Song, B.; Kim, K.; Eom, J.; Kim, K.; Burm, J. High Frame-Rate VGA CMOS Image Sensor Using Non-Memory Capacitor Two-Step Single-Slope ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2147–2155. [Google Scholar] [CrossRef]

- Liu, M.; Zhu, S.; Xu, Y. A 9-bit 8.3 MS/s column SAR ADC with hybrid RC DAC for CMOS image sensors. Microelectron. J. 2023, 131, 105630. [Google Scholar] [CrossRef]

- Brenna, S.; Bonfanti, A.; Lacaita, A.L. A 70.7-dB SNDR 100-kS/s 14-b SAR ADC with attenuation capacitance calibration in 0.35-µm CMOS. Analog. Integr. Circuits Signal Process. 2016, 89, 357–371. [Google Scholar] [CrossRef]

| (V) | Conv. (µA) | Prop. (µA) | Conv. (ns) | Prop. (ns) |

|---|---|---|---|---|

| 1.0 | 52.84 | 37.80 | 1.023 | 1.170 |

| 1.2 | 49.57 | 34.61 | 1.024 | 1.165 |

| 1.4 | 45.96 | 31.53 | 1.033 | 1.180 |

| 1.6 | 42.06 | 28.68 | 1.052 | 1.213 |

| 1.8 | 37.94 | 26.25 | 1.087 | 1.267 |

| 2.0 | 33.77 | 24.57 | 1.147 | 1.350 |

| Spivak [28] | Chen [29] | Lee [30] | Liu [31] | Brenna [32] | This Work | |

|---|---|---|---|---|---|---|

| Process | 350 nm | 350 nm | 130 nm | 180 nm | 350 nm | 350 nm |

| Supply (V) | 3.3 | \ | 2.8/1.5 | 1.8 | 1.8 | 3.3 |

| Pixel Array | 32 × 32 | 800 × 600 | 640 × 480 | \ | \ | 1024 × 1024 |

| ADC Type | Pixel | TSSS | SAR | SAR | NS SAR | |

| Frame Rate (fps) | \ | 50 | 320 | \ | \ | 60 |

| Sampling Rate (MHz) | \ | \ | \ | 8.3 | 0.1 | 0.125 |

| DR (dB) | 58 | 84 | 75 | \ | \ | 72.6 |

| NS Mode | No | Yes | No | No | No | Yes |

| ENOB (bit) | 6.85 | \ | \ | 8.35 | 11.45 | 11.06 |

| DNL (LSB) | \ | −0.4/+0.8 | −0.49/+1.34 | −0.89/+0.98 | −1/+1 | −0.59/0.89 |

| INL (LSB) | \ | −3/+0.5 | −2.47/+2.44 | −1.8/+1.9 | −2.6/+2.1 | −1.58/1.36 |

| Area (mm2) | \ | 0.024 | 0.0066 | 0.05 | 1.35 | 0.073 |

| Power * (μW) | 192.0 | 241.2 | \ | 500 | 43.4 | 125.7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ouyang, X.; Kuang, H.; Kong, D.; Cheng, Z.; Yuan, H. A Phase-Adjustable Noise-Shaping SAR ADC for Mitigating Parasitic Capacitance Effects from PIP Capacitors. Sensors 2025, 25, 6029. https://doi.org/10.3390/s25196029

Ouyang X, Kuang H, Kong D, Cheng Z, Yuan H. A Phase-Adjustable Noise-Shaping SAR ADC for Mitigating Parasitic Capacitance Effects from PIP Capacitors. Sensors. 2025; 25(19):6029. https://doi.org/10.3390/s25196029

Chicago/Turabian StyleOuyang, Xuelong, Hua Kuang, Dalin Kong, Zhengxi Cheng, and Honghui Yuan. 2025. "A Phase-Adjustable Noise-Shaping SAR ADC for Mitigating Parasitic Capacitance Effects from PIP Capacitors" Sensors 25, no. 19: 6029. https://doi.org/10.3390/s25196029

APA StyleOuyang, X., Kuang, H., Kong, D., Cheng, Z., & Yuan, H. (2025). A Phase-Adjustable Noise-Shaping SAR ADC for Mitigating Parasitic Capacitance Effects from PIP Capacitors. Sensors, 25(19), 6029. https://doi.org/10.3390/s25196029