A PFM-Based Calibration Method for Low-Power High-Linearity Digital Pixel

Abstract

1. Introduction

2. PFM-Based Digital Pixel and Nonlinearity

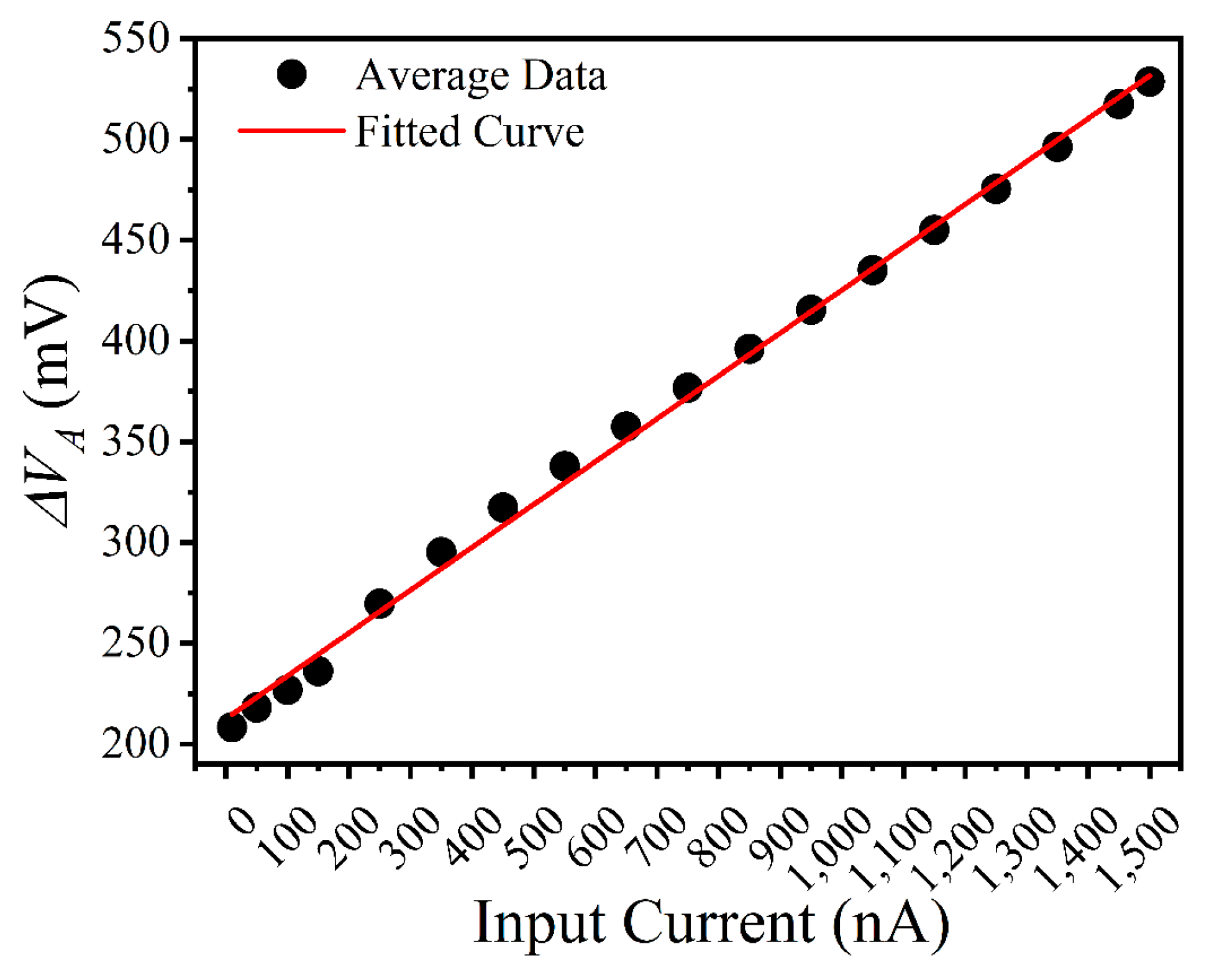

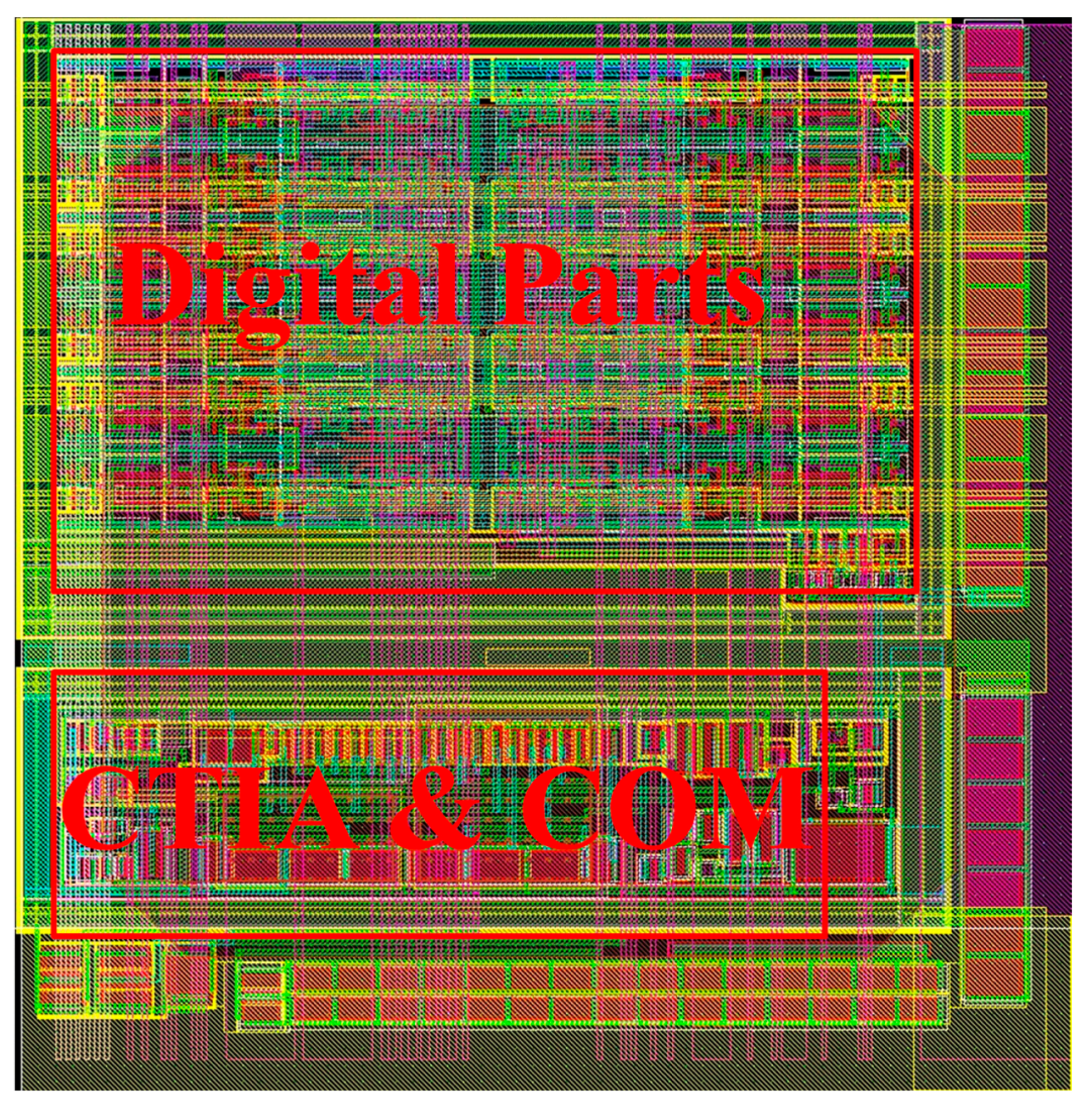

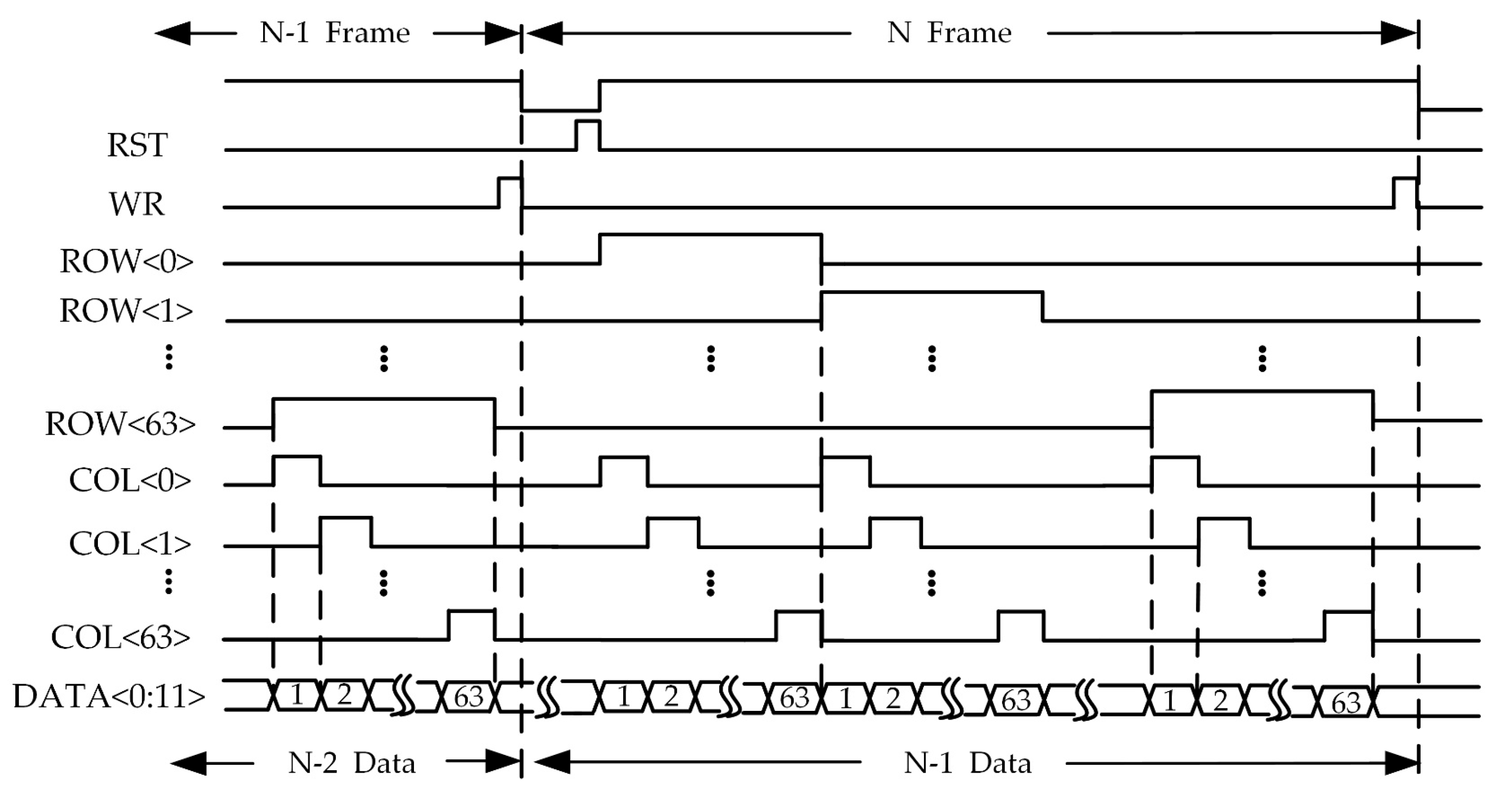

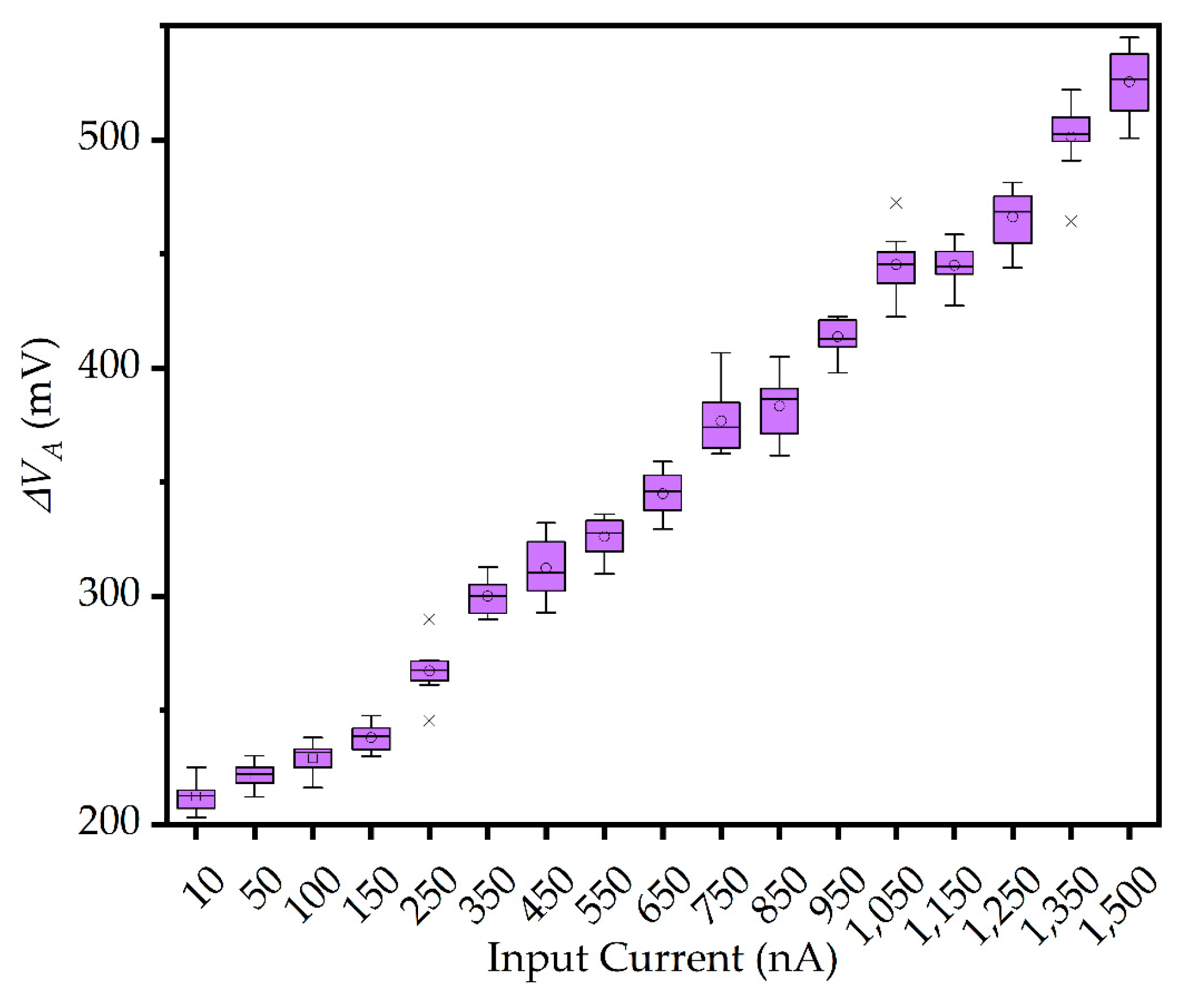

3. DROIC Design

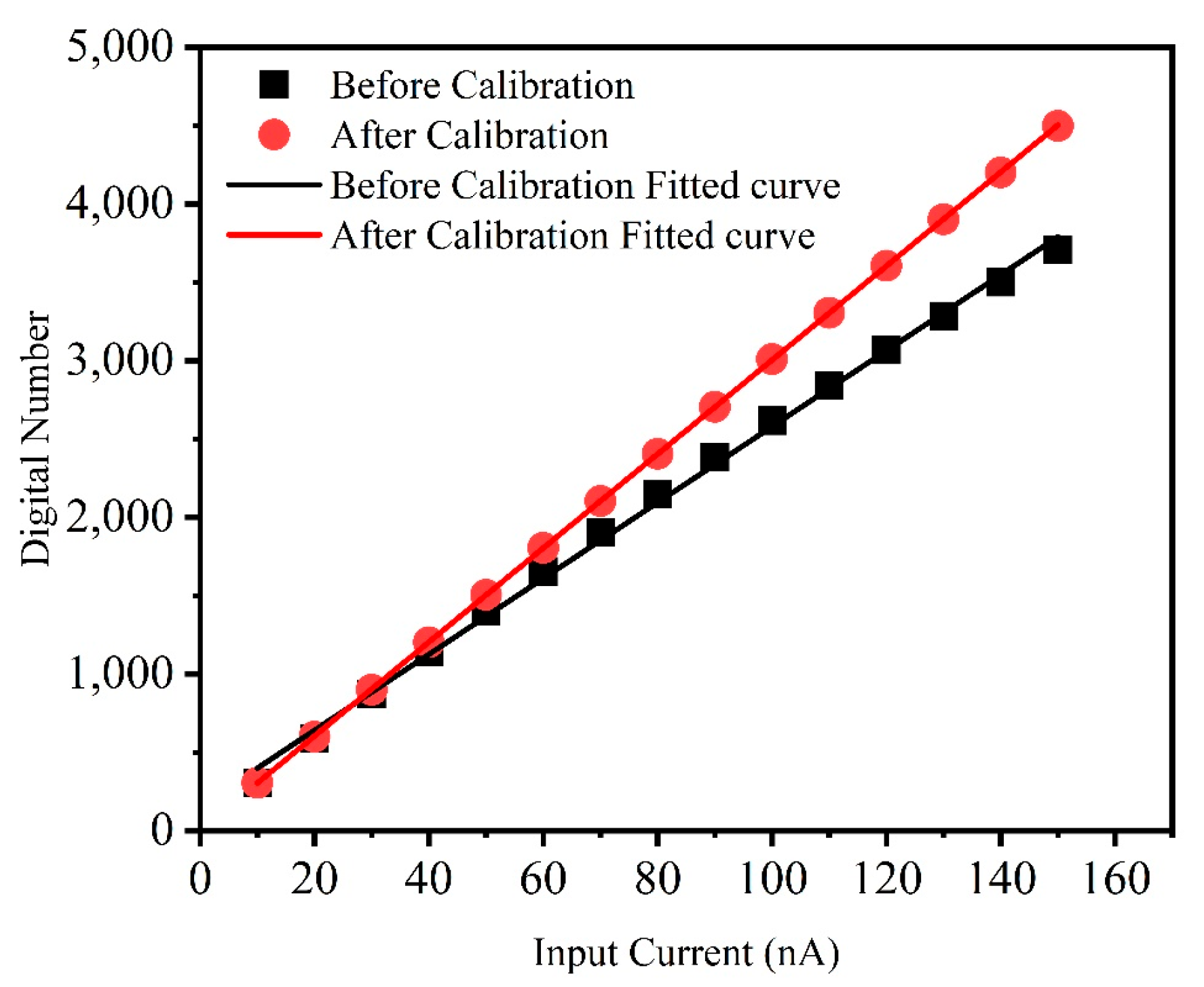

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Lee, H.-J.; Eom, J.H.; Kang, K.-K.; Ryu, S.-M.; Jang, A.; Kim, J.G.; Jang, H.; Kim, J.; Choi, H.; Jung, H.; et al. 640 × 512 dual-band midwave and longwave infrared focal plane array at i3system. In Infrared Technology and Applications XLIX; Ting, D.Z., Fulop, G.F., Zheng, L.L., Eds.; SPIE: Bellingham, WA, USA, 2023; p. 20. [Google Scholar] [CrossRef]

- Kelleci, B.; Kisa, M.E.; Ergen, E.; Oktay, Z.N.; Akbulut, M.; Nuzumlali, Ö.L. Development of 1280 × 1024 15μm pixel pitch ROIC for MWIR and LWIR IIR detectors. In Infrared Technology and Applications XLIX; Ting, D.Z., Fulop, G.F., Zheng, L.L., Eds.; SPIE: Bellingham, WA, USA, 2023; p. 48. [Google Scholar] [CrossRef]

- Zeng, Y.; Yang, S.; Liu, Y.; Bao, R.; Zhu, Z.; Lin, J.; Zhou, X.; Chen, Y.; Yin, J.; Mak, P.-I.; et al. A Digital Readout Integrated Circuit Based on Pixel-Level ADC Incorporating On-Chip Image Algorithm Calibration for IRFPA. IEEE Sens. J. 2023, 23, 21747–21756. [Google Scholar] [CrossRef]

- Kim, H.-J. Design of A prototype 128 × 128 ROIC array for 2.6 μm-wavelength SWIR image sensor applications. Integration 2024, 98, 102232. [Google Scholar] [CrossRef]

- Qiu, J.; Liu, Y.; Zhang, G.; Shi, K.; Li, Y.; Luo, Y. Modified vapor phase deposition technology for high-performance uncooled MIR PbSe detectors. RSC Adv. 2021, 11, 34908–34914. [Google Scholar] [CrossRef] [PubMed]

- Mirzaei, M.R.; Shi, Z. Room-temperature nanostructured PbSe/CdSe mid-infrared photodetector: Annealing effects. J. Vac. Sci. Technol. B 2024, 42, 012204. [Google Scholar] [CrossRef]

- Kim, C.Y.; Woo, D.H.; Lee, H.C. High-Dynamic-Range ROIC With Asynchronous Self-Controlled Two-Gain Modes for MWIR Focal Plane Arrays. IEEE Sens. J. 2019, 19, 615–622. [Google Scholar] [CrossRef]

- Chu, P.; Chen, H.; Ding, R. A novel linear-logarithmic readout integrated circuit with high dynamic range. Infrared Phys. Technol. 2020, 105, 103158. [Google Scholar] [CrossRef]

- Margarit, J.M.; Teres, L.; Serra-Graells, F. A Sub-μW Fully Tunable CMOS DPS for Uncooled Infrared Fast Imaging. IEEE Trans. Circuits Syst. I 2009, 56, 987–996. [Google Scholar] [CrossRef]

- Mirzaei, M.R.; Shi, Z.; Mirzaei, M.R.; Shi, Z. High-performance uncooled PbSe/CdSe nanostructured mid-infrared photodetector with tunable cutoff wavelength. Appl. Phys. Lett. 2024, 125, 083501. [Google Scholar] [CrossRef]

- Ma, H.; Kong, H.; Chang, C. Design of a multi-mode digital pixel with conversion data protection. IET Circuits Devices Syst. 2022, 16, 501–524. [Google Scholar] [CrossRef]

- Kayahan, H.; Yazici, M.; Ceylan, Ö.; Gurbuz, Y. A new digital readout integrated circuit (DROIC) with pixel parallel A/D conversion and reduced quantization noise. Infrared Phys. Technol. 2014, 63, 125–132. [Google Scholar] [CrossRef]

- Chen, Y.; Yuan, F.; Khan, G. A new wide dynamic range CMOS pulse-frequency-modulation digital image sensor with in-pixel variable reference voltage. In Proceedings of the 2008 51st IEEE International Midwest Symposium on Circuits and Systems, Knoxville, TN, USA, 10–13 August 2008; pp. 129–132. [Google Scholar] [CrossRef]

- Abbasi, S.; Galioglu, A.; Shafique, A.; Ceylan, O.; Yazici, M.; Gurbuz, Y. A PFM-Based Digital Pixel With an Off-Pixel Residue Measurement for Small Pitch FPAs. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 887–891. [Google Scholar] [CrossRef]

- Figueras, R.; Margarit, J.M.; Vergara, G.; Villamayor, V.; Gutierrez-Alvarez, R.; Fernandez-Montojo, C.; Teres, L.; Serra-Graells, F. A 128× 128-pix 4-kfps 14-bit Digital-Pixel PbSe-CMOS Uncooled MWIR Imager. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Goto, M.; Honda, Y.; Watabe, T.; Hagiwara, K.; Nanba, M.; Iguchi, Y.; Saraya, T.; Kobayashi, M.; Higurashi, E.; Toshiyoshi, H.; et al. Quarter Video Graphics Array Digital Pixel Image Sensing With a Linear and Wide- Dynamic-Range Response by Using Pixel-Wise 3-D Integration. IEEE Trans. Electron Devices 2019, 66, 969–975. [Google Scholar] [CrossRef]

- Abbasi, S.; Ceylan, O.; Gurbuz, Y. A DROIC Based on PFM ADCs Employing Over-Integration for Error Shaping. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 3713–3722. [Google Scholar] [CrossRef]

- Dei, M.; Figueras, R.; Margarit, J.M.; Teres, L.; Serra-Graells, F. Highly linear integrate-and-fire modulators with soft reset for low-power high-speed imagers. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Chen, D.G.; Matolin, D.; Bermak, A.; Posch, C. Pulse-Modulation Imaging—Review and Performance Analysis. IEEE Trans. Biomed. Circuits Syst. 2011, 5, 64–82. [Google Scholar] [CrossRef] [PubMed]

- Allen, P.E.; Holberg, D.R. CMOS Analog Circuit Design, 3rd ed.; The Oxford series in electrical and computer engineering; Oxford University Press: New York, NY, USA; Oxford, UK, 2012. [Google Scholar]

- Jo, Y.M.; Woo, D.H.; Kang, S.G.; Lee, H.C. Very Wide Dynamic Range ROIC With Pixel-Level ADC for SWIR FPAs. IEEE Sens. J. 2016, 16, 7227–7233. [Google Scholar] [CrossRef]

- Altun, O.; Kepenek, R.; Tasdemir, F.; Akyurek, F.; Tunca, C.; Akbulut, M.; Nuzumlali, O.L.; Inceturkmen, E. Development of a fully programmable ROIC with 15 μm pixel pitch for MWIR applications. In Proceedings of the SPIE Defense + Security, Anaheim, CA, USA, 9–13 April 2017; Andresen, B.F., Fulop, G.F., Hanson, C.M., Miller, J.L., Norton, P.R., Eds.; p. 1017720. [Google Scholar] [CrossRef]

| [15] | [21] | [22] | This Work | |

|---|---|---|---|---|

| Array Size | 128 × 128 | 640 × 512 | 640 × 512 | 64 × 64 |

| Pixel Size (μm) | 50 × 50 | 25 × 25 | 15 × 15 | 50 × 50 |

| Input Structure | CTIA | CTIA | DI | CTIA |

| Pixel Type | Digital | Digital | Analog | Digital |

| Max Input Current | 2 μA | 60 nA | - | 1.5 μA |

| Resolution (bits) | 10 | 13 | - | 12 |

| Capacity (Me−) | - | 350 | 4.5 | 560 |

| Frame Rate (fps) | 4000 | 730 | 300 | 4000 |

| Static Power | 10 μW/pixel | - | 100 mW | 6 μW/pixel |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cheng, Y.; Liu, J.; Wang, X.; Hou, H.; Jiang, Q.; Chang, Y. A PFM-Based Calibration Method for Low-Power High-Linearity Digital Pixel. Sensors 2025, 25, 252. https://doi.org/10.3390/s25010252

Cheng Y, Liu J, Wang X, Hou H, Jiang Q, Chang Y. A PFM-Based Calibration Method for Low-Power High-Linearity Digital Pixel. Sensors. 2025; 25(1):252. https://doi.org/10.3390/s25010252

Chicago/Turabian StyleCheng, Yu, Jionghan Liu, Xiyuan Wang, Hongyu Hou, Qian Jiang, and Yuchun Chang. 2025. "A PFM-Based Calibration Method for Low-Power High-Linearity Digital Pixel" Sensors 25, no. 1: 252. https://doi.org/10.3390/s25010252

APA StyleCheng, Y., Liu, J., Wang, X., Hou, H., Jiang, Q., & Chang, Y. (2025). A PFM-Based Calibration Method for Low-Power High-Linearity Digital Pixel. Sensors, 25(1), 252. https://doi.org/10.3390/s25010252