Fourth-Order Quadratic Buck Converter Controller Design †

Abstract

1. Introduction

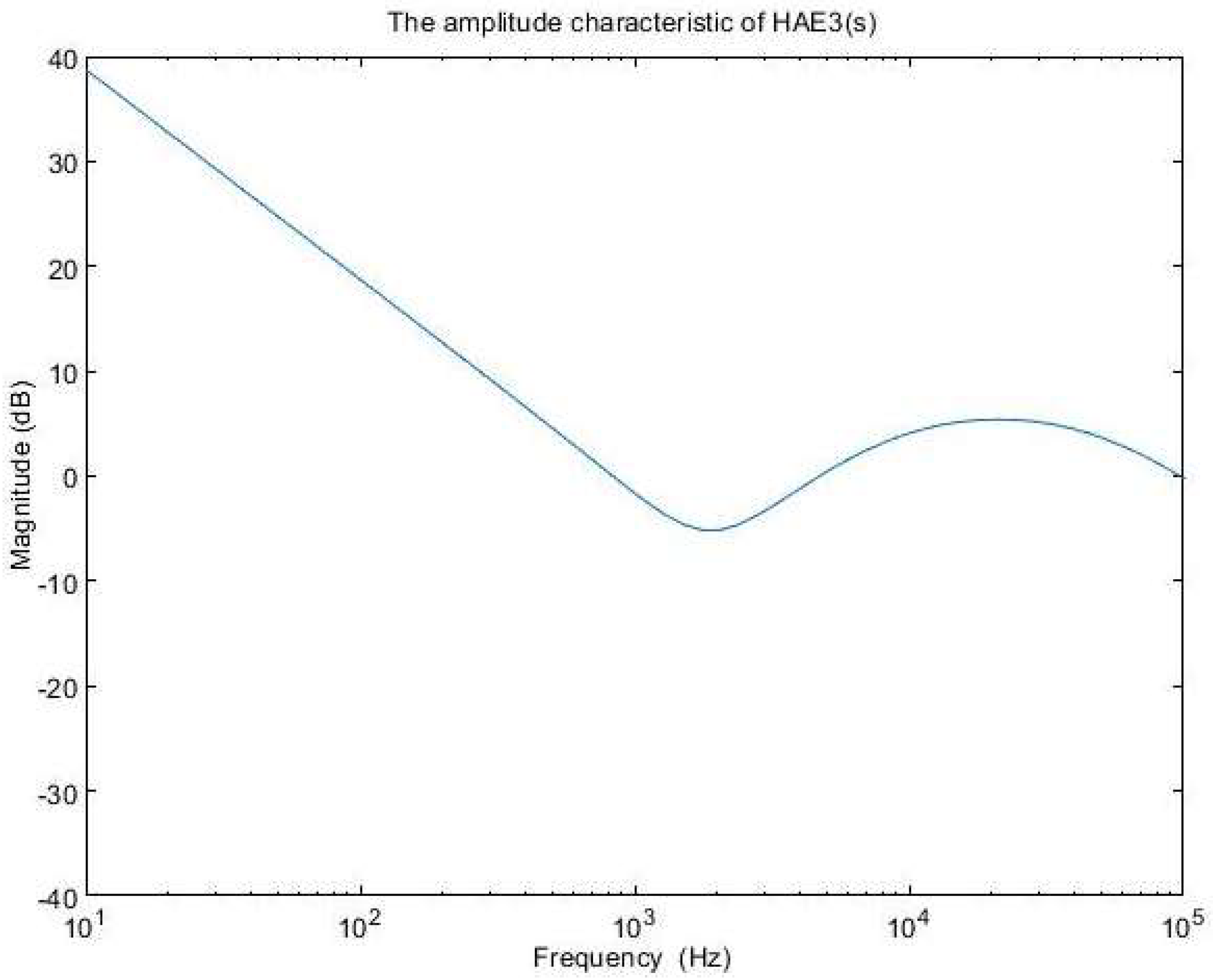

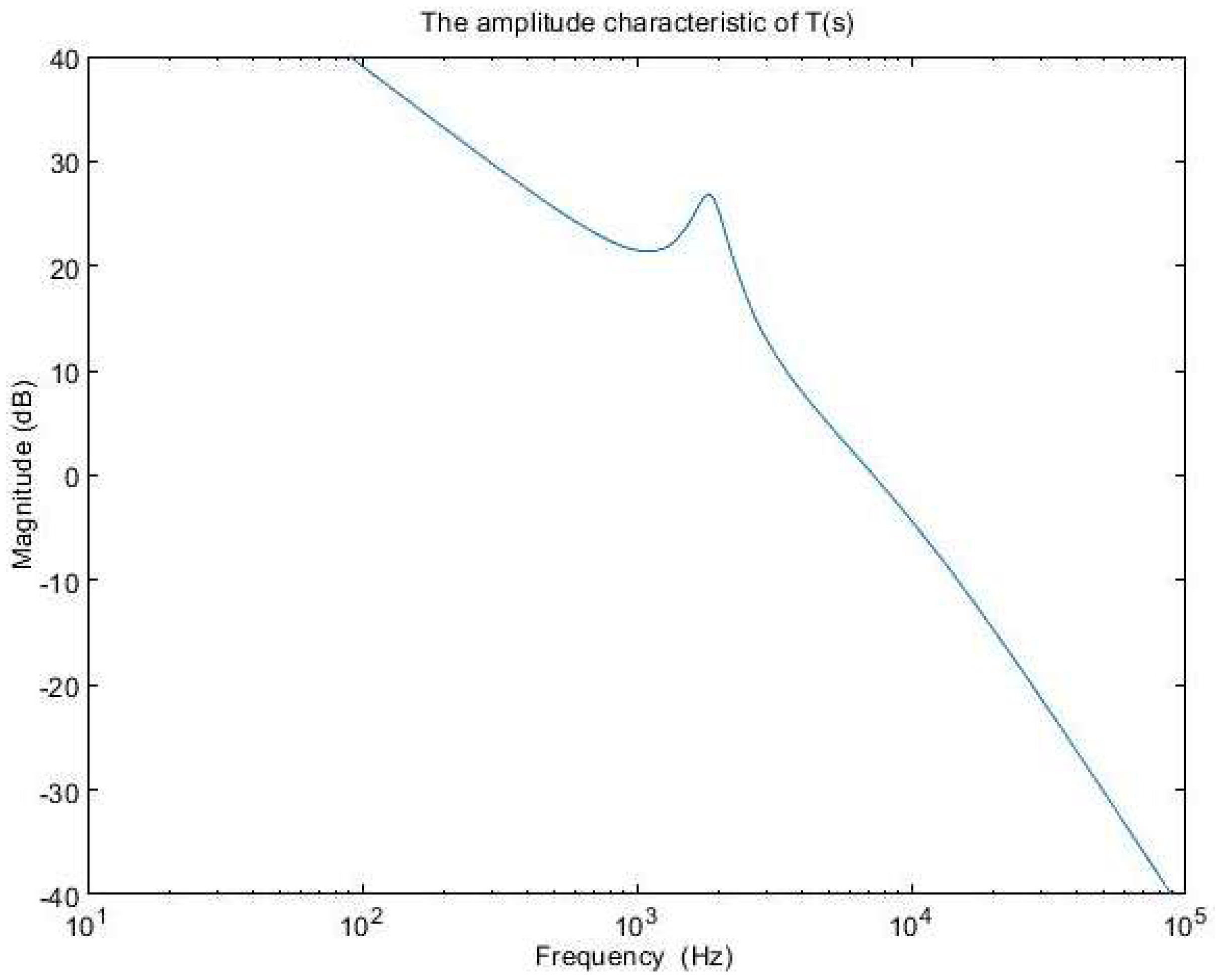

- Small-signal analysis was carried out using a state–space model;

- Linearization of the control-to-output function;

- Approximation using a second-order function;

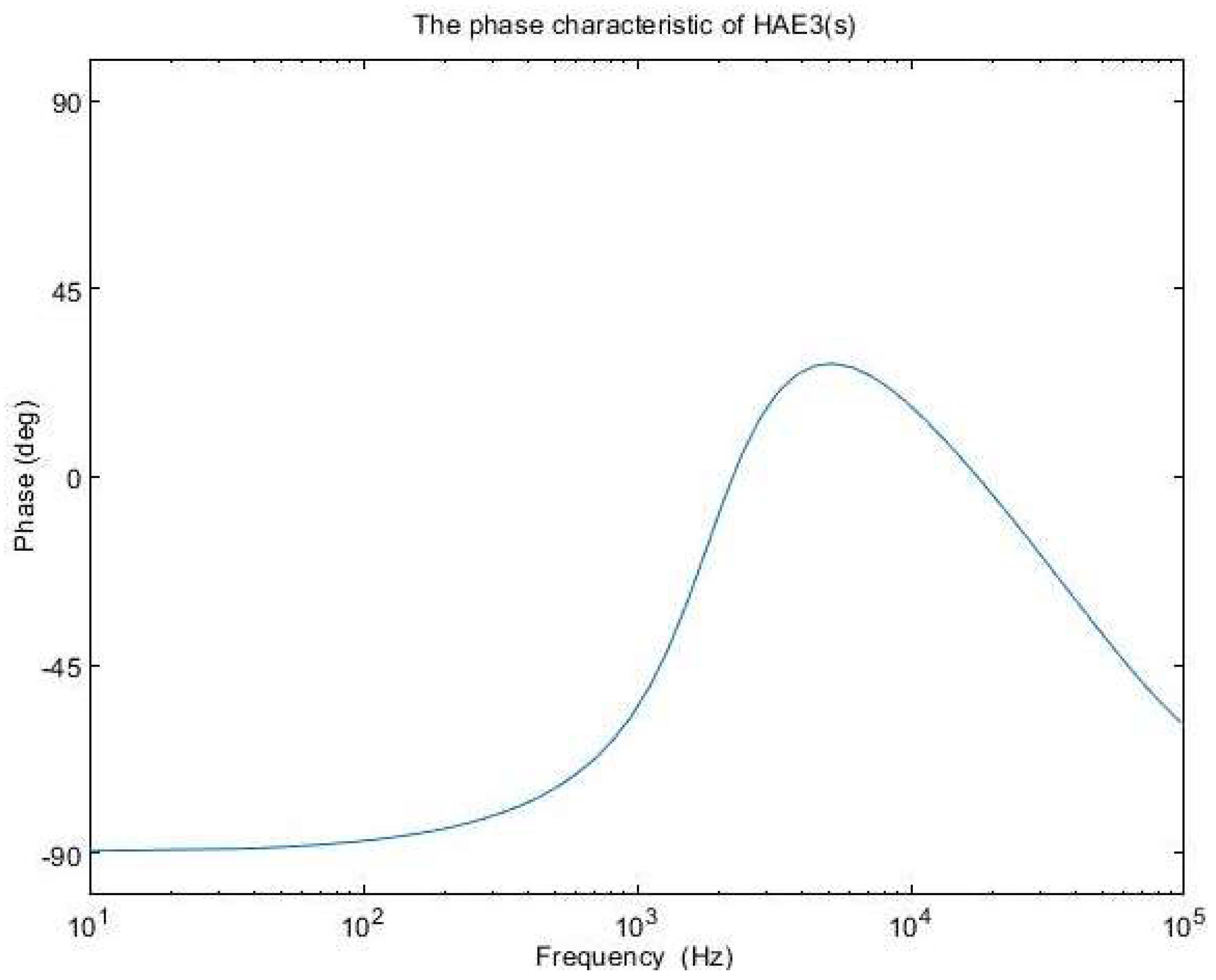

- A type III error amplifier was designed;

- The feasibility of the type III controller was confirmed in the simulations.

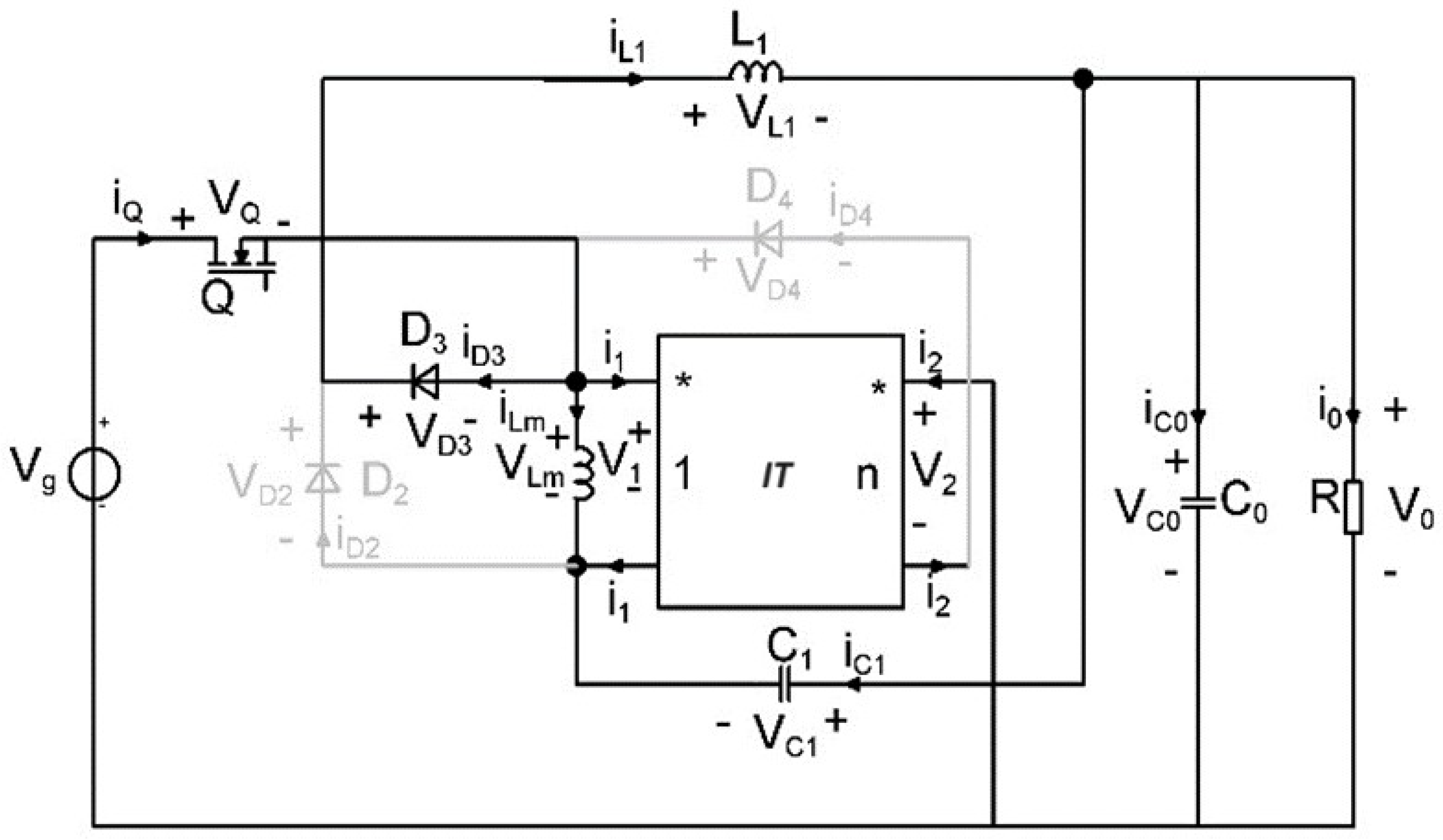

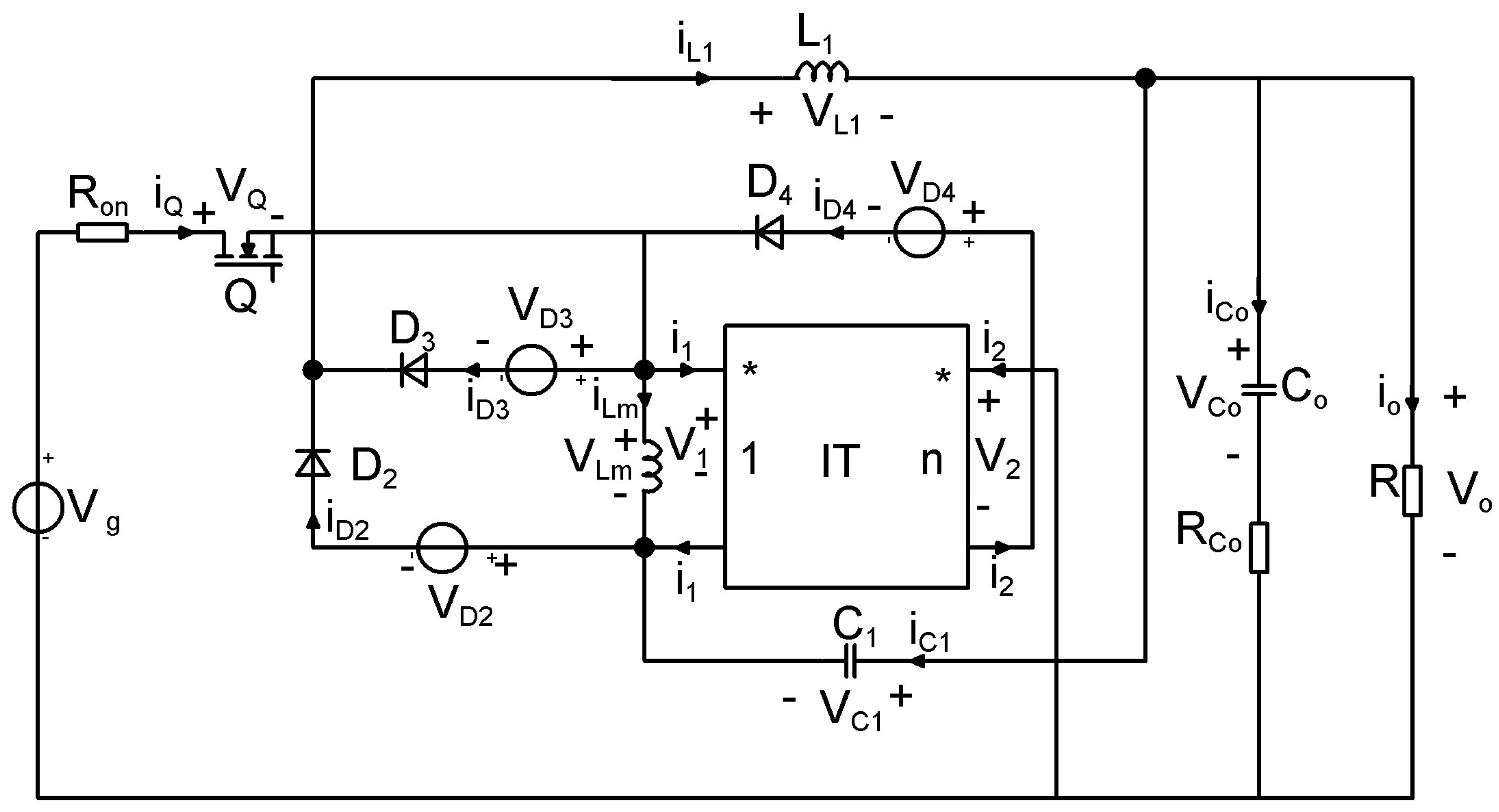

2. Materials and Methods

3. Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Tettamanti, M.; Pidutti, A.; Croce, P.D.; Baschirotto, A. An Asynchronous Constant TOFF, 10 A, Buck Converter with Peak Current Mode Control for Automotive Applications. In Proceedings of the 2023 18th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Valencia, Spain, 18–21 June 2023; pp. 49–52. [Google Scholar]

- Reyes-Portillo, I.A.; Morales-Saldaña, J.A.; Netzahuatl-Huerta, E.M.; Palacios-Hernández, E.R.; Méndez-Elizondo, S.R. Modeling of a Quadratic Buck Converter Based on the R2P2 Concept for PV Applications. In Proceedings of the 2020 IEEE International Autumn Meeting on Power, Electronics and Computing (ROPEC), Ixtapa, Mexico, 4–6 November 2020; pp. 1–6. [Google Scholar]

- Yeh, W.-T.; Yao, G.-S.; Chen, C.-Y.; Tsai, C.-H. A 411nA Quiescent Current Hysteretic Buck Converter with Self-Control Biasing and Dynamic Voltage Scaling (DVS) for IoT Applications. In Proceedings of the 2023 International VLSI Symposium on Technology, Systems and Applications (VLSI-TSA/VLSI-DAT), HsinChu, Taiwan, 17–20 April 2023; pp. 1–2. [Google Scholar]

- Widjonarko; Rahardi, G.A.; Avian, C.; Hadi, W.; Herdiyanto, D.W.; Satrio, P.L. Driver for LED Lamp with Buck Converter Controlled by PID. In Proceedings of the 2021 International Seminar on Intelligent Technology and Its Applications (ISITIA), Surabaya, Indonesia, 21–22 July 2021; pp. 216–219. [Google Scholar]

- Deekshitha, C.; Shenoy, K.L. Design and simulation of synchronous buck converter for LED application. In Proceedings of the 2017 2nd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, India, 19–20 May 2017; pp. 142–146. [Google Scholar]

- Malik, M.S.; Khan, H.A.; Zaffar, N.A. Evaluation of a Single Inductor based Single-Input Dual-Output Buck Converter for DC Microgrid Applications. In Proceedings of the 2018 IEEE 7th World Conference on Photovoltaic Energy Conversion (WCPEC) (A Joint Conference of 45th IEEE PVSC, 28th PVSEC & 34th EU PVSEC), Waikoloa, HI, USA, 10–15 June 2018; pp. 0613–0617. [Google Scholar]

- Bizzarri, F.; Gardini, L.; Nora, P.; Brambilla, A. A Stability Condition for Constant-On Time Buck Converters Suitable for Automotive Applications. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–5. [Google Scholar]

- Babu, P.N.; Bana, P.R.; Peesapati, R.B.; Panda, G. An Interleaved Buck Converter Based Active Power Filter for Photovoltaic Energy Application. In Proceedings of the 2019 International Conference on Power Electronics Applications and Technology in Present Energy Scenario (PETPES), Mangalore, India, 29–31 August 2019; pp. 1–6. [Google Scholar]

- Rehman, H.U. Modified Switched-Inductor Based DC-DC Buck-Boost Converter for Low-Power Applications. In Proceedings of the IECON 2021—47th Annual Conference of the IEEE Industrial Electronics Society, Toronto, ON, Canada, 13–16 October 2021; pp. 1–6. [Google Scholar]

- Zanatta, N.; Caldognetto, T.; Biadene, D.; Spiazzi, G.; Mattavelli, P. A Two-Stage Twin-Bus Buck Converter for Battery Charging Applications. In Proceedings of the 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 19–23 March 2023; pp. 1908–1914. [Google Scholar]

- Sankaranarayanan, S.; Vinod, K.C.; Sreekumar, A.; Laxminidhi, T.; Singhal, V.; Chauhan, R. Single Inductor Dual Output Buck Converter for Low Power Applications and Its Stability Analysis. In Proceedings of the 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), Pune, India, 6–10 January 2018; pp. 347–352. [Google Scholar]

- Divya, G.; Sridharan, S.; Velmurugan, P. Integrated Interleaved Luo Converter with Buck Converter Designed for Electric Vehicle Application. In Proceedings of the 2023 9th International Conference on Electrical Energy Systems (ICEES), Chennai, India, 23–25 March 2023; pp. 670–673. [Google Scholar]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 2nd ed.; Springer: New York, NY, USA, 2012. [Google Scholar]

- Dumitru, F.; Dimitriu, B.; Campanu, I.; Brezeanu, G. An Asynchronous digital, Hysteretic Controller for an Automotive Application DC-DC Buck Converter. In Proceedings of the 2022 International Semiconductor Conference (CAS), Poiana Brasov, Romania, 12–14 October 2022; pp. 213–216. [Google Scholar]

- Chaudhary, K.; Singh, K.A.; Chaudhary, A. Integrated Quadruple Output Synchronous Buck Converter for E-Mobility Application. IEEE Trans. Ind. Appl. 2022, 58, 5558–5567. [Google Scholar] [CrossRef]

- Talukder, R.; Golla, T.; Setty, A.R.; Sridharan, S.; Kapat, S. Performance and Stability Analysis of a Multiphase Buck Converter under Mixed-Signal Current Mode Control for Mobile and Automotive Applications. In Proceedings of the 2022 IEEE 1st Industrial Electronics Society Annual On-Line Conference (ONCON), Kharagpur, India, 9–11 December 2022; pp. 1–6. [Google Scholar]

- Ravi, D.; Ghosh, A. Voltage Mode Control of Buck Converter using Practical PID Controller. In Proceedings of the 2022 International Conference on Intelligent Controller and Computing for Smart Power (ICICCSP), Hyderabad, India, 21–23 July 2022; pp. 1–6. [Google Scholar]

- Nayak, G.; Nath, S. Voltage Mode Control of Magnetically Coupled SIDO Buck Converter. In Proceedings of the 2018 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Chennai, India, 18–21 December 2018; pp. 1–6. [Google Scholar]

- Botila, D.-A.; Pop-Calimanu, I.-M.; Lascu, D. A Novel Single Switch Step Down Converter. In Proceedings of the 2021 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), Gliwice, Poland, 25–29 April 2021; pp. 31–38. [Google Scholar] [CrossRef]

- Gabian, G.; Gamble, J.; Blalock, B.; Costinett, D. Hybrid buck converter optimization and comparison for smart phone integrated battery chargers. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 2148–2154. [Google Scholar]

- Anushka, P.V.; Mani, N.; Issac, K. Switched-inductor semi-quadratic buck converter. In Proceedings of the 2017 International Conference on Technological Advancements in Power and Energy (TAP Energy), Kollam, India, 21–23 December 2017; pp. 1–6. [Google Scholar]

- Mummadi, V. Two-Switch Semi-Quadratic Buck Converter. IEEE Trans. Ind. Electron. 2016, 64, 1185–1194. [Google Scholar]

- Trakuldit, S.; Tattiwong, K.; Bunlaksananusorn, C. Design and evaluation of a Quadratic Buck Converter. Energy Rep. 2022, 8 (Suppl. S1), 536–543. [Google Scholar] [CrossRef]

- Biswas, M.; Majhi, S.; Nemade, H. A Larger Step-down Ratio Buck Converter with Reduced Ripple in Input Current and Output Voltage. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Smart Grid and Renewable Energy (PESGRE2020), Cochin, India, 2–4 January 2020; pp. 1–7. [Google Scholar]

- Yau, Y.T.; Jiang, W.Z.; Hwu, K.I. Bidirectional Operation of High Step-Down Converter. IEEE Trans. Power Electron. 2015, 30, 6829–6844. [Google Scholar] [CrossRef]

- Demian, A.E.; Treviso, C.H.G.; Gallo, C.A.; Tofoli, F.L. Non-isolated DC-DC converters with wide conversion range used to drive high-brightness LEDs. In Proceedings of the 2009 Brazilian Power Electronics Conference, Bonito-Mato Grosso do Sul, Brazil, 27 September–1 October 2009; pp. 598–605. [Google Scholar]

- Wang, X. One-cycle controlled quadratic buck converter. Int. J. Circ. Theor. Appl. 2018, 46, 1392–1406. [Google Scholar] [CrossRef]

- Maksimovic, D.; Cuk, S. Switching Converters with Wide DC Conversion Range. IEEE Trans. Power Electron. 1991, 6, 151–157. [Google Scholar] [CrossRef]

- Palomo, R.L.; Morales-Saldana, J.A.; Hernandez, E.P. Quadratic Step-Down dc-dc Converters Based on Reduced Redundant Power Processing Approach. IET Power Electron. 2013, 6, 136–145. [Google Scholar] [CrossRef]

- Lica, S.; Pop-Calimanu, I.-M.; Lascu, D. A New High Performance Step-Down Quadratic Converter. In Proceedings of the 2021 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), Gliwice, Poland, 25–29 April 2021; pp. 15–22. [Google Scholar]

- Pop, G.; Jurca, L.-D.; Pop, I.; Lascu, D. A New Highly Step-Down Quadratic Converter. In Proceedings of the 2023 22nd International Symposium on Power Electronics (Ee), Novi Sad, Serbia, 25–28 October 2023; pp. 01–06. [Google Scholar]

- Chen, G.; Deng, Y.; Dong, J.; Hu, Y.; Jiang, L.; He, X. Integrated Multiple-Output Synchronous Buck Converter for Electric Vehicle Power Supply. IEEE Trans. Veh. Technol. 2017, 66, 5752–5761. [Google Scholar] [CrossRef]

- Lica, S.; Lie, I.; Wegner, A.N.; Pop-Călimanu, I.M. A Generalized Model for Single-Switch Stacked Step-Down Converters. In Proceedings of the 2020 International Symposium on Electronics and Telecommunications (ISETC), Timisoara, Romania, 5–6 November 2020; pp. 1–4. [Google Scholar]

- Hinov, N.; Grigorova, T. Design Considerations of Multi-Phase Buck DC-DC Converter. Appl. Sci. 2023, 13, 11064. [Google Scholar] [CrossRef]

- Martinez, W.; Imaoka, J.; Itoh, Y.; Yamamoto, M.; Umetani, K. A novel high step-down interleaved converter with coupled inductor. In Proceedings of the 2015 IEEE International Telecommunications Energy Conference (INTELEC), Osaka, Japan, 18–22 October 2015; pp. 1–6. [Google Scholar]

- Yadlapalli, R.T.; Kotapati, A. Efficieny analysis of Quadratic buck converter for LED lamp driver applications. In Proceedings of the 2017 International Conference on Trends in Electronics and Informatics (ICEI), Tirunelveli, India, 11–12 May 2017; pp. 210–214. [Google Scholar]

- Altuğ, B.A.; Kababiyik, A.; Dincol, E.; Batunlu, C. Buck Converter with Optocoupler Based Switching. In Proceedings of the 2021 8th International Conference on Electrical and Electronics Engineering (ICEEE), Antalya, Turkey, 9–11 April 2021; pp. 184–190. [Google Scholar]

- Nayanasiri, D.; Li, Y. Step-Down DC–DC Converters: An Overview and Outlook. Electronics 2022, 11, 1693. [Google Scholar] [CrossRef]

- Jude, G.-M.; Pop-Calimanu, I.-M. A Novel Hybrid Quadratic Buck Converter. In Proceedings of the 2022 International Symposium on Electronics and Telecommunications (ISETC), Timisoara, Romania, 10–11 November 2022; pp. 1–4. [Google Scholar]

- Jude, G.-M.; Pop-Calimanu, I.-M.; Renken, F. A New Step-Up Converter with Coupled Inductor. In Proceedings of the 2020 International Symposium on Electronics and Telecommunications (ISETC), Timisoara, Romania, 5–6 November 2020; pp. 1–4. [Google Scholar]

- MATLAB, Matlab User Guide. Available online: https://matlab.mathworks.com/ (accessed on 20 November 2023).

- Basso, C. Switch-Mode Power Supplies, Spice Simulations and Practical Designs, 2nd ed.; McGraw-Hill: New York, NY, USA, 2014. [Google Scholar]

- Simulation Research, Caspoc, User Manual. Available online: http://www.simulationresearch.com (accessed on 20 November 2023).

| Semiconductor Devices | State 1 | State 2 |

|---|---|---|

| Q | On | Off |

| D2 | Off | On |

| D3 | On | Off |

| D4 | Off | On |

| Parameter | Proposed | QBC1 [28] | QBC2 [27] | QBC3 [29] | QBC4 [30] | Single Switch [19] | Stacked [33] | Classical [13] |

|---|---|---|---|---|---|---|---|---|

| No. of transistor | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| No. of diodes | 3 | 3 | 3 | 3 | 3 | 2 | 3 | 1 |

| Total no. of components | 9 | 8 | 8 | 8 | 8 | 8 | 12 | 4 |

| System order | 4 | 4 | 4 | 4 | 4 | 5 | 8 | 2 |

| Static Conversion Ratio (M) | ||||||||

| Transistor voltage stress | ||||||||

| Transistor DC current stress | ||||||||

| Maximum diode voltage stress | ||||||||

| Maximum diode DC current stress |

| Component | Theoretical Value | Simulated Value |

|---|---|---|

| Coupled inductor L2 | 398.84 µH | 463 µH |

| Coupled inductor L3 | 173.73 µH | 207 µH |

| Single inductor L1 | 264.83 µH | 266 µH |

| Inner capacitor C1 | 3.07 µF | 10 µF |

| Output capacitor C0 | 1.81 µF | 10 µF |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pop, G.-M.; Pop-Calimanu, I.-M.; Lascu, D. Fourth-Order Quadratic Buck Converter Controller Design. Sensors 2024, 24, 557. https://doi.org/10.3390/s24020557

Pop G-M, Pop-Calimanu I-M, Lascu D. Fourth-Order Quadratic Buck Converter Controller Design. Sensors. 2024; 24(2):557. https://doi.org/10.3390/s24020557

Chicago/Turabian StylePop, Gabriela-Madalina, Ioana-Monica Pop-Calimanu, and Dan Lascu. 2024. "Fourth-Order Quadratic Buck Converter Controller Design" Sensors 24, no. 2: 557. https://doi.org/10.3390/s24020557

APA StylePop, G.-M., Pop-Calimanu, I.-M., & Lascu, D. (2024). Fourth-Order Quadratic Buck Converter Controller Design. Sensors, 24(2), 557. https://doi.org/10.3390/s24020557