Electronically Tunable Memristor Emulator Implemented Using a Single Active Element and Its Application in Adaptive Learning

Abstract

:1. Introduction

- A single active block, i.e., DVCC, is used to implement the memristive behavior that comprises only one capacitor as a passive element.

- The operating frequency achieved here is the highest (up to 100 MHz) when compared to other recently available emulator models.

- The tunability is an additional advantage achieved using two PMOS serving as an active resistor.

- Lastly, the transistor count is the least among all the available designs, i.e., 15 transistors.

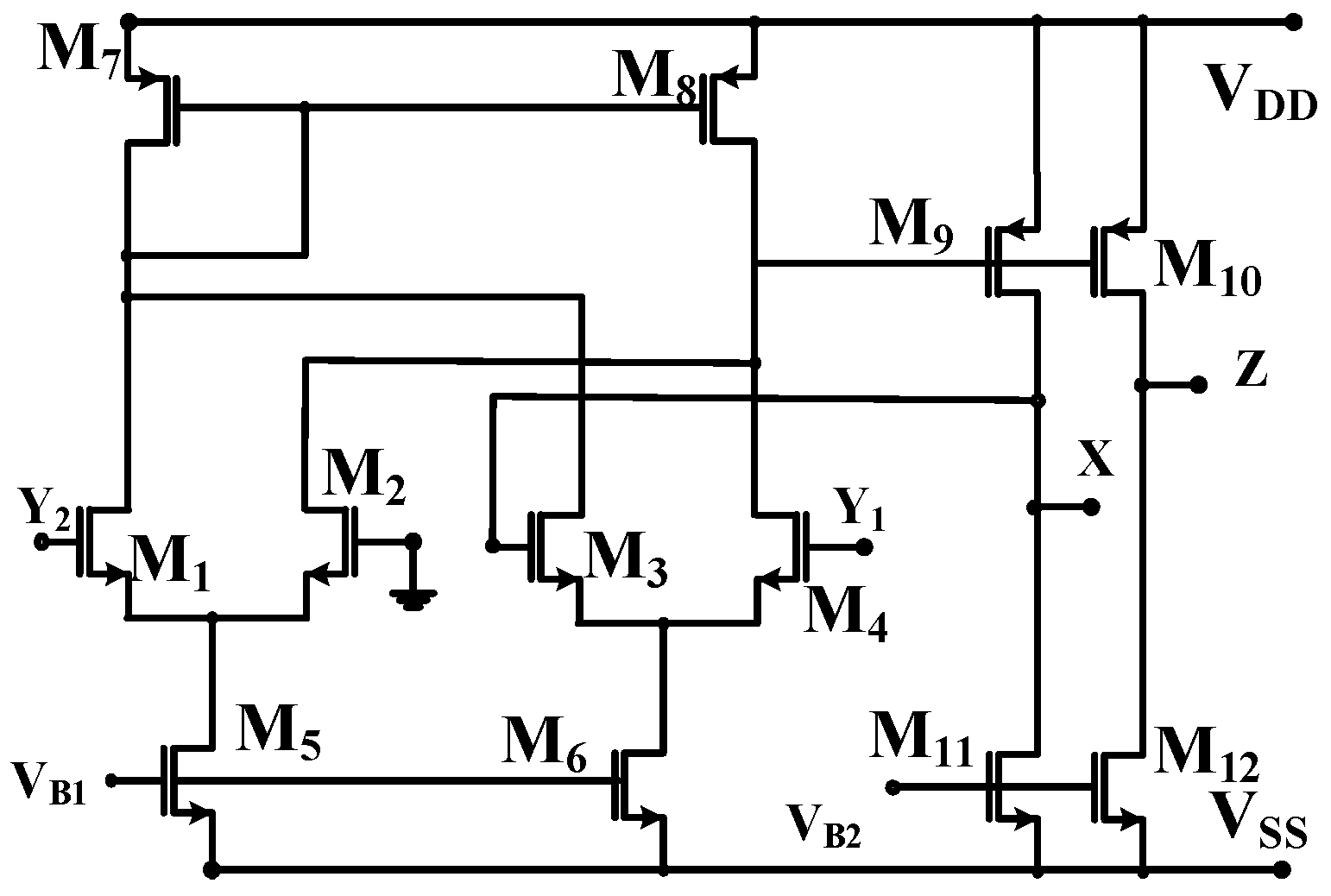

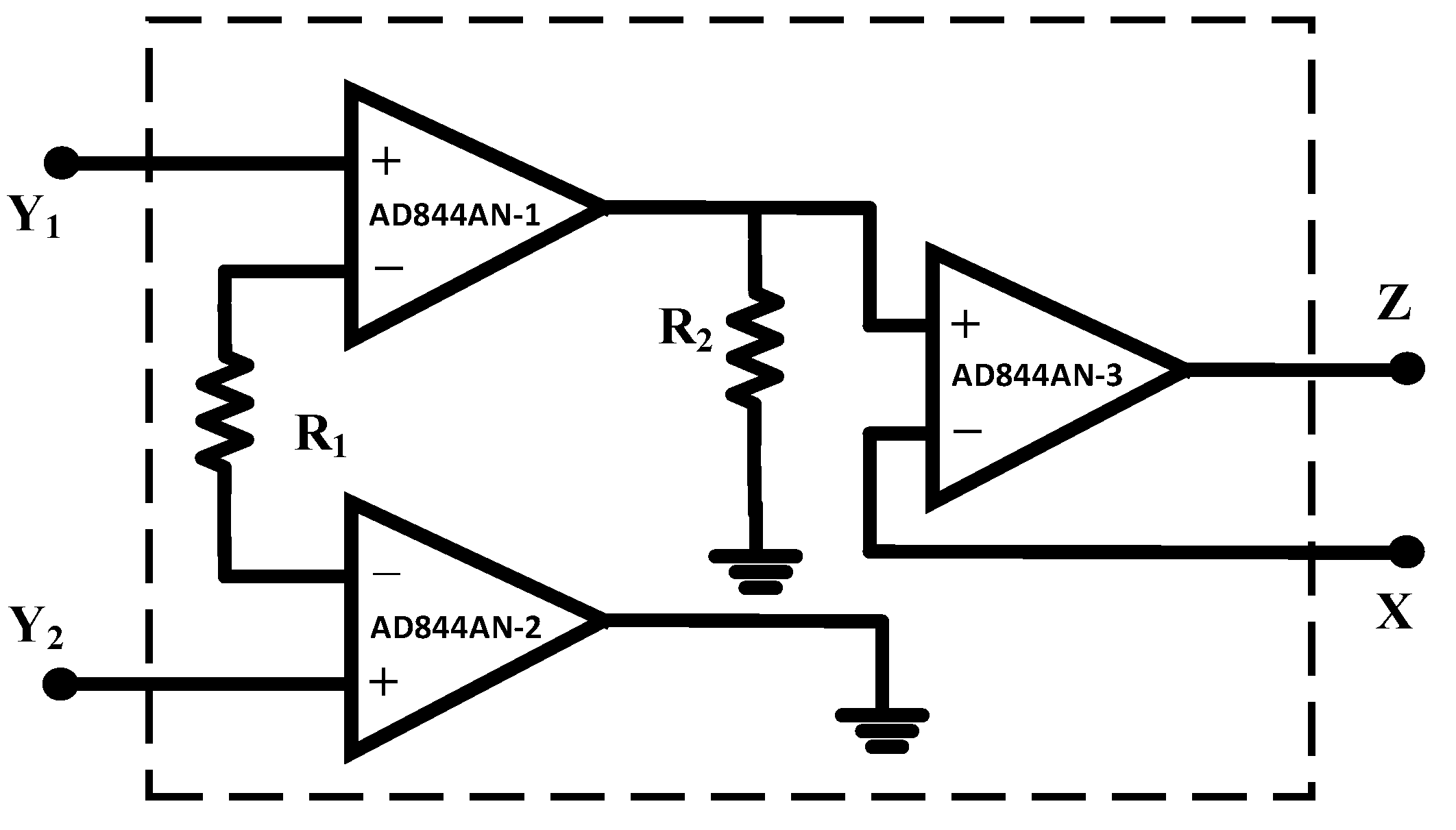

2. Differential Voltage Current Conveyor (DVCC) Block

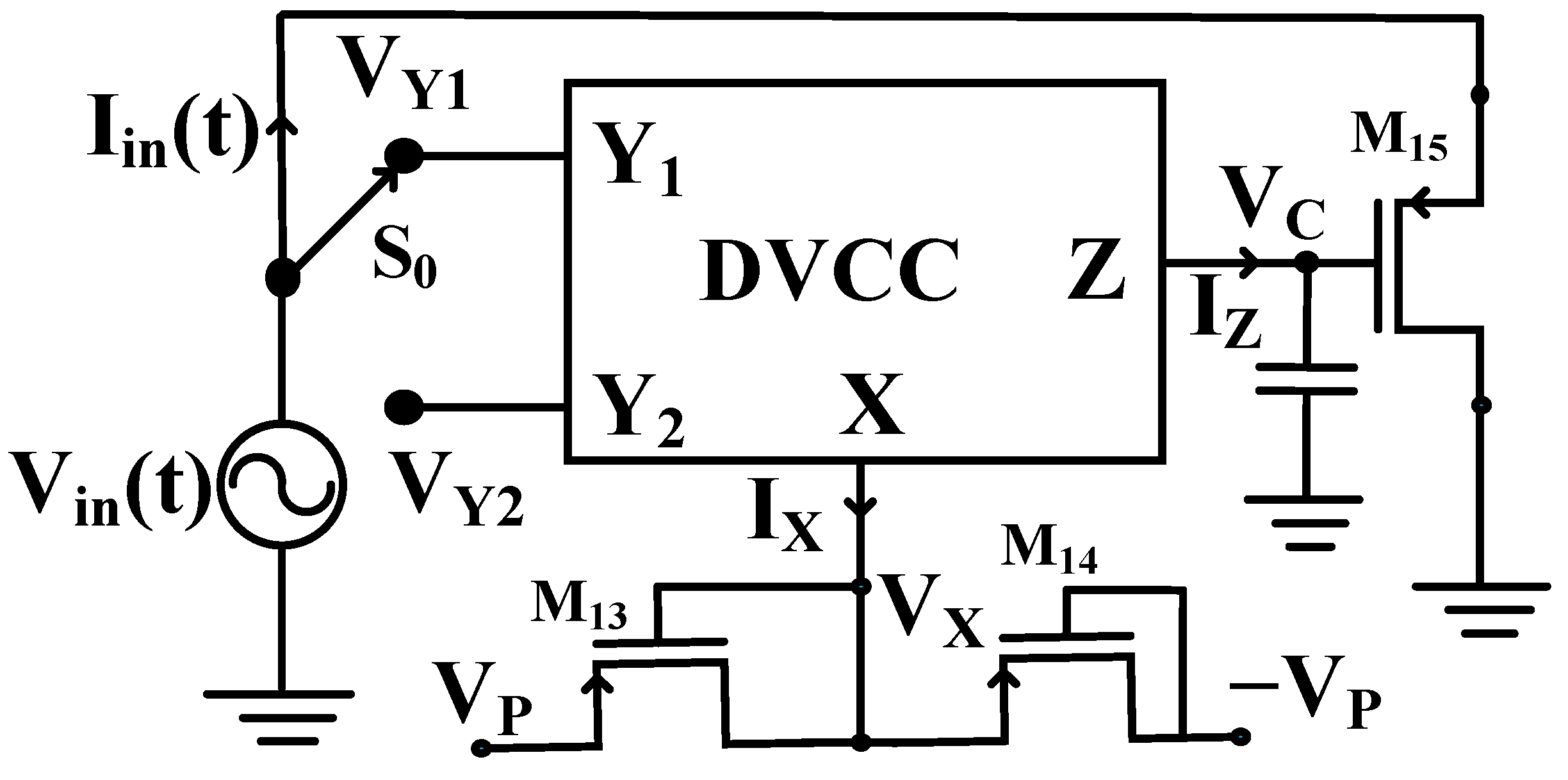

3. Proposed Memristor Emulator Design

3.1. Mathematical Analysis of Memristor Emulator

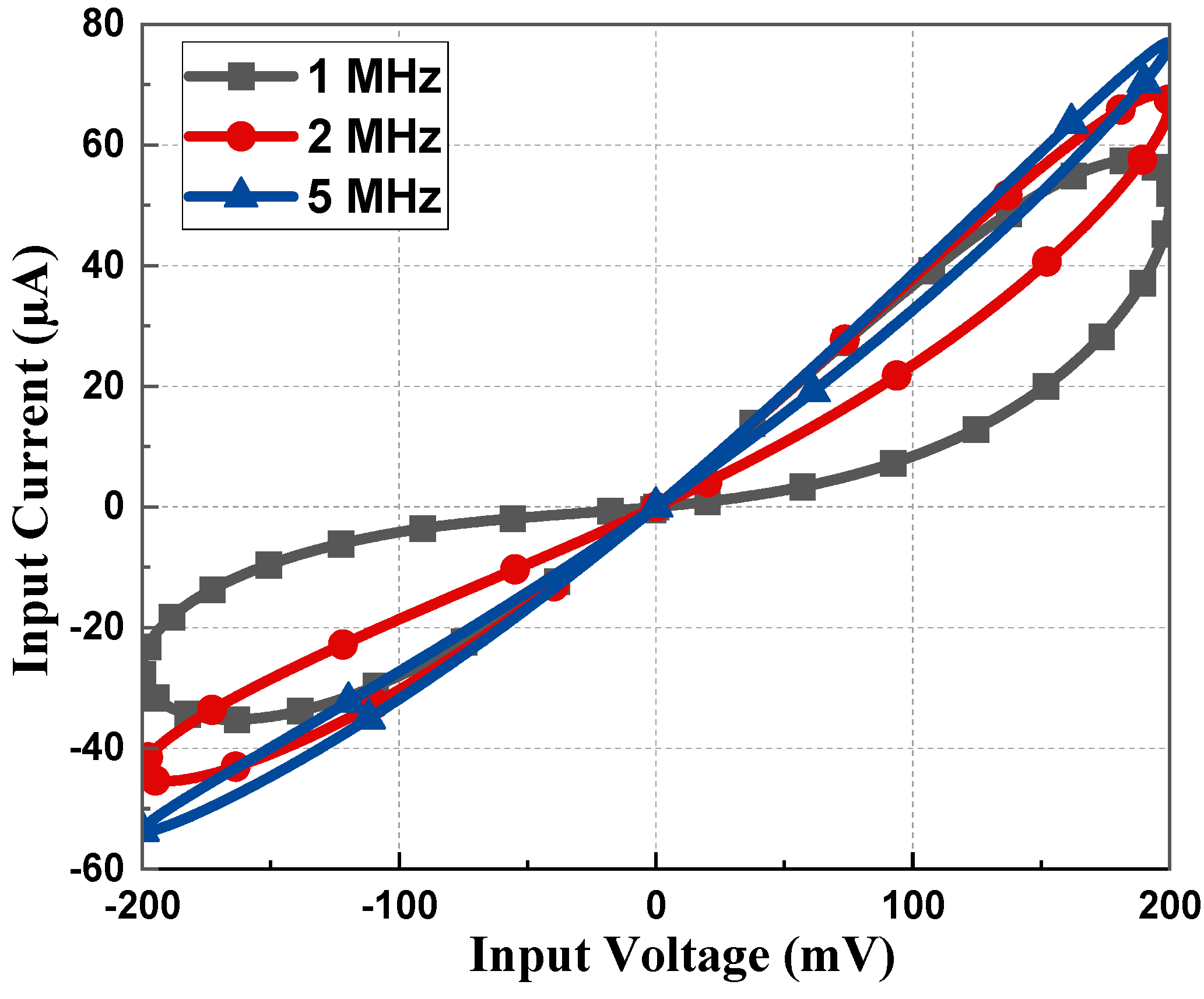

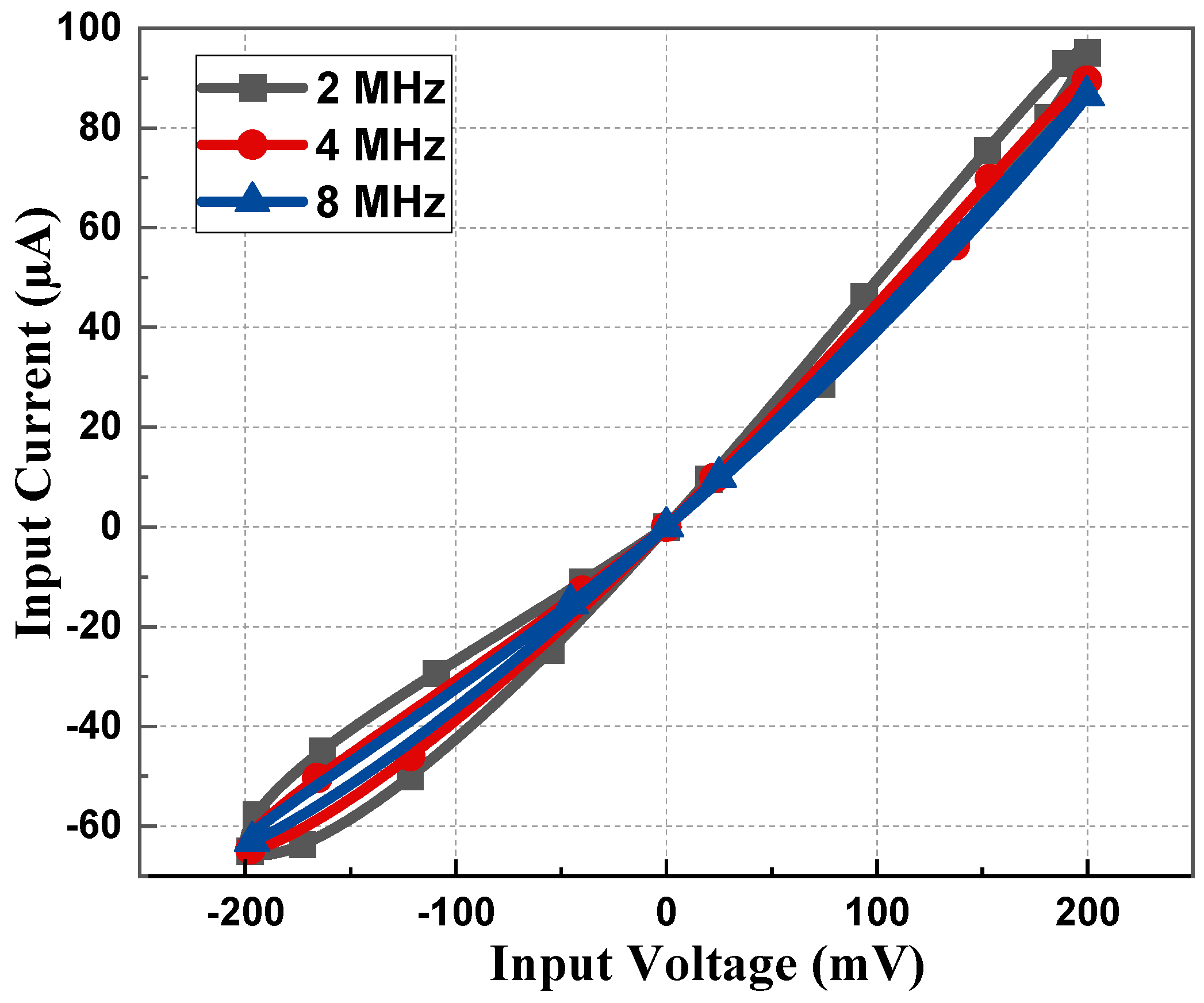

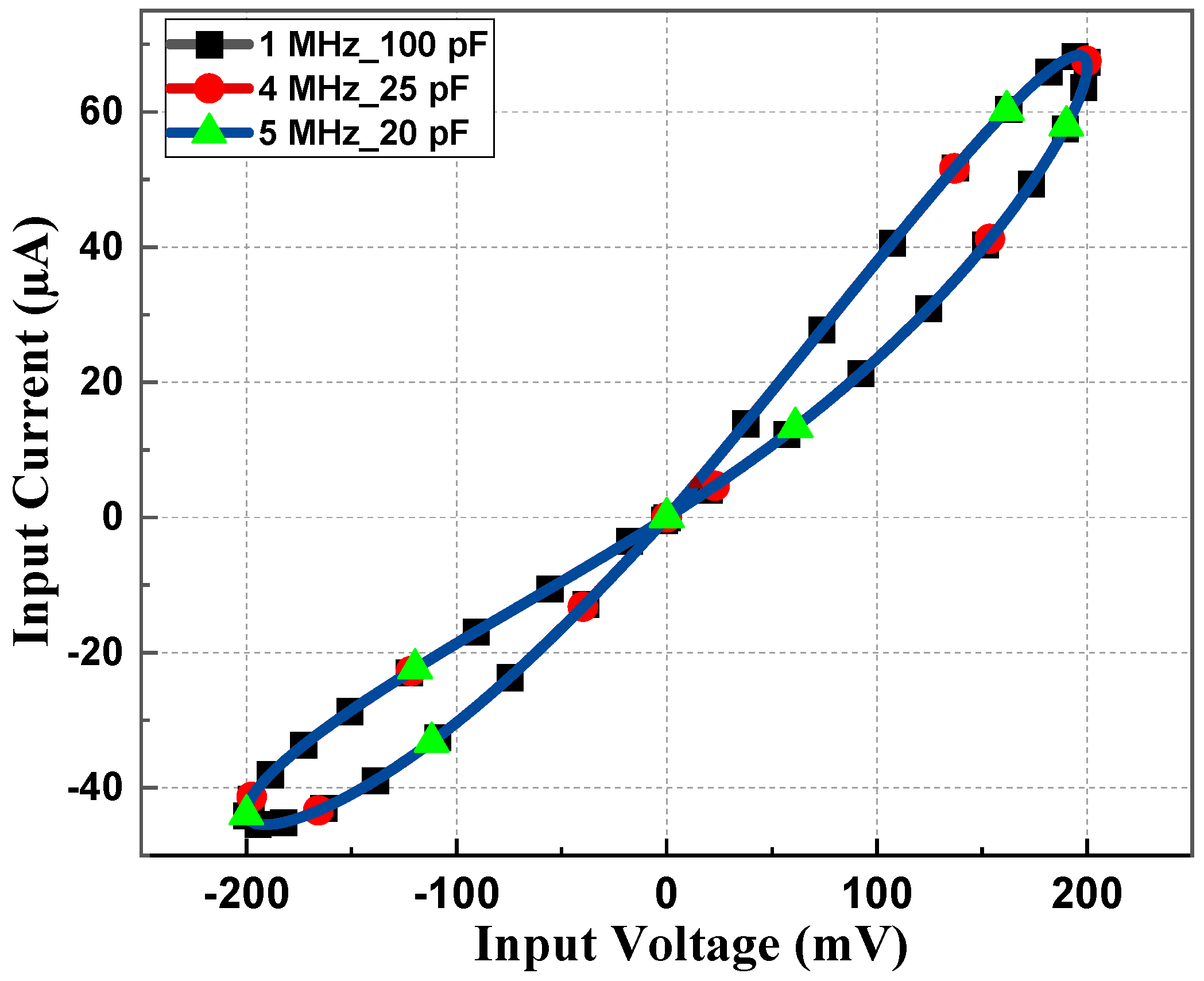

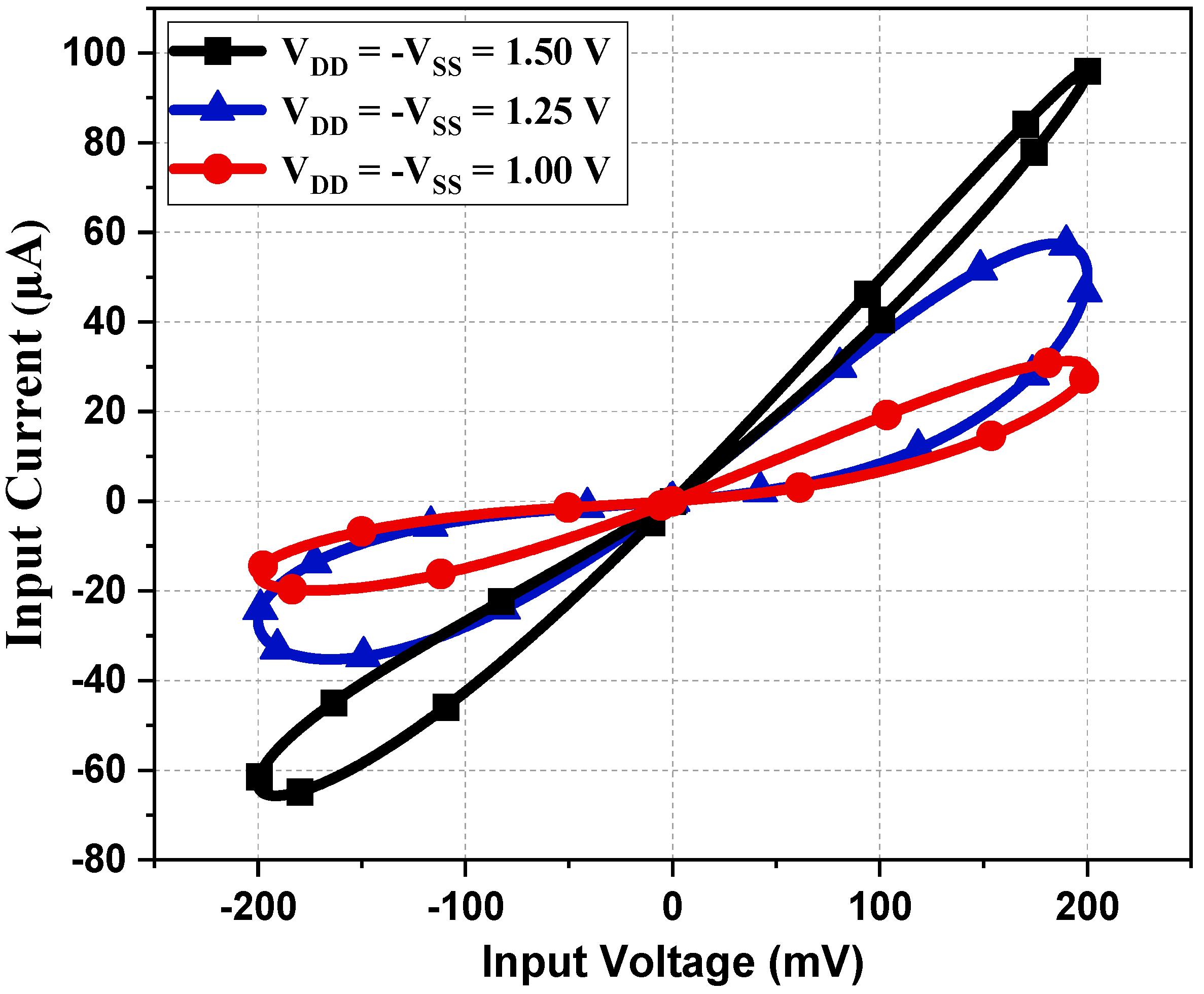

3.2. Frequency Response Analysis

4. Discussion

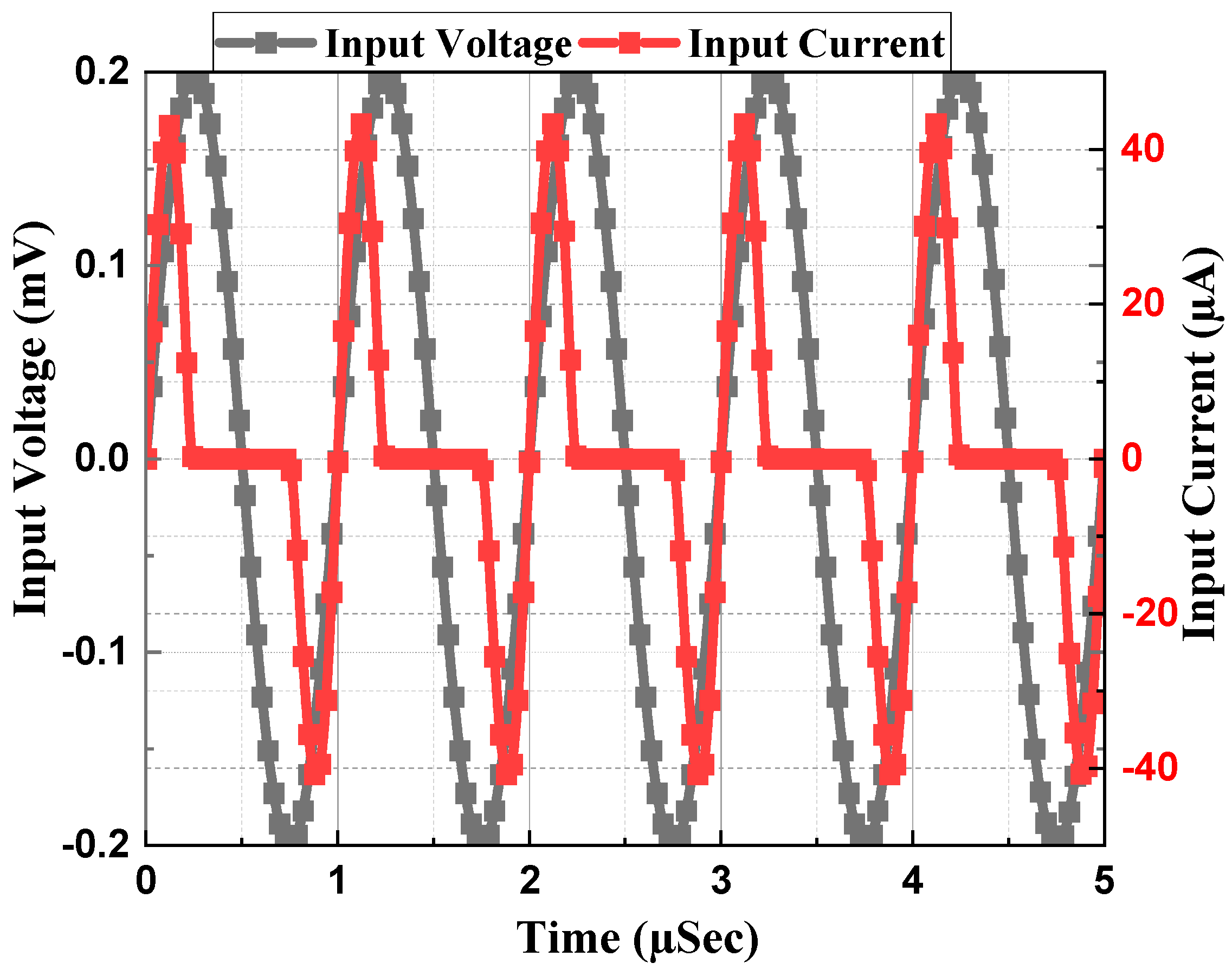

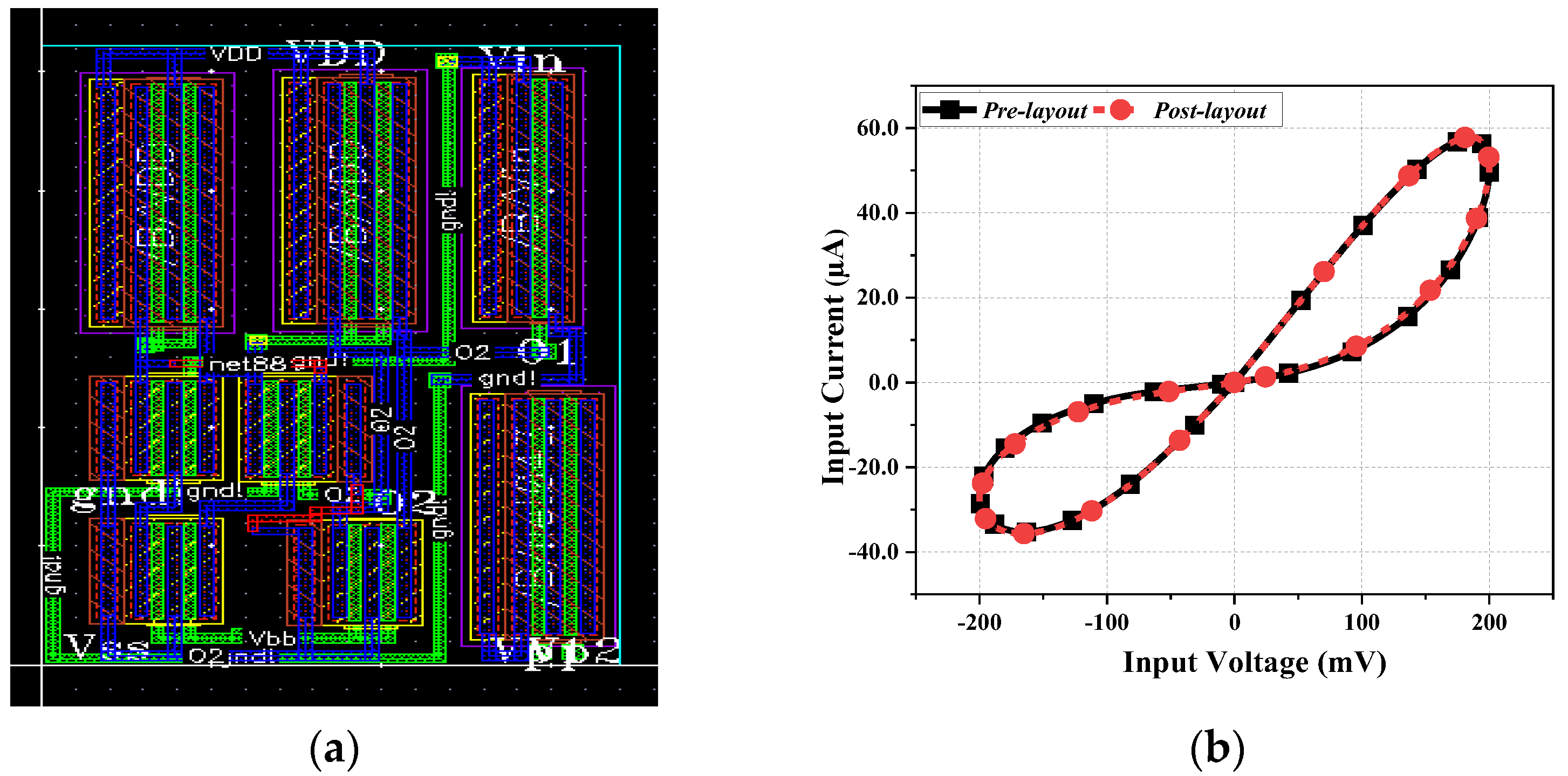

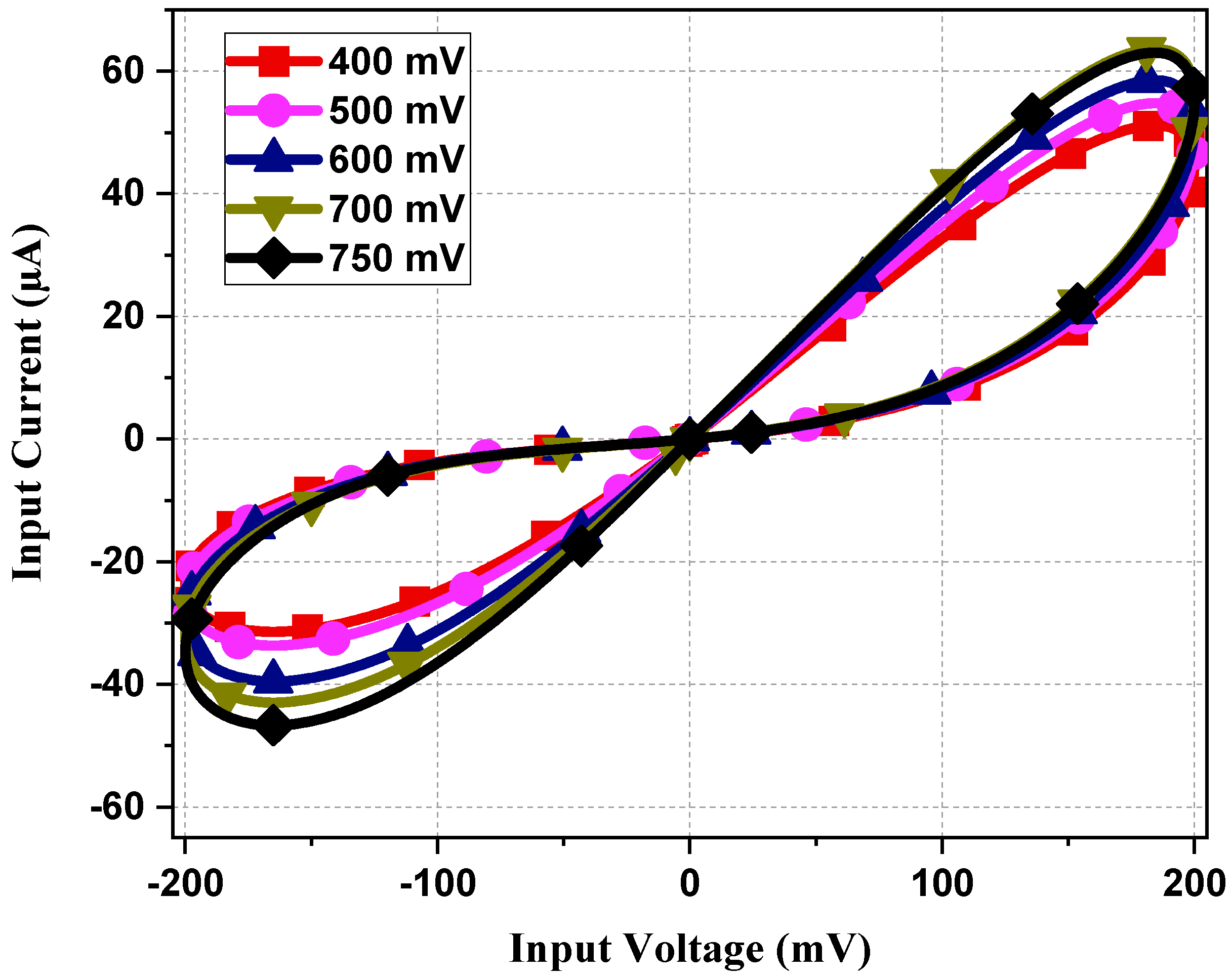

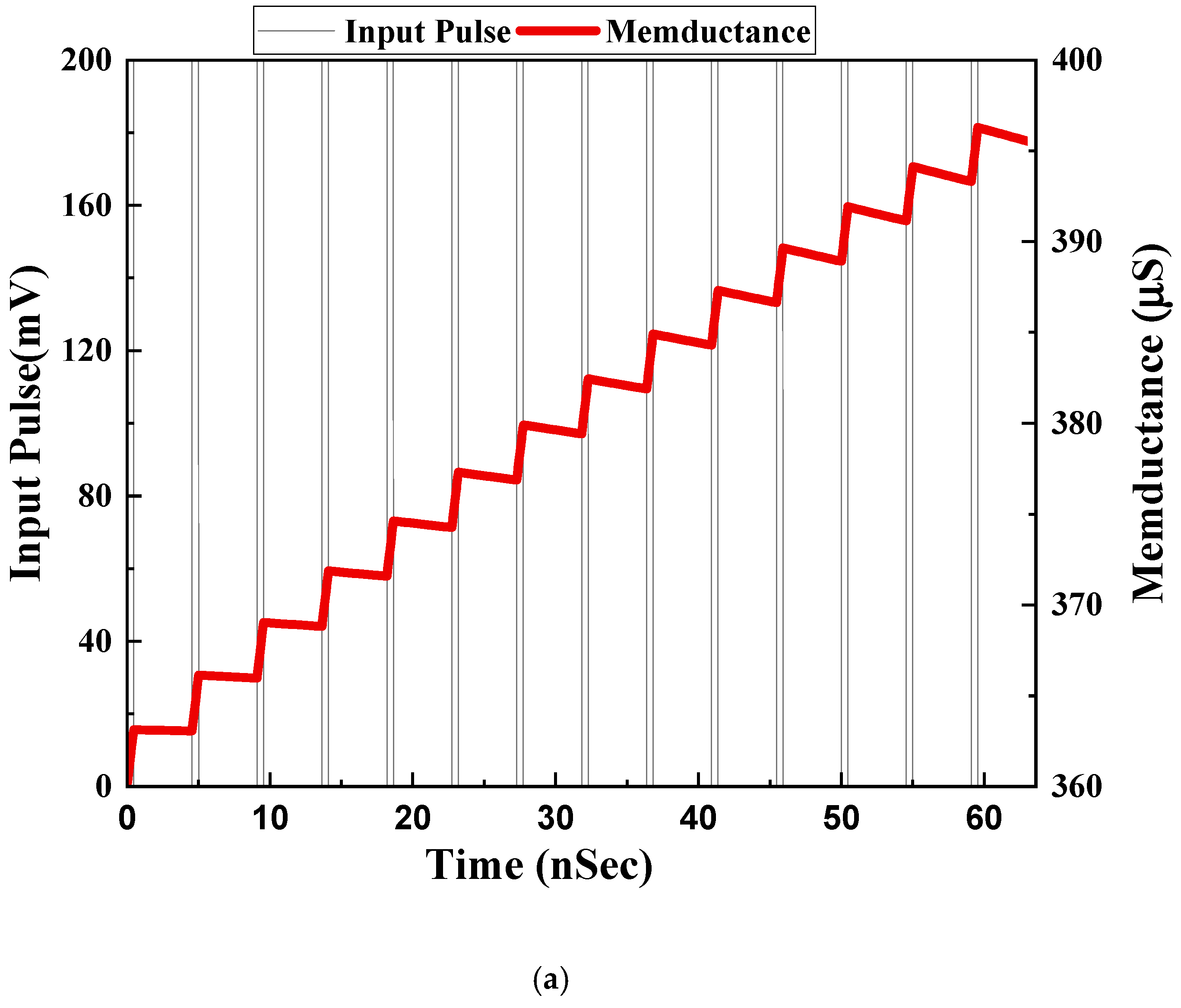

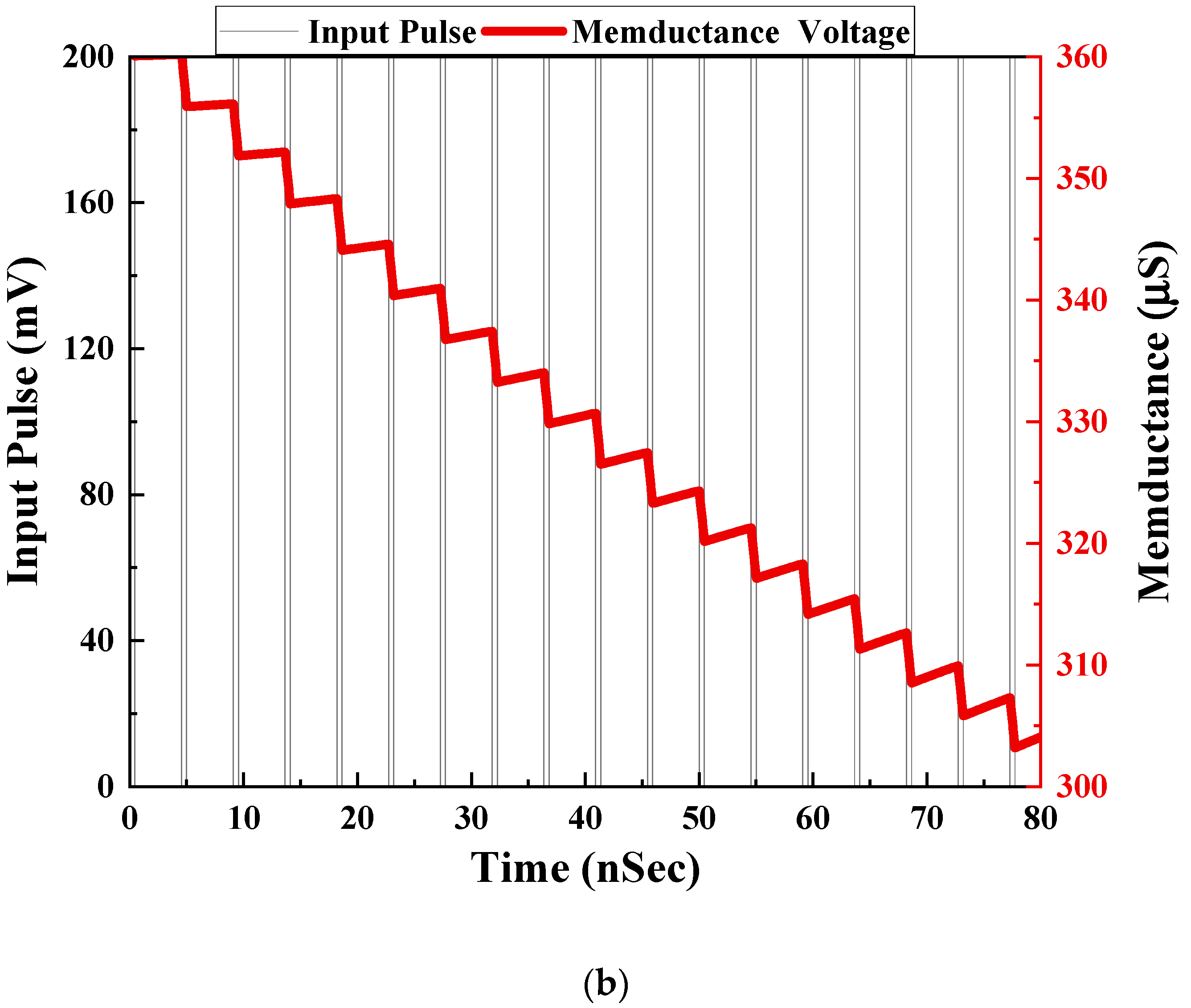

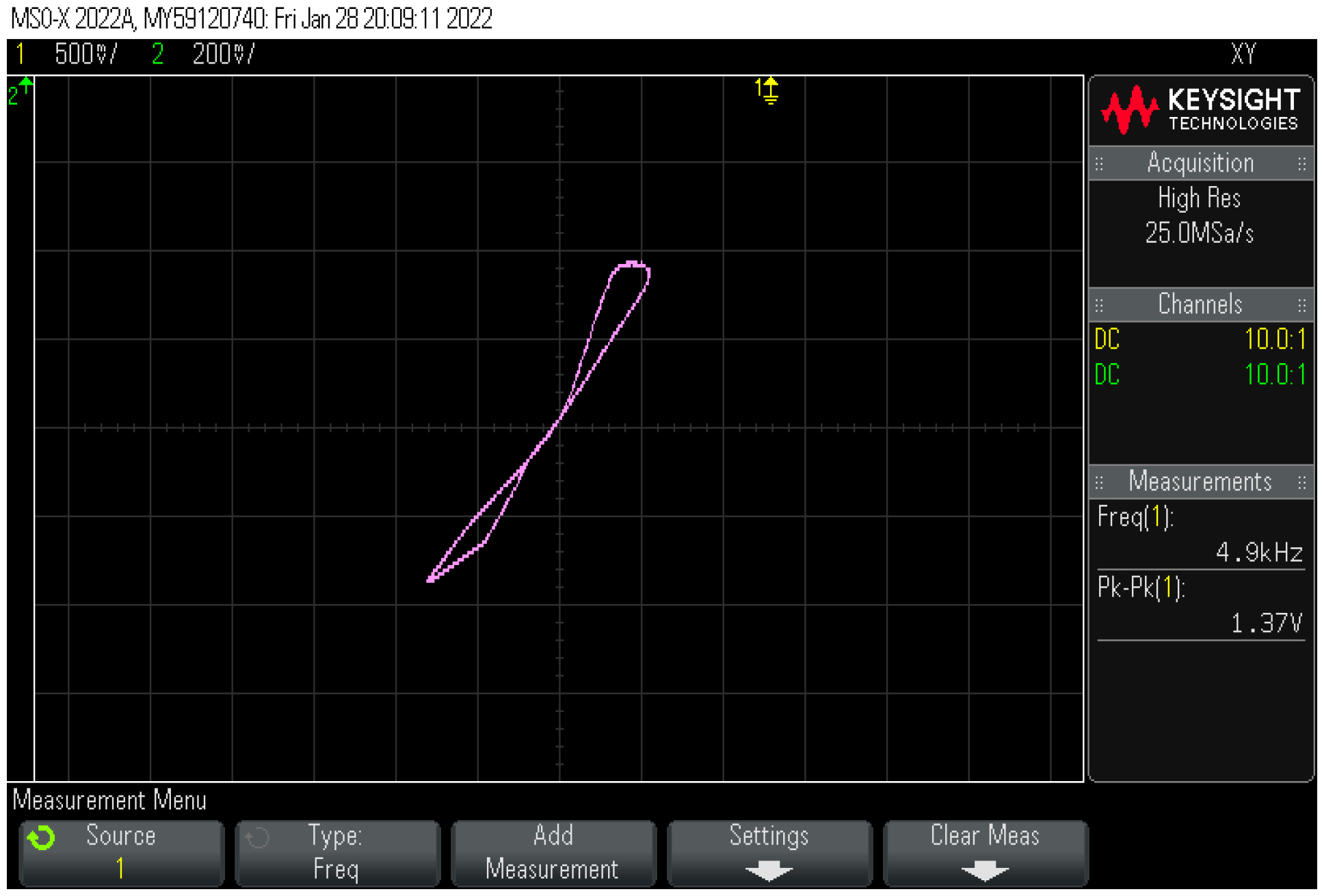

5. Experimental Results

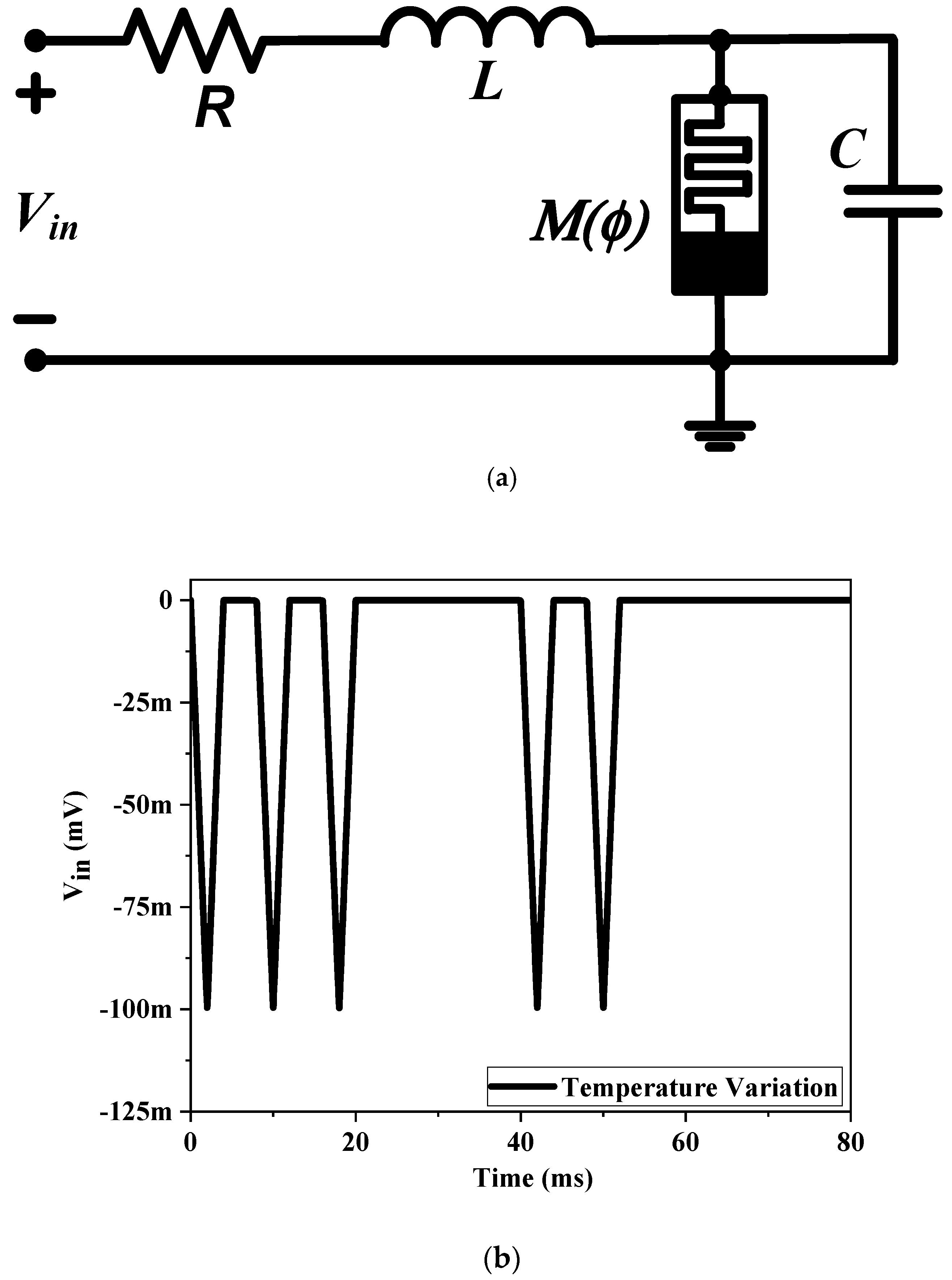

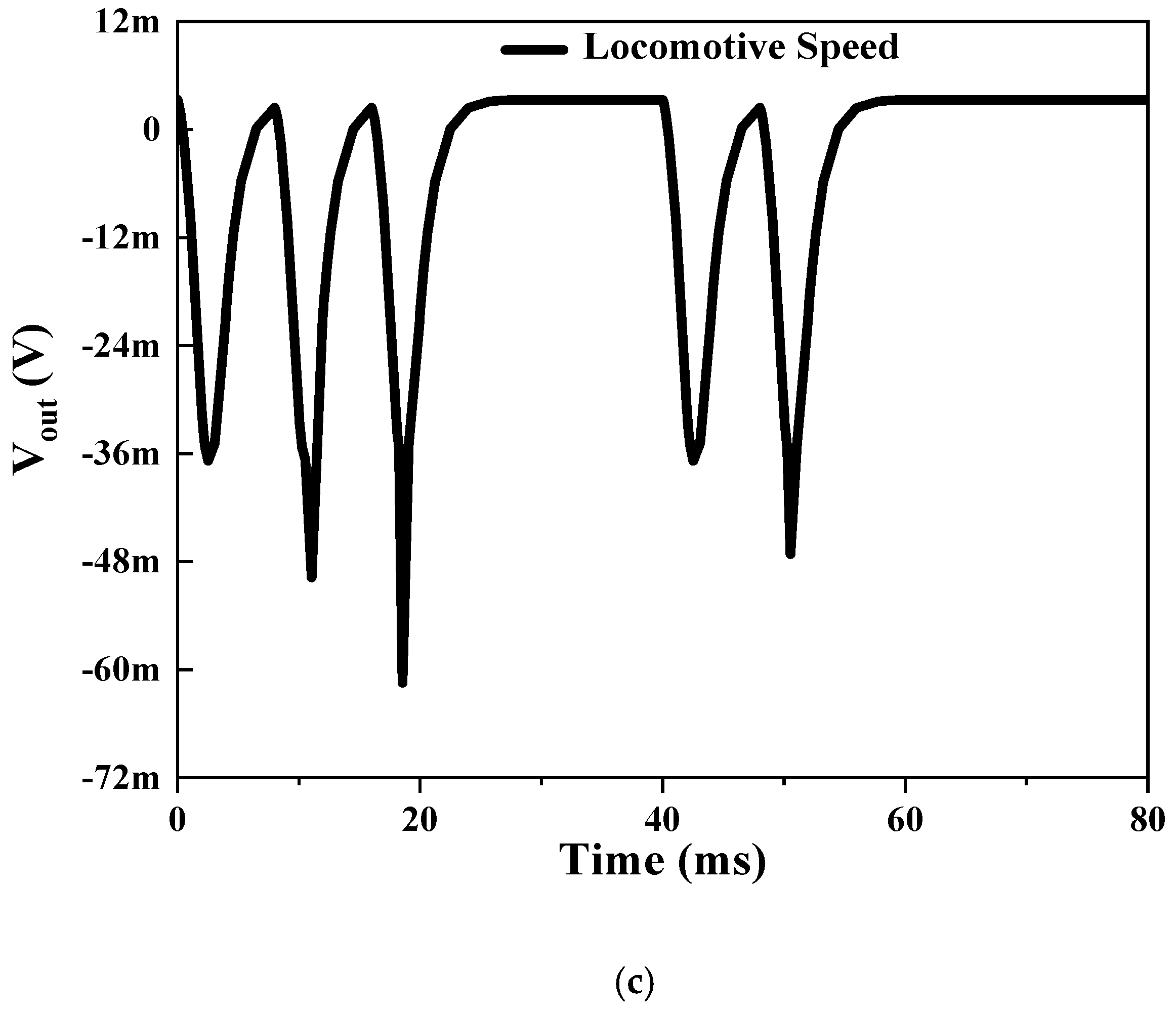

6. Application

7. Summary

Author Contributions

Funding

Conflicts of Interest

References

- Chua, L. Memristor-the missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Ajayan, J.; Nirmal, D.; Jebalin, B.K.; Sreejith, S. Advances in neuromorphic devices for the hardware implementation of neuromorphic computing systems for future artificial intelligence applications: A critical review. Microelectron. Eng. 2022, 105634. [Google Scholar] [CrossRef]

- Liang, H.N.; Bai, N.; Zou, L.Q.; Sun, H.J.; Xue, K.H.; Cheng, W.M.; Lu, H.; Miao, X.S. Resistive Switching Characteristics of HfO x-Based Memristor by Inserting GeTe Layer. IEEE Trans. Electron. Devices 2022, 70, 83–87. [Google Scholar] [CrossRef]

- Sozen, H.; Cam, U. First-order memristor–capacitor filter circuits employing hp memristor. J. Circuits Syst. Comput. 2014, 23, 1450116. [Google Scholar] [CrossRef]

- Pershin, Y.V.; Di Ventra, M. Practical approach to programmable analog circuits with memristors. IEEE Trans. Circuits Syst. I: Regul. Pap. 2010, 57, 1857–1864. [Google Scholar] [CrossRef]

- Muthuswamy, B. Implementing memristor based chaotic circuits. Int. J. Bifurcat Chaos 2010, 20, 1335–1350. [Google Scholar] [CrossRef]

- Pershin, Y.V.; Sazonov, E.; Di Ventra, M. Analogue-to-digital and digital-to-analogue conversion with memristive devices. Electron. Lett. 2012, 48, 73–74. [Google Scholar] [CrossRef]

- Sánchez-López, C.; Aguila-Cuapio, L.E. A 860 kHz grounded memristor emulator circuit. AEU-Int. J. Electron Commun. 2017, 73, 23–33. [Google Scholar] [CrossRef]

- Sharma, P.K.; Ranjan, R.K.; Khateb, F.; Kumngern, M. Charged controlled mem-element emulator and its application in a chaotic system. IEEE Access 2020, 8, 171397–171407. [Google Scholar] [CrossRef]

- Ranjan, R.K.; Sharma, P.K.; Sagar; Raj, N.; Kumari, B.; Khateb, F. Memristor emulator circuit using multiple-output OTA and its experimental results. J. Circuits Syst. Comput. 2019, 28, 1950166. [Google Scholar] [CrossRef]

- Babacan, Y.; Yesil, A.; Kacar, F. Memristor emulator with tunable characteristic and its experimental results. AEU-Int. J. Electron. Commun. 2017, 81, 99–104. [Google Scholar] [CrossRef]

- Kanyal, G.; Kumar, P.; Paul, S.K.; Kumar, A. OTA based high frequency tunable resistorless grounded and floating memristor emulators. AEU-Int. J. Electron. Commun. 2018, 92, 124–145. [Google Scholar] [CrossRef]

- Yesil, A.; Babacan, Y.; Kacar, F. Electronically tunable memristor based on VDCC. AEU-Int. J. Electron. Commun. 2019, 107, 282–290. [Google Scholar] [CrossRef]

- Ayten, U.E.; Minaei, S.; Sağbaş, M. Memristor emulator circuits using single CBTA. AEU-Int. J. Electron. Commun. 2017, 82, 109–118. [Google Scholar] [CrossRef]

- Ranjan, R.K.; Rani, N.; Pal, R.; Paul, S.K.; Kanyal, G. Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectron. Eng. 2017, 60, 119–128. [Google Scholar] [CrossRef]

- Yadav, N.; Rai, S.K.; Pandey, R. Novel memristor emulators using fully balanced VDBA and grounded capacitor. Iran. J. Sci. Technol. - Trans. Electr. Eng. 2021, 45, 229–245. [Google Scholar] [CrossRef]

- Yeşil, A.; Babacan, Y.; Kaçar, F. Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2018, 38, 1123–1132. [Google Scholar] [CrossRef]

- Vista, J.; Ranjan, A. Flux controlled floating memristor employing VDTA: Incremental or decremental operation. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2020, 40, 364–372. [Google Scholar] [CrossRef]

- Gupta, S.; Rai, S.K. New grounded and floating decremental/incremental memristor emulators based on CDTA and its application. Wirel. Pers. Commun. 2020, 113, 773–798. [Google Scholar] [CrossRef]

- Ranjan, R.K.; Raj, N.; Bhuwal, N.; Khateb, F. Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU-Int. J. Electron. Commun. 2017, 82, 177–190. [Google Scholar] [CrossRef]

- Prasad, S.S.; Kumar, P.; Ranjan, R.K. Resistorless memristor emulator using CFTA and its experimental verification. IEEE Access 2021, 9, 64065–64075. [Google Scholar] [CrossRef]

- Raj, N.; Ranjan, R.K.; Khateb, F. Flux-controlled memristor emulator and its experimental results. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2020, 28, 1050–1061. [Google Scholar] [CrossRef]

- Yadav, N.; Rai, S.K.; Pandey, R. New grounded and floating memristor emulators using OTA and CDBA. Int. J. Circuit Theory Appl. 2020, 48, 1154–1179. [Google Scholar] [CrossRef]

- Yesil, A.; Babacan, Y.; Kacar, F. An electronically controllable, fully floating memristor based on active elements: DO-OTA and DVCC. AEU-Int. J. Electron. Commun. 2020, 123, 153315. [Google Scholar] [CrossRef]

- Bhardwaj, K.; Srivastava, M. New Multiplier-Less Compact Tunable Charge-Controlled Memelement Emulator Using Grounded Passive Elements. Circuits Syst. Signal Process. 2021, 41, 2429–2465. [Google Scholar] [CrossRef]

- Vista, J.; Ranjan, A. A simple floating MOS-memristor for high-frequency applications. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2019, 27, 1186–1195. [Google Scholar] [CrossRef]

- Yildiz, H.A.; Ozoguz, S. MOS-only implementation of memristor emulator circuit. AEU-Int. J. Electron. Commun. 2021, 141, 153975. [Google Scholar] [CrossRef]

- Sharma, P.K.; Prasad, S.S.; Tasneem, S.; Priyadarshini, B.; Ranjan, R.K. Resistive Tunable Memristor Emulator Model and its Application. AEU-Int. J. Electron. Commun. 2022, 160, 154500. [Google Scholar] [CrossRef]

- Bhardwaj, K.; Srivastava, M. New Electronically/Resistively Tunable Floating Emulators to Realize Memristor and Inverse Memristor. 2021. Available online: https://assets.researchsquare.com/files/rs-594531/v1_covered.pdf?c=1631872158 (accessed on 9 January 2023).

- Prasad, S.S.; Kumar, P.; Raj, N.; Sharma, P.K.; Priyadarshini, B.; Ranjan, R.K.; Prommee, P. A compact floating and grounded memristor model using single active element. AEU-Int. J. Electron. Commun. 2022, 157, 154426. [Google Scholar] [CrossRef]

- Petrović, P.B. A Universal Electronically Controllable Memelement Emulator Based on VDCC with Variable Configuration. Electronics 2022, 11, 3957. [Google Scholar] [CrossRef]

| Ref. & Year | Active Components | Power Supply (V) | No. of MOS | Passive Comp. (R, C) | Operating Freq. (Hz) | I/D * | Exp. Results | Tech. Used | Power Dissipation (W) |

|---|---|---|---|---|---|---|---|---|---|

| [9] 2017 | 1 CCII, 1 Multiplier | ±10 | - | 1, 1 | 860 k | - | Yes | BJT | -- |

| [12] 2017 | 1 MO-OTA, 1 Multiplier | ±1.25/±5 | >38 | 1, 1 | 1 k | - | Yes | CMOS/BJT | -- |

| [13] 2018 | 2 OTA | ±1.2 | 34 | 0, 1 | 8 M | Both | Yes | CMOS | -- |

| [14] 2019 | 1 VDCC, 2 Transistors | ±0.9 | 26 | 0, 1 | 2 M | Both | Yes | CMOS | -- |

| [15] 2017 | 1 CBTA, 1 Multiplier | ±0.9 | 23 | 2, 1 | 460 k | - | No | CMOS | -- |

| [17] 2021 | 1 FB-VDBA | ±0.9 | 19 | 0, 1 | 1 M | Both | No | CMOS | -- |

| [18] 2018 | 1 VDTA | ±0.9 | 16 | 0, 1 | 50 M | Both | Yes | CMOS | -- |

| [19] 2020 | 1 VDTA | ±0.9 | 16 | 1, 1 | 50 M | Both | Yes | CMOS | 8 µ |

| [20] 2020 | 1 CDTA, 1 OTA | ±0.9 | 36 | 0, 1 | 2 M | Both | No | CMOS | -- |

| [22] 2021 | 1 CFTA | ±1.2 | 28 | 0, 1 | 9 M | Both | Yes | CMOS | -- |

| [23] 2020 | 1 CCII, 1 OTA | ±1.2 | 24 | 1, 1 | 25.3 M | Both | Yes | CMOS | 9.56 m |

| [24] 2020 | 1 CDBA, 1 OTA | ±0.9 | 27 | 0, 1 | 1 M | Both | No | CMOS | -- |

| [25] 2020 | 1 DO-OTA, 1 DVCC, 2 Transistors | ±0.9 | 29 | 0, 1 | 1.5 M | I | Yes | CMOS | -- |

| [26] 2021 | 1 VDCC, 1 OTA | -- | 35 | 2, 1 | 1 M | I | Yes | CMOS | -- |

| [29] 2022 | 1 DVCC, 1 OTA | ±0.9 | 23 | 1, 1 | 30 M | Both | Yes | CMOS | 591 µ |

| [30] 2021 | 2 MVDCC | ±0.9 | 52 | 2, 1 | 500 k | I | Yes | CMOS | -- |

| [31] 2022 | 1 DVCCTA | ±1 | 27 | 2, 1 | 12.8 M | Both | Yes | CMOS | 8.74 m |

| [32] 2022 | 1 VDCC, 2 MOS | ±0.9 | 24 | 0, 1 | 10 M | Both | No | CMOS | -- |

| [32] 2022 | 2 VDCC, 2 MOS | ±0.9 | 46 | 0, 1 | 50 M | Both | No | CMOS | -- |

| Proposed Design | 1 DVCC, 3 Transistors | ±1.25 | 15 | 0, 1 | 100 M | Both | Yes | CMOS | 7.64 µ |

| MOSFET | W (in µm) | L (in nm) |

|---|---|---|

| M1–M4 | 5 | 360 |

| M5–M6, M11–M12 | 4 | 360 |

| M7–M9, M15 | 10 | 360 |

| M13–M14 | 20 | 360 |

| M10 | 9 | 360 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tasneem, S.; Kumar Sharma, P.; Kumar Ranjan, R.; Khateb, F. Electronically Tunable Memristor Emulator Implemented Using a Single Active Element and Its Application in Adaptive Learning. Sensors 2023, 23, 1620. https://doi.org/10.3390/s23031620

Tasneem S, Kumar Sharma P, Kumar Ranjan R, Khateb F. Electronically Tunable Memristor Emulator Implemented Using a Single Active Element and Its Application in Adaptive Learning. Sensors. 2023; 23(3):1620. https://doi.org/10.3390/s23031620

Chicago/Turabian StyleTasneem, Sadaf, Pankaj Kumar Sharma, Rajeev Kumar Ranjan, and Fabian Khateb. 2023. "Electronically Tunable Memristor Emulator Implemented Using a Single Active Element and Its Application in Adaptive Learning" Sensors 23, no. 3: 1620. https://doi.org/10.3390/s23031620

APA StyleTasneem, S., Kumar Sharma, P., Kumar Ranjan, R., & Khateb, F. (2023). Electronically Tunable Memristor Emulator Implemented Using a Single Active Element and Its Application in Adaptive Learning. Sensors, 23(3), 1620. https://doi.org/10.3390/s23031620