Design of a CMOS Image Sensor with Bi-Directional Gamma-Corrected Digital-Correlated Double Sampling

Abstract

:1. Introduction

2. Proposed CIS Structure

2.1. Correlated Double Sampling (CDS)

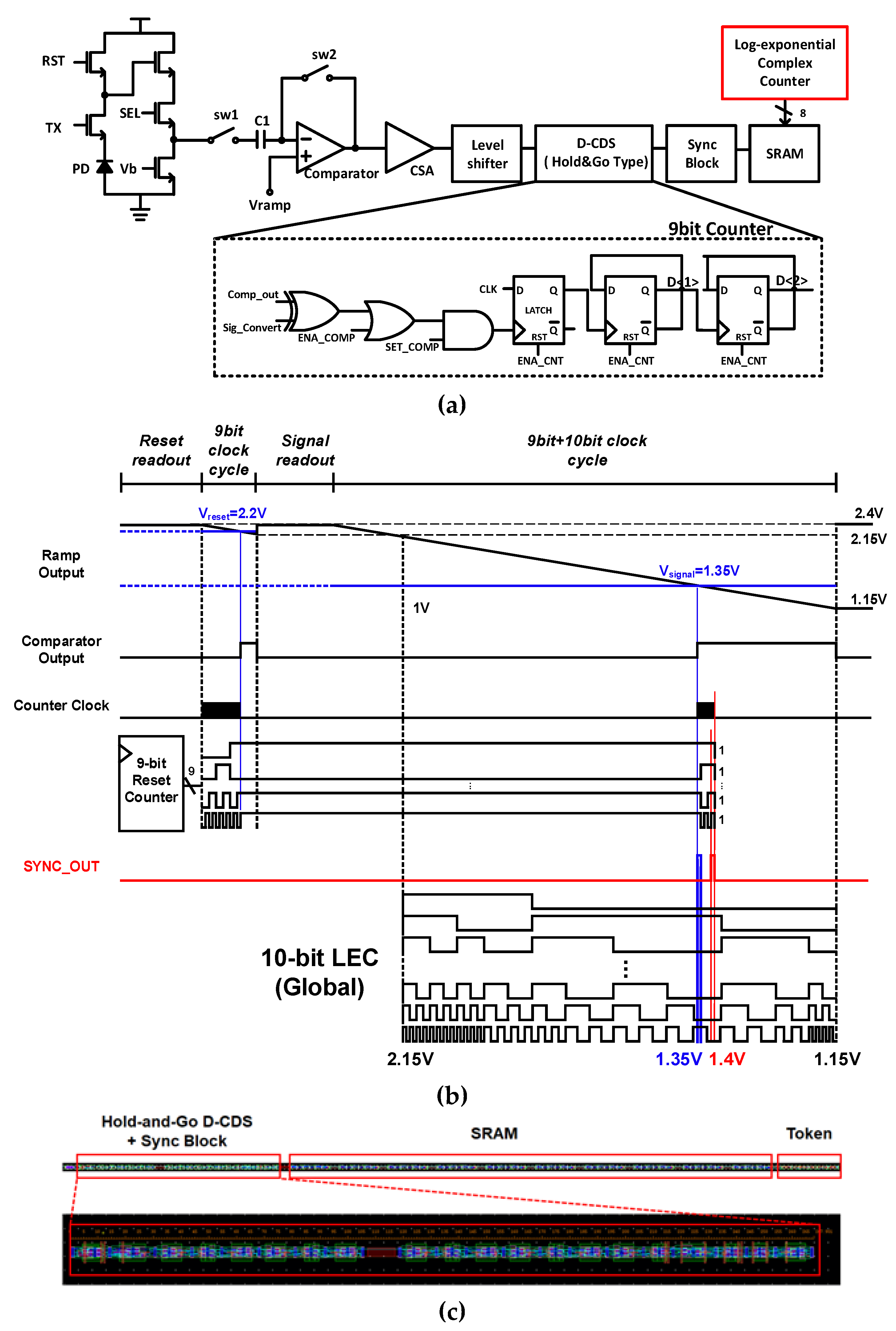

2.2. D-CDS Operation Using Hold-and-Go Counter Structure

2.3. Log-Exponential Counter

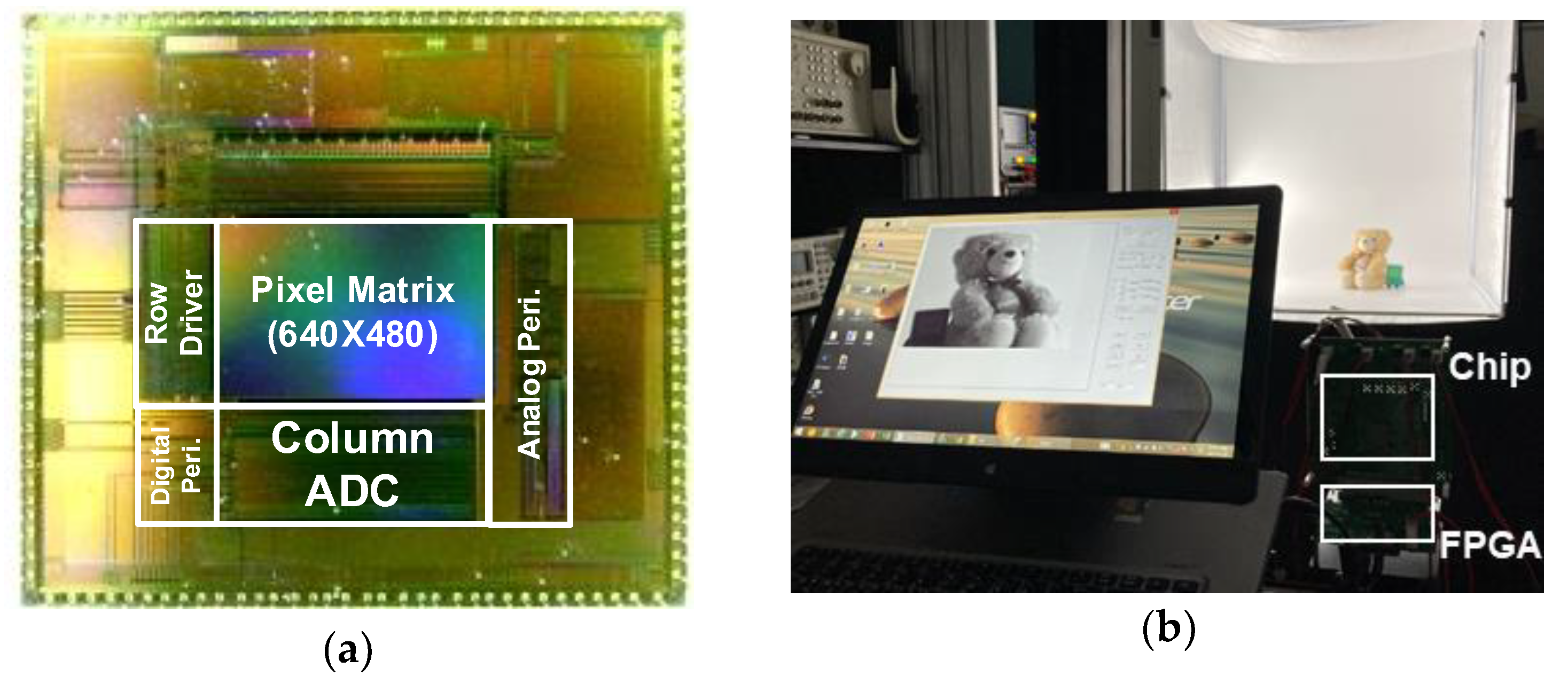

3. Experiment Results

3.1. Modified-Absolute Mean Brightness Error

3.2. Signal-to-Noise Ratio

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Huang, Z.; Zhang, X.; Chen, L.; Zhu, Y.; An, F.; Wang, H.; Feng, S. A Vector-Quantization Compression Circuit with On-Chip Learning Ability for High-Speed Image Sensor. IEEE Access 2017, 5, 22132–22143. [Google Scholar] [CrossRef]

- Bae, M.; Choi, B.S.; Jo, S.H.; Lee, H.H.; Choi, P.; Shin, J.K. A Linear-Logarithmic CMOS Image Sensor with Adjustable Dynamic Range. IEEE Sens. J. 2016, 16, 5222–5226. [Google Scholar] [CrossRef]

- Lee, S.; Yang, K. High dynamic-range CMOS image sensor cell based on self-adaptive photosensing operation. IEEE Trans. Electron Devices 2006, 53, 1733–1735. [Google Scholar] [CrossRef]

- Shaharom, M.; Collins, S. An integrating wide dynamic range nMOS pixel with a logarithmic reference voltage generator. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 1918–1921. [Google Scholar] [CrossRef]

- Acosta-Serafini, P.; Masaki, I.; Sodini, C. A 1/3” VGA linear wide dynamic range CMOS image sensor implementing a predictive multiple sampling algorithm with overlapping integration intervals. IEEE J. Solid-State Circuits 2004, 39, 1487–1496. [Google Scholar] [CrossRef]

- Ham, S.; Lee, Y.; Jung, W.; Lim, S.; Yoo, K.; Chae, Y.; Han, G. CMOS image sensor with analog gamma correction using nonlinear single-slope ADC. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems, Kos, Greece, 21–24 May 2006; pp. 3578–3581. [Google Scholar] [CrossRef]

- Priyadarshini, N.; Sarkar, M. A High Dynamic Range CMOS Image Sensor using Programmable Linear-Logarithmic Counter for Low Light Imaging Applications. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Kim, D.; Song, M. An Enhanced Dynamic-Range CMOS Image Sensor Using a Digital Logarithmic Single-Slope ADC. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 653–657. [Google Scholar] [CrossRef]

- Im, H.; Park, K.; Cho, J.H.; Choo, H.S.; Kim, S.Y. Design of a Pseudo-Wide Dynamic Range CMOS Image Sensor by Using the Bidirectional Gamma Curvature Technique. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 1596–1599. [Google Scholar] [CrossRef]

- Baek, C.; Lim, C.; Kim, D.; Song, M. Design of a 10-bit CMOS image sensor based on an 8-bit configurable hold-and-go counter. In Proceedings of the 2012 ESSCIRC (ESSCIRC), Bordeaux, France, 17–21 September 2012; pp. 393–397. [Google Scholar] [CrossRef]

- Park, K.; Yeom, S.; Kim, S.Y. Ultra-Low Power CMOS Image Sensor With Two-Step Logical Shift Algorithm-Based Correlated Double Sampling Scheme. IEEE Trans. Circuits Syst. Regul. Pap. 2020, 67, 3718–3727. [Google Scholar] [CrossRef]

- Huang, S.C.; Cheng, F.C.; Chiu, Y.S. Efficient Contrast Enhancement Using Adaptive Gamma Correction with Weighting Distribution. IEEE Trans. Image Process. 2013, 22, 1032–1041. [Google Scholar] [CrossRef] [PubMed]

- Park, I.; Jo, W.; Park, C.; Park, B.; Cheon, J.; Chae, Y. A 640 × 640 Fully Dynamic CMOS Image Sensor for Always-On Operation. IEEE J. Solid-state Circuits 2020, 55, 898–907. [Google Scholar] [CrossRef]

| DN @8 lux | Linear | ¾ Point B-Gamma | ½ Point B-Gamma | ¼ Point B-Gamma | Avg. B-Gamma |

|---|---|---|---|---|---|

| 3.6 | 11.49 | 12.79 | 12.23 | 12.74 | 12.69 |

| 10.1 | 18.72 | 19.19 | 19.19 | 19.27 | 19.22 |

| 19.3 | 22.44 | 22.73 | 22.75 | 22.51 | 22.66 |

| 23.6 | 23.58 | 23.81 | 23.82 | 23.79 | 23.81 |

| 27.5 | 24.38 | 24.58 | 24.64 | 24.60 | 24.61 |

| 36.9 | 25.90 | 26.08 | 26.03 | 25.60 | 25.90 |

| 44.3 | 26.70 | 27.06 | 26.81 | 26.47 | 26.78 |

| 54.8 | 27.70 | 27.87 | 27.83 | 27.48 | 27.73 |

| [7] | [8] | [9] | This Work | |

|---|---|---|---|---|

| Types of CDS | A-CDS | A-CDS | A-CDS | D-CDS |

| Technology [μm] | 0.35 | 0.35 | 0.11 | 0.11 |

| Power Dissipation [mW] | N/A | 30 | 6 | 6.3 |

| Frame Rate | N/A | 15 fps | 15 fps | 16.6 fps |

| Pixel Size [μm2] | 9 9 | 5.6 5.6 | 3.2 3.2 | 3.2 3.2 |

| Random noise [μVrms] | N/A | N/A | - | 392 (1)(2) |

| Pixel Array | 128 × 128 | 320 × 240 (QVGA) | 640 × 480 (VGA) | 640 × 480 (VGA) |

| Dynamic range [dB] | 89 | 64.8 | 61.5 | 61.5 |

| ADC Resolution [bit] | 8 | 10 | 8 | 10 |

| FoM [ | N/A | N/A | - | 472 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cho, J.; Choo, H.; Lee, S.; Yoon, S.; Kam, G.; Kim, S. Design of a CMOS Image Sensor with Bi-Directional Gamma-Corrected Digital-Correlated Double Sampling. Sensors 2023, 23, 1031. https://doi.org/10.3390/s23021031

Cho J, Choo H, Lee S, Yoon S, Kam G, Kim S. Design of a CMOS Image Sensor with Bi-Directional Gamma-Corrected Digital-Correlated Double Sampling. Sensors. 2023; 23(2):1031. https://doi.org/10.3390/s23021031

Chicago/Turabian StyleCho, Jaehee, Hyunseon Choo, Suhyeon Lee, Seungju Yoon, Gyuwon Kam, and Sooyoun Kim. 2023. "Design of a CMOS Image Sensor with Bi-Directional Gamma-Corrected Digital-Correlated Double Sampling" Sensors 23, no. 2: 1031. https://doi.org/10.3390/s23021031

APA StyleCho, J., Choo, H., Lee, S., Yoon, S., Kam, G., & Kim, S. (2023). Design of a CMOS Image Sensor with Bi-Directional Gamma-Corrected Digital-Correlated Double Sampling. Sensors, 23(2), 1031. https://doi.org/10.3390/s23021031