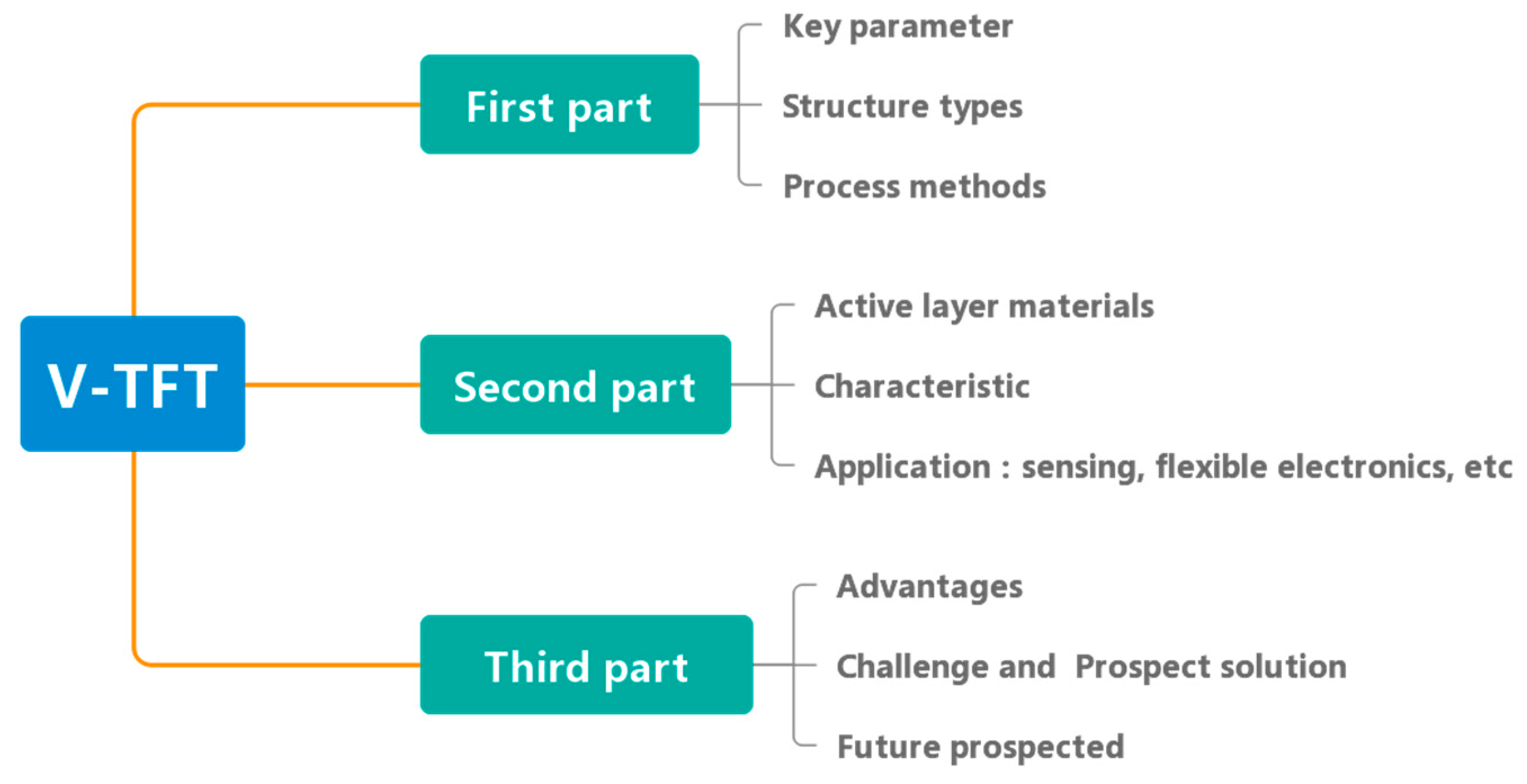

Research Progress of Vertical Channel Thin Film Transistor Device

Abstract

:1. Introduction

2. V-TFT Device Key Parameters

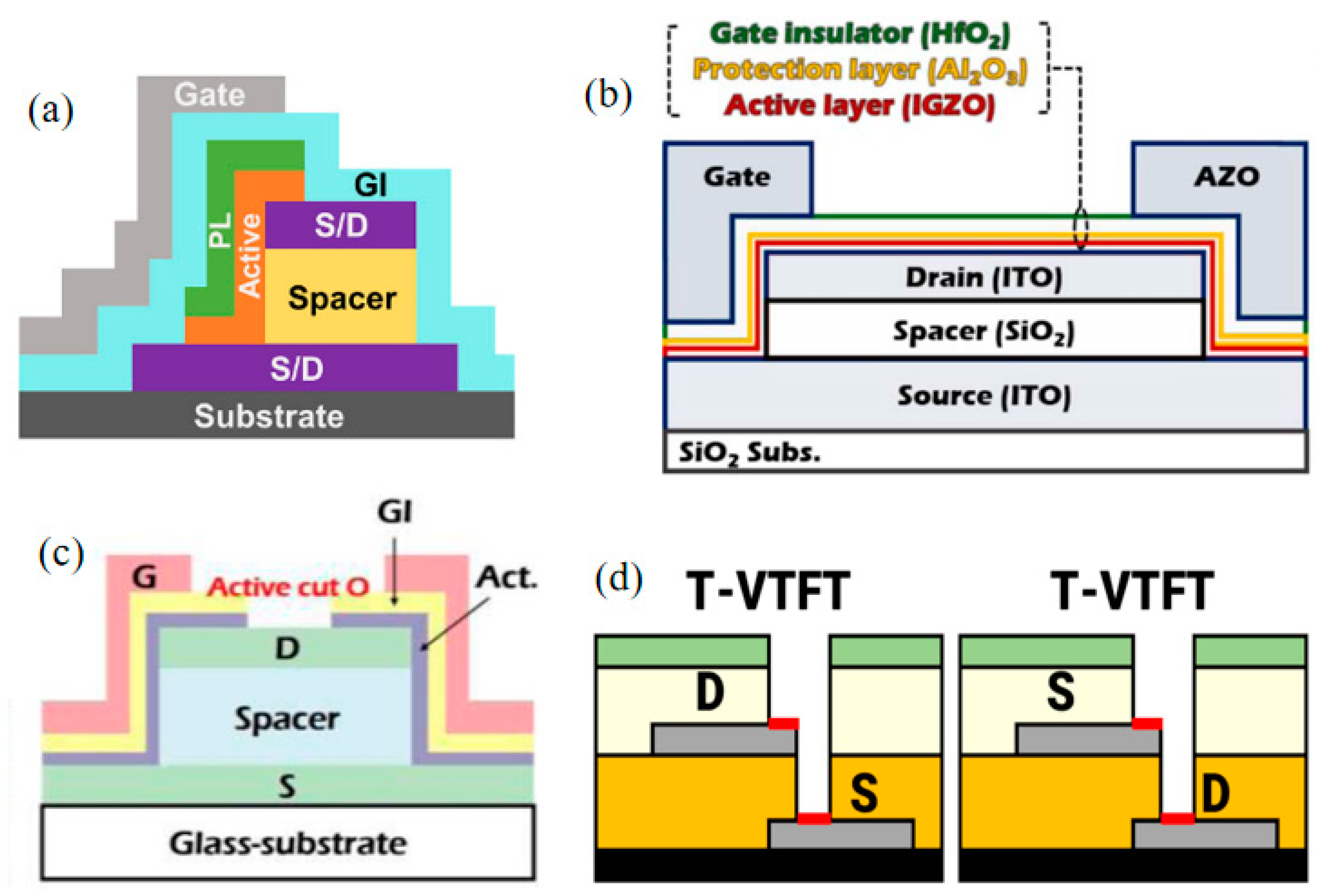

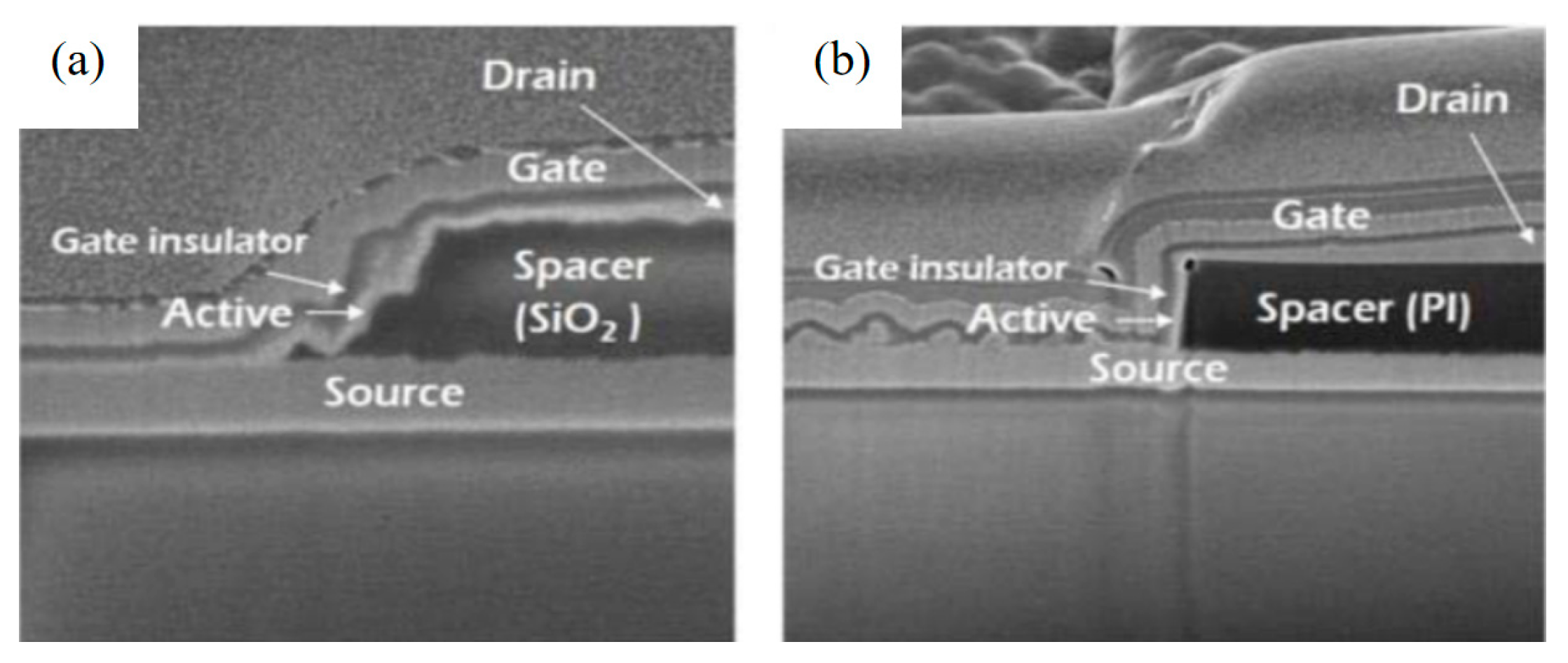

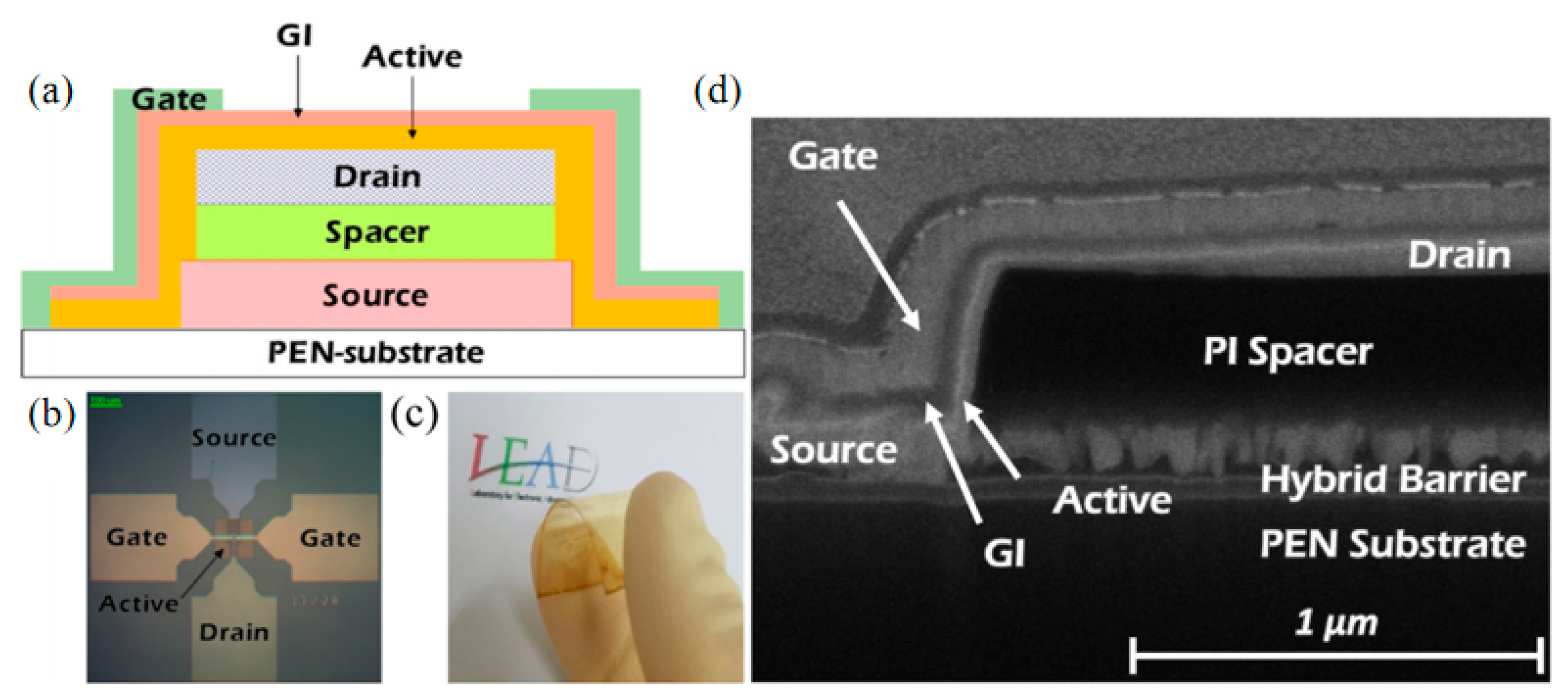

3. The Structure of V-TFT Devices

4. V-TFT Preparation Process and Spacer Material Selection

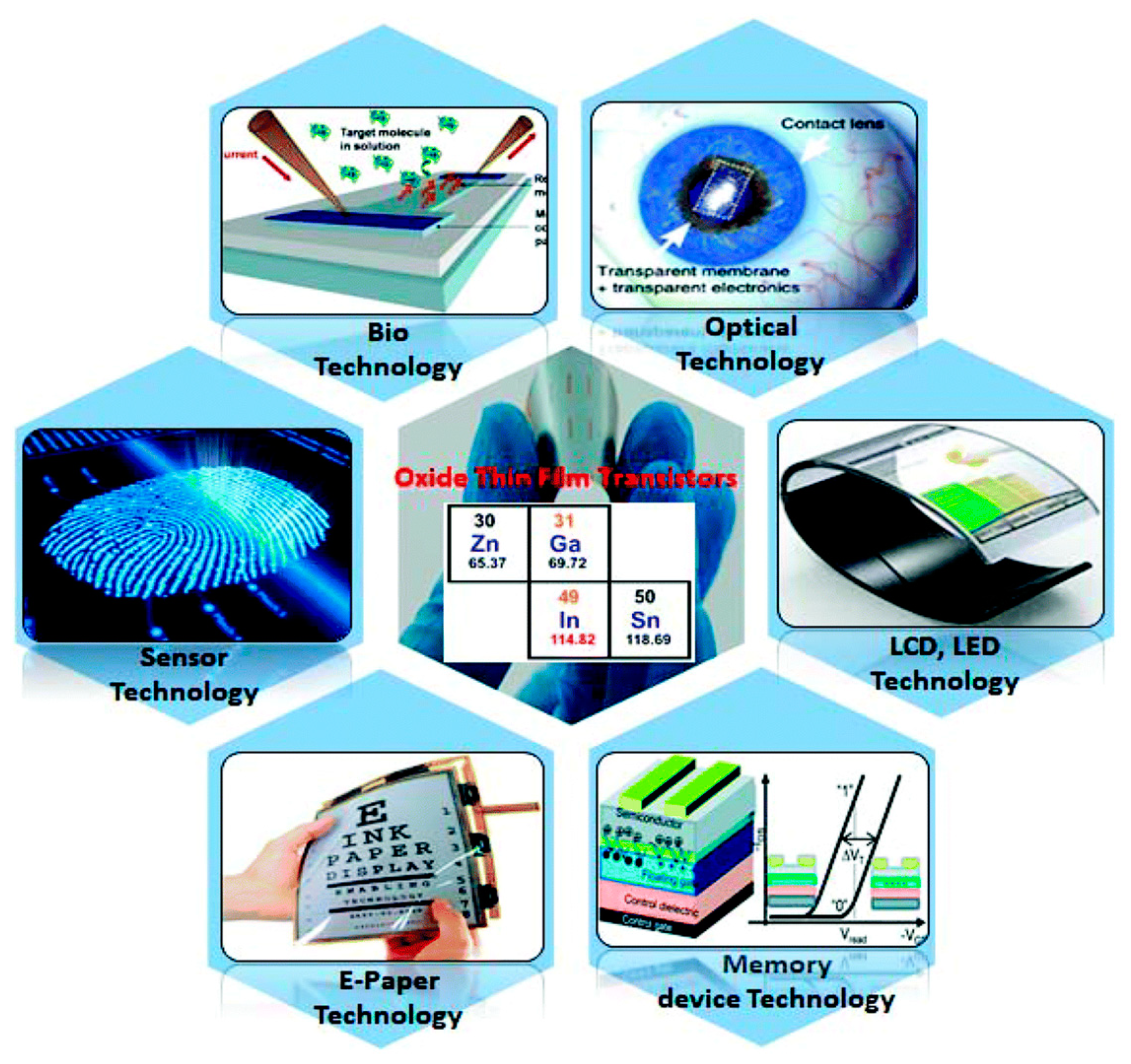

5. The Development of V-TFT Active Layer Materials

5.1. a-Si as V-TFT Active Layer

5.2. Low Temperature Polycrystalline Silicon as V-TFT Active Layer

5.3. AOS and Other Materials as V-TFT Active Layers

6. The Advantages and Practical Applications of V-TFT

- (1)

- V-TFT structures are independent of the requirements of high-precision photolithography, precise control of the channel length by adjusting the thickness of the deposited film (spacer layer) allows easy access to sub-1 μm channel lengths. Independent of high-precision photolithography requirements, it will reduce significant costs.

- (2)

- The shortening of the V-TFT channel length, which enables the requirement for a high-resolution TFT display and an increase in the corresponding pixel density. Higher package densities are obtained, and their integration is increased.

- (3)

- The reduction of the V-TFT channel length enables the TFT width-to-length ratio W/L to increase, achieves lower power consumption, allows control of high currents at low voltages, and greater on-state currents under the same conditions.

- (4)

- The channel structure of the V-TFT is on a vertical sidewall, and when the device itself is bent and stretched by the flexible substrate, the device will not be much affected by the bending of the substrate because the channel direction is perpendicular to the substrate. This will enable us to meet the needs of today’s society in terms of ultra-high-resolution displays and flexible displays.

| Device Type | Channel Aspects | Physics Aspects | Structure Aspects |

|---|---|---|---|

| Planar TFT | Lithography equipment limitations make it difficult to achieve sub-micron channel length | Difficulty in obtaining high current at low voltage, challenge in improving packaging density | The structure itself is greatly affected by bending |

| Vertical TFT | Independent from high precision photolithography requirements and easy access to sub-micron channel length | Smaller size, high-resolution, low power consumption, higher integration | Channel direction is perpendicular to the substrate, not affected by the bending of the substrate |

7. Huge Potential for V-TFT Applications in Sensing and Other Areas

- (1)

- V-TFT-based sensors are expected to have high sensitivity and high responsiveness. Because the V-TFT channel length is shorter compared to conventional TFT channels, the carrier transfer rate becomes faster under the same conditions, a characteristic that makes V-TFT-based sensors much more sensitive and responsive than planar TFT sensors under the same conditions.

- (2)

- Since one of the advantages of V-TFT over conventional TFT is the small footprint, V-TFT-based sensors can offer unique advantages in higher resolution applications. In chemical sensors, this means being able to sense and measure changes in the concentration of target molecules in greater detail. The high resolution and precision provides more accurate analytical results and increases the sensitivity and reliability of the chemical sensor.

- (3)

- Now, it has been reported that the V-TFT has a low leakage current [56]. In sensor applications, this also means that small current changes or signals can be measured more accurately, improving the sensitivity and accuracy of the sensor.

8. Challenges and Prospects

- (1)

- During the etching process, the vertical sidewalls have a rough surface with the unavoidable introduction of impurities, which in turn causes higher off-state currents.

- (2)

- The reduced channel size of V-TFT devices will bring about the problem of the short-channel effect. To effectively suppress the short-channel effect, the thickness of the gate insulator layer needs to be reduced. The reduced in gate insulator thickness will inevitably lead to an increase in gate leakage current.

9. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Choi, J.H.; Yang, J.H.; Pi, J.E.; Hwang, C.Y.; Kim, Y.H.; Kim, G.H.; Kim, H.O.; Hwang, C.S. The new route for realization of 1-μm-pixel-pitch high-resolution displays. J. Soc. Inf. Disp. 2019, 27, 487–496. [Google Scholar] [CrossRef] [Green Version]

- Ohara, M.; Kohda, T.; Furuichi, S.; Nakada, T.; Kawase, K.; Kohda, Y.; Ishikawa, T.; Sumiyoshi, K.; Funakoshi, A. 13.2: Invited Paper: Recent Progress and Future Trend of Ultra-High-Resolution Large-Sized TFT-LCD Monitor Electronics. SID Symp. Dig. Tech. Pap. 2002, 33, 168–171. [Google Scholar] [CrossRef]

- Kaya, S.; Schmidl, D.; Schmetterer, L.; Witkowska, K.J.; Unterhuber, A.; Aranha Dos Santos, V.; Baar, C.; Garhofer, G.; Werkmeister, R.M. Effect of hyaluronic acid on tear film thickness as assessed with ultra-high resolution optical coherence tomography. Acta Ophthalmol. 2015, 93, 439–443. [Google Scholar] [CrossRef] [PubMed]

- Komatsu, R.; Nakazato, R.; Sasaki, T.; Suzuki, A.; Senda, N.; Kawata, T.; Jimbo, Y.; Aoyama, T.; Ohno, N.; Kawashima, S.; et al. Repeatedly foldable AMOLED display. J. Soc. Inf. Disp. 2015, 23, 41–49. [Google Scholar] [CrossRef]

- Noda, M.; Kobayashi, N.; Katsuhara, M.; Yumoto, A.; Ushikura, S.; Yasuda, R.; Hirai, N.; Yukawa, G.; Yagi, I.; Nomoto, K.; et al. An OTFT-driven rollable OLED display. J. Soc. Inf. Disp. 2011, 19, 316–322. [Google Scholar] [CrossRef]

- Mizukami, M.; Hirohata, N.; Iseki, T.; Ohtawara, K.; Tada, T.; Yagyu, S.; Abe, T.; Suzuki, T.; Fujisaki, Y.; Inoue, Y.; et al. Flexible AM OLED panel driven by bottom-contact OTFTs. IEEE Electron Device Lett. 2006, 27, 249–251. [Google Scholar] [CrossRef]

- Jia, Y.; Liu, Z.; Wu, D.; Chen, J.; Meng, H. Mechanical simulation of foldable AMOLED panel with a module structure. Org. Electron. 2019, 65, 185–192. [Google Scholar] [CrossRef]

- Mizukami, M.; Cho, S.-I.; Watanabe, K.; Abiko, M.; Suzuri, Y.; Tokito, S.; Kido, J. Flexible Organic Light-Emitting Diode Displays Driven by Inkjet-Printed High-Mobility Organic Thin-Film Transistors. IEEE Electron Device Lett. 2018, 39, 39–42. [Google Scholar] [CrossRef]

- Mativenga, M.; Geng, D.; Kim, B.; Jang, J. Fully transparent and rollable electronics. ACS Appl. Mater. Interfaces 2015, 7, 1578–1585. [Google Scholar] [CrossRef]

- Jin, D.-U.; Kim, T.-W.; Koo, H.-W.; Stryakhilev, D.; Kim, H.-S.; Seo, S.-J.; Kim, M.-J.; Min, H.-K.; Chung, H.-K.; Kim, S.-S. 47.1: Invited Paper: Highly Robust Flexible AMOLED Display on Plastic Substrate with New Structure. SID Symp. Dig. Tech. Pap. 2010, 41, 703–705. [Google Scholar] [CrossRef]

- Jang, H.J.; Lee, J.Y.; Kwak, J.; Lee, D.; Park, J.-H.; Lee, B.; Noh, Y.Y. Progress of display performances: AR, VR, QLED, OLED, and TFT. J. Inf. Disp. 2019, 20, 1–8. [Google Scholar] [CrossRef] [Green Version]

- Peng, C.; Huang, H.; Xu, M.; Chen, L.; Li, X.; Zhang, J. A Simple Doping Process Achieved by Modifying the Passivation Layer for Self-Aligned Top-Gate In-Ga-Zn-O Thin-Film Transistors at 200 °C. Nanomaterials 2022, 12, 4021. [Google Scholar] [CrossRef] [PubMed]

- Peng, C.; Xu, M.; Chen, L.; Li, X.; Zhang, J. Improvement of properties of top-gate IGZO TFT by oxygen-rich ultrathin in situ ITO active layer. Jpn. J. Appl. Phys. 2022, 61, 070914. [Google Scholar] [CrossRef]

- Peng, C.; Yang, S.; Pan, C.; Li, X.; Zhang, J. Effect of Two-Step Annealing on High Stability of a-IGZO Thin-Film Transistor. IEEE Trans. Electron Devices 2020, 67, 4262–4268. [Google Scholar] [CrossRef]

- Rachmady, W.; Agrawal, A.; Sung, S.; Dewey, G.; Chouksey, S.; Chu-Kung, B.; Elbaz, G.; Fischer, P.; Huang, C.; Jun, K. 300 mm heterogeneous 3D integration of record performance layer transfer germanium PMOS with silicon NMOS for low power high performance logic applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 29.7.1–29.7.4. [Google Scholar]

- Han, J.-W.; Oh, J.S.; Meyyappan, M. Cofabrication of Vacuum Field Emission Transistor (VFET) and MOSFET. IEEE Trans. Nanotechnol. 2014, 13, 464–468. [Google Scholar] [CrossRef]

- Meindl, J.D. Beyond Moore’s Law: The interconnect era. Comput. Sci. Eng. 2003, 5, 20–24. [Google Scholar] [CrossRef]

- Shalf, J. The future of computing beyond Moore’s Law. Philos. Transact. A Math. Phys. Eng. Sci. 2020, 378, 20190061. [Google Scholar] [CrossRef] [Green Version]

- Xuejue, H.; Wen-Chin, L.; Charles, K.; Hisamoto, D.; Leland, C.; Kedzierski, J.; Anderson, E.; Takeuchi, H.; Yang-Kyu, C.; Asano, K.; et al. Sub 50-nm FinFET: PMOS. In Proceedings of the International Electron Devices Meeting 1999. Technical Digest (Cat. No.99CH36318), Washington, DC, USA, 5–8 December 1999; pp. 67–70. [Google Scholar]

- Hisamoto, D.; Lee, W.-C.; Kedzierski, J.; Anderson, E.; Takeuchi, H.; Asano, K.; King, T.-J.; Bokor, J.; Hu, C. A folded-channel MOSFET for deep-sub-tenth micron era. IEDM Tech. Dig. 1998, 1998, 1032–1034. [Google Scholar]

- Huang, K.; Duan, X.; Feng, J.; Sun, Y.; Lu, C.; Chen, C.; Jiao, G.; Lin, X.; Shao, J.; Yin, S.; et al. Vertical Channel-All-Around (CAA) IGZO FET under 50 nm CD with High Read Current of 32.8 μA/μm (Vth + 1 V), Well-performed Thermal Stability up to 120 °C for Low Latency, High-density 2T0C 3D DRAM Application. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022; pp. 296–297. [Google Scholar]

- Bai, Z.; Gong, T.; Duan, X.; Wang, J.; Xiao, K.; Geng, D.; Li, L. Low Frequency Noise of Channel-All-Around (CAA) InGaZnO Field Effect Transistors. IEEE Electron Device Lett. 2022, 43, 2117–2120. [Google Scholar] [CrossRef]

- Chen, Q.; Wang, L.; Duan, X.; Guo, J.; Wang, Z.; Huang, K.; Feng, J.; Sun, Y.; Jiao, G.; Jing, W.; et al. Investigation of Asymmetric Characteristics of Novel Vertical Channel-All-Around (CAA) In-Ga-Zn-O Field Effect Transistors. IEEE Electron Device Lett. 2022, 43, 894–897. [Google Scholar] [CrossRef]

- Bae, G.; Bae, D.-I.; Kang, M.; Hwang, S.; Kim, S.; Seo, B.; Kwon, T.; Lee, T.; Moon, C.; Choi, Y. 3nm GAA technology featuring multi-bridge-channel FET for low power and high performance applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 28.27.21–28.27.24. [Google Scholar]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In-Ga-Zn-O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef]

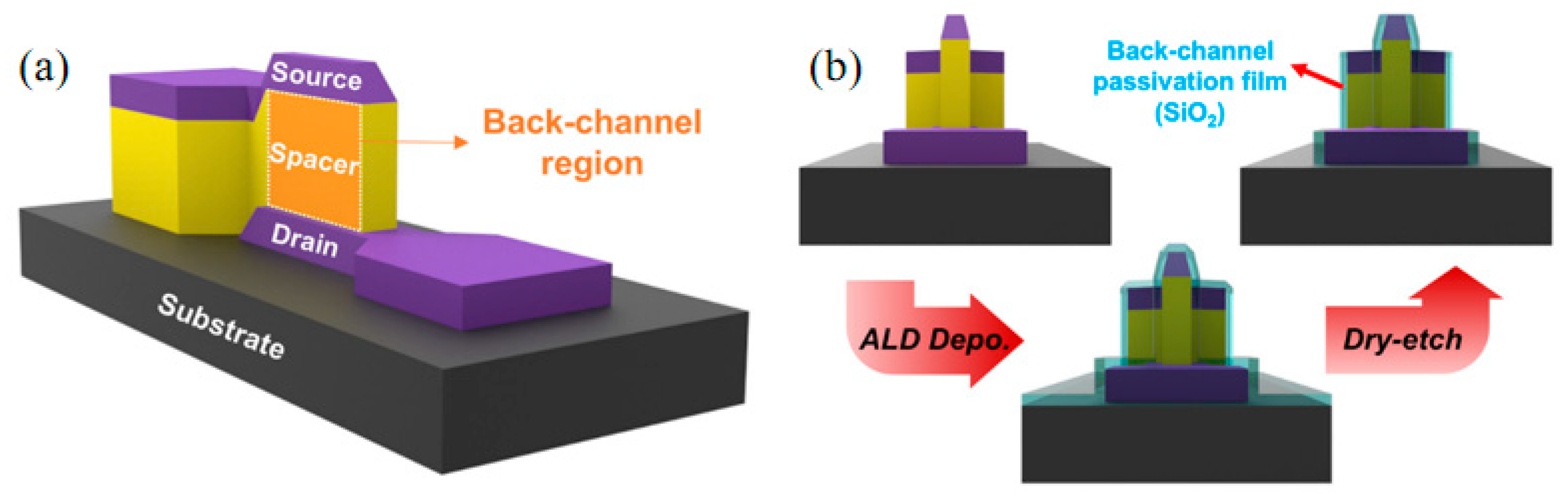

- Lee, K.-H.; Lee, S.H.; Cho, S.-J.; Hwang, C.-S.; Park, S.-H.K. Improving the electrical performance of vertical thin-film transistor by engineering its back-channel interface. Microelectron. Eng. 2022, 253, 111676. [Google Scholar] [CrossRef]

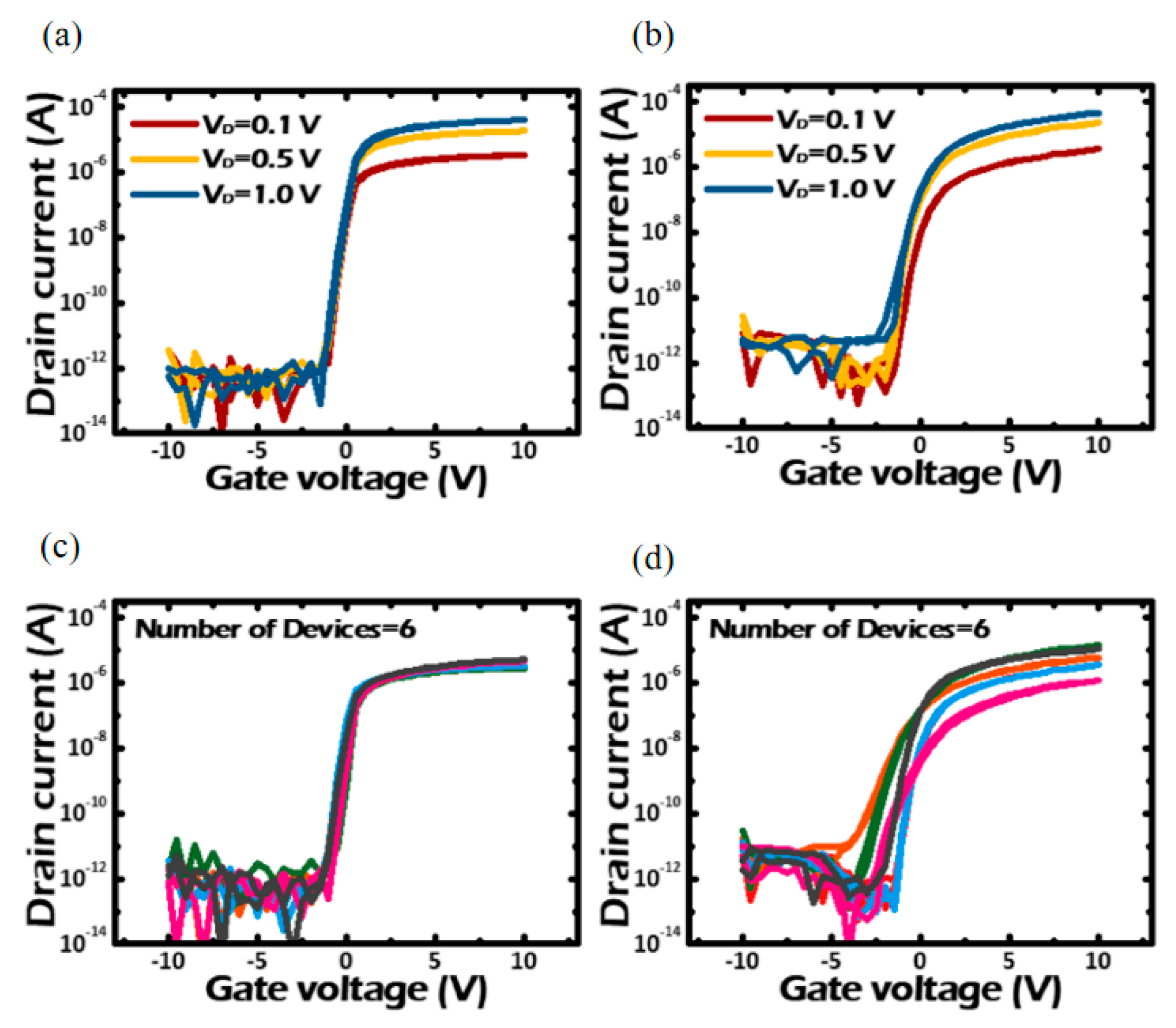

- Ryoo, H.-J.; Seong, N.-J.; Choi, K.-J.; Yoon, S.-M. Implementation of oxide vertical channel TFTs with sub-150 nm channel length using atomic-layer deposited IGZO active and HfO2 gate insulator. Nanotechnology 2021, 32, 255201. [Google Scholar] [CrossRef] [PubMed]

- Kim, Y.-M.; Kang, H.-B.; Kim, G.-H.; Hwang, C.-S.; Yoon, S.-M. Improvement in Device Performance of Vertical Thin-Film Transistors Using Atomic Layer Deposited IGZO Channel and Polyimide Spacer. IEEE Electron Device Lett. 2017, 38, 1387–1389. [Google Scholar] [CrossRef]

- Ahn, H.-M.; Moon, S.-H.; Kwon, Y.-H.; Seong, N.-J.; Choi, K.-J.; Hwang, C.-S.; Yang, J.-H.; Kim, Y.-H.; Yoon, S.-M. Geometrical and Structural Design Schemes for Trench-Shaped Vertical Channel Transistors Using Atomic-Layer Deposited In-Ga-Zn-O. IEEE Electron Device Lett. 2022, 43, 1909–1912. [Google Scholar] [CrossRef]

- Baek, Y.J.; Kang, I.H.; Hwang, S.H.; Han, Y.L.; Kang, M.S.; Kang, S.J.; Kim, S.G.; Woo, J.G.; Yu, E.S.; Bae, B.S. Vertical oxide thin-film transistor with interfacial oxidation. Sci. Rep. 2022, 12, 3094. [Google Scholar] [CrossRef]

- Saitoh, A.S.A.; Matsumura, M.M.M. Excimer-laser-produced amorphous-silicon vertical thin-film transistors. Jpn. J. Appl. Phys. 1997, 36, L668. [Google Scholar] [CrossRef]

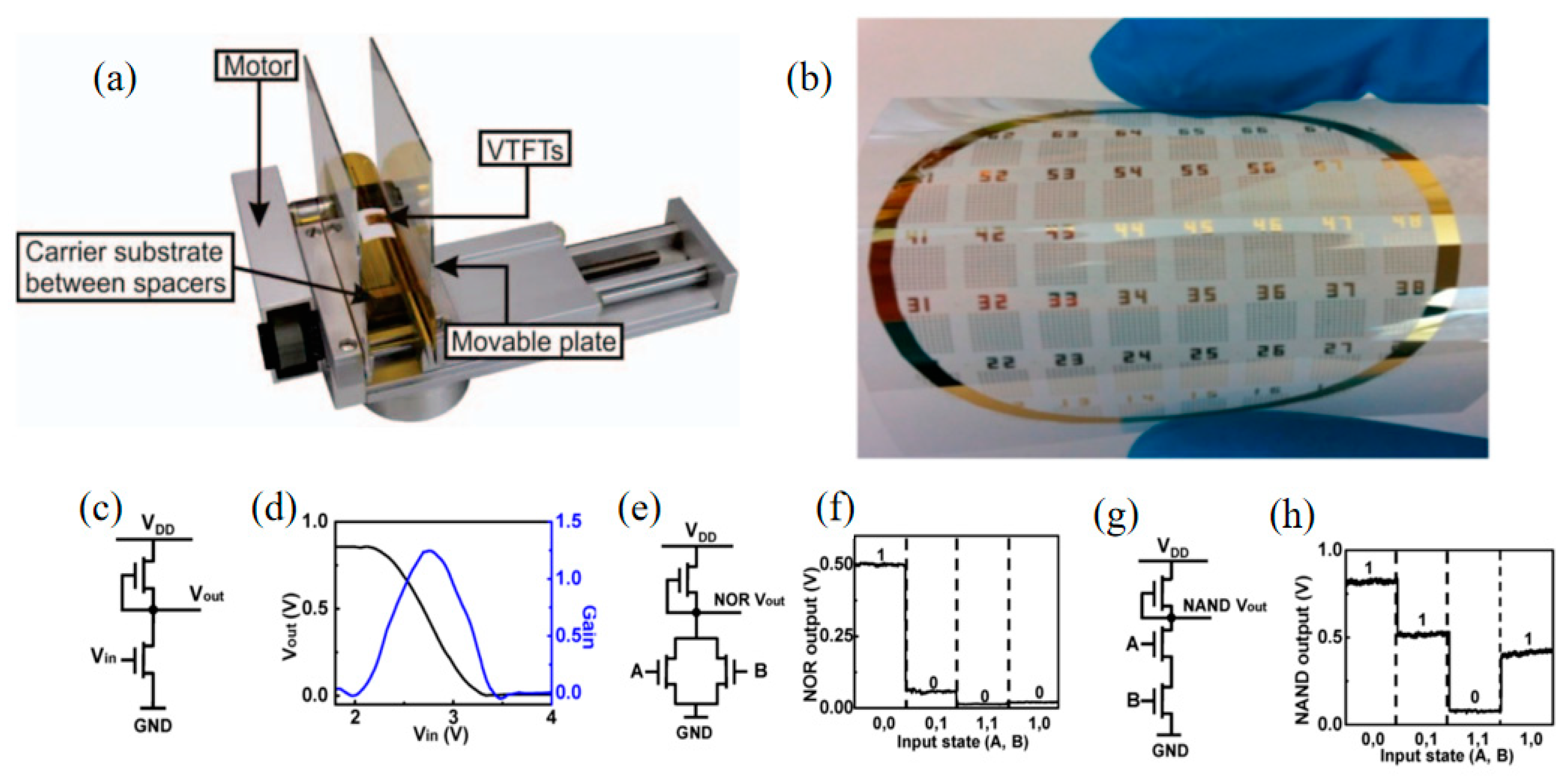

- Liu, Y.; Zhou, H.; Cheng, R.; Yu, W.; Huang, Y.; Duan, X. Highly flexible electronics from scalable vertical thin film transistors. Nano Lett 2014, 14, 1413–1418. [Google Scholar] [CrossRef] [PubMed]

- Liu, L.; Liu, Y.; Duan, X. Graphene-based vertical thin film transistors. Sci. China Inf. Sci. 2020, 63, 201401. [Google Scholar] [CrossRef]

- Kim, H.-R.; Yang, J.-H.; Kim, G.-H.; Yoon, S.-M. Flexible vertical-channel thin-film transistors using In-Ga-Zn-O active channel and polyimide spacer on poly(ethylene naphthalate) substrate. J. Vac. Sci. Technol. B 2019, 37, 010602. [Google Scholar] [CrossRef]

- Hwang, C.-S.; Park, S.-H.K.; Oh, H.; Ryu, M.-K.; Cho, K.-I.; Yoon, S.-M. Vertical Channel ZnO Thin-Film Transistors Using an Atomic Layer Deposition Method. IEEE Electron Device Lett. 2014, 35, 360–362. [Google Scholar] [CrossRef]

- Choi, S.-N.; Yoon, S.-M. Implementation of In–Ga–Zn–O Thin-Film Transistors with Vertical Channel Structures Designed with Atomic-Layer Deposition and Silicon Spacer Steps. Electron. Mater. Lett. 2021, 17, 485–492. [Google Scholar] [CrossRef]

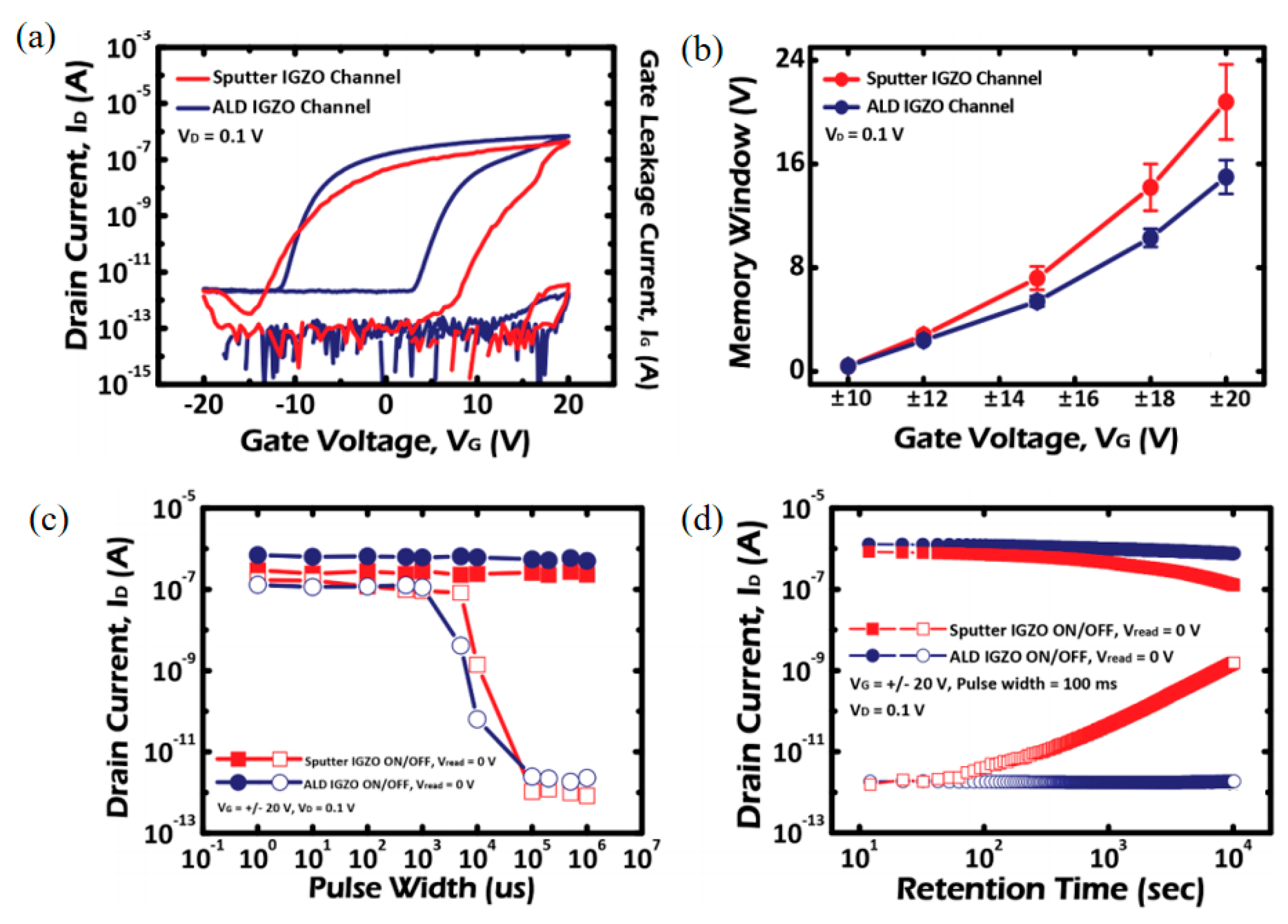

- Kim, H.R.; Kim, G.H.; Seong, N.J.; Choi, K.J.; Kim, S.K.; Yoon, S.M. Comparative studies on vertical-channel charge-trap memory thin-film transistors using In-Ga-Zn-O active channels deposited by sputtering and atomic layer depositions. Nanotechnology 2020, 31, 435702. [Google Scholar] [CrossRef] [PubMed]

- Moradi, M.; Fomani, A.A.; Nathan, A. Effect of gate dielectric scaling in nanometer scale vertical thin film transistors. Appl. Phys. Lett. 2011, 99, 223503. [Google Scholar] [CrossRef]

- Sun, K.G.; Nelson, S.F.; Jackson, T.N. Modeling of Self-Aligned Vertical ZnO Thin-Film Transistors. IEEE Trans. Electron Devices 2015, 62, 1912–1917. [Google Scholar] [CrossRef]

- Kim, Y.-M.; Kim, G.-H.; Yoon, S.-M. Transparent oxide thin-film transistors with vertical channel structure using atomic-layer-deposited In-Ga-Zn-O thin films. In Proceedings of the 2017 24th International Workshop on Active-Matrix Flatpanel Displays and Devices (AM-FPD), Kyoto, Japan, 4–7 July 2017; pp. 312–315. [Google Scholar]

- Ryoo, H.-J.; Ahn, H.-M.; Seong, N.-J.; Choi, K.-J.; Hwang, C.-S.; Chang, S.-J.; Yoon, S.-M. Device Characterization of Nanoscale Vertical-Channel Transistors Implemented with a Mesa-Shaped SiO2 Spacer and an In–Ga–Zn–O Active Channel. ACS Appl. Electron. Mater. 2021, 3, 4189–4196. [Google Scholar] [CrossRef]

- Neamen, D.A. Semiconductor Physics and Devices: Basic Principles; Neamen, D.A., Ed.; McGraw-Hill: New York, NY, USA, 2012; pp. 290–291. [Google Scholar]

- Uchida, Y.; Nara, Y.; Matsumura, M. Proposed vertical-type amorphous-silicon field-effect transistors. IEEE Electron Device Lett. 1984, 5, 105–107. [Google Scholar] [CrossRef]

- Chan, I.; Nathan, A. Amorphous silicon thin-film transistors with 90° vertical nanoscale channel. Appl. Phys. Lett. 2005, 86, 253501. [Google Scholar] [CrossRef]

- Toure, H.D.; Gaillard, T.; Coulon, N.; Bonnaud, O. A Vertical Thin Film Transistor Based on Low Temperature Technology (T < 600 °C). ECS Trans. 2008, 16, 165. [Google Scholar]

- Zhang, P.; Jacques, E.; Rogel, R.; Coulon, N.; Bonnaud, O. Quasi-vertical multi-tooth thin film transistors based on low-temperature technology (T ≤ 600 °C). Solid-State Electron. 2013, 79, 26–30. [Google Scholar] [CrossRef]

- Boesen, G.; Jacobs, J.E. ZnO field-effect transistor. Proc. IEEE 1968, 56, 2094–2095. [Google Scholar] [CrossRef]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Park, S.-H.K.; Cho, D.-H.; Hwang, C.-S.; Yang, S.; Ryu, M.K.; Byun, C.-W.; Yoon, S.M.; Cheong, W.-S.; Cho, K.I.; Jeon, J.-H. Channel Protection Layer Effect on the Performance of Oxide TFTs. ETRI J. 2009, 31, 653–659. [Google Scholar] [CrossRef]

- Park, S.-H.K.; Kim, H.-O.; Cho, S.-H.; Ryu, M.K.; Yang, J.-H.; Ko, J.-B.; Hwang, C.-S. (Invited) Gate Insulator for High Mobility Oxide TFT. ECS Trans. 2014, 64, 123. [Google Scholar] [CrossRef]

- Nelson, S.F.; Levy, D.H.; Tutt, L.W. Defeating the trade-off between process complexity and electrical performance with vertical zinc oxide transistors. Appl. Phys. Lett. 2012, 101, 183503. [Google Scholar] [CrossRef]

- Nelson, S.F.; Tutt, L.W. Zinc oxide ring oscillators with vertical thin film transistors. In Proceedings of the 71st Device Research Conference, South Bend, IN, USA, 23–26 June 2013; pp. 169–170. [Google Scholar]

- Yeom, H.-I.; Moon, G.; Nam, Y.; Ko, J.-B.; Lee, S.-H.; Choe, J.; Choi, J.H.; Hwang, C.-S.; Park, S.-H.K. 60-3:Distinguished Paper: Oxide Vertical TFTs for the Application to the Ultra High Resolution Display. SID Symp. Dig. Tech. Pap. 2016, 47, 820–822. [Google Scholar] [CrossRef]

- Ahn, H.-M.; Kwon, Y.-H.; Seong, N.-J.; Choi, K.-J.; Hwang, C.-S.; Yoon, S.-M. Impact of Strategic Approaches for Improving the Device Performance of Mesa-shaped Nanoscale Vertical-Channel Thin-Film Transistors Using Atomic-Layer Deposited In–Ga–Zn–O Channel Layers. Electron. Mater. Lett. 2022, 18, 294–303. [Google Scholar] [CrossRef]

- Ahn, H.-M.; Kwon, Y.-H.; Seong, N.-J.; Choi, K.-J.; Hwang, C.-S.; Yang, J.-H.; Kim, Y.-H.; Kim, G.; Yoon, S.-M. Improvement in current drivability and stability in nanoscale vertical channel thin-film transistors via band-gap engineering in In-Ga-Zn-O bilayer channel configuration. Nanotechnology 2023, 34, 155301. [Google Scholar] [CrossRef]

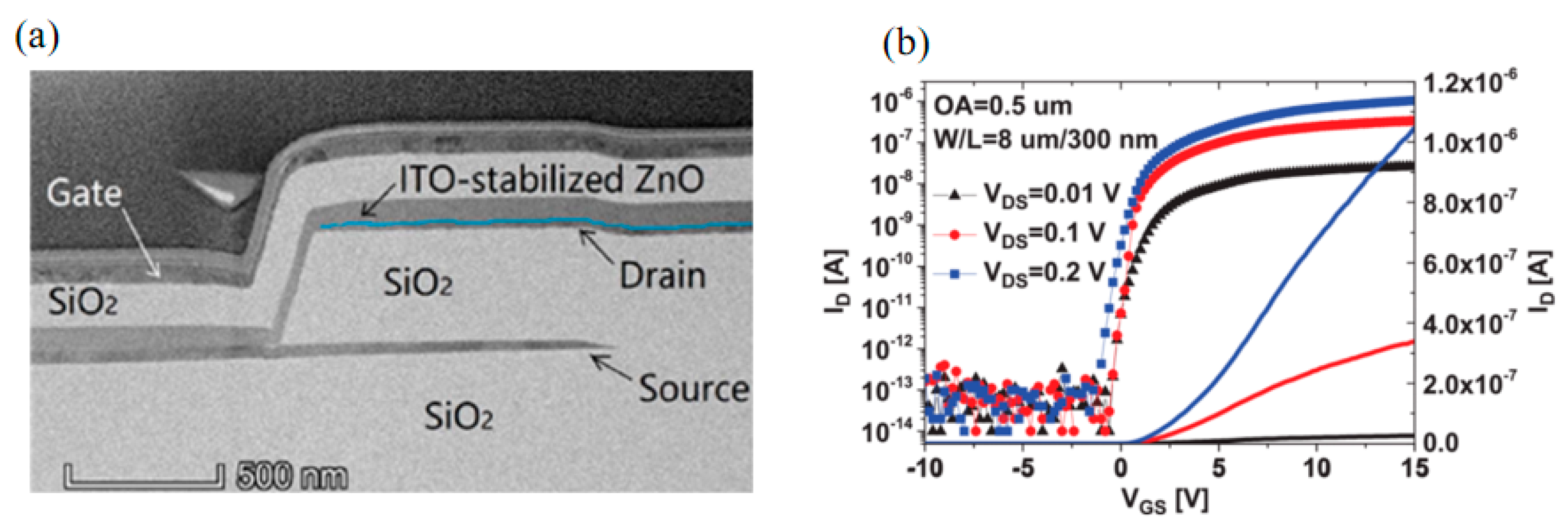

- Yin, X.; Deng, S.; Li, G.; Zhong, W.; Chen, R.; Li, G.; Yeung, F.S.Y.; Wong, M.; Kwok, H.S. Low Leakage Current Vertical Thin-Film Transistors With InSnO-Stabilized ZnO Channel. IEEE Electron Device Lett. 2020, 41, 248–251. [Google Scholar] [CrossRef]

- Ho Rha, S.; Jung, J.; Soo Jung, Y.; Jang Chung, Y.; Ki Kim, U.; Suk Hwang, E.; Keon Park, B.; Joo Park, T.; Choi, J.-H.; Seong Hwang, C. Vertically integrated submicron amorphous-In2Ga2ZnO7 thin film transistor using a low temperature process. Appl. Phys. Lett. 2012, 100, 203510. [Google Scholar] [CrossRef]

- Petti, L.; Aguirre, P.; Münzenrieder, N.; Salvatore, G.A.; Zysset, C.; Frutiger, A.; Büthe, L.; Vogt, C.; Tröster, G. Mechanically flexible vertically integrated a-IGZO thin-film transistors with 500 nm channel length fabricated on free standing plastic foil. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 11.14.11–11.14.14. [Google Scholar] [CrossRef]

- Song, J.; Huang, X.; Han, C.; Yu, Y.; Su, Y.; Lai, P. Recent Developments of Flexible InGaZnO Thin-Film Transistors. Phys. Status Solidi A 2021, 218, 2000527. [Google Scholar] [CrossRef]

- Han, G.; Cao, S.; Yang, Q.; Yang, W.; Guo, T.; Chen, H. High-Performance All-Solution-Processed Flexible Photodetector Arrays Based on Ultrashort Channel Amorphous Oxide Semiconductor Transistors. ACS Appl. Mater. Interfaces 2018, 10, 40631–40640. [Google Scholar] [CrossRef]

- Burr, G.W.; Virwani, K.; Shenoy, R.S.; Fraczak, G.; Rettner, C.T.; Padilla, A.; King, R.S.; Nguyen, K.; Bowers, A.N.; Jurich, M.; et al. Recovery dynamics and fast (sub-50ns) read operation with Access Devices for 3D crosspoint memory based on mixed-ionic-electronic-conduction (MIEC). In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013; pp. T66–T67. [Google Scholar]

- Lee, S.H.; Park, H.C.; Kim, M.S.; Kim, H.W.; Choi, M.R.; Lee, H.G.; Seo, J.W.; Kim, S.C.; Kim, S.G.; Hong, S.B.; et al. Highly productive PCRAM technology platform and full chip operation: Based on 4F2 (84nm pitch) cell scheme for 1 Gb and beyond. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 3.3.1–3.3.4. [Google Scholar]

- Siau, C.; Kim, K.H.; Lee, S.; Isobe, K.; Shibata, N.; Verma, K.; Ariki, T.; Li, J.; Yuh, J.; Amarnath, A.; et al. 13.5 A 512Gb 3-bit/Cell 3D Flash Memory on 128-Wordline-Layer with 132MB/s Write Performance Featuring Circuit-Under-Array Technology. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 218–220.

- Bedeschi, F.; Fackenthal, R.; Resta, C.; Donze, E.M.; Jagasivamani, M.; Buda, E.C.; Pellizzer, F.; Chow, D.W.; Cabrini, A.; Calvi, G.M.A.; et al. A Bipolar-Selected Phase Change Memory Featuring Multi-Level Cell Storage. IEEE J. Solid-State Circuits 2009, 44, 217–227. [Google Scholar] [CrossRef]

- Zhang, W.; Xu, J.; Wang, S.; Zhou, Y.; Mi, J. Metrology Challenges in 3D NAND Flash Technical Development and Manufacturing. J. Microelectron. Manuf. 2019, 3, 1–8. [Google Scholar] [CrossRef]

- Tiwari, N.; Nirmal, A.; Kulkarni, M.R.; John, R.A.; Mathews, N. Enabling high performance n-type metal oxide semiconductors at low temperatures for thin film transistors. Inorg. Chem. Front. 2020, 7, 1822–1844. [Google Scholar] [CrossRef]

- Chuang, C.H.; Weng, H.K.; Chen, J.W.; Shaikh, M.O. Ultrasonic tactile sensor integrated with TFT array for force feedback and shape recognition. Sens. Actuator A Phys 2018, 271, 348–355. [Google Scholar] [CrossRef]

- Aditya Kumar, S.; Nikita Kar, C.; Arnab, H.; Basanta, B. Room-Temperature Au/TiO2Nanorods/Ti TFT Butanone Sensor: Role of Surface States. J. Electron. Mater. 2023, 52, 3622–3632. [Google Scholar] [CrossRef]

- Afsar, Y.; Moy, T.; Brady, N.; Wagner, S.; Sturm, J.C.; Verma, N. An Architecture for Large-Area Sensor Acquisition Using Frequency-Hopping ZnO TFT DCOs. IEEE J. Solid-State Circuits 2018, 53, 297–308. [Google Scholar] [CrossRef]

- Cai, G.; Qiang, L.; Yang, P.; Chen, Z.; Zhuo, Y.; Li, Y.; Pei, Y.; Wang, G. High Sensitivity pH Sensor Based on Electrolyte-gated In2O3 TFT. IEEE Electron Device Lett. 2018, 39, 1409–1412. [Google Scholar] [CrossRef]

- Chen, Y.; Geng, D.; Jang, J. Integrated Active-Matrix Capacitive Sensor using a-IGZO TFTs for AMOLED. IEEE J. Electron Devices Soc. 2018, 6, 214–218. [Google Scholar] [CrossRef]

- Kim, K.-N.; Ko, W.-S.; Byun, J.-H.; Lee, D.-Y.; Jeong, J.-K.; Lee, H.-D.; Lee, G.-W. Bottom-Gated ZnO TFT Pressure Sensor with 1D Nanorods. Sensors 2022, 22, 8907. [Google Scholar] [CrossRef] [PubMed]

- Noriyuki, K.; Tomohiro, S.; Takuro, T.; Daiki, S.; Kazunori, M.; Miya, Y.; Katsuyoshi, H. Shear-Force Sensor With Point-Symmetric Electrodes Driven by LTPS TFT Active Matrix Backplane. IEEE Sens. J. 2021, 22, 3080–3086. [Google Scholar] [CrossRef]

- Tai, Y.-H.; Tu, C.-C.; Yuan, Y.-C.; Chang, Y.-J.; Hsu, M.-H.; Chuang, C.-Y. Light-Controlled Gap-Type TFT Used for Large-Area Under-Screen Fingerprint Sensor. IEEE J. Electron Devices Soc. 2021, 9, 517–520. [Google Scholar] [CrossRef]

- Xin, C.; Chen, L.; Li, T.; Zhang, Z.; Zhao, T.; Li, X.; Zhang, J. Highly Sensitive Flexible Pressure Sensor by the Integration of Microstructured PDMS Film With a-IGZO TFTs. IEEE Electron Device Lett. 2018, 39, 1073–1076. [Google Scholar] [CrossRef]

- Sekitani, T.; Zschieschang, U.; Klauk, H.; Someya, T. Flexible organic transistors and circuits with extreme bending stability. Nat. Mater. 2010, 9, 1015–1022. [Google Scholar] [CrossRef] [PubMed]

- Karner-Petritz, E.; Petritz, A.; Uemura, T.; Namba, N.; Araki, T.; Sekitani, T.; Stadlober, B. Ultraflexible Organic Active Matrix Sensor Sheet for Tactile and Biosignal Monitoring. Adv. Electron. Mater. 2023, 2201333. [Google Scholar] [CrossRef]

- Shen, Y.C.; Yang, C.H.; Chen, S.W.; Wu, S.H.; Yang, T.L.; Huang, J.J. IGZO thin film transistor biosensors functionalized with ZnO nanorods and antibodies. Biosens. Bioelectron. 2014, 54, 306–310. [Google Scholar] [CrossRef]

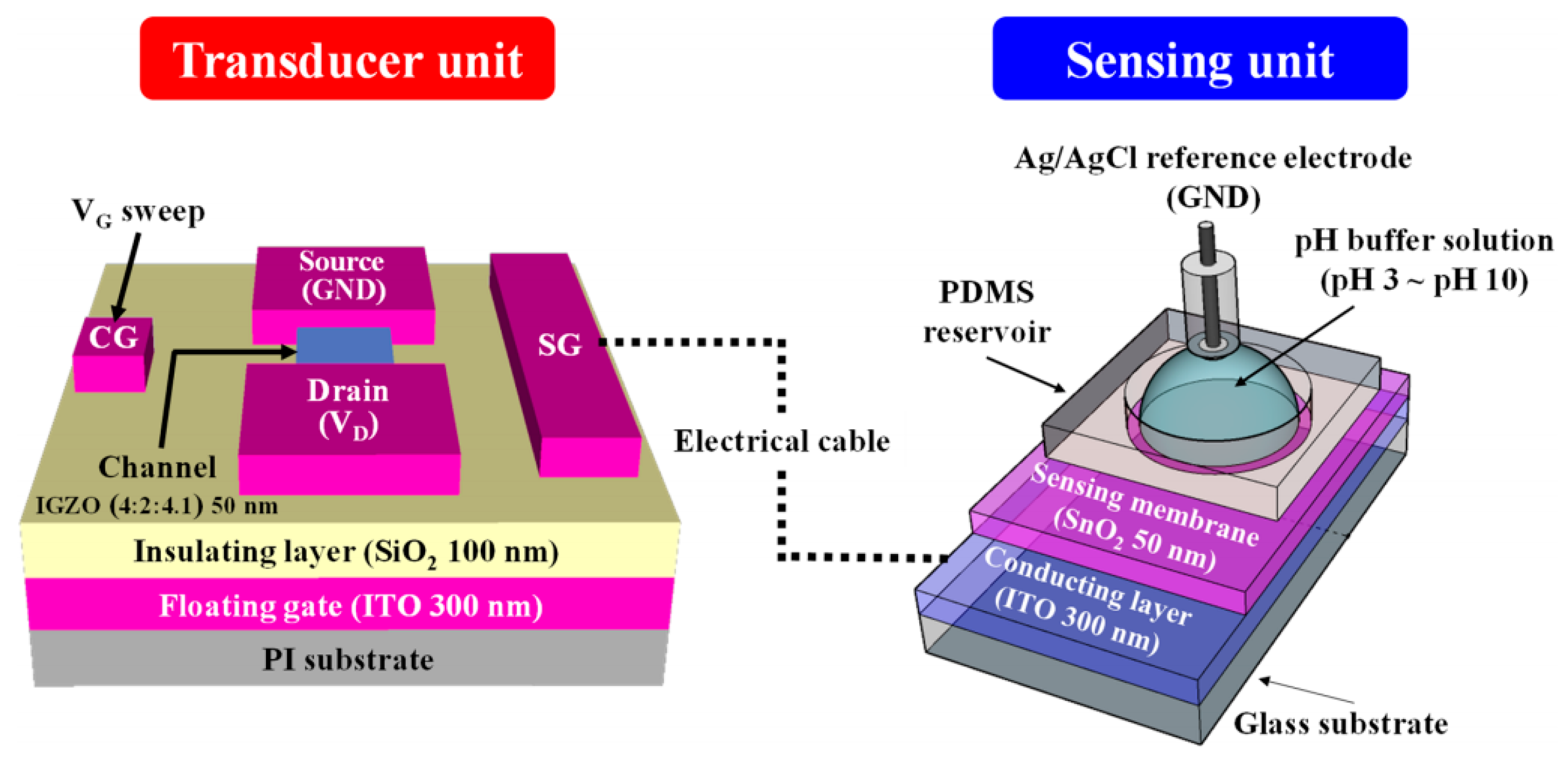

- Hyun, T.-H.; Cho, W.-J. Fully Transparent and Highly Sensitive pH Sensor Based on an a-IGZO Thin-Film Transistor with Coplanar Dual-Gate on Flexible Polyimide Substrates. Chemosensors 2023, 11, 46. [Google Scholar] [CrossRef]

- McAlpine, M.C.; Ahmad, H.; Wang, D.; Heath, J.R. Highly ordered nanowire arrays on plastic substrates for ultrasensitive flexible chemical sensors. Nat. Mater. 2007, 6, 379–384. [Google Scholar] [CrossRef]

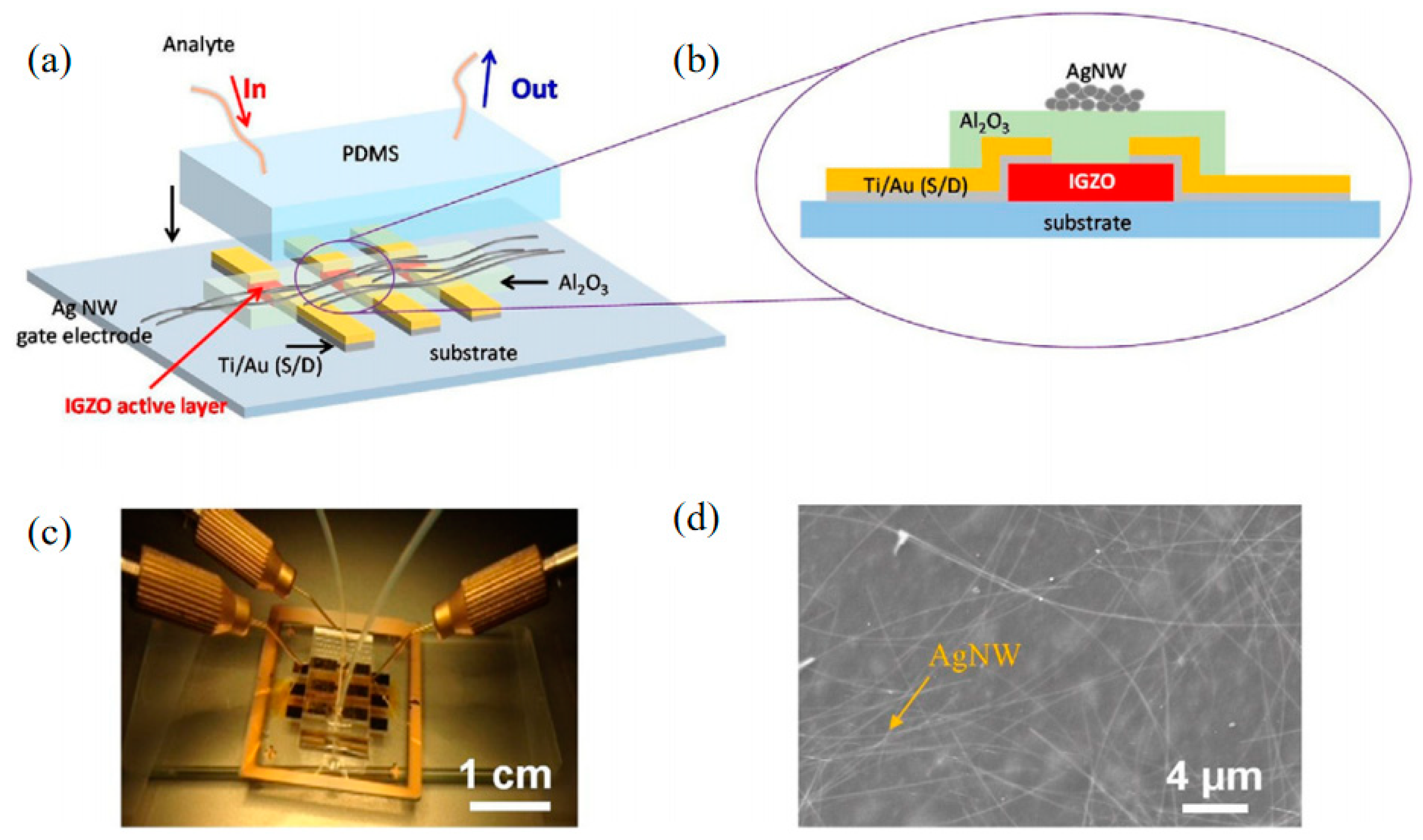

- Yoo, T.-H.; Moon, H.G.; Wang, B.-Y.; Sang, B.-I.; Angadi, B.; Oh, Y.-J.; Choi, W.K.; Kang, C.-Y.; Hwang, D.K. InGaZnO transistor based on porous Ag nanowire-functionalized gate electrode for detection of bio-relevant molecules. Sens. Actuators B: Chem. 2018, 254, 36–43. [Google Scholar] [CrossRef]

- Knobelspies, S.; Bierer, B.; Daus, A.; Takabayashi, A.; Salvatore, G.A.; Cantarella, G.; Ortiz Perez, A.; Wollenstein, J.; Palzer, S.; Troster, G. Photo-Induced Room-Temperature Gas Sensing with a-IGZO Based Thin-Film Transistors Fabricated on Flexible Plastic Foil. Sensors 2018, 18, 358. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Cavallari, M.R.; Izquierdo, J.E.; Braga, G.S.; Dirani, E.A.; Pereira-da-Silva, M.A.; Rodriguez, E.F.; Fonseca, F.J. Enhanced Sensitivity of Gas Sensor Based on Poly(3-hexylthiophene) Thin-Film Transistors for Disease Diagnosis and Environment Monitoring. Sensors. 2015, 15, 9592–9609. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Zhu, X.; Li, X.; Gu, C.; Ye, Z.; Cao, Z.; Zhang, X.; Jin, C.; Liu, Y. Monolithic Integration of Vertical Thin-Film Transistors in Nanopores for Charge Sensing of Single Biomolecules. ACS Nano 2021, 15, 9882–9889. [Google Scholar] [CrossRef] [PubMed]

- Yoon, S.; Tak, Y.J.; Yoon, D.H.; Choi, U.H.; Park, J.S.; Ahn, B.D.; Kim, H.J. Study of nitrogen high-pressure annealing on InGaZnO thin-film transistors. ACS Appl. Mater. Interfaces 2014, 6, 13496–13501. [Google Scholar] [CrossRef] [PubMed]

- Hu, S.; Lu, K.; Ning, H.; Fang, Z.; Liu, X.; Xie, W.; Yao, R.; Zou, J.; Xu, M.; Peng, J. Effect of ITO Serving as a Barrier Layer for Cu Electrodes on Performance of a-IGZO TFT. IEEE Electron Device Lett. 2018, 39, 504–507. [Google Scholar] [CrossRef]

- Wang, C.; Peng, C.; Wen, P.; Xu, M.; Chen, L.; Li, X.; Zhang, J. Improvement of Performance of Back Channel Etching InGaZnO Thin-Film Transistors by CF4 Plasma Treatment. IEEE Trans. Electron Devices 2023, 70, 1687–1691. [Google Scholar] [CrossRef]

- Choi, H.S.; Cho, W.J. Investigation of Multi-Level Cell Characteristic in Amorphous Indium-Gallium-Zinc Oxide Thin-Film-Transistor Based 1T-1R Non-Volatile Memory Device. J Nanosci Nanotechnol 2019, 19, 6031–6035. [Google Scholar] [CrossRef]

- Choi, H.S.; Cho, W.J. Controlling In-Ga-Zn-O Thin-Film Resistance by Vacuum Rapid Thermal Annealing and Application to Transparent Electrode. Phys. Status Solidi A 2018, 216, 1800653. [Google Scholar] [CrossRef]

- Zhou, S.; Fang, Z.; Ning, H.; Cai, W.; Zhu, Z.; Wei, J.; Lu, X.; Yuan, W.; Yao, R.; Peng, J. Bias Stability Enhancement in Thin-Film Transistor with a Solution-Processed ZrO2 Dielectric as Gate Insulator. Appl. Sci. 2018, 8, 806. [Google Scholar] [CrossRef] [Green Version]

- Abliz, A.; Gao, Q.; Wan, D.; Liu, X.; Xu, L.; Liu, C.; Jiang, C.; Li, X.; Chen, H.; Guo, T.; et al. Effects of Nitrogen and Hydrogen Codoping on the Electrical Performance and Reliability of InGaZnO Thin-Film Transistors. ACS Appl. Mater. Interfaces 2017, 9, 10798–10804. [Google Scholar] [CrossRef]

- Wu, F.; Tian, H.; Shen, Y.; Hou, Z.; Ren, J.; Gou, G.; Sun, Y.; Yang, Y.; Ren, T.L. Vertical MoS(2) transistors with sub-1-nm gate lengths. Nature 2022, 603, 259–264. [Google Scholar] [CrossRef]

- Chau, R.; Doyle, B.; Datta, S.; Kavalieros, J.; Zhang, K. Integrated nanoelectronics for the future. Nat. Mater. 2007, 6, 810–812. [Google Scholar] [CrossRef] [PubMed]

- Yu, W.J.; Li, Z.; Zhou, H.; Chen, Y.; Wang, Y.; Huang, Y.; Duan, X. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 2013, 12, 246–252. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Baby, T.T.; Rommel, M.; von Seggern, F.; Friederich, P.; Reitz, C.; Dehm, S.; Kubel, C.; Wenzel, W.; Hahn, H.; Dasgupta, S. Sub-50 nm Channel Vertical Field-Effect Transistors using Conventional Ink-Jet Printing. Adv. Mater. 2017, 29, 1603858. [Google Scholar] [CrossRef]

- Yakimets, D.; Eneman, G.; Schuddinck, P.; Trong Huynh, B.; Bardon, M.G.; Raghavan, P.; Veloso, A.; Collaert, N.; Mercha, A.; Verkest, D.; et al. Vertical GAAFETs for the Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2015, 62, 1433–1439. [Google Scholar] [CrossRef]

- Oh, H.; Park, J.; Choi, W.; Kim, H.; Tchoe, Y.; Agrawal, A.; Yi, G.C. Vertical ZnO Nanotube Transistor on a Graphene Film for Flexible Inorganic Electronics. Small 2018, 14, e1800240. [Google Scholar] [CrossRef] [PubMed]

- Liu, Y.; Guo, J.; Zhu, E.; Wang, P.; Gambin, V.; Huang, Y.; Duan, X. Maximizing the Current Output in Self-Aligned Graphene-InAs-Metal Vertical Transistors. ACS Nano 2019, 13, 847–854. [Google Scholar] [CrossRef] [PubMed]

- Zou, Y.; Shi, Y.; Wang, B.; Liu, M.; An, J.; Zhang, N.; Qi, L.; Yu, W.; Li, D.; Li, S. Electrical and Optoelectrical Dual-Modulation in Perovskite-Based Vertical Field-Effect Transistors. ACS Photonics 2022, 10, 2280–2289. [Google Scholar] [CrossRef]

- Yamazaki, S. (Invited) A Possibility of Crystalline Indium-Gallium-Zinc-Oxide to Very Large Scale Integration. ECS Trans. 2013, 54, 85. [Google Scholar] [CrossRef]

- Lim, T.; Lee, S.; Lee, J.; Choi, H.; Jung, B.; Baek, S.; Jang, J. Artificial Synapse Based on Oxygen Vacancy Migration in Ferroelectric-Like C-Axis-Aligned Crystalline InGaSnO Semiconductor Thin-Film Transistors for Highly Integrated Neuromorphic Electronics. Adv. Funct. Mater. 2022, 33, 2212367. [Google Scholar] [CrossRef]

| Spacer Material Selection Indicator | Material Types | Process Compatibility | Interface Properties | Cost Controllability |

|---|---|---|---|---|

| Selection requirements | Good insulating properties | Compatible with the other material preparation process | Minimize interface effects such as interface defects | The preparation process reproducible, large areas and low cost |

| Years | Mobility (cm2/Vs) | Ion/Ioff | SS (mV/dec) | Channel Length (nm) | Active Layer Materials | Method | Reference |

|---|---|---|---|---|---|---|---|

| 2008 | N/A | 108 | 800 | 100 | a-Si:H | sputtering | [44] |

| 2012 | 0.03 | 104 | 3000–6000 | 310 | IGZO | sputtering | [57] |

| 2012 | 12.7 | 5 × 107 | 70 | 500 | ZnO | ALD | [51] |

| 2013 | 3.96 | 103 | 3600 | 1000 | Poly silicon | sputtering | [46] |

| 2013 | 11.8 | 2 × 107 | 600 | 500 | IGZO | sputtering | [58] |

| 2014 | 3.3 | 8.8 × 106 | 400 | 500 | ZnO | ALD | [35] |

| 2015 | 0.2 | 104 | 400 | 300 | IGZO | sputtering | [59] |

| 2017 | 7.1 | 103 | 1200 | 300 | IGZO | ALD | [28] |

| 2018 | N/A | 105 | 900 | 121 | In2O3 | solution | [60] |

| 2019 | 5.96 | 3.3 × 107 | 210 | 300 | ITO-stabilized ZnO | sputtering | [56] |

| 2021 | 3.21 | 6.9 × 107 | 460 | 250 | IGZO | ALD | [36] |

| 2021 | 0.1 | 8.8 × 103 | 800 | 160 | IGZO | ALD | [41] |

| 2021 | 0.19 | 106 | 540 | 130 | IGZO | ALD | [27] |

| 2022 | 2.2 | 4.2 × 109 | 430 | 170 | IGZO | ALD | [54] |

| 2022 | 24.1 | 1.2 × 109 | 213 | 400 | IGZO | ALD | [29] |

| 2023 | N/A | 4.8 × 109 | 180 | 150 | IGZO | ALD | [55] |

| Device Type | Mobility (cm2/Vs) | Ion/Ioff | SS (mV/dec) | Reference | Device Dimension | Power Consumption |

|---|---|---|---|---|---|---|

| Planar TFT | 8.82 | 1.07 × 109 | 330 | [85] | Large | High |

| 11.5 | 2.4 × 1010 | 200 | [86] | |||

| 16.4 | 1.1 × 1010 | 340 | [87] | |||

| 10.8 | 9.2 × 107 | 226 | [88] | |||

| 36.187 | 3.56 × 107 | 315.45 | [89] | |||

| 12.7 | 7.6 × 105 | 340 | [90] | |||

| 45.3 | 108 | 210 | [91] | |||

| Vertical TFT | 0.2 | 104 | 400 | [59] | Small | Low |

| 7.1 | 103 | 1200 | [26] | |||

| 3.21 | 6.9 × 107 | 460 | [36] | |||

| 0.1 | 8.8 × 103 | 800 | [41] | |||

| 0.19 | 106 | 540 | [27] | |||

| 2.2 | 4.2 × 109 | 430 | [54] | |||

| 24.1 | 1.2 × 109 | 213 | [29] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, B.; Huang, H.; Wen, P.; Xu, M.; Peng, C.; Chen, L.; Li, X.; Zhang, J. Research Progress of Vertical Channel Thin Film Transistor Device. Sensors 2023, 23, 6623. https://doi.org/10.3390/s23146623

Sun B, Huang H, Wen P, Xu M, Peng C, Chen L, Li X, Zhang J. Research Progress of Vertical Channel Thin Film Transistor Device. Sensors. 2023; 23(14):6623. https://doi.org/10.3390/s23146623

Chicago/Turabian StyleSun, Benxiao, Huixue Huang, Pan Wen, Meng Xu, Cong Peng, Longlong Chen, Xifeng Li, and Jianhua Zhang. 2023. "Research Progress of Vertical Channel Thin Film Transistor Device" Sensors 23, no. 14: 6623. https://doi.org/10.3390/s23146623

APA StyleSun, B., Huang, H., Wen, P., Xu, M., Peng, C., Chen, L., Li, X., & Zhang, J. (2023). Research Progress of Vertical Channel Thin Film Transistor Device. Sensors, 23(14), 6623. https://doi.org/10.3390/s23146623