A Size, Weight, Power, and Cost-Efficient 32-Channel Time to Digital Converter Using a Novel Wave Union Method

Abstract

1. Introduction

| RMS Resolution [Ps] | Channel | System | DNL (LSB) | INL (LSB) | Architecture | Ref. |

|---|---|---|---|---|---|---|

| 2.9 | 16-Ch | Xilinx Spartan-6 | N/A | 19.36 | Time Coding Line TCL | [26] |

| 3.9 | 2-Ch Dual-Sampling | Xilinx Ultra-Scale | N/A | N/A | TDL | [19] |

| 4.2 | 2-Ch (M = 8) Multi-Chain | Xilinx Virtex-6 | 3.8 | 19.36 | Plain Tapped-Delay | [27] |

| 4.5 | 8 -Ch | Xilinx Kintex-7 | 4.11 | 18.85 | Time interval Counter | [28] |

| 6 | 1-Ch | Custom ASIC | N/A | N/A | MASH TDC | [7] |

| 7.4 | 1-Ch | Xilinx Virtex-5 | 1.4 | 3.09 | Matrix of Counter | [29] |

| 10 | 128-Ch | Xilinx Kintex-7 | 42 | N/A | TDL | [10] |

| 10.23 | 256-Ch | Xilinx Kintex-7 | N/A | N/A | TDL | [18] |

| 20 | 264-Ch | Lattice ECP3-150 EA FPGA | N/A | N/A | Delay Line TDC | [17] |

| 69 | 64-Ch | ProASIC3 | N/A | N/A | Coarse-Time Counters | [30] |

| 81.3 | 4-Ch | Xilinx XC3S200AN | N/A | 1.93 | Pulse-Shrinking | [20] |

| 198 | 8-Ch | Xilinx kintex-7 | 1.1 | 2.7 | Multi-Phase Clocks | [16] |

2. Proposed WU-A Launcher

3. Calibration

3.1. Calibration Algorithm

3.2. Encoder

4. Implementation

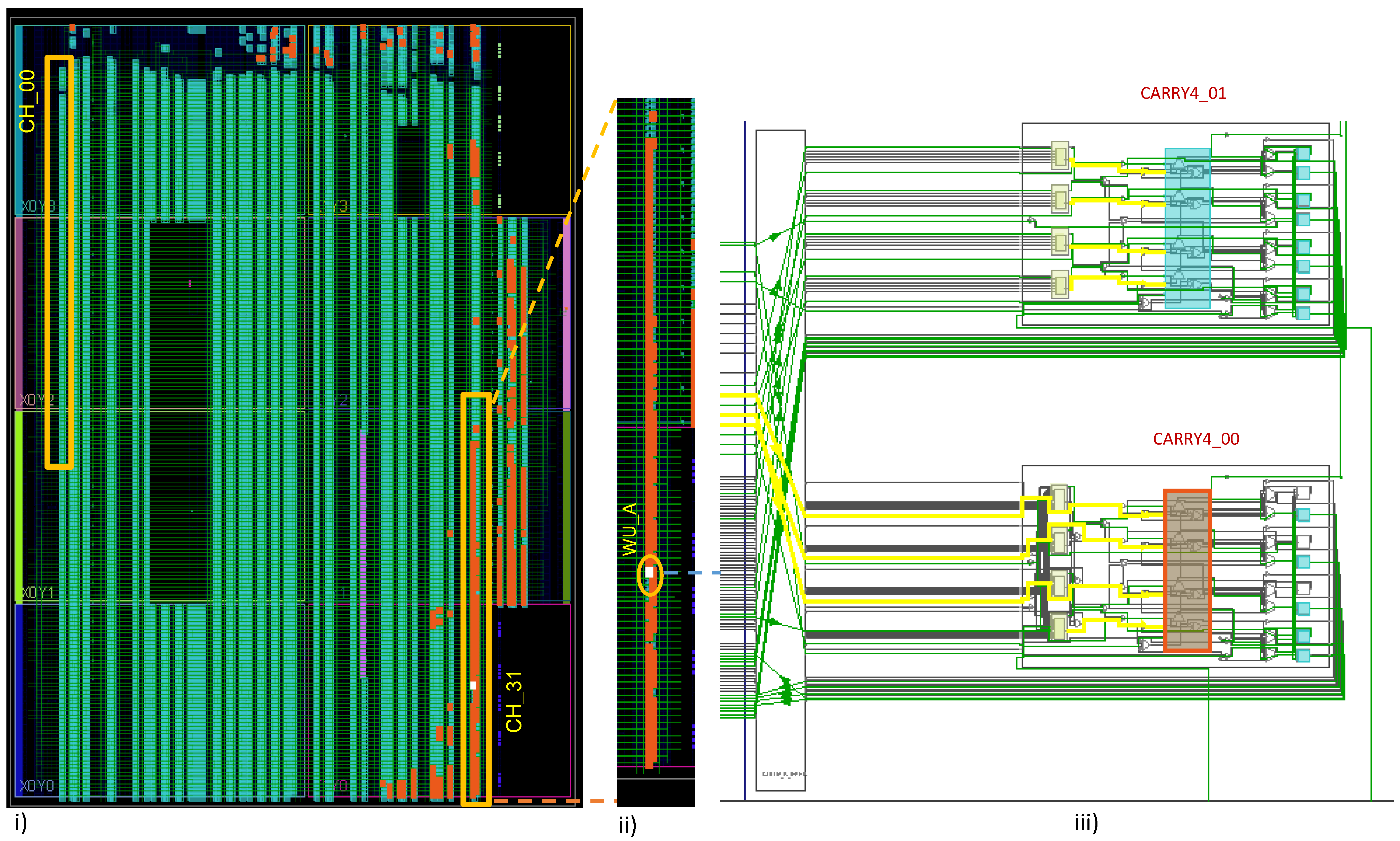

Layout of Single Channel and 32-Channel WU-A TDC

5. Results and Discussion

5.1. Algorithm

5.2. Time Measurements

5.3. Average Process

5.4. Statistical Results

5.5. Test of Differential and Integral Non-Linearity

5.6. On-Chip Power

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Henzler, S.; Henzler, S. Time-to-Digital Converter Basics; Springer: Berlin/Heidelberg, Germany, 2010. [Google Scholar]

- Nolet, F.; Lemaire, W.; Dubois, F.; Roy, N.; Carrier, S.; Samson, A.; Charlebois, S.A.; Fontaine, R.; Pratte, J.F. A 256 Pixelated SPAD readout ASIC with in-Pixel TDC and embedded digital signal processing for uniformity and skew correction. Nucl. Instruments Methods Phys. Res. Sect. Accel. Spectrometers Detect. Assoc. Equip. 2020, 949, 162891. [Google Scholar] [CrossRef]

- Lecoq, P. Pushing the limits in time-of-flight PET imaging. IEEE Trans. Radiat. Plasma Med. Sci. 2017, 1, 473–485. [Google Scholar] [CrossRef]

- Szplet, R.; Sondej, D.; Grzęda, G. High-precision time digitizer based on multiedge coding in independent coding lines. IEEE Trans. Instrum. Meas. 2016, 65, 1884–1894. [Google Scholar] [CrossRef]

- Xie, W.; Wang, Y.; Chen, H.; Li, D.D.U. 128-channel high-linearity resolution-adjustable time-to-digital converters for LiDAR applications: Software predictions and hardware implementations. IEEE Trans. Ind. Electron. 2021, 69, 4264–4274. [Google Scholar] [CrossRef]

- Korkan, A.O.; Yuksel, H. A novel time-to-amplitude converter and a low-cost wide dynamic range FPGA TDC for LiDAR application. IEEE Trans. Instrum. Meas. 2022, 71, 1–15. [Google Scholar] [CrossRef]

- Cao, Y.; De Cock, W.; Steyaert, M.; Leroux, P. Design and assessment of a 6 ps-resolution time-to-digital converter with 5 MGy gamma-dose tolerance for LIDAR application. IEEE Trans. Nucl. Sci. 2012, 59, 1382–1389. [Google Scholar] [CrossRef]

- Gariepy, G.; Tonolini, F.; Henderson, R.; Leach, J.; Faccio, D. Detection and tracking of moving objects hidden from view. Nat. Photonics 2016, 10, 23–26. [Google Scholar] [CrossRef]

- Lin, S.J.; Chen, H.C. A TDC-Based Temperature Sensor for Biomedical Applications. IEEE Sens. J. 2022, 22, 10396–10403. [Google Scholar] [CrossRef]

- Liu, C.; Wang, Y. A 128-channel, 710 M samples/second, and less than 10 ps RMS resolution time-to-digital converter implemented in a Kintex-7 FPGA. IEEE Trans. Nucl. Sci. 2015, 62, 773–783. [Google Scholar] [CrossRef]

- Roberts, G.W.; Ali-Bakhshian, M. A brief introduction to time-to-digital and digital-to-time converters. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 153–157. [Google Scholar] [CrossRef]

- Seo, Y.H.; Kim, J.S.; Park, H.J.; Sim, J.Y. A 0.63 ps resolution, 11b pipeline TDC in 0.13 μm CMOS. In Proceedings of the 2011 Symposium on VLSI Circuits-Digest of Technical Papers, Kyoto, Japan, 15–17 June 2011; pp. 152–153. [Google Scholar]

- Wu, J. Several key issues on implementing delay line based TDCs using FPGAs. IEEE Trans. Nucl. Sci. 2010, 57, 1543–1548. [Google Scholar] [CrossRef]

- Machado, R.; Cabral, J.; Alves, F.S. Recent developments and challenges in FPGA-based time-to-digital converters. IEEE Trans. Instrum. Meas. 2019, 68, 4205–4221. [Google Scholar] [CrossRef]

- Chen, C.C.; Hwang, C.S.; Lin, Y.; Chen, G.H. Note: All-digital pulse-shrinking time-to-digital converter with improved dynamic range. Rev. Sci. Instruments 2016, 87, 046104. [Google Scholar] [CrossRef]

- Sano, Y.; Horii, Y.; Ikeno, M.; Sasaki, O.; Tomoto, M.; Uchida, T. Subnanosecond time-to-digital converter implemented in a Kintex-7 FPGA. Nucl. Instruments Methods Phys. Res. Sect. Accel. Spectrometers Detect. Assoc. Equip. 2017, 874, 50–56. [Google Scholar] [CrossRef]

- Neiser, A.; Adamczewski-Musch, J.; Hoek, M.; Koenig, W.; Korcyl, G.; Linev, S.; Maier, L.; Michel, J.; Palka, M.; Penschuck, M.; et al. TRB3: A 264 channel high precision TDC platform and its applications. J. Instrum. 2013, 8, C12043. [Google Scholar] [CrossRef]

- Song, Z.; Wang, Y.; Kuang, J. A 256-channel, high throughput and precision time-to-digital converter with a decomposition encoding scheme in a Kintex-7 FPGA. J. Instrum. 2018, 13, P05012. [Google Scholar] [CrossRef]

- Wang, Y.; Liu, C. A 3.9 ps time-interval RMS precision time-to-digital converter using a dual-sampling method in an UltraScale FPGA. IEEE Trans. Nucl. Sci. 2016, 63, 2617–2621. [Google Scholar] [CrossRef]

- Bayer, E.; Traxler, M. A High-Resolution (<10 ps RMS) 48-Channel Time-to-Digital Converter (TDC) Implemented in a Field Programmable Gate Array (FPGA). IEEE Trans. Nucl. Sci. 2011, 58, 1547–1552. [Google Scholar]

- Kwiatkowski, P.; Sondej, D.; Szplet, R. Bubble-Proof Algorithm for Wave Union TDCs. Electronics 2022, 11, 30. [Google Scholar] [CrossRef]

- Wu, J. On-Chip processing for the wave union TDC implemented in FPGA. In Proceedings of the 2009 16th IEEE-NPSS Real Time Conference, Beijing, China, 10–15 May 2009; pp. 279–282. [Google Scholar]

- Pan, W.; Gong, G.; Li, J. A 20-ps time-to-digital converter (TDC) implemented in field-programmable gate array (FPGA) with automatic temperature correction. IEEE Trans. Nucl. Sci. 2014, 61, 1468–1473. [Google Scholar] [CrossRef]

- Xie, W.; Chen, H.; Li, D.D.U. Are wave union methods still suitable for 20 nm FPGA-based high-resolution (<2 ps) time-to-digital converters? arXiv 2020, arXiv:2009.03591. [Google Scholar]

- Wang, Y.; Liu, C. A nonlinearity minimization-oriented resource-saving time-to-digital converter implemented in a 28 nm Xilinx FPGA. IEEE Trans. Nucl. Sci. 2015, 62, 2003–2009. [Google Scholar] [CrossRef]

- Szplet, R.; Jachna, Z.; Kwiatkowski, P.; Rozyc, K. A 2.9 ps equivalent resolution interpolating time counter based on multiple independent coding lines. Meas. Sci. Technol. 2013, 24, 035904. [Google Scholar] [CrossRef]

- Shen, Q.; Liu, S.; Qi, B.; An, Q.; Liao, S.; Shang, P.; Peng, C.; Liu, W. A 1.7 ps equivalent bin size and 4.2 ps RMS FPGA TDC based on multichain measurements averaging method. IEEE Trans. Nucl. Sci. 2015, 62, 947–954. [Google Scholar] [CrossRef]

- Szplet, R.; Kwiatkowski, P.; Jachna, Z.; Różyc, K. An eight-channel 4.5-ps precision timestamps-based time interval counter in FPGA chip. IEEE Trans. Instrum. Meas. 2016, 65, 2088–2100. [Google Scholar] [CrossRef]

- Zhang, M.; Wang, H.; Liu, Y. A 7.4 ps FPGA-based TDC with a 1024-unit measurement matrix. Sensors 2017, 17, 865. [Google Scholar] [CrossRef]

- Wang, S.Y.; Wu, J.; Yao, S.H.; Chang, W.C. A field-programmable gate array (FPGA) TDC for the fermilab SeaQuest (E906) experiment and its test with a novel external wave union launcher. IEEE Trans. Nucl. Sci. 2014, 61, 3592–3598. [Google Scholar] [CrossRef]

- Lusardi, N.; Garzetti, F.; Geraci, A. Digital instrument with configurable hardware and firmware for multi-channel time measures. Rev. Sci. Instruments 2019, 90, 055113. [Google Scholar] [CrossRef]

- Kwiatkowski, P.; Szplet, R. Multisampling wave union time-to-digital converter. In Proceedings of the 2020 6th International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Krakow, Poland, 23–25 September 2020; pp. 1–5. [Google Scholar]

- Xie, W.; Chen, H.; Li, D.D.U. Efficient time-to-digital converters in 20 nm FPGAs with wave union methods. IEEE Trans. Ind. Electron. 2021, 69, 1021–1031. [Google Scholar] [CrossRef]

- Xilinx, I. Series FPGAs Configurable Logic Block–User Guide. 2016. Available online: https://www.xilinx.com/support/documentation/user_guides/ug474_7Series_CLB.pdf (accessed on 22 April 2023).

- Xilink, A. Evaluation Boards. 2023. Available online: xilinx.com/products/boards-and-kits/see-all-evaluation-boards.html (accessed on 22 April 2023).

- Kwiatkowski, P.; Sondej, D.; Szplet, R. A brief review of wave union TDCs. In Proceedings of the 2021 7th International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Krakow, Poland, 22–25 June 2021; pp. 1–6. [Google Scholar]

- Wang, Y.; Zhou, X.; Song, Z.; Kuang, J.; Cao, Q. A 3.0-ps rms precision 277-MSamples/s throughput time-to-digital converter using multi-edge encoding scheme in a Kintex-7 FPGA. IEEE Trans. Nucl. Sci. 2019, 66, 2275–2281. [Google Scholar] [CrossRef]

- Akgun, O.C. An asynchronous pipelined time-to-digital converter using time-domain subtraction. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Hu, X.; Zhao, L.; Liu, S.; Wang, J.; An, Q. A stepped-up tree encoder for the 10-ps wave union TDC. IEEE Trans. Nucl. Sci. 2013, 60, 3544–3549. [Google Scholar] [CrossRef]

- Wang, J.; Feng, C.; Dong, W.; Shen, Z.; Liu, S. A high precision time-to-digital converter based on multi-chain interpolation with a low cost artix-7 FPGA. In Proceedings of the 2021 7th International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Krakow, Polan, 22–25 June 2021; pp. 1–5. [Google Scholar]

- Atlys Board Reference Manual; Digilent: Pullman, DC, USA, 2017.

- Parsakordasiabi, M.; Vornicu, I.; Rodríguez-Vázquez, Á.; Carmona-Galán, R. A low-resources TDC for multi-channel direct ToF readout based on a 28-nm FPGA. Sensors 2021, 21, 308. [Google Scholar] [CrossRef] [PubMed]

- Wu, J.; Shi, Y.; Zhu, D. A low-power wave union TDC implemented in FPGA. J. Instrum. 2012, 7, C01021. [Google Scholar] [CrossRef]

| Ref. | Board | Process | Method | RMS Resolution [ps] | DNL (LSB) | INL (LSB) |

|---|---|---|---|---|---|---|

| [23] | Cyclone II | 90 nm | WU-TDL | 21.00 | N/A | N/A |

| [10] | Kintex-7 | 28 nm | TDL-TDC, WU-A Flip-Flop | 10 | N/A | N/A |

| [4] | Spartan-6 | 45 nm | Multichain 2-stage, WU-A LUT | 6 | [−1.00, 6.25] | [−26.2, 11.5] |

| [19] | Kintex-7 | 28 nm | WU-A-based (Multiplexers, TDL) (Eight edges) | 3.90 | [−1.00, 4.50] | [−37.70, 12] |

| [31] | Artix-7 | 28 nm | 16 Ch-Super WU-TDL-TDC | 12.5 | N/A | [−3.7, 4.8] |

| [24] | UltraScale | 20 nm | Sub-TDL, WU-A Compensation | 3.58 | [−0.92, 1.75] | [−1.20, 5.97] |

| [32] | Kintex-7 | 28 nm | Multisampling WU-A (4×transistions, 2×snapshots) | 4.65 | [−0.96, 4.26] | [−25.09, 4.26] |

| This Work | Artix-7 | 45 nm | 32-channel, TDL-TDC, WU-A (Start in First Element) | 1.81 | [−1.01, +0.92] | [−25.24, +26.24] |

| FPGA Board | Kintex-7 | Virtex-5 | Spartan-6 | Zynq-7020 | Artix-7 | Ultra-Scale+ |

|---|---|---|---|---|---|---|

| Process | 28 nm | 65 nm | 45 nm | 28 nm | 45 nm | 16 nm |

| Logic Cells | 356,160 | 330,000 | 43,661 | 85,000 | 33,280 | 154,000 |

| DSP Slices | 1440 | 64 | 58 | 220 | 90 | 360 |

| Memory | 25,740 | 4608 | 2088 | 4900 | 1800 | 7600 |

| I/O Pins | 500 | 680 | 348 | 200 | 250 | 252 |

| Clock Regions | 12 | 16 | 12 | 8 | 8 | 12 |

| CLBs | 27,825 | 17,280 | 5831 | 34,675 | 7925 | 10,980 |

| Resource | WU-A 32-Channels Utilization (%) | Artix-7 Available |

|---|---|---|

| LUT | 73.86% | 63,400 |

| LUTRAM | 32.05% | 19,000 |

| FF | 33.41% | 126,800 |

| BRAM | 84.81% | 135 |

| Clock Regen | 85% X0-Y0 to X1-Y3 | 8 Clocks regions |

| Parameter | Value/Range |

|---|---|

| Average Precision | 2.57 |

| Worst Case Precision | 8.97 |

| Best Case Precision | 0.04 |

| RMS Resolution | 1.817 |

| DNL, DNL | 1.923, [−1.01, +0.923] LSB |

| INL, DNL | 51.68, [−25.24, +26.24] LSB |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alshahry, S.M.; Alshehry, A.H.; Alhazmi, A.K.; Chodavarapu, V.P. A Size, Weight, Power, and Cost-Efficient 32-Channel Time to Digital Converter Using a Novel Wave Union Method. Sensors 2023, 23, 6621. https://doi.org/10.3390/s23146621

Alshahry SM, Alshehry AH, Alhazmi AK, Chodavarapu VP. A Size, Weight, Power, and Cost-Efficient 32-Channel Time to Digital Converter Using a Novel Wave Union Method. Sensors. 2023; 23(14):6621. https://doi.org/10.3390/s23146621

Chicago/Turabian StyleAlshahry, Saleh M., Awwad H. Alshehry, Abdullah K. Alhazmi, and Vamsy P. Chodavarapu. 2023. "A Size, Weight, Power, and Cost-Efficient 32-Channel Time to Digital Converter Using a Novel Wave Union Method" Sensors 23, no. 14: 6621. https://doi.org/10.3390/s23146621

APA StyleAlshahry, S. M., Alshehry, A. H., Alhazmi, A. K., & Chodavarapu, V. P. (2023). A Size, Weight, Power, and Cost-Efficient 32-Channel Time to Digital Converter Using a Novel Wave Union Method. Sensors, 23(14), 6621. https://doi.org/10.3390/s23146621