1. Introduction

Event Timers (ET) are high-precision electronic devices that measure the time interval between two events (i.e., voltage pulses) with extreme precision. Existing ET such as A033-ET and A040-ET are characterized by 3 to 4 ps root-mean square error (RMSE) for single-shot pulses [

1], in stable operating conditions. These timers are used in scientific applications such as satellite laser ranging (SLR) [

2,

3,

4,

5] and optical time domain reflectometry (OTDR) [

6,

7]. For example, in SLR, the Event Timers are used to measure the time delay between the emission of the laser pulse and its reception at the ground station. Picosecond-precision time resolution is required for SLR applications, e.g., the study of Earth’s gravity field.

However, the existing Event Timers have certain limitations. The measurement precision is negatively affected by changes in the ambient temperature. This requires stable operating environments, which are difficult and expensive to achieve. In addition, the events that need to be captured by the timer in SLR and other applications have high dynamic ranges. The precise time an event exceeds the ET’s sensitivity threshold and is registered by the ET therefore depends on the event’s amplitude, rather than just the timing of its peak. This is called the time-walk effect; an amplitude-based compensation mechanism is typically used to remove it from the measurement results. However, using an amplitude-measurement device complicates the setup and leads to a lengthy dead time after each event. When SLR measurements are taken during the daytime, noise spikes caused by ambient daylight register as frequent low-amplitude events, and therefore the dead time should be minimized.

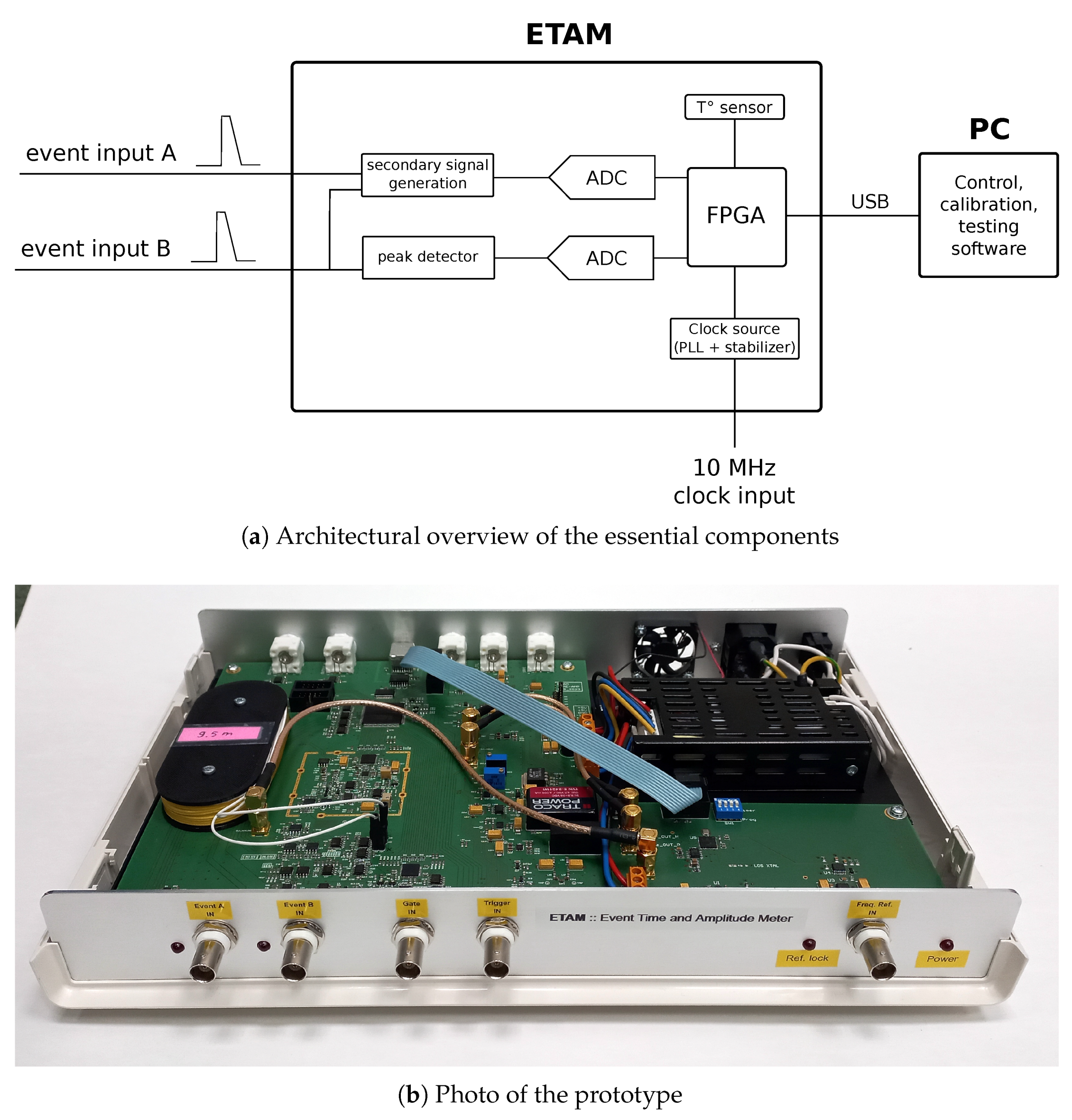

We present the ETAM (Event Time and Amplitude Meter) (

Figure 1): a next-generation ET with built-in amplitude measurement functionality. It features two novel contributions:

- 1.

Adaptive compensation of the measurement error based on temperature readings, with the goal to increase measurement stability under ambient temperature changes.

- 2.

Integration of a peak-detector-based circuit for accurately determining the amplitude of nanosecond-duration pulses with low dead time.

Previous ET models require recalibration whenever their operating temperature changes. The ETAM includes a temperature sensor and uses a dynamic compensation method parameterized by the timer’s internal temperature. The method uses calibration tables built during the manufacturing process, which cycles the ETAM through a range of temperatures in a controlled manner. This method ensures high stability under changing ambient conditions.

The ETAM (

Figure 1) supports two analog inputs with user-configurable event-detection thresholds and polarities (i.e., detecting either rising or falling edge), in contrast with the previous ET which supported only digital inputs. In addition, a high-stability 10 MHz clock input is required for accurate measurements, although the ETAM also includes an internal crystal oscillator and can be operated without this external clock. The signal processing in the ETAM is based on a high-accuracy analog-to-digital converter (ADC) and a powerful Field Programmable Gate Array (FPGA). Finally, the ETAM is connected to a controller PC through a standard USB 2.0 interface, providing a convenient and flexible means of data transfer and measurement control.

Experiments show that the ETAM achieves a 2.1–2.4 ps RMSD in a stable environment. We evaluated the ETAM’s architecture in a temperature chamber and found that its timing precision stability is high, with a <3 ps RMSD in the 5–40 °C range. In terms of amplitude measurement, ETAM decreases the dead time to around 40 ns, and achieves an accuracy of 2.3 mV RMSD for pulses with duration between 700 ps to 100 ns. These results are all improvements over previous-generation ET and will enable higher accuracy SLR measurements and other applications.

The paper is structured as follows:

Section 2 presents a background on Event Timers.

Section 3 presents the evolution of the ETAM, its design, operation and performance summary.

Section 4 describes the measurement stabilization method that allows accurate results to be achieved in a wide range of operating temperatures.

Section 5 covers the amplitude measurement technique used in the ETAM. Finally,

Section 6 concludes the paper.

3. ETAM: Next Generation Event Timer

3.1. Design of the ETAM

Figure 1a shows a high-level non-comprehensive schematic overview of the ETAM. It has two event inputs

A and

B and one 10 MHz reference clock input (some non-essential inputs and outputs are not shown in the image). The external clock is expected to be extremely stable in order to achieve the specified timing precision. In the absence of an external clock, the internal crystal oscillator can also be used; however, high precision is then not guaranteed. The 10 MHz clock input, if present, is up-converted in the internal Phase Locked Loop (PLL) to a 100 MHz clock source, which is supplied to the FPGA and other digital logic in the device. The stabilized PLL is implemented on a daughter-board connected with the main board of the ETAM via extension headers for control interface and coaxial cables for clocks.

The main board of the ETAM features all the components required digital and analog signal processing logic. There is a secondary signal generation circuit; following the EET principles, it is used to create a fixed-parameter signal. The event input

B is also connected to a peak detector circuit (

Section 5). ETAM measures the amplitude of events by digitizing the peak-detected signal. This built-in amplitude measurement functionality allows to correct the timing interval measurement results in a post-processing step, as well as to record additional information about the event itself. Two high-speed ADC circuits (12 and 14 bit) are present for sampling the secondary signal and the peak-detectors output, respectively. The ADC are controlled by a FPGA chip (Intel/Altera Cyclone III), which in turn is driven by the system clock coming from the PLL daughter-board. Finally, the main board features a communication interface (USB 2.0) between the FPGA and the PC, which controls and receives measurements from the ETAM.

A noteworthy feature is the on-board temperature sensor, implemented via an off-the-shelf integrated circuit. Its design requirements are rather low, approx. ±0.25 °C precision and ±1 °C accuracy, due to the fact that the temperature sensor is used to compensate for event timing precision and accuracy drift, which by themselves are rather stable in temperature and would not benefit from higher accuracy temperature measurements. The secondary purpose of the on-board temperature sensor is to monitor device temperature during testing, where a higher accuracy external sensor can be used if necessary.

3.2. ETAM Operation

The following is a brief summary of event processing with the ETAM. The starting point is when an event arrives on one of the inputs A or B. When the input amplitude exceeds a preconfigured threshold, the secondary signal generation circuitry kicks in and generates a triangle-shaped analog signal on its output. If the event has arrived on the input B, the peak-detector circuit is enabled and starts its sample-and-hold operation. It outputs a signal corresponding to the maximum of voltage on input B.

The ETAM is controlled by an FPGA chip, which also samples the ADC. Sampling of the secondary signal is triggered by the signal level reaching a preconfigured threshold, while ADC sampling of the peak detector output is triggered by trailing edge of the pulse input signal. After sampling of both has been completed, the FPGA resets the the peak detector (the timing circuit is self-resetting).

Once the event is detected, the next step is to compute the timestamp of the event. The timestamp consists of two parts (

Section 2.1). The coarse-grained part is the number of system clock ticks since the star of the timer. The fine-grained part is the offset of the event with respect to the system clock tick where it took place. This part is obtained via a lookup in a calibration table. The table maps each possible above-threshold value from the ADC to a timing offset. The details of the calibration process (i.e., how the table is constructed) are described elsewhere, for instance [

8] presents one method to calibrate an Event Timer.

The FPGA also continuously monitors the internal temperature, and when a significant deviation is detected, the host software replaces the current calibration table with the one that matches the current temperature (

Section 4).

Finally, the PC to which ETAM is connected receives the stream of timestamps, and using its control and measurement software, applies another set of corrections (e.g., based on the amplitudes of the events). It then expresses the time stamp in a relevant time scale, such as UTC or PC system time.

3.3. ETAM Performance

Table 1 shows the expected performance of the ETAM, based on preliminary test results. The results demonstrate improvements both in timing precision and in temperature stability. Moreover, the ETAM features reduced dead-time for the timing measurement itself, not to mention the additional amplitude measurement functionality.

4. Measurement Error Stabilization

4.1. Overview

The EET method requires a calibration function

that converts ADC readings to fine-grained timestamps. This function is implemented as a lookup table, using the fact that only a finite number of ADC readings are possible. At the core, the construction of a single ETAM calibration table happens the same way as for the previous-generation Event Timers [

8]. However, previous-generation ET require a recalibration whenever environmental temperature changes, in order to maintain precise timing, due to the fact that the shape of the secondary signal is affected by environmental conditions.

In contrast, the ETAM production process now includes the creation of numerous different calibration tables, one for each potential operating temperature, with one-degree Celsius interval. More formally, during the production process the ETAM’s manufacturer is building a set of functions parameterized by a temperature parameter T. This parameter T takes values from the set °C, where is the minimum expected operational temperature and is the maximum.

During operation, the ETAM monitors its internal temperature using a built-in temperature sensor (

Figure 1a). Whenever the ETAM detects a shift greater than 0.5 °C from the calibration temperature of the current table, it switches to another table, better corresponding to the new operational temperature. If the temperature goes below the expected minimum expected operational temperature, the table for

is used; similarly, the

table is used for temperatures above

.

The calibration tables are presently stored in the non-volatile memory of the PC that controls the ETAM. This is due to their relatively large size: tens of kilobytes per table for a 14-bit ADC. We are exploring alternative methods, such as polynomial approximation and other compression techniques, to make it possible to fully store all calibration settings in the on-board FPGA.

4.2. Metrics

The main stability metrics of an Event Timer are:

precision drift: changes in random error with changes in ambient temperature;

epoch drift: shift in time scale with changes in ambient temperature;

offset drift: change of relative delays of input channels with changes in ambient temperature.

Previous-generation ET has features for stabilizing each of these parameters to some extent, however field applications with environments significantly harsher than climate-controlled laboratory, such as on-site optical cable monitoring, still pose a serious challenge for measurements with high precision and accuracy requirements.

Precision is currently stabilized by the self-calibration procedure and construction of many calibration tables, as described above. Additionally, the ETAM features a new ADC chip in the time-to-digital conversion circuitry, and the rest of the circuitry has received a major update, leading to a significantly more stable gain.

Epoch drift in the earlier ET models is passively compensated in hardware, by carefully selecting a thermistor for each unit. The new ETAM corrects both for the precision decrease (random error) and epoch drift (systematic error) with changing temperatures using the same method, the multiple table-based calibration approach. However, both the new and the old method does not account for component aging, and so requires periodic re-calibration throughout the lifetime of the device. The improved interpolation circuit discussed earlier is also expected to have a positive, albeit small effect on epoch stability.

Offset drift is mitigated by circuit design—the two ETAM input channels are made as similar as possible and are joined into one signal path as early as possible. This design approach, in combination with use of high-speed integrated circuits, makes propagation delays for each channel, and, consequently, their difference, very small: on the order of a nanosecond. The resulting inter-channel delay (i.e., offset) stability is proportional to the delay itself with values of <200 fs/°C, which is negligible compared with offsets introduced by the external equipment.

4.3. Performance Evaluation

During the experiments, the ETAM under test is placed in a thermal chamber and the rest of equipment outside it (

Figure 4). Tektronix AFG-31252 arbitrary function generator is used to generate the calibration and testing signals. The signal is generated in two channels, connected to the ETAM’s input channels A and B. The period between pulse events is set to 10 ms, amplitude to 2.5 V, width to 100 ns. Channel B has a 700 ns lead delay. The experiment consists of two stages described below.

4.3.1. Calibration Table Collection

The Event Timer and PC software executes the following algorithm:

- 1.

Set temperature chamber to a predefined temperature, with a 1 °C step.

- 2.

Wait while the T° in the chamber matches the preset value.

- 3.

Run the calibration procedure using the generator’s signal as a reference.

- 4.

Save the calibration table for the specific temperature.

4.3.2. Timing Precision Testing

The Event Timer and PC software executes the following algorithm:

- 1.

Set temperature chamber to a predefined temperature, with a 0.5 °C step.

- 2.

Measure the T° in the thermal chamber and the internal T° of the ETAM.

- 3.

Apply the calibration table corresponding to the internal T° of the device.

- 4.

Accumulate 4000 time measurements in a batch.

- 5.

Save, process and display the measurement results.

The summary results of the tests are provided in

Table 1.

Figure 5 shows the dependence on the precision error on the temperature for the ETAM and the previous-generation event timer. The previous-generation timer has a clear dependence between the error and the internal temperature. In contrast, the ETAM has nearly constant error in the intra-channel event timing (input A to A), and small error in the inter-channel event timing (input A to B). These are preliminary results of the first prototype, and it is likely that the increase inter-channel error will be reduced in the future.

5. Amplitude Measurements

5.1. Motivation

The measurement of amplitude for short pulses poses a significant technical challenge. To accomplish this, the Riga Satellite Laser Ranging (SLR) station currently utilizes a combination of Event Timing technology and an Amplitude-to-Time Interval Converter (ATIC) [

19,

21]. The ATIC effectively converts the pulse amplitude into a proportional time interval, which can then be measured using an event timer. However, this method has the drawback of a relatively long dead-time, which typically falls within the range of microseconds.

The new pulse amplitude measurement technology implemented in ETAM reduces it to approximately 40 ns, an order of magnitude improvement compared with the ATIC. Instead of the amplitude-to-time interval conversion, the ETAM employs a high-speed peak detector to capture the pulse amplitude at a higher rate. The dead time for event timing itself also is slightly reduced compared with the previous-generation Event Timers (

Table 1). Moreover, the ETAM simplifies the application of Event Timers in the SLR domain and has the potential to reduce costs, due to this integration of amplitude measurements and timing in a single device.

5.2. Overview

Direct conversion of pulses with a duration of < 2 ns is currently impossible in a cost-efficient way, because this requires an ADC with a sampling frequency on the order of a GHz. If a peak-detector is used instead, it stores the maximum amplitude of the input pulse and holds it for a time sufficient for its digitization with a much slower ADC.

Figure 6 shows a simplified circuit of the peak detector. In essence, it is of conventional topology first described in [

17] and, more recently, in good detail, in [

18]. In our work it has been updated with modern high-speed operational amplifiers. The ETAM’s peak detector circuit is composed of two buffer stages. The first one (OA

) is characterized by its high-speed operation, and low output resistance (output capability to quickly charge the storage capacitor C

). The second one (OA

) is characterized by its high input resistance, low input offset voltage and offset current. The circuit also includes a storage capacitor (C

) that exhibits minimal charge leakage, a Schottky diode (D) with high-frequency capabilities of up to 12, GHz and small parasitic parameters, as well as a reset circuitry.

The circuit functions by tracking the input signal voltage (V) and maintaining the peak value of the signal on the output (V) until it is reset by the reset circuitry. This feature enables the use of a slower ADC for capturing and digitally processing the output signal. However, this circuit has certain limitations. The bandwidth limitations of the circuit components significantly affect pulses with widths less than 10 ns. Additionally, the voltage drop across D restricts the minimum pulse amplitude that can be captured. Furthermore, the nonlinearity of D introduces substantial pulse width dependency, thereby impacting precise amplitude measurements.

5.3. Performance Evaluation

In order to evaluate the performance of the peak-detector for pulse amplitude measurement, we use an experimental amplitude measurement device (AMD) based the peak detector circuit (shown in

Figure 6) with a high-precision pulse generator (Tabor Electronics WS835), which can generate arbitrary nanosecond duration pulses.

A single input pulse (or an input pulse with a low repetition frequency) is fed to the AMD from the generator as a source. To characterize the AMDs amplitude measurement performance, an iterative approach is used, where a parameter of the pulse is iteratively changed in a predefined range of values.

5.3.1. Dependence on Pulse Amplitude

The experiment consists of feeding the ETAM pulse signals with fixed parameters and variable amplitude in the operational range from −2 V to −0.05 V (−50 mV).

Since the generated pulse amplitude may deviate from the generator settings, a precise digital multi-meter is used to establish the relationship between generator signal settings and generated voltage. This enables more precise mapping of pulse amplitude settings to their corresponding generated pulse amplitudes , accounting for any potential deviations from the generator’s settings. The measurement error here is defined as , where is the measured amplitude and the reference (“true”) amplitude.

In the experiments, pulses with an amplitude greater than mV were not detected by the AMD. Therefore, it is recommended to limit the range of input pulse amplitudes to between −2 V and −100 mV in order to ensure accurate pulse amplitude registration.

The measurement error within the defined input pulse amplitude range is depicted in

Figure 7. Across the entire range, the difference fluctuates by approximately 80 mV. Nevertheless, a 5th order polynomial fitted to the results provides a reliable approximation of the systematic error. The resulting absolute error is <4.5 mV after compensation.

5.3.2. Dependence on Pulse Width

In this experiment, the pulse width setting

is varied between 1 ns and 100 ns. The amplitude is fixed to 1 V. As shown in

Figure 8, in the range 2 ns

100 ns the measurement uncertainty is approximately ±35 mV. By using a ninth-order polynomial to compensate for systematic error, the measurement uncertainty could be reduced to approximately ±4 mV. Furthermore, considering the aforementioned approximation and assuming a pulse width precision of ±100 ps, the estimated precision is approximately ±1 mV.

5.3.3. Dependence on Pulse Leading Edge Duration

In this experiment, the goal is to check how the duration of the leading edge of the event impacts the measurement results. To evaluate this, the time of the leading edge for 1 V pulse was changed in the range from 1 ns to 1000 ns (1 s).

For the prototype used in tests, long (>100 ns) leading edge compromises stability of operation of the high-speed comparator integrated circuit, which is used to detect the incoming signal. As shown in

Figure 9, this leads to a system malfunction and high apparent measurement error. If application requires working with such slow signals, stability can be easily improved by increasing hysteresis of the comparator circuit. Other than that, the influence of leading edge duration on the measured pulse amplitude is small: ±20 mV for leading edge duration in the 1 to 100 ns range.

5.3.4. Summary

Table 2 shows a summary of the performance. In addition to the experiments presented in detail above, we also study the impact from the trailing edge, period, and delay after enable. To summarize the discoveries and recommendations for the future work:

- 1.

High-accuracy reference for input pulse amplitude is required for calibration of the measurement device.

- 2.

Modification of the peak-detector’s clear-time setting could be used to reduce the lower limit of input pulse period.

- 3.

Extremely slow input pulse leading edges are causing faulty sampling of the peak detector output.

- 4.

The influence of the input pulse leading edge on the measurement results may be related to the pulse signal overshoot in the peak detector.

- 5.

The accuracy and uniformity of pulse amplitude measurements could be improved by processing more ADC samples from the peak detector’s output.