Abstract

This paper presents a low-complexity multi-size circular-shift network (MCSN) structure for 5th-generation (5G) New Radio (NR) quasi-cyclic low-density parity-check (QC-LDPC) decoders. In particular, a fine-coarse approach-based multi-size cyclic shift network, which decomposes the cyclic shift size into fine part and coarse part, is introduced. The proposed MCSN structure is composed of a pre-rotator performing the fine part of the cyclic shift, and a main rotator executing the coarse part of the cyclic shift. In addition, a forward routing circular-shift (FRCS) network, which is based on the barrel shifter and the forward routing process is presented. The proposed switch network is able to support all 51 different submatrix sizes as defined in the 5G NR standard through an efficient forward routing switch network and help reduce the hardware complexity using a cyclic shift size decomposition method. The proposed MCSN is analyzed, and indicates a substantial reduction in the hardware complexity. The experimental results on TSMC 65-nm CMOS technology show that the proposed MCSN structure for 5G NR LDPC decoder offers an area saving up to 56.75% compared to related works in the literature.

1. Introduction

Low-density parity-check (LDPC) codes [1], which were first proposed by R. Gallager in the early 1960s and rediscovered by MacKay and Neal [2] in 1996, have received significant attention thanks to their powerful error correction capability. Recently, LDPC codes have been adopted in the enhanced Mobile Broad Band (eMBB) as the error correction coding scheme for the fifth generation (5G) data channel [3]. The 3rd Generation Partnership Project (3GPP) introduced two rate-compatible base graphs, BG1 and BG2 [4], to support the rate compatible and scalable data transmission. Accordingly, several studies have been conducted on the 5G New Radio (NR) LDPC codes [5,6,7,8]. In [5], an adaptation of the MinSum decoders for the LDPC used in the eMBB scenario in the 5G mobile networks is proposed. In [6], a hardware-friendly LDPC decoding schedules for 5G hybrid automatic repeat request applications is presented. An algebra-assisted method for constructing 5G LDPC codes can be found in [7]. An efficient encoding method and a high-throughput low-complexity encoder architecture for the 5G NR standard is presented in [8].

In recent years, research on LDPC codes has centered around structured LDPC codes known as the quasi-cyclic low-density parity-check (QC-LDPC) codes [9,10,11,12,13], which have demonstrated great advantages over other types of LDPC codes in terms of hardware implementation and excellent error performance over noisy channels. In QC-LDPC codes, the parity-check matrix consists of either cyclic permutation submatrixes or zero matrixes of the same size, determining the interconnection between the check node processing units (CNUs) and variable node processing units (VNUs). The interconnection network for the QC-LDPC codes is highly structured and can be characterized by the submatrix size and the circular-shift value of each cyclic permutation submatrix. The decoding process of a QC-LDPC code requires circular-shift network (CSN) because of its cyclic characteristic. However, a QC-LDPC decoder for emerging wireless communication systems must support multiple code rates, various block lengths, and different submatrix sizes. The QC-LDPC codes adopted by the WiMAX standard (IEEE 802.16e) [14] supports 19 different submatrix sizes with four distinct code rates and six different class codes (distinct distributions of the number of variable nodes per column of check nodes per row). The submatrix sizes vary from 24 to 96. In the 5G NR LDPC code specification, 51 different lifting sizes are defined, and there are eight different permutation matrix designs per base graph [4]. For this reason, the switch network between CNUs and VNUs should be reconfigurable to support any submatrix sizes defined in the standards of applications. A switch network with varying sizes is called a multi-size circular-shift network (MCSN).

Over the past few years, various works have been introduced in order to improve the signal congestion and hardware complexity of the MCSN for QC-LDPC decoders [15,16,17,18,19]. Benes network [15], which is capable of routing any permutation where Z is a power of 2, is a widely used structure. Benes network has been proven to be an optimal non-blocking permutation network. The main drawback of this method is its long critical path and high complexity, which makes it less efficient for implementation with the large size of submatrixes. One of the simplest approaches is assigning a multiple-input multiplexer (MUX) to each output. A MUX is assigned to an output, and each MUX has as many inputs as the number of input data items of the MCSN. This method suffers from high complexity since very wide-input MUXs is required. To overcome the overhead incurred by wide-input MUXs, Rovini [16] proposed a pre-rotator structure, in which small pre-rotators reduce the input width of the MUXs considerably. Furthermore, many other structures have been presented such as: rotator-in-series (RIS) structure [17], rotator-in-parallel (RIP) structure [16,18], and fine-coarse (FC) structure [19]. However, the switch network structures in [15,16,17,18,19] are not suitable for 5G NR LDPC decoders where the submatrix sizes cover a very wide range from 2 to 384. To overcome the limitations of those approaches, this paper considers the design of low-complexity multi-size circular-shift network for 5G NR LDPC decoders, which requires significantly low hardware complexity compared to the conventional architectures. To the best of our knowledge, this is the first work proposing a low-complexity MCSN for the 5G NR LDPC decoders in the literature.

This paper targets the design of a novel low-complexity MCSN structure for 5G NR LDPC decoders using the fine-coarse approach. The proposed MCSN architecture can support all the cyclic shifts for all submatrix sizes defined in the 5G NR standard. The simulation results show that the area of the proposed structure is reduced more than 18% compared to the existing works. Therefore, our study provides a promising multi-size cyclic-shifter design for 5G NR LDPC decoders.

The rest of this paper is organized as follows. Section 2 gives a brief overview of the characteristics of 5G NR LDPC codes and outlines the conventional LDPC multi-size cyclic-shifter structures in the literature. A novel low-complexity MCSN architecture is described in Section 3. Section 4 presents the implementation results and comparison. Finally, conclusions are drawn in Section 5.

2. Multi-Size Circular-Shift Network for 5G NR LDPC Decoder

2.1. 5G NR LDPC Characteristics

QC-LDPC codes play a crucial role in 5G communications. In the 3GPP standard meeting, QC-LDPC codes were accepted as the channel coding scheme for 5G eMBB data channel. The brief structure of NR LDPC base graph is illustrated in [8]. In particular, the columns of the base graph are partitioned into three parts: information columns, core parity columns, and extension parity columns. The rows of the base graph are divided into two parts: core check rows, and extension check rows. Specifically, the base matrix consists of five submatrixes: (1) submatrix A is reserved for systematic bits; (2) submatrix B, a square matrix with dual-diagonal structure, corresponds to the first set of parity bits; (3) submatrix O is an all-zero matrix; (4) submatrix C corresponds to single parity-check (SPC) rows; and (5) an identity matrix I corresponds to the second set of parity bits. The combination of submatrix A and submatrix B is defined as the kernel, and three submatrixes O, I and C are called extensions. This code structure is similar to the Raptor-like extension as described in [20].

The 3GPP has agreed to consider two rate-compatible base graphs, BG1 and BG2, which have a similar structure for the channel coding. While BG1 is designed for larger block lengths and higher rates , BG2 is targeted for smaller block lengths and lower rates . The exact usage of base graphs and the definition of the two matrixes can be found in the 5G NR standard specification [4].

2.2. Multi-Size Circular-Shift Network

In addition to computation units, the switch network is an essential element which occupies significant portion of the LDPC decoder area. In QC-LDPC codes, the parity-check matrix is composed of cyclic permutation submatrixes that determine the interconnection network between the CNUs and VNUs. Accordingly, the decoder needs to circularly shift an array of Z messages where Z being the size of the submatrix, also referred to as block size. QC-LDPC codes simplify the switch network by a great deal as the requirement of all random shifting (or permutation) is eliminated and only cyclic shifting is required.

In many modern communication standards, the LDPC codes are defined for different codeword lengths and block sizes , with , where K is the number of admissible sizes. Therefore, an MSCS network, which is capable of circular shift over an arbitrary number of data, is mandatory. An MSCS network block rotates a specified amount of data. If Pw-bit data are inputted with a shift size Z and circular-shift amount c, the first Z input data are rotated by c to produce the output . The output data beyond the specified size of Z are redundant. The sizes and shift amounts are determined by the adopted QC-LDPC codes.

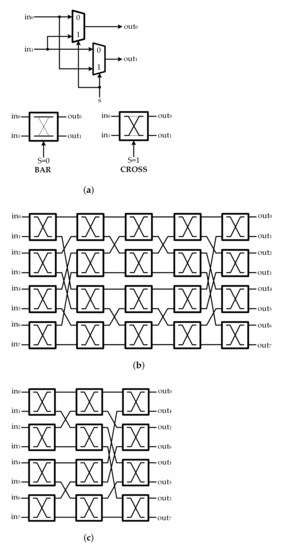

Generally, the Benes network is a very well-known non-blocking multistage interconnection network. A Benes network is capable of performing any desired permutation over P data units, where the input size P of the Benes network is a power of 2. The network comprises of stages of switches. Each switch element consists of two 2-input MUXs and can operate either in the BAR or in the CROSS state, as depicted in Figure 1a. An example of a Benes network with P = 8 is shown in Figure 1b. The switch network designed for QC-LDPC decoders is generally optimized for a given size of permutation matrix with the Benes network. To properly control all the switch units and realize the desired permutation result, the control signals for all switches must be provided. Those control signals are pre-computed and stored in a dedicated LUT. However, as the submatrix size increases, the required size of LUT becomes a dominant area consuming factor. Therefore, the Benes network with a large size of submatrix is inefficient as it suffers from significant hardware overhead. Furthermore, Benes network offers a limited application, as the number of inputs should be a power of 2.

Figure 1.

(a) Benes network switch; (b) Benes network when P = 8; (c) Banyan network when .

For the QC-LDPC decoders, switch networks are only required to implement the circular shifts. It was shown that only the first or last stages of the P input Benes network are needed to perform all cyclic shifts for P inputs [21]. Therefore, the implementation of the half or reduced Benes network referred to as Banyan network [22] in Figure 1c, is a preferable switching network structure. When the submatrix size is not a power of 2, it is possible to use an Banyan network where . However, an additional multiplexing stage must be carried out either at the switch network input or output. In recent years, many techniques were proposed to modify the Benes network to make it more efficient for the reconfigurable QC-LDPC decoders [15].

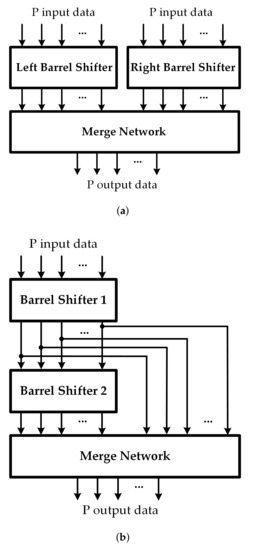

The MSCS network structures can be implemented with typical barrel rotators. The structures exploit two barrel rotators which can be placed in parallel [23] or in series [17], as shown in Figure 2a,b, respectively. The output data of the MSCS network are combined from the outputs of two barrel rotators. In the Rotator-In-Parallel (RIP) structure [23], the left rotator performs the left shift by c to the input data, and the right rotator performs the right shift by to the input data. After that, the obtained results from the barrel rotators are combined by MUXs to become the output data. In the Rotator-In-Series (RIS) structure, the first barrel rotator, rotates the input data by c. The result obtained from the first barrel rotator is then rotated by the second barrel rotator in the same direction by [17]. In addition, the output data are selected from the outputs of the barrel rotators and then combined by MUXs to become the output data. One of the most straightforward ways to employ an MSCS network block would be using a MUX network. An P-to-1 (w-bit) MUX can be used to connect P inputs to an output since the output data can be selected from P input data. The main drawback of this structure is that many wide-input MUXs are required. These wide-input MUXs are normally implemented by cascading a lot of 2-to-1 MUXs.

Figure 2.

(a) RIP structure; (b) RIS structure.

To improve the performance of the MUX network structure, Rovini [16] introduced a pre-rotator structure exploiting the size-common-divisor property, as shown in Figure 3. The input data are rotated by pre-rotators so that the amount of input data is the greatest common divisor (GCD) of all block sizes before being processed by a MUX network. More precisely, with the maximum block size P, the MSCS network is composed of g-input pre-rotators and additional stage of P -to-1 MUXs, also referred to as adaptation network (AN), where g is the GCD and . This structure substantially reduces the MUX input width from P to g. However, the MUX network still occupies a significant area. Specifically, the equivalent number of 2-to-1 MUXs is , where the first term and the second term are for the pre-rotators and the MUX network, respectively. In [19,24], the MUX network in the AN is substituted with the Benes network and the RIP structure, respectively, to enhance the complexity of the MSCS network block.

Figure 3.

Pre-rotator and MUX network structure.

The previous MSCS network structures are proposed to support multiple submatrix sizes in the QC-LDPC decoders. However, previously proposed structures are not suitable for 5G NR LDPC decoders where the submatrix size varies largely from 2 to 384. The considerable variation in submatrix sizes would result in the high inefficiency in hardware use and the high complexity in the interconnecting network in conventional switching network structures. To overcome the limitations of existing MSCS network structures, the design considered in this paper, referred to as low-complexity multi-size circular-shift network for 5G NR LDPC decoders, requires significantly low hardware complexity compared to conventional structures.

3. Proposed Low-Complexity Multi-Size Circular-Shift Network for 5G New Radio LDPC Decoder

3.1. Modified Lifting Size Table for 5G New Radio LDPC Codes

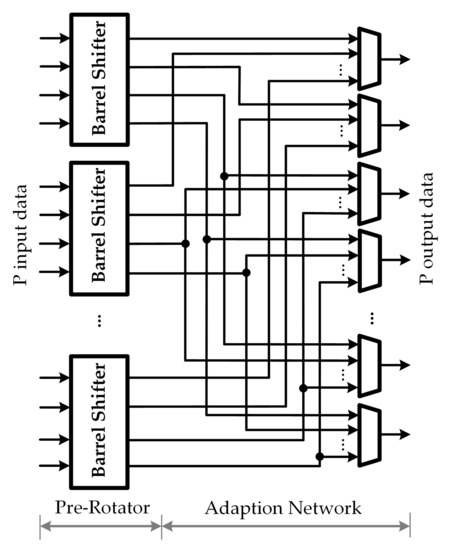

LDPC codes for the 5G NR wireless communication standard are defined for 51 different lifting sizes Z as shown in Figure 4a. The set of lifting sizes Z supported for the base graph are all values of the form for where and includes all such Z distributed over the range from 2 to 384. The lifting sizes Z can be organized into eight sets, one for each value of a. To make it more convenient for our proposed MSCS network structure, the lifting size table is efficiently modified as shown in Figure 4b. Precisely, the two rows for and 7 are removed from the modified table. Instead, three new columns for , 10, and 12 are created in the table. Accordingly, the value of lifting sizes , 192, 256, 320, and 384 are sufficiently reallocated into new positions in the modified table.

Figure 4.

(a) Lifting size Z table; (b) Modified lifting size Z table for standard 5G LDPC codes.

3.2. Structure of Forward Routing Network

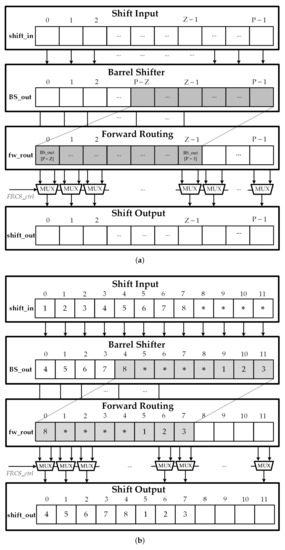

In this section, an efficient reconfigurable message passing network based on the barrel shifter and an additional forward routing stage is presented. Please note that the maximum input size that can be supported by the circular-shift network is P, the block size of the input data for the circular shift is Z, and the value of the required circular shift is c, where . The structure of the Forward Routing Circular-Shift (FRCS) network is illustrated in Figure 5a, which includes 3 stages. The first stage is the barrel shifter, the second stage is the forward routing module, and the final stage is the selection scheme. The barrel shifter with input size P in the first stage can be easily constructed from stages of 2-to-1 MUXs. The barrel shifter circularly shifts the input message according to the specific shift amount c. The control signals for the barrel shift network can be easily determined from the value of the shift amount c. In the next step, the forward routing module simply takes the value of the th to th shifted message as input data and fetches into next stage. The shifted message from the barrel shifter and the forward routing message is fed into the final stage to generate the expected output. The selection stage is in charge of selecting a signal from the barrel shifter or the forward routing network and routing a proper signal to the output. In the selection stage, the expected output message is determined by a MUX network where the control signal is defined as follows:

Figure 5.

(a) FRCS network structure; (b) An example of FRCS network with , and .

According to the controller design, the final output messages comes from the forward routing module if and from the barrel shifter if . An output block with can have any value because its value is ignored in the following blocks. Figure 5b illustrates the operation of the FRCS network with and . The control signal is defined as follows:

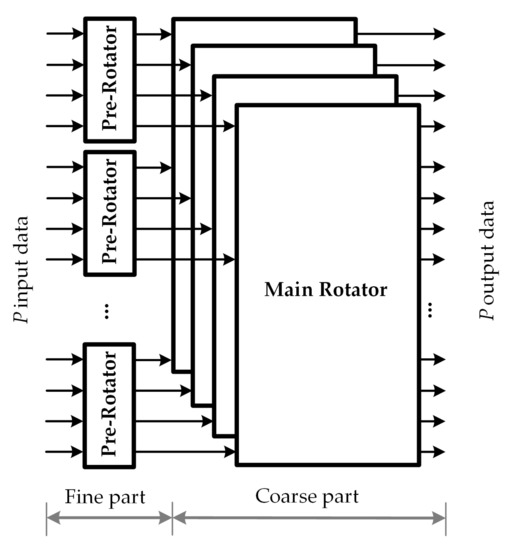

3.3. Fine-Coarse Structure for Circular-Shift Network

The fine-coarse structure for circular-shift network is designed to support different block sizes, in which the maximum block size is defined by P. Let denotes the GCD between all block sizes, and . To support multi circular shifts with low complexity, the proposed low-complexity MSCS network for 5G NR LDPC decoders is decomposed into two parts: the fine part and the coarse part. More precisely, the MSCS network architecture comprises of -input pre-rotators, plus an additional stage of -input main rotators. Let Z denotes the block size of the circular-shift message and c denotes the circular-shift value which is distributed over the range from 0 to . The fine-coarse structure decomposes the circular shift into a pre-circular shift and a main circular shift . The circular-shift amount c can be described by the sum of two terms as , where . In the fine-coarse structure, the output data are generated in two steps, which are listed below:

- Step 1. Pre-rotator: Each sub-block of input data are processed by a pre-rotator subnetwork to generate the pre-circular shift by performing shift operation.

- Step 2. Main rotator: The k-th ouput datum of each pre-rotator network is distributed into the k-th main rotator subnetwork, where . The main circular shift is generated by performing shift operation on each main rotator subnetwork. To overcome the inside-group rotation at the pre-rotator network, the cross-group movement is performed by the circular shift at the k-th main rotator subnetwork where .

As shown in Figure 6, the fine-coarse structure has two components, i.e., the pre-rotator network, and the main rotator network, which corresponds to step 1, and 2 described above. In this structure, the support of multiple sizes is achieved by rearranging the system into smaller subnetwork with fixed block sizes.

Figure 6.

Fine-coarse structure.

3.4. Proposed Low-Complexity Multi-Size Circular-Shift Network

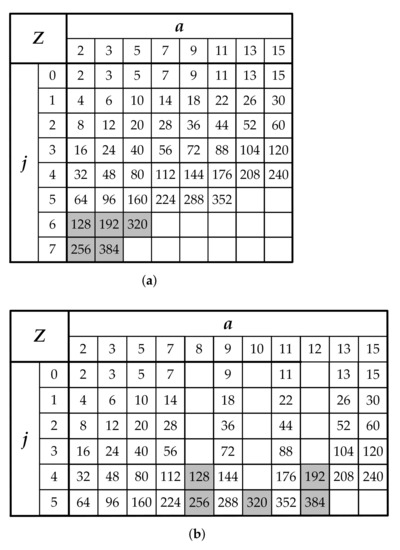

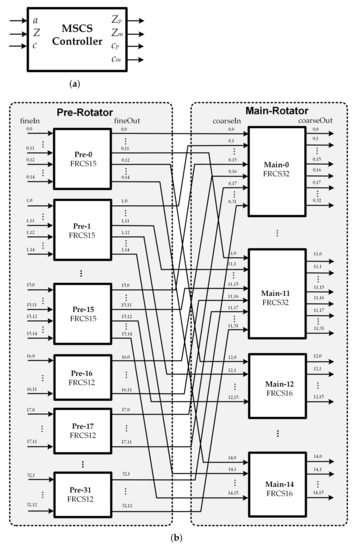

The principal of our proposed low-complexity MSCN structure for 5G NR LDPC decoders is based on the fine-coarse structure and the forward routing network. The design target of the proposed architecture is focused on multi-size message-passing network with lower complexity. In general, the fine-coarse structure decomposes the system into smaller subnetworks with fixed block sizes. The block size of the subnetworks is determined by the GCD of all supported block sizes. For 5G NR LDPC codes, the block sizes vary over a very large range from 2 to 384. In this case, the MSCN structure would be made of 192 2-input pre-rotators, plus an additional stage of 2 192-input main rotators as the GCD is 2. When the size of the submatrix is 384, this approach reduces the hardware complexity compared with the direct implementation using 384 384-to-1 MUXs. However, it still suffers from significant hardware overhead. Therefore, the same technique is not directly applicable in the case of 5G NR LDPC codes. There is a need to accommodate all 51 block sizes while achieving lower complexity. To overcome the drawback, a novel MSCS network architecture based on fine-coarse structure, in which the subnetworks are reconfigurable, is presented in this section. Figure 7 illustrates the proposed low-complexity MSCS network structure. As shown in Figure 7b, the proposed structure can be constructed from two stages of the sub-MSCS network in which FRCS structure is conducted. First, denote the maximum block sizes of the MSCS network is P, the size of the submatrix for the circular shift is Z, and the value of the required circular shift is c. For this fine-coarse structure, and which are the set of maximum block size, the size of the submatrix for the circular shift, and the circular-shift value for the sub-MSCS network in the pre-rotator and main rotator stage, respectively, are further defined.

Figure 7.

Proposed MSCS network structure for 5G NR LDPC decoders: (a) MSCS controller; (b) Two stages of the sub-MSCS network.

Based on the characteristics of the modified lifting sizes Z table in Figure 4b, the pre rotator block can be constructed from 32 FRCSs, named as , in which the first 16 FRCSs (for ) are with input size (FRCS15) and the remaining 16 FRCSs for are with input size (FRCS12). Similarly, the main rotator is decomposed into 15 FRCSs, denoted as . The first to the 12th FRCS (FRCS32) (for ) have the same number of input blocks while the remaining 3 FRCSs (FRCS16) only comprise of input blocks for . In this structure, all the control signals can be implemented with small area and determined on-the-fly. The control signal for the proposed MSCS network would be calculated from the values of P, c and a, as illustrated in Figure 7b. Please note that the values of a in the modified table in Figure 4b are handled instead of the original ones. The MSCS network controller consists of two parts: a circular-shift sizes generator and a circular-shift amount generator. The values of the circular shift sizes for pre rotator and main rotator subnetworks are defined as follows:

In the fine-coarse structure, the circular-shift amount c can be described by the sum of two terms as , where as mentioned in previous section. Therefore, the circular-shift values for the two rotators can be determined as follows:

The MSCS network concurrently routes all messages through the two-stage network. As first, the pre-circular shift with a size of is performed on the Z messages, and then the main circular shift with a size of is finally performed on the result of the pre-circular shift. First, the input data of size Z are evenly distributed among the first pre rotators of the fine part. The rest of the pre rotator stage is ignored. For instance, the first pre rotator takes the first signals from the input messages, the second pre rotator selects the next set of signals, and the last set of signals will be fed into the final pre rotator . Each pre rotator block carries out the circular shift of messages by . Before the main circular shift is exploited, the proper outputs from the pre rotator stage are assigned to the inputs of each main rotator block. In this stage, the jth main rotator block takes all the jth output signal of each pre rotator in previous stage. Similarly, each main rotator block performs the circular shift on the selected -message with the circular-shift value , which is defined in Equation (5). To achieve the final circular shift message, each -message from the first to the th main rotator block is sequentially routed to the output of the MSCS network.

4. Implementation Results and Comparison

Table 1 reports a resource breakdown of the proposed MCSN for 5G NR LDPC decoder. As can be seen from Table 1, the proposed MCSN requires 972,256 adders/subtractors, 483,092 comparators, 732,228 multiplexers and 482,448 logic shifters. The number of adders is about 85% of the number of subtractors. The greater comparator is the majority of the comparators.

Table 1.

Resource Breakdown of Multi-Size Circular-Shift Network for 5G NR LDPC Decoders.

To confirm the efficiency of our solution, we have compared the conventional RIP structure [23], the fine-coarse architecture with MUXs network [16], the fine-coarse structure with RIP network [24] with our proposed MCSN network for multi-size message passing network of the 5G LDPC decoder where the full lifting set Z is given by {2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 18, 20, 22, 24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384}. The proposed MCSN network structures are synthesized using the TSMC 65-nm CMOS technology. The ASIC post synthesis implementation results on are reported in Table 2.

Table 2.

ASIC Implementation Results of Multi-Size Circular-Shift Network for 5G NR LDPC Decoders.

As can be seen from Table 2, the proposed MCSN structure occupies an area of 0.301 mm and works at a high frequency of 580 MHz. Since the proposed work and other architectures are implemented with different parameters such as maximum shift size P, CMOS technology, and the quantization bits, it is necessary to apply performance normalization to 65-nm CMOS technology for a fair comparison. Specifically, the normalization method presented in [25] is used. We also consider the maximum shift size P and the quantization bits in the normalization. From the normalized results, it is confirmed that the proposed solution helps reduce the complexity in comparison to the works introduced in [16,23,24]. Specifically, the area reduction from the RIP structure [23], the fine-coarse architecture with MUXs network [16], and the fine-coarse structure with RIP network [24] are 56.75%, 18.87%, and 49.75%, respectively. The proposed MCSN can be well operated at the high frequency of 580 MHz. Therefore, the proposed MCSN structure is a promising solution to reduce the complexity of the QC-LDPC decoders for 5G NR.

5. Conclusions

In this paper, a novel reconfigurable message-passing network architecture has been proposed for 5G NR QC-LDPC decoders. The proposed MCSN structure using fine-coarse approach with low complexity is capable of supporting 51 different submatrix sizes of the 5G NR standard and exhibits low complexity. Simulation results prove that the proposed MCSN structure requires small area over its predecessors. Therefore, the proposed design is appropriate for applications with multimode QC-LDPC decoders in 5G standard requirements.

Author Contributions

T.T.N. and T.T.B.N. conceptualized the idea of this research, conducted experiments, collected data, and prepared the original version. T.T.N. reviewed, analyzed data, and updated the manuscript. H.L. supervised, validated, reviewed, and supported the research with funding. All authors have read and agreed to the published version of the manuscript.

Funding

This research was supported by the MSIT (Ministry of Science and ICT) under the ITRC support program (IITP-2021-0-02052) supervised by the IITP, and in part by INHA UNIVERSITY Research Grant.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Gallager, R.G. Low-density Parity-check Codes. IRE Trans. Inform. Theory 1962, 8, 21–28. [Google Scholar] [CrossRef]

- MacKay, D.J.; Neal, R.M. Near Shannon Limit Performance of Low-density Parity-check Codes. Electron. Lett. 1996, 32, 1645–1646. [Google Scholar] [CrossRef]

- Session Chairman (Nokia). Chairman’s Notes of Agenda Item 7.1.5 Channel Coding and Modulation. 3GPP TSG RAN WG1 Meeting No. 87, R1-1613710. 2016. Available online: https://portal.3gpp.org/ngppapp/CreateTdoc.aspx?mode=view&contributionId=752413 (accessed on 7 December 2021).

- Ad-Hoc Chair (Nokia). Chairman’s Notes of Agenda Item 7.1.4. Channel Coding. 3GPP TSG RAN WG1 Meeting AH 2, R1-1711982. 2017. Available online: https://portal.3gpp.org/ngppapp/CreateTdoc.aspx?mode=view&contributionId=805088 (accessed on 7 December 2021).

- Le Trung, K.; Ghaffari, F.; Declercq, D. An Adaptation of Min-Sum Decoder for 5G Low-Density Parity-Check Codes. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar]

- Liang, C.; Li, M.; Lee, H.; Lee, H.; Ueng, Y. Hardware-friendly LDPC Decoding Scheduling for 5G HARQ Applications. In Proceedings of the 2019 IEEE International Conference on Acoustics, Speech and Signal Processing, Brighton, UK, 12–17 May 2019; pp. 1418–1422. [Google Scholar]

- Li, H.; Bai, B.; Mu, X.; Zhang, J.; Xu, H. Algebra-assisted Construction of Quasi-cyclic LDPC Codes for 5G New Radio. IEEE Access 2018, 6, 50229–50244. [Google Scholar] [CrossRef]

- Nguyen, T.T.B.; Nguyen Tan, T.; Lee, H. Efficient QC-LDPC Encoder for 5G New Radio. Electronics 2019, 8, 668. [Google Scholar] [CrossRef]

- Ajaz, S.; Nguyen, T.T.B.; Lee, H. An Area-Efficient Half-Row Pipelined Layered LDPC Decoder Architecture. J. Semicond. Technol. Sci. (JSTS) 2017, 17, 845–853. [Google Scholar] [CrossRef]

- Nguyen, T.T.B.; Lee, H. Low-complexity Multi-mode Multi-way Split-row Layered LDPC Decoder for Gigabit Wireless Communications. Integr. VLSI J. 2019, 65, 189–200. [Google Scholar] [CrossRef]

- Ajaz, S.; Lee, H. Efficient Multi-Gb/s Multi-mode LDPC Decoder Architecture for IEEE 802.11ad Applications. Integr. VLSI J. 2015, 51, 21–36. [Google Scholar] [CrossRef]

- Ajaz, S.; Lee, H. An Efficient Radix-4 Quasi-cyclic Shift Network for QC-LDPC Decoders. IEICE Electron. Express 2014, 11, 1–6. [Google Scholar] [CrossRef][Green Version]

- Ajaz, S.; Lee, H. Reduced-complexity Local Switch Based Multi-mode QC-LDPC Decoder Architecture for Gigabit Wireless Communications. IET Electron. Lett. 2013, 49, 1246–1248. [Google Scholar] [CrossRef]

- Jung, Y.; Jung, Y.; Lee, S.; Kim, J. Low-complexity Multi-way and Reconfigurable Cyclic Shift Network of QC-LDPC Decoder for Wi-Fi/WIMAX Applications. IEEE Trans. Consum. Electron. 2013, 2013, 467–475. [Google Scholar] [CrossRef]

- Oh, D.; Parhi, K.K. Low-Complexity Switch Network for Reconfigurable LDPC Decoders. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2010, 18, 85–94. [Google Scholar] [CrossRef]

- Rovini, M.; Gentile, G.; Fanucci, L. Multi-size Circular Shifting Networks for Decoders of Structured LDPC Codes. Electron. Lett. 2007, 43, 938–940. [Google Scholar] [CrossRef]

- Xiang, B.; Zeng, X. A 4.84 mm2 847–955 Mb/s 397 mW Dual-path Fully-overlapped QC-LDPC Decoder for the WiMAX System in 0.13 µm CMOS. In Proceedings of the 2010 Symposium on VLSI Circuits, Honolulu, HI, USA, 16–18 June 2010; pp. 211–212. [Google Scholar]

- Peng, X.; Chen, Z.; Zhao, X.; Zhou, D.; Goto, S. A 115 mW 1Gbps QC-LDPC Decoder ASIC for WiMAX in 65nm CMOS. In Proceedings of the 2011 IEEE Asian Solid-State Circuits Conference, Jeju, Korea, 14 November 2011; pp. 317–320. [Google Scholar]

- Kang, H.-J.; Yang, B.-D. Low-complexity Multi-size Cyclic-shifter for QC-LDPC Codes. ETRI J. 2017, 39, 319–325. [Google Scholar] [CrossRef]

- Chen, T.; Vakilinia, K.; Member, S.; Divsalar, D.; Fellow, L.; Wesel, R.D.; Member, S. Protograph-Based Raptor-Like LDPC Codes. IEEE Trans. Commun. 2015, 63, 1522–1532. [Google Scholar] [CrossRef]

- Benes, V.E. Optimal Rearrangeable Multistage Connecting Networks. Bell Syst. Tech. J. 1964, 43, 1641–1656. [Google Scholar] [CrossRef]

- Tang, J.; Bhatt, T.; Sundaramurthy, V.; Parhi, K.K. Reconfigurable Shuffle Network Design in LDPC Decoders. In Proceedings of the IEEE 17th International Conference on Application-specific Systems, Architectures and Processors (ASAP’06), Steamboat Springs, CO, USA, 11–13 September 2006; pp. 81–86. [Google Scholar]

- Chen, X.; Lin, S.; Akella, V. QSN—A Simple Circular-Shift Network for Reconfigurable Quasi-Cyclic LDPC Decoders. IEEE Trans. Circuits Syst. II Exp. Briefs 2010, 57, 782–786. [Google Scholar] [CrossRef]

- Kang, H.-J.; Yang, B.-D. Low-complexity, High-speed Multi-size Cyclic-shifter for Quasi-cyclic LDPC Decoder. Electron. Lett. 2018, 54, 452–454. [Google Scholar] [CrossRef]

- Li, M.; Naessens, F.; Debacker, P.; Raghavan, P.; Desset, C.; Li, M.; Dejonghe, A.; Van Der Perre, L. An Area and Energy Efficient Half-row-paralleled Layer LDPC Decoder for the 802.11ad Standard. In Proceedings of the SiPS 2013 Proceedings, Taipei, Taiwan, 16–18 October 2013; pp. 112–117. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).