1. Introduction

Energy harvesting technology is considered a key technology for battery-free Internet of Things (IoT) devices [

1,

2,

3]. Since RF signals of various frequency bands such as 5G, Wi-Fi, and TV exist around us, RF energy harvesting can be a very useful energy source [

4,

5,

6,

7,

8]. However, when the available power of the surrounding RF signal is low, the output DC voltage of the RF rectifier is lower than the voltage required by the system, making it difficult to use as a power source. To increase the DC output voltage, a multi-stage rectifier is required, which significantly reduces the efficiency of energy harvesting [

9].

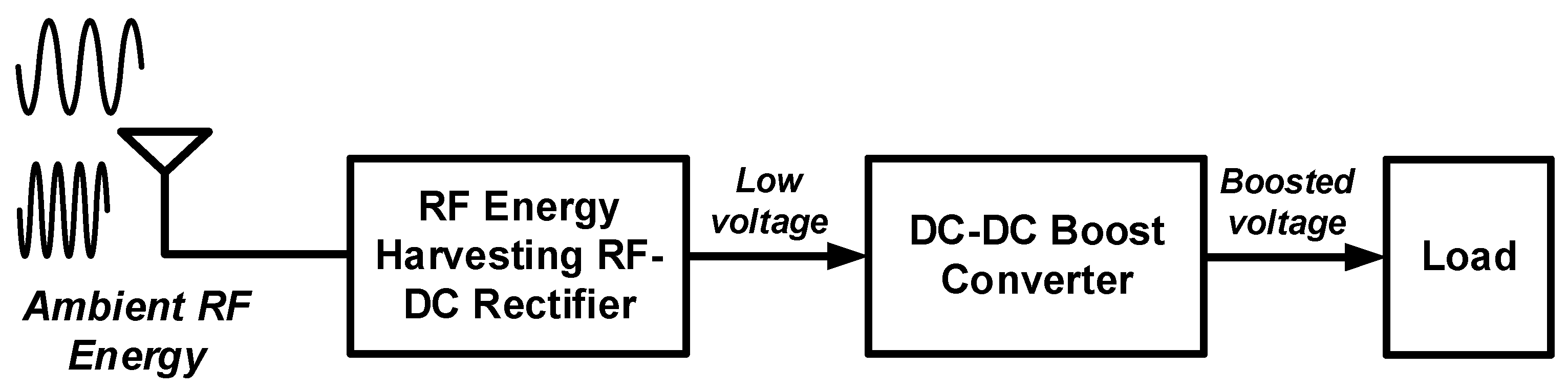

Therefore, the proposed RF energy harvesting system adopts a DC-DC boost converter to convert the low output voltage of the RF-DC rectifier into a high voltage of 1 V or more.

Figure 1 shows a block diagram of an RF energy harvesting system consisting of an RF energy harvesting RF-DC rectifier and a DC-DC boost converter. The power management circuit for RF energy harvesting system consists of an RF-DC rectifier that harvests ambient RF energy and converts it to DC voltage, and a DC-DC boost converter that boosts the voltage to a higher DC voltage and supplies it to the load.

1.1. Main Contribution

Since the output DC voltage of the RF-DC rectifier for RF energy harvesting varies greatly depending on the RF input power, the DC-DC boost converter is required to achieve high power conversion efficiency (PCE) in a wide input voltage range [

4,

5,

6,

7,

8,

9]. Therefore, to obtain high PCE for different input voltages in a wide input voltage range, an optimal design method of design parameters including an optimal peak inductor current design according to the input voltage is required.

In this paper, we propose an optimal design methodology to achieve high efficiency in a wide input voltage range based on loss analysis and modeling of an inductor-based DC-DC boost converter. In the proposed efficiency optimization design methodology of the DC-DC boost converter, each loss component of the inductor-based DC-DC boost converter is analyzed and the loss modeling result according to the design parameters is presented. Based on the loss analysis and modeling, optimum design parameters including inductance and peak inductor current are obtained to achieve the maximum PCE by minimizing the total loss according to different input voltages in a wide input voltage range.

1.2. Organization

This paper is organized as follows.

Section 2 introduces the previous DC-DC boost converters for energy harvesting.

Section 3 introduces the efficiency problem and the system model of an inductor-based DC-DC boost converter.

Section 4 presents loss analysis and modeling of the boost converter.

Section 5 focuses on the design methodology for optimizing power conversion efficiency.

Section 6 highlights the circuit simulation results. Finally, concluding remarks are given in

Section 7.

2. Previous DC-DC Boost Converters for Energy Harvesting

DC-DC boost converters based on transformers, switched capacitors, and inductors are used to convert a low input voltage to a high voltage for energy harvesting applications. The transformer-based boost converter operates at a low input voltage of 21 mV without a separate start-up circuit [

10], but the transformer increases the area and reduces efficiency at low input voltages. Capacitive-based boost converters are advantageous for on-chip integration because they do not require an inductor and have a relatively small physical form factor [

11,

12,

13,

14]. A capacitive-based boost converter with a dynamic body biasing technique that operates at a low input voltage of 0.15 V without a start-up circuit has been demonstrated in [

13]. However, it has a limited voltage conversion ratio and relatively low power conversion efficiency at low input voltage. Inductor-based converters are difficult to integrate on-chip due to off-chip inductors but operate at a relatively low input voltage and achieve high power conversion efficiency in a low input voltage range compared with capacitive-based boost converters [

15].

In recent works, several approaches have been proposed to improve the power conversion efficiency of low input voltage boost converters for thermoelectric energy harvesting [

16,

17,

18,

19,

20,

21,

22,

23]. In [

17,

18], high conversion efficiency is achieved by applying an adaptive gate biasing technique and a peak inductor current control scheme, respectively. However, these designs achieve high efficiency at relatively high input power levels of hundreds of μW or more. In [

19], a loss optimization design for MOS switch width and switching frequency has been reported to minimize the total loss to achieve high efficiency in a DC-DC boost converter. In [

22], an optimization method for finding the optimum switching frequency, inductance value, and switch size of the converter has been reported. However, these methods obtain high efficiency in a specific input voltage range for thermoelectric energy harvesting, and the efficiency is significantly reduced in a wide input voltage range outside this range.

4. Loss Analysis and Modeling of DC-DC Boost Converter

The conduction loss due to the equivalent series resistance (ESR),

RESR,L, of the inductor is expressed as:

The conduction loss of the switches is expressed as the sum of the losses due to the on resistance per unit width of the switches

M1 and

M2,

RM1 and

RM2, respectively, and the losses due to the leakage current per unit width of the switches

M1 and

M2,

ILEAK,M1 and

ILEAK,M2, respectively. The conduction loss due to the switches is expressed as:

where

WM1 and

WM2 are the widths of

M1 and

M2, respectively.

In the DC-DC boost converter, switching losses occur in the transition period by charging and discharging the NMOS and PMOS switch capacitances. The switching loss increases proportionally to the gate–drain capacitances per unit width of

M1 and

M2,

CGD,M1 and

CGD,M2, respectively, with the Miller effect, the drain–body capacitances per unit width of

M1 and

M2,

CDB,M1 and

CDB,M2, respectively, and the parasitic capacitance of the inductor,

CL,PAR, expressed as:

Buffer stages are required as a driver circuit to drive NMOS and PMOS switches. Therefore, in addition to the power consumed to charge and discharge the gate capacitances of the NMOS and PMOS switches,

CGS,M1 and

CGS,M2, respectively, additional power is consumed by the buffer stages. The switching loss of the buffer stages is proportional to the gate equivalent capacitance of

M1 and

M2 with the Miller effect and is expressed as:

Therefore, the total loss of the DC-DC booster converter including conduction loss due to ESR of the inductor, conduction loss due to switches, switching loss of NMOS and PMOS, and switching loss of buffer stages, respectively, expressed in (3)–(6) is as follows.

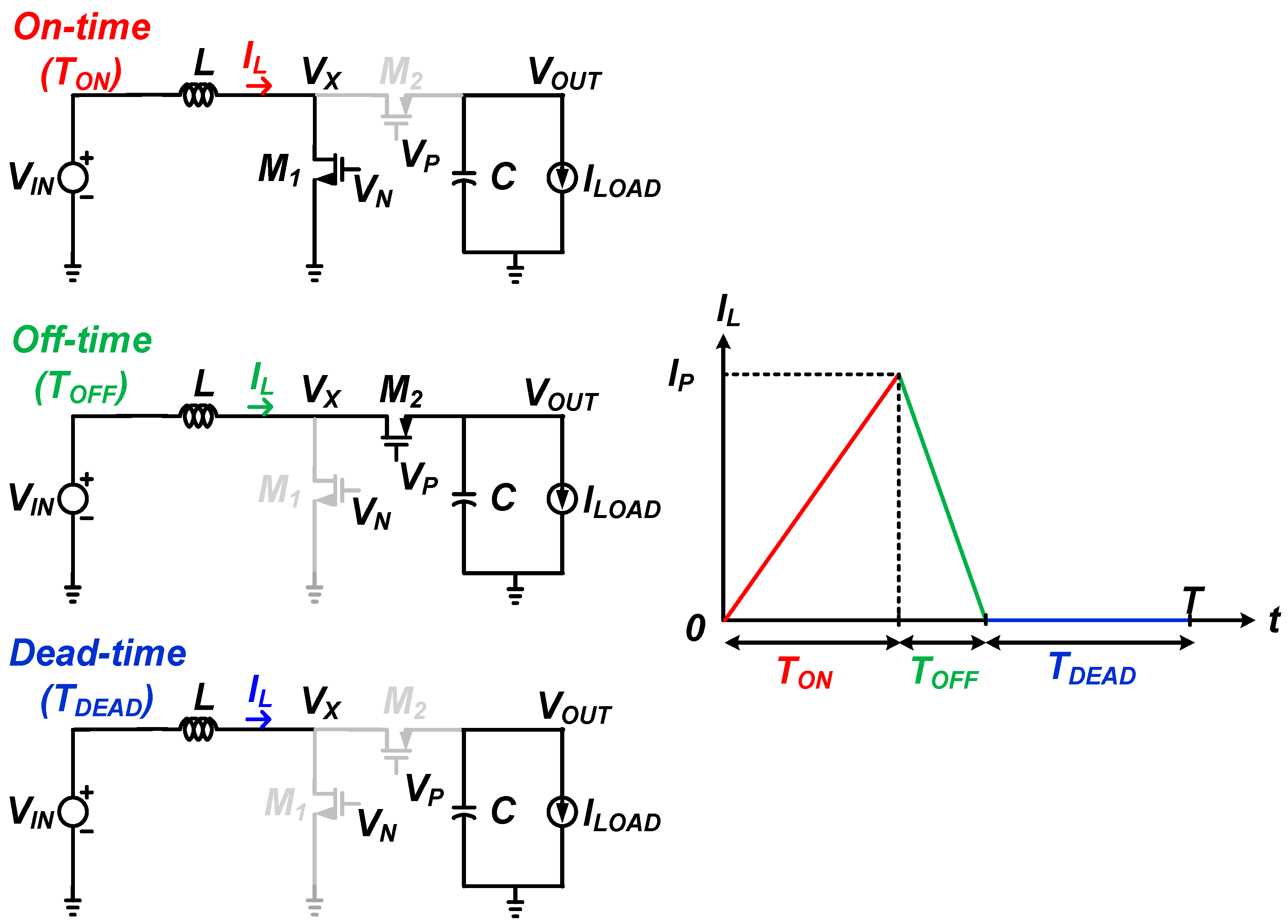

Figure 4 shows the modeling results of each loss component of the boost converter according to the inductance

L using (3)–(6) when

VIN = 0.1 V,

VOUT = 1 V,

ILOAD = 1 mA,

WM1 =

WM2 = 20 mm, and

IP = 30 mA. The inductor is designed as an off-chip component and the DCR of the inductor is modeled as a resistance value that increases with

L. As shown in

Figure 4, as the inductance increases, conduction loss of the inductor increases and switching loss and buffer loss decrease.

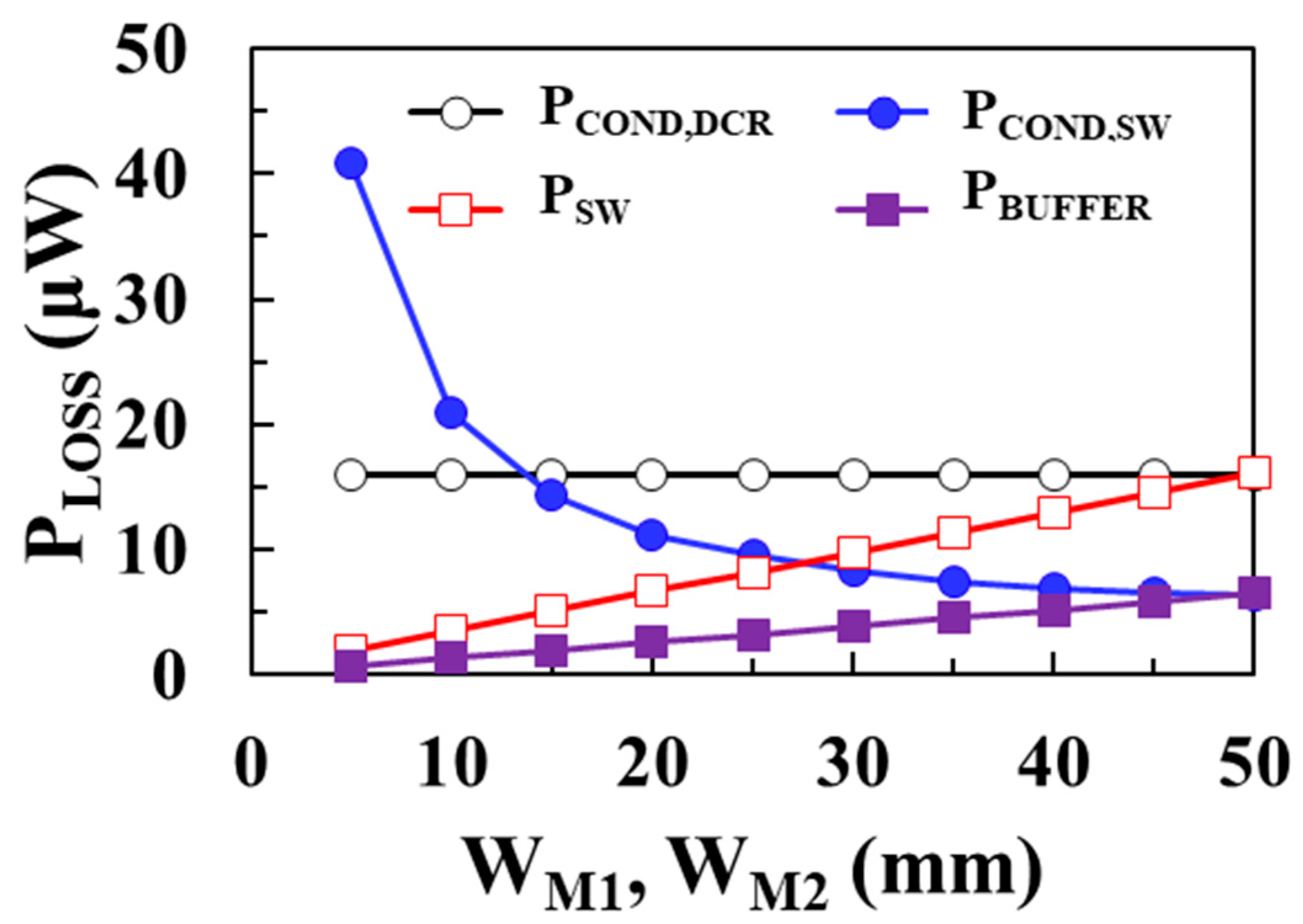

Figure 5 shows the modeling results of each loss component of the boost converter according to the widths of

M1 and

M2 switches using (3)–(6) when

VIN = 0.1 V,

VOUT = 1 V,

ILOAD = 1 mA,

L = 10 μH, and

IP = 30 mA. As shown in

Figure 5, as the width of the MOSFET switches increases, conduction loss of the switches decreases and the switching loss and buffer loss increase.

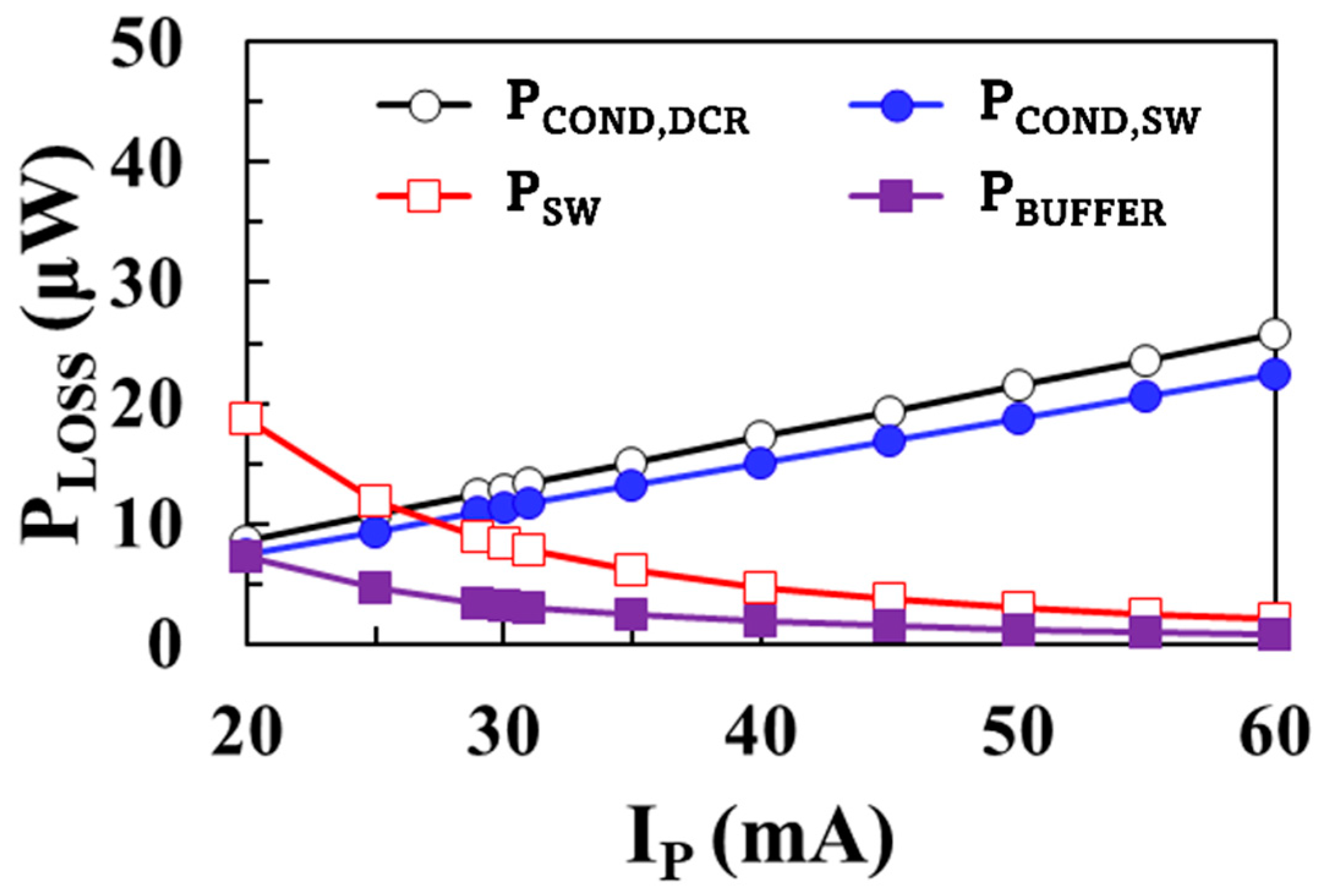

Figure 6 shows the modeling results of each loss component of the boost converter according to the peak inductor current

IP using (3)–(6) when

VIN = 0.1 V,

VOUT = 1 V,

ILOAD = 1 mA,

WM1 =

WM2 = 20 mm, and

L = 10 μH. As the peak inductor current increases, conduction loss of the inductor and switches increase and switching loss and buffer loss decrease.

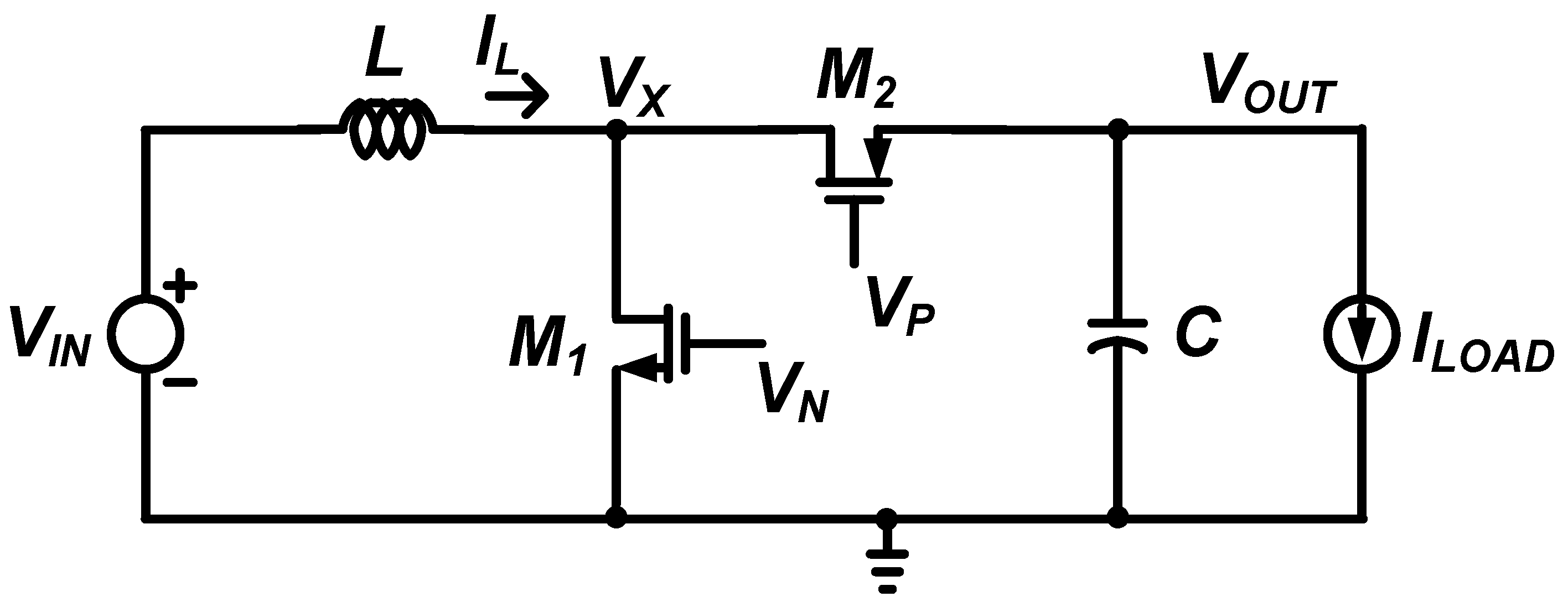

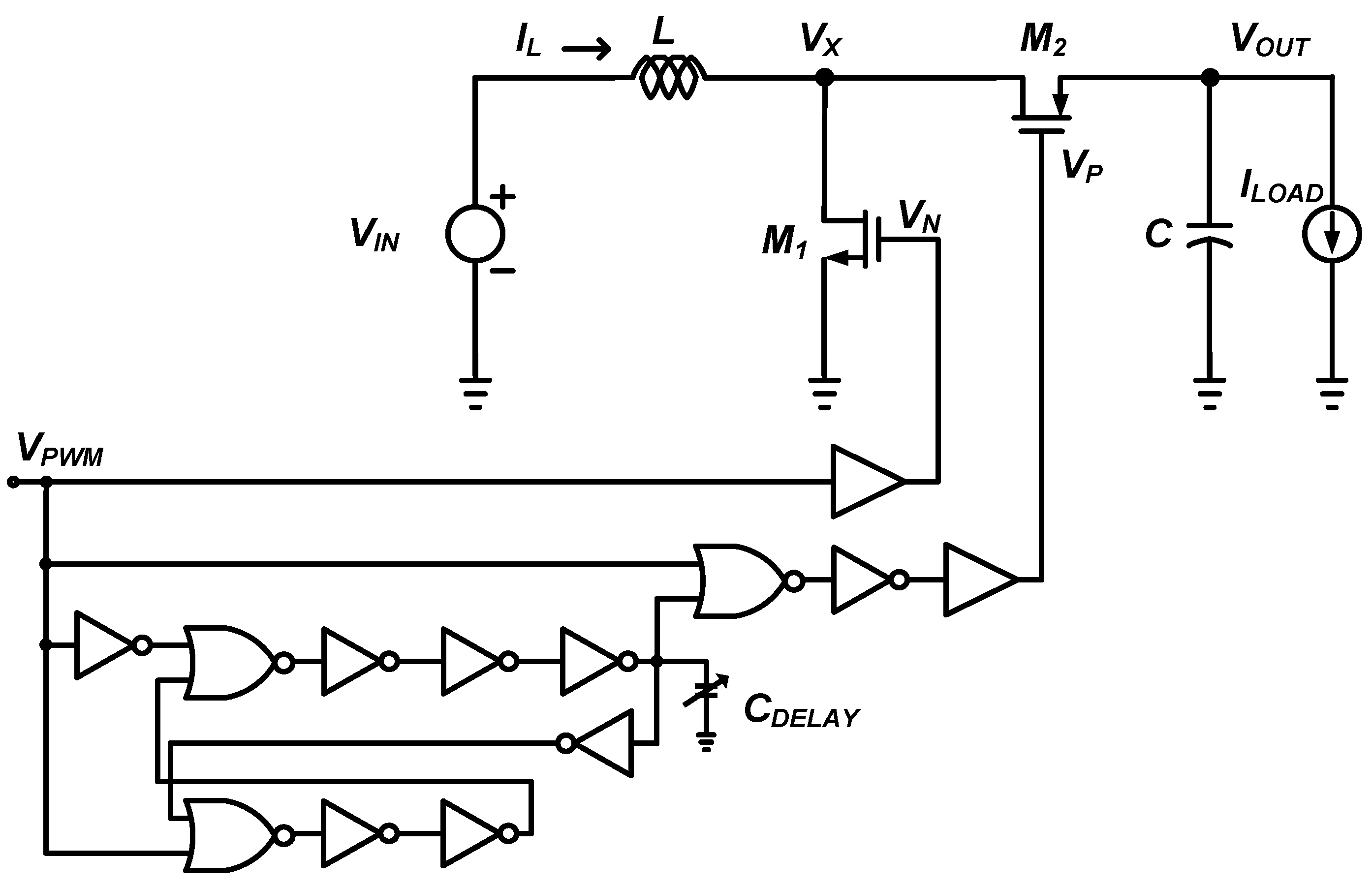

5. Proposed Efficiency Optimization Design

Figure 7 shows the schematic of the DC-DC boost converter with the control circuits for generating the pulses to drive and control the switches. The low input voltage DC-DC boost converter operates in discontinuous conduction mode (DCM) to obtain higher efficiency at the low input voltage operation of 0.1 V. A pulse width modulation (PWM) scheme-based control system is applied to keep the output voltage constant in the DC-DC boost converter. The PWM scheme-based control method adjusts the output voltage of the converter under different load current conditions by adjusting the duty cycle of the drive signal with a fixed frequency [

18]. The duty cycle of the driving signal to control the NMOS and PMOS switches of a DC-DC converter is proportional to the control voltage, which is the difference between the output voltage of the converter and the reference voltage. The PWM input (

VPWM) is used to drive the switch transistor

M1 through the buffer. The time delay controlled by the digital gates and

CDELAY compensates for the time delay between the switch control signals

VN and

VP so that transistor

M2 turns on quickly enough after transistor

M1 turns off. The output of the

OR gate drives the gate of the switch transistor

M2 through a buffer. Current sensing for switch transistor

M2 is performed by a comparator and the comparator’s output signal is used to sense when the current through switch transistor

M2 goes to zero.

In an RF-DC converter for RF energy harvesting, the output DC voltage varies according to the RF input power. Therefore, the DC-DC boost converter following the RF-DC converter is required to achieve high efficiency over a wide input voltage range. To obtain high efficiency in a wide input voltage range, it is necessary to derive the optimal value of each design parameter to minimize the loss by modeling the loss of the converter according to the input voltage.

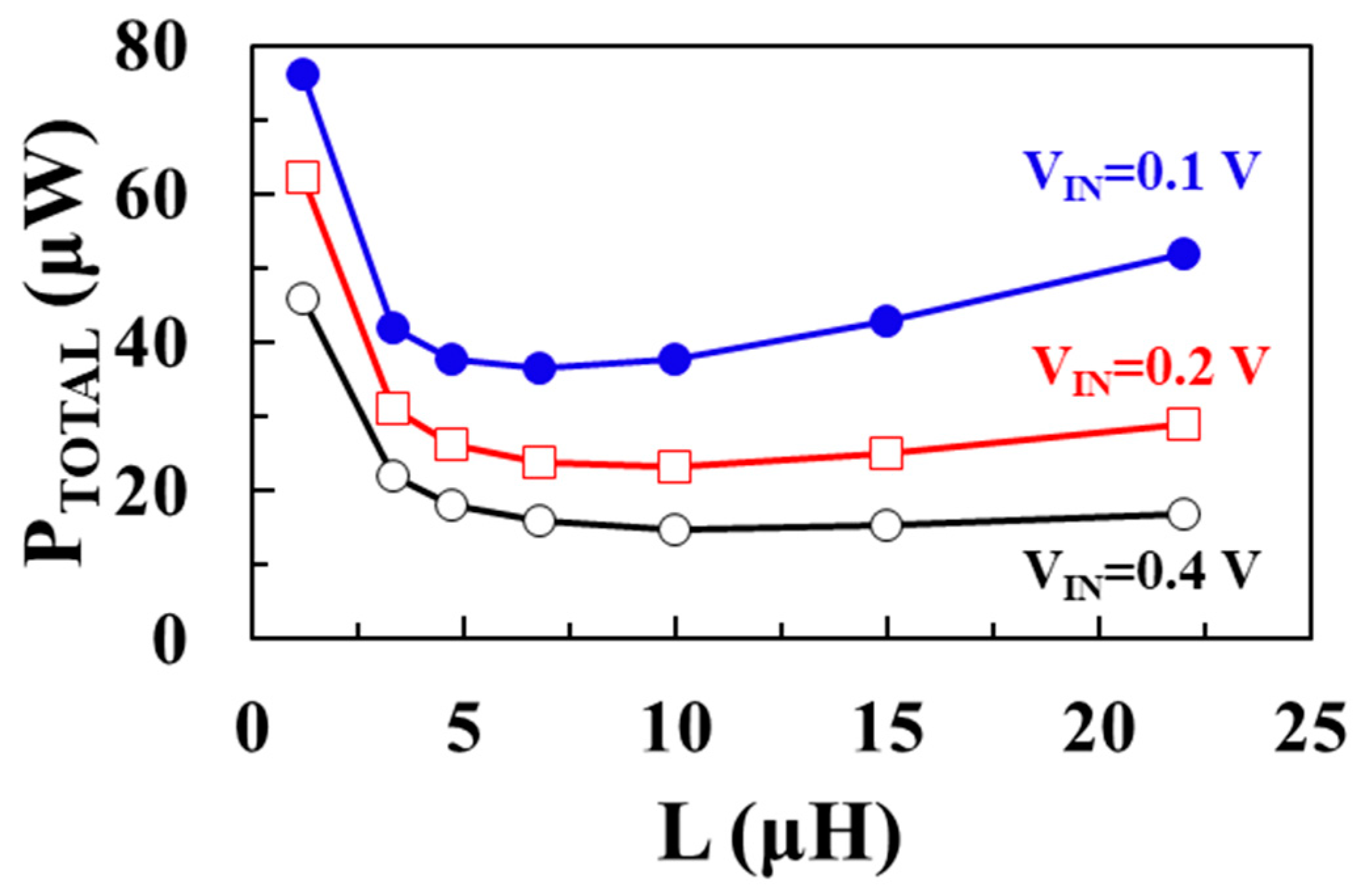

Figure 8 shows the modeled total loss (

PTOTAL) as a function of inductance

L using (7) for input voltages of 0.1 V, 0.2 V, and 0.4 V, respectively, when

VOUT = 1 V,

ILOAD = 1 mA,

WM1 =

WM2 = 20 mm, and

IP = 30 mA.

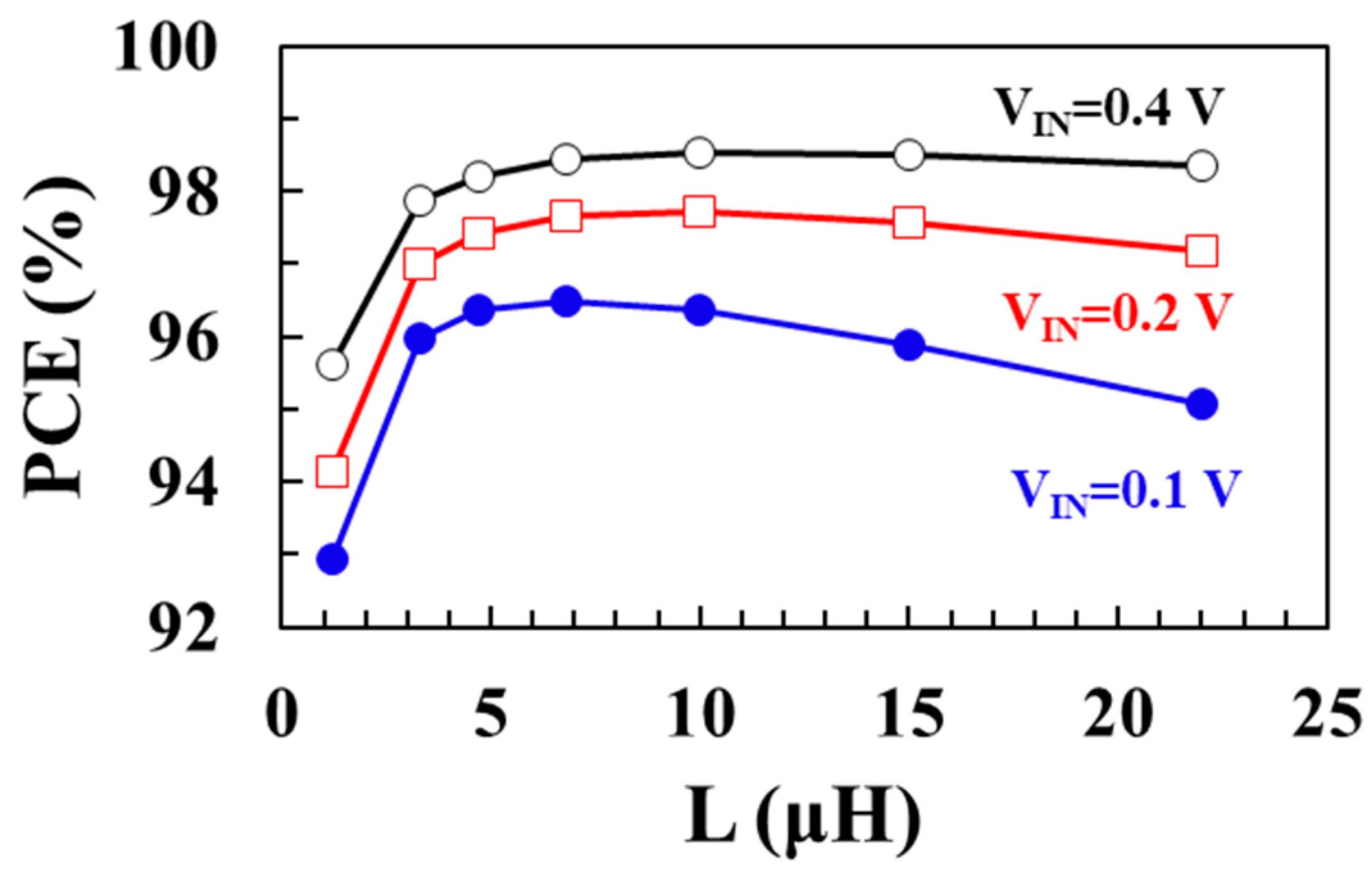

Figure 9 shows the modeled power conversion efficiency (PCE) as a function of the inductance

L using (7) for input voltages of 0.1 V, 0.2 V, and 0.4 V, respectively. As the input voltage increases, the optimum inductance to achieve the minimum total loss increases. At an input voltage of 0.1 V, a maximum efficiency of 96.5% is achieved when

L is 6.8 μH. At input voltages of 0.2 V and 0.4 V, maximum efficiencies of 97.7% and 98.5% are achieved when

L is 10 μH, respectively.

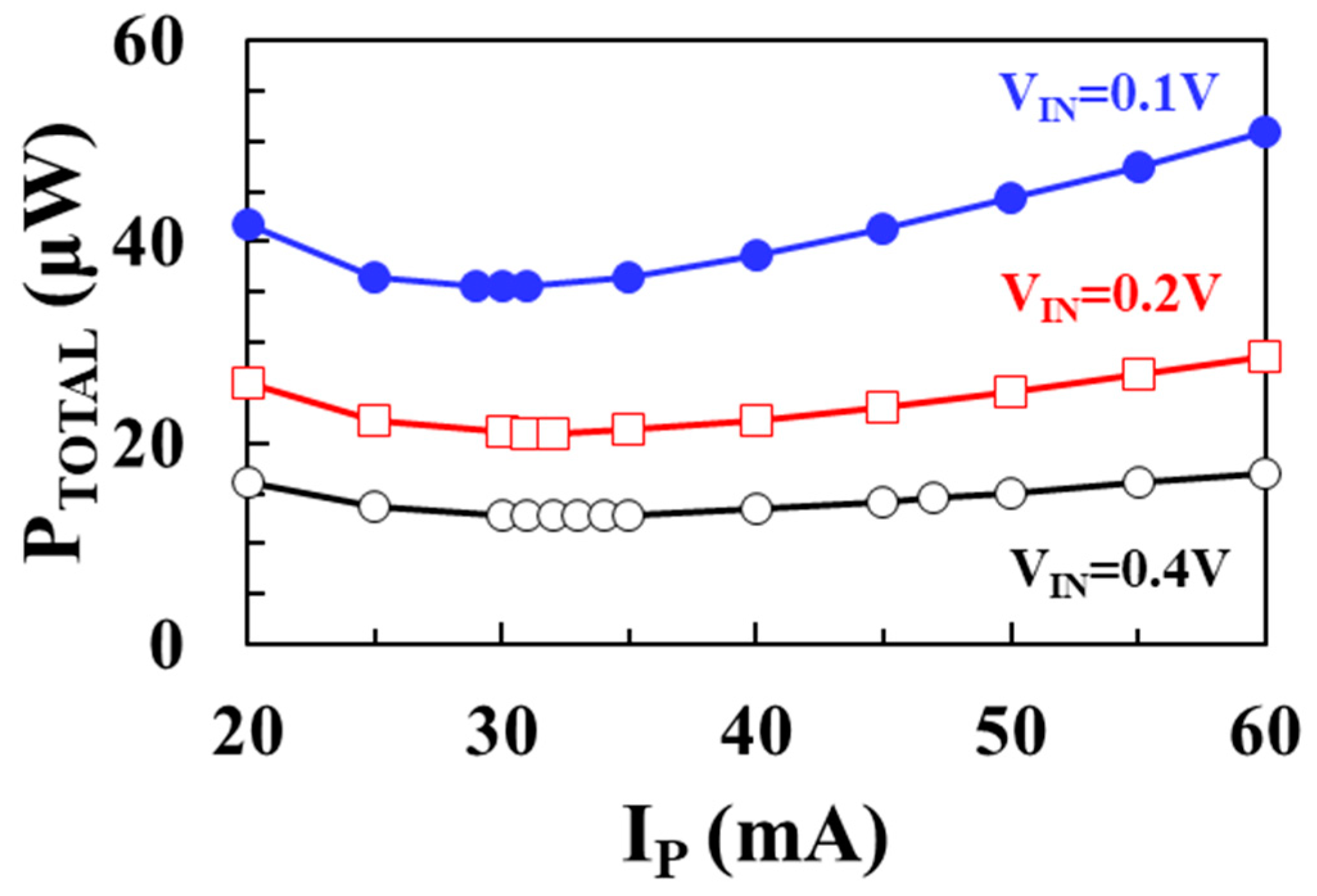

Figure 10 shows the modeled total loss (

PTOTAL) as a function of peak inductor current

IP using (7) for input voltages of 0.1 V, 0.2 V, and 0.4 V, respectively, when

VOUT = 1 V,

ILOAD = 1 mA,

L = 10 μH,

WM1 =

WM2 = 20 mm.

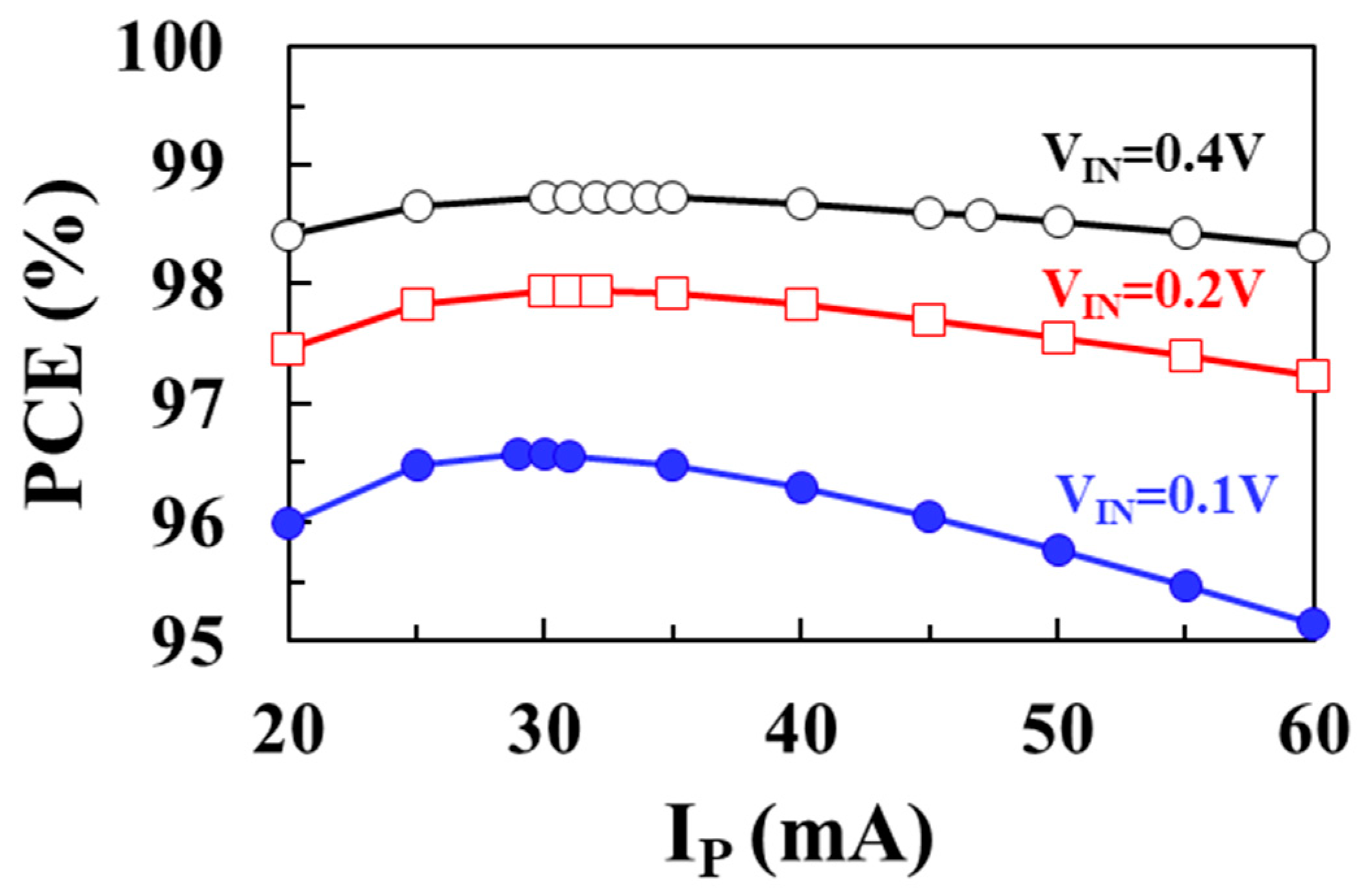

Figure 11 shows the PCE according to the peak inductor current (

IP) for input voltages of 0.1 V, 0.2 V, and 0.4 V, respectively. As the input voltage increases, the optimum peak inductor current to achieve the minimum total loss increases. At an input voltage of 0.1 V, a maximum efficiency of 96.6% is achieved when

IP is 29 mA. At an input voltage of 0.2 V, a maximum efficiency of 97.7% is achieved when

IP is 31 mA, and at an input voltage of 0.4 V, a maximum efficiency of 98.7% is achieved when

IP is 33 mA.

6. Simulation Results and Comparison

In this paper, the DC-DC boost converter has been designed using a 65 nm CMOS technology. To verify the effectiveness of the DC-DC boost converter and to compare it with the proposed model, post-layout simulations with Spectre were carried out.

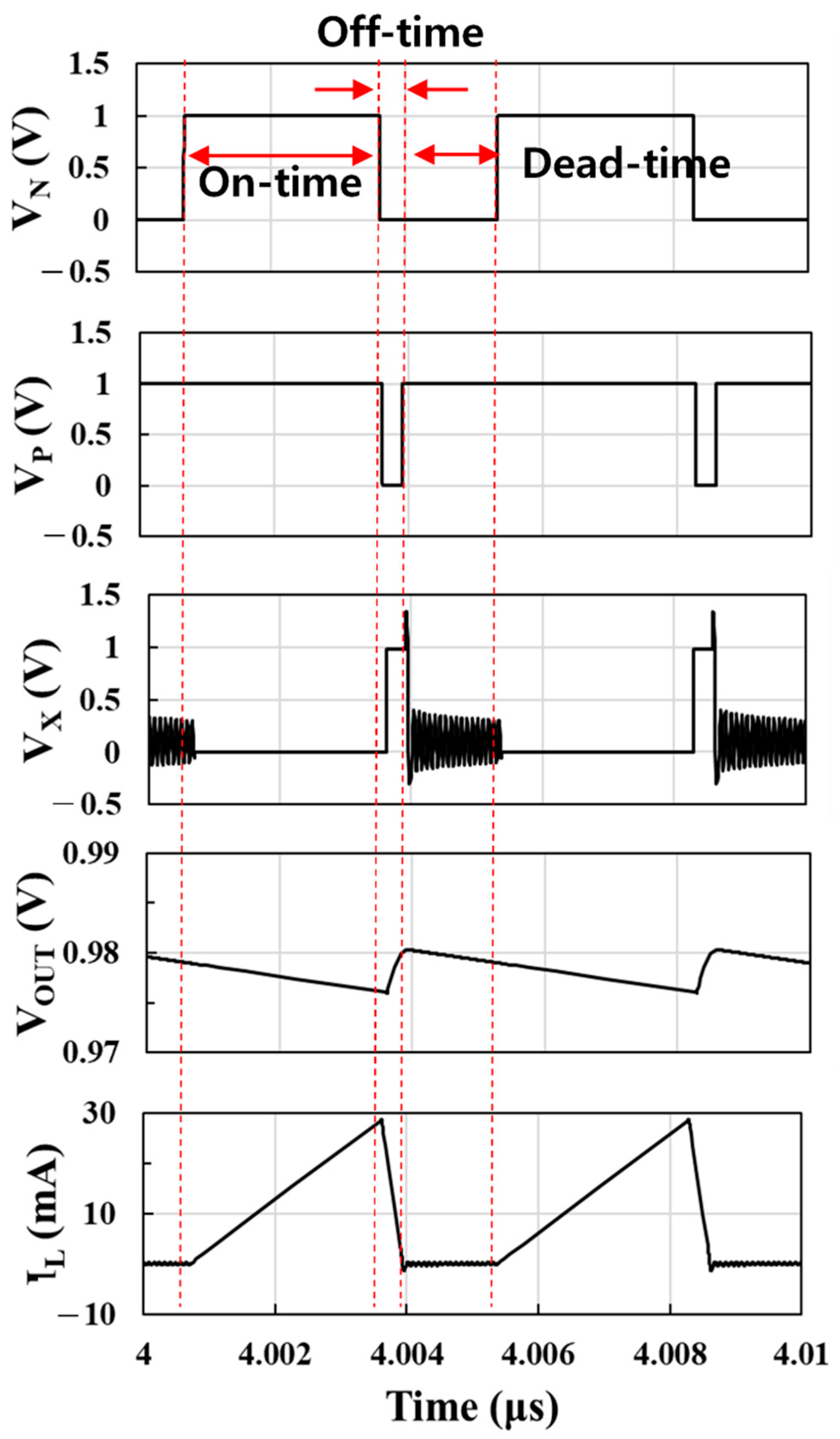

Figure 12 shows the waveforms of the switch control signals

VN and

VP, internal node voltage

VX, output voltage

VOUT, and inductor current

IL for an input voltage of 0.1 V.

VN and VP are the output signals of the control circuit to control the switch on-off of the converter. When VN and VP are high at the same time, the inductor is connected to ground during on time so that IL increases from 0 mA to 29 mA and the load capacitor is discharged by the load current and VOUT decreases. When VN and VP are low at the same time, the inductor is connected to the output during off time and the output capacitor is not only discharged by the constant load current but also charged by the inductor current, so that VOUT increases. Conduction losses mainly occur as current flows during on time and off time. During the dead time when VN is low and VP is high, no current flows through the inductor and, as in the on-time period, the output capacitor is discharged by constant load current and VOUT decreases. Ringing occurs due to the resonance of the inductor and parasitic capacitor during dead time.

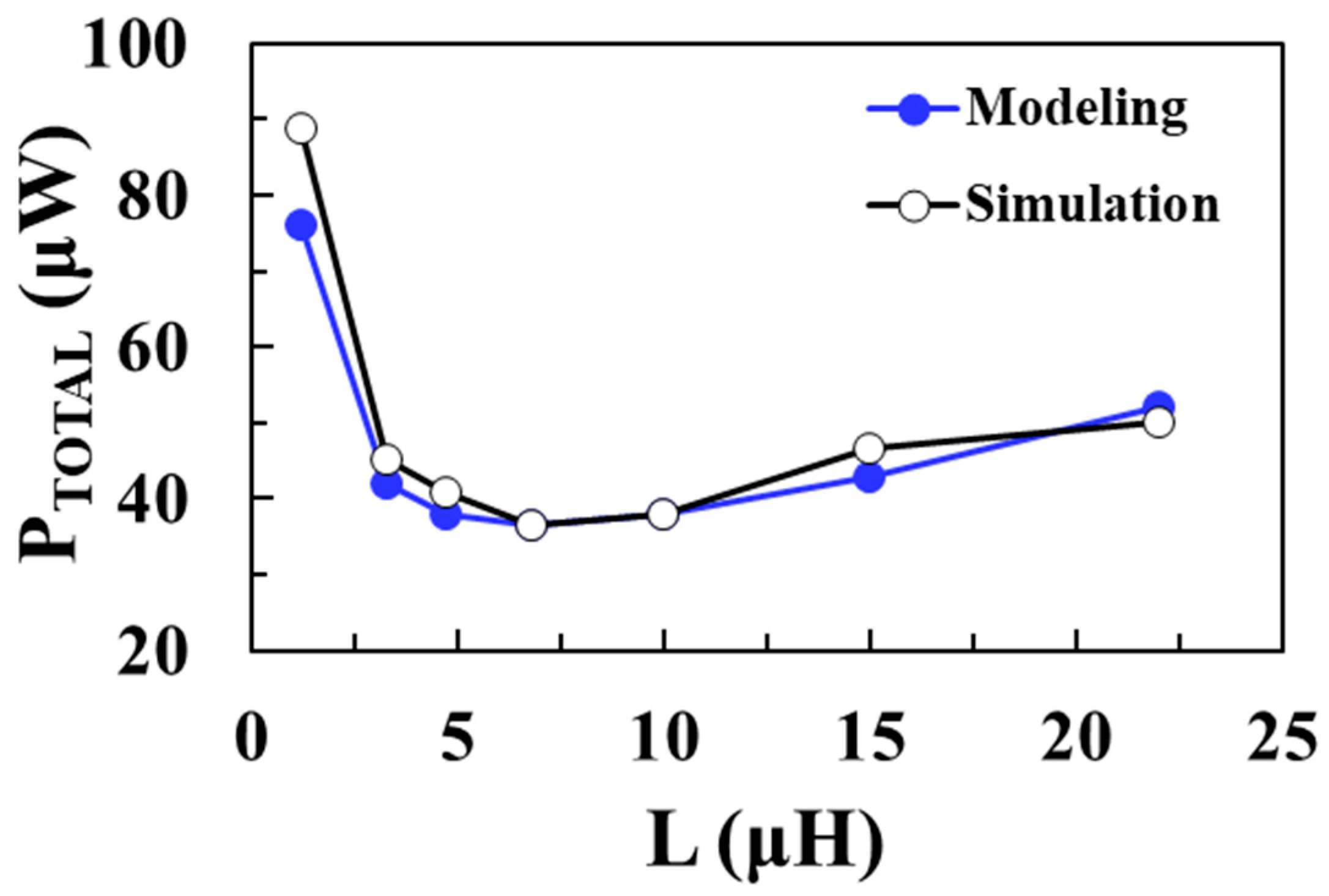

Figure 13 shows the total loss of the DC-DC boost converter according to the inductance

L for an input voltage of 0.1 V and compares the circuit simulation results with the proposed modeling results when

VOUT = 1 V,

ILOAD = 1 mA,

WM1 =

WM2 = 20 mm, and

IP = 30 mA. As the inductance decreases, the switching frequency increases and the switching losses of NMOS and PMOS increase. On the other hand, as the inductance increases, the ESR of the inductor increases and conduction loss of the inductor increases. Therefore, there is an optimal inductance value that minimizes the total loss. It shows that the modeled total loss of the boost converter agrees well with the circuit simulation results, with a minimum loss of 36.4 μW achieved for an

L of 6.8 μH.

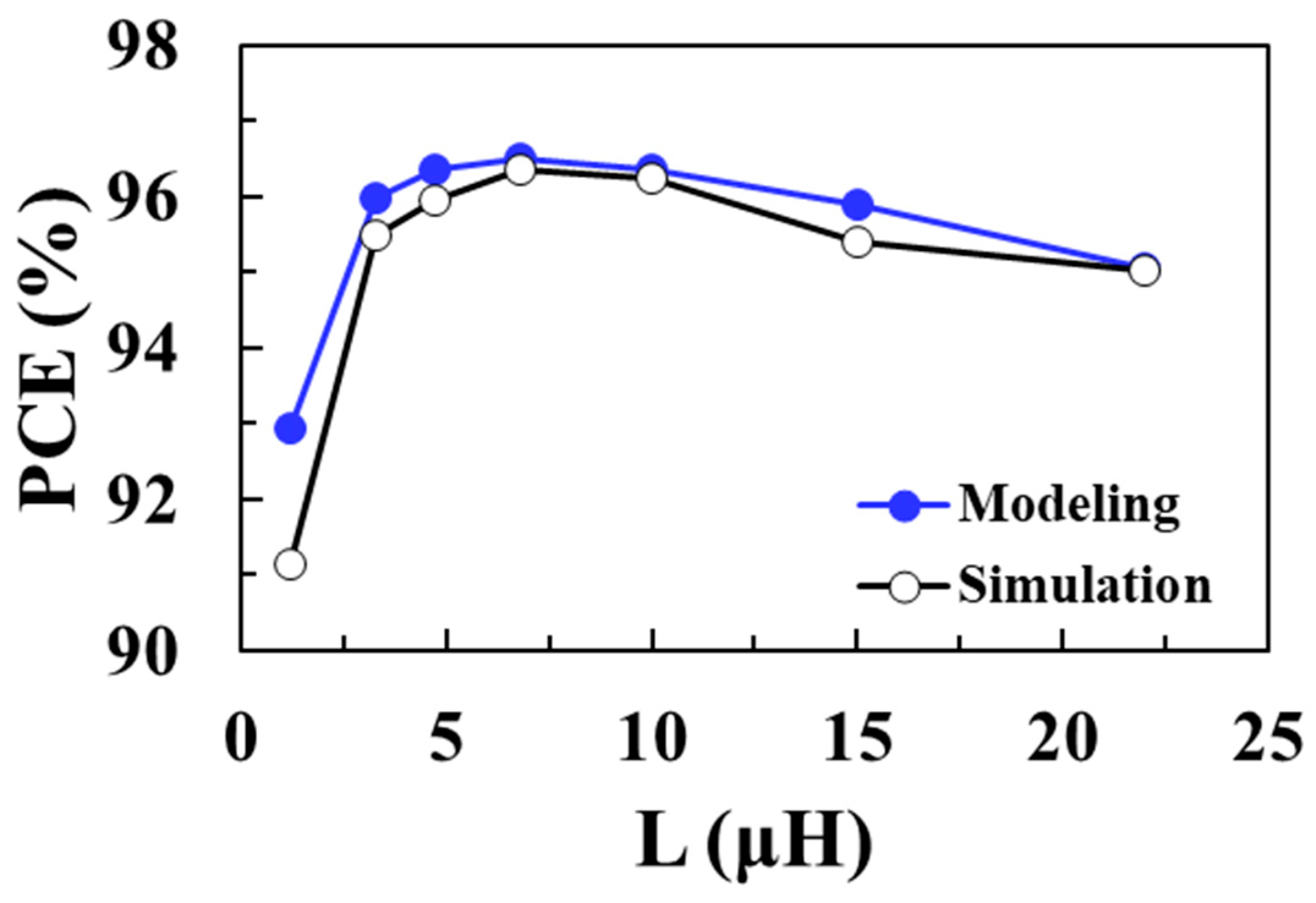

Figure 14 shows the PCE of the converter according to

L for an input voltage of 0.1 V and compares the circuit simulation results with the proposed modeling results. A maximum efficiency of 96.5% is achieved at an optimum

L of 6.8 μH and the proposed model accurately predicts the optimal

L value to obtain the maximum PCE.

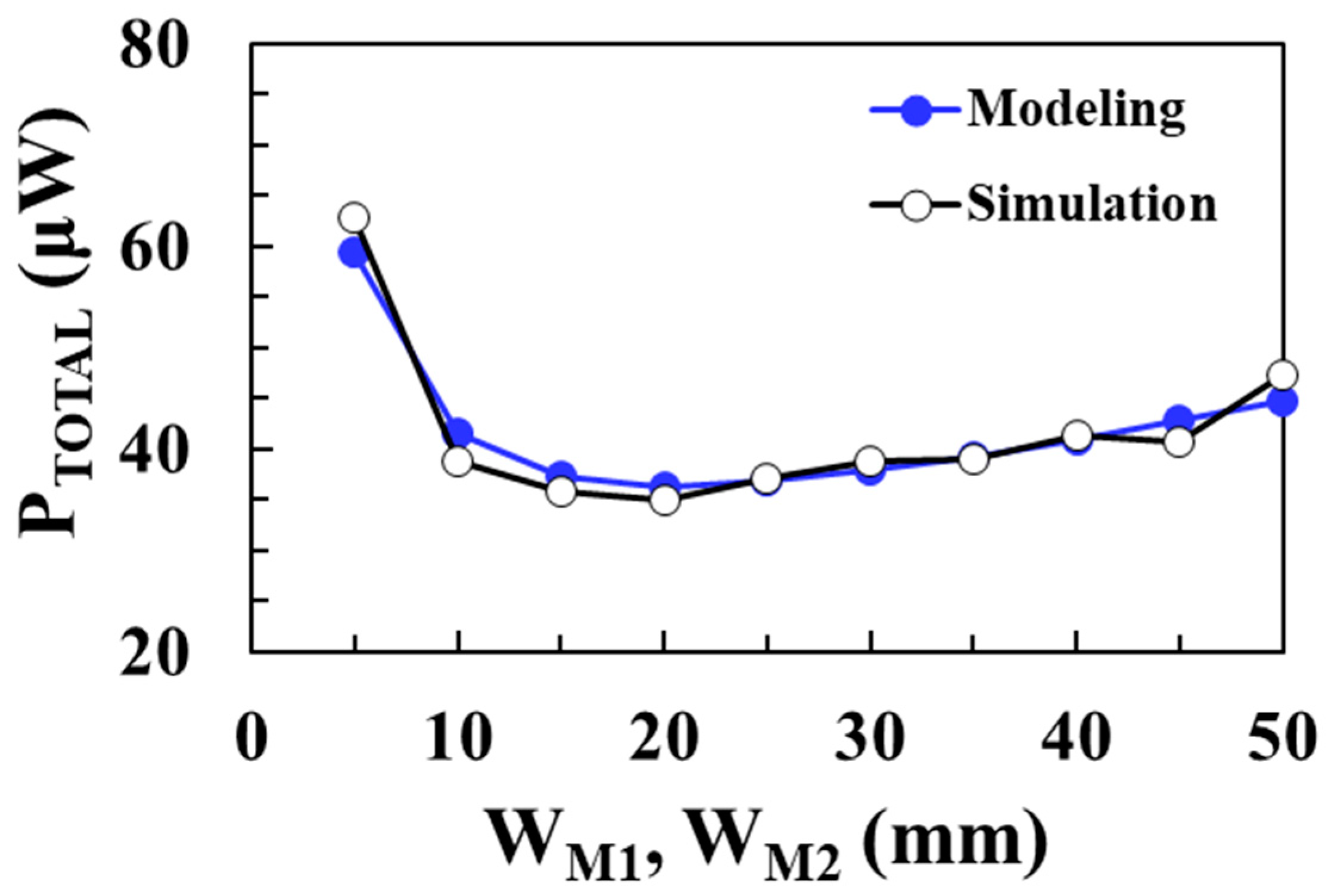

Figure 15 shows the total loss of the DC-DC boost converter according to the width of

M1 and

M2 switches for an input voltage of 0.1 V and compares the circuit simulation results with the proposed modeling results when

VOUT = 1 V,

ILOAD = 1 mA,

L = 10 μH, and

IP = 30 mA. As the NMOS and PMOS switches’ width decreases, the on resistance increases and the conduction losses of the switches increase. On the other hand, as the switches’ width increases, the capacitances increase and the switching losses of the NMOS and PMOS increase. Therefore, there is an optimal switch width that minimizes the total loss. The modeled total loss agrees well with the circuit simulation results and a minimum loss of 36.3 μW is achieved when the switch width is 20 mm.

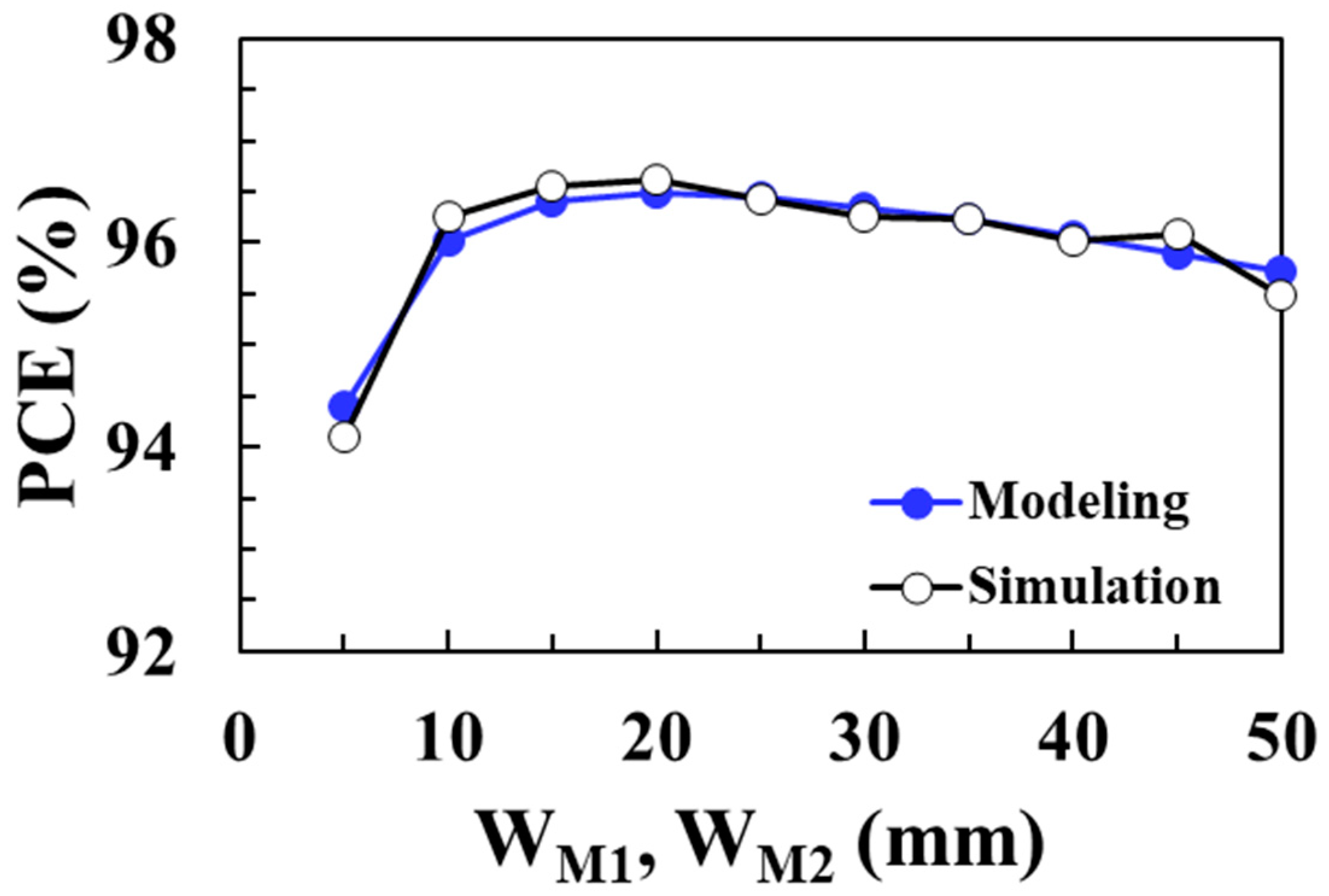

Figure 16 shows the PCE of the boost converter according to the width of

M1 and

M2 switches for an input voltage of 0.1 V and compares the circuit simulation results with the proposed modeling results. A maximum efficiency of 96.5% is achieved at an optimum switch width of 20 mm and the proposed model accurately predicts the optimal switch width to obtain the maximum PCE.

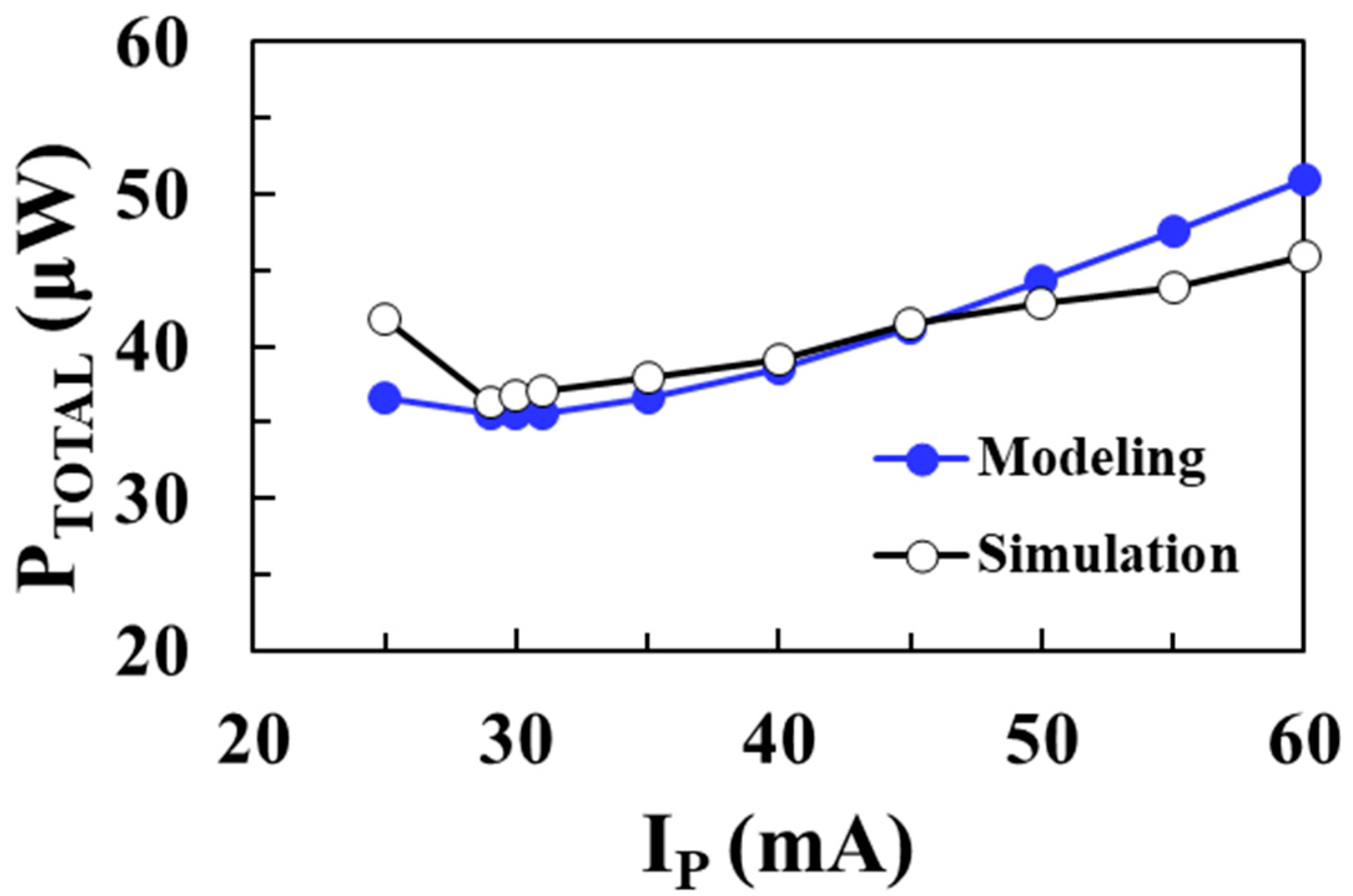

Figure 17 shows the total loss of the DC-DC boost converter according to the peak inductor current

IP for an input voltage of 0.1 V and compares the circuit simulation results with the proposed modeling results when

VOUT = 1 V,

ILOAD = 1 mA,

L = 10 μH, and

WM1 =

WM2 = 20 mm. As the peak inductor current decreases, the switching frequency increases and the switching losses of the NMOS and PMOS increase. On the other hand, as the peak inductor current increases, conduction losses in the switches and inductor increase. Therefore, there is an optimal peak inductor current that minimizes total losses. The modeled total loss agrees well with the circuit simulation results, with a minimum loss of 35.6 μW achieved at an

IP of 29 mA.

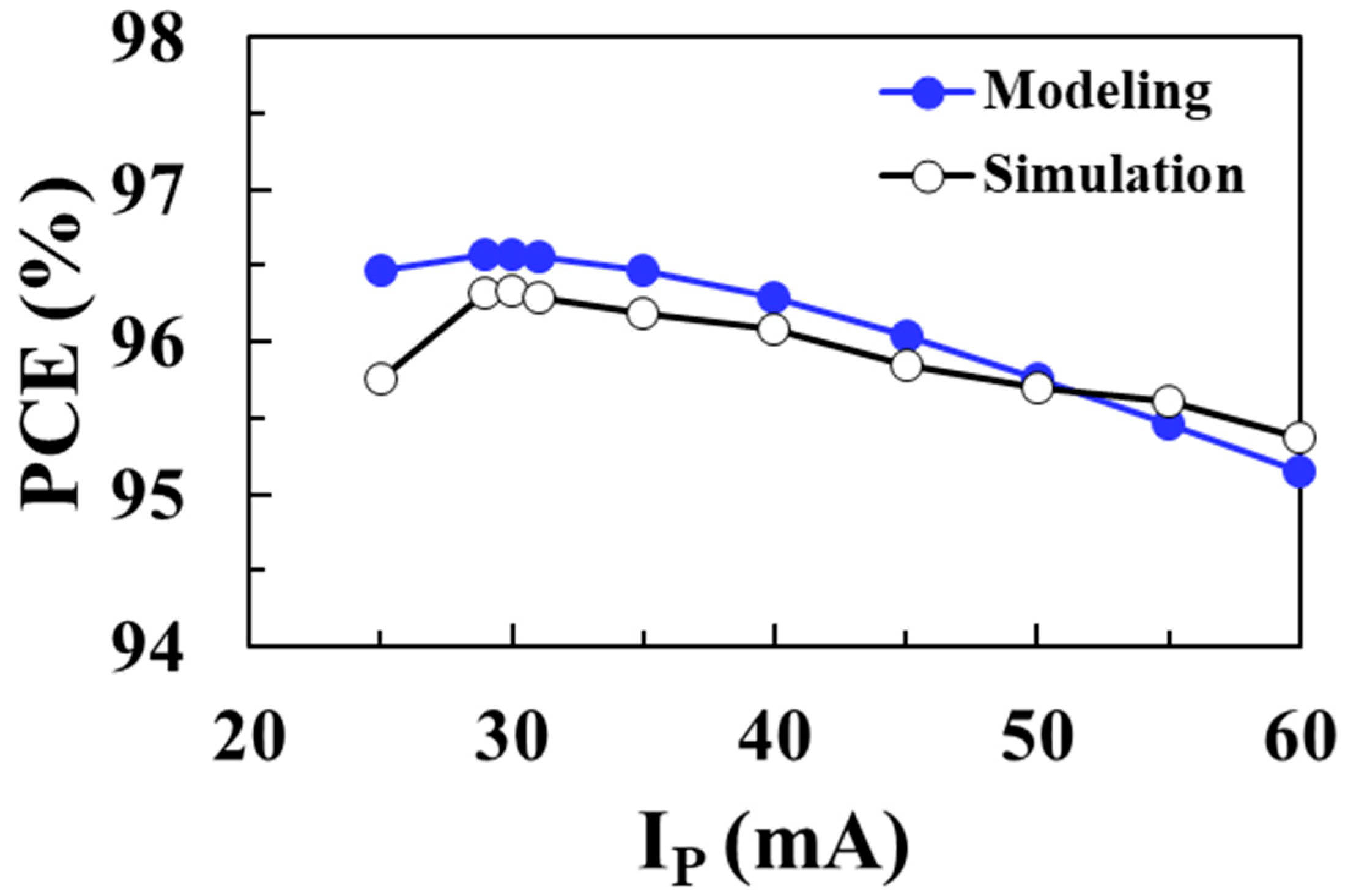

Figure 18 shows the PCE of the boost converter according to the peak inductor current

IP for an input voltage of 0.1 V and compares the circuit simulation results with the proposed modeling results. A maximum efficiency of 96.6% is achieved at an optimum

IP of 29 mA and the proposed model accurately predicts the optimal

IP to obtain the maximum PCE.

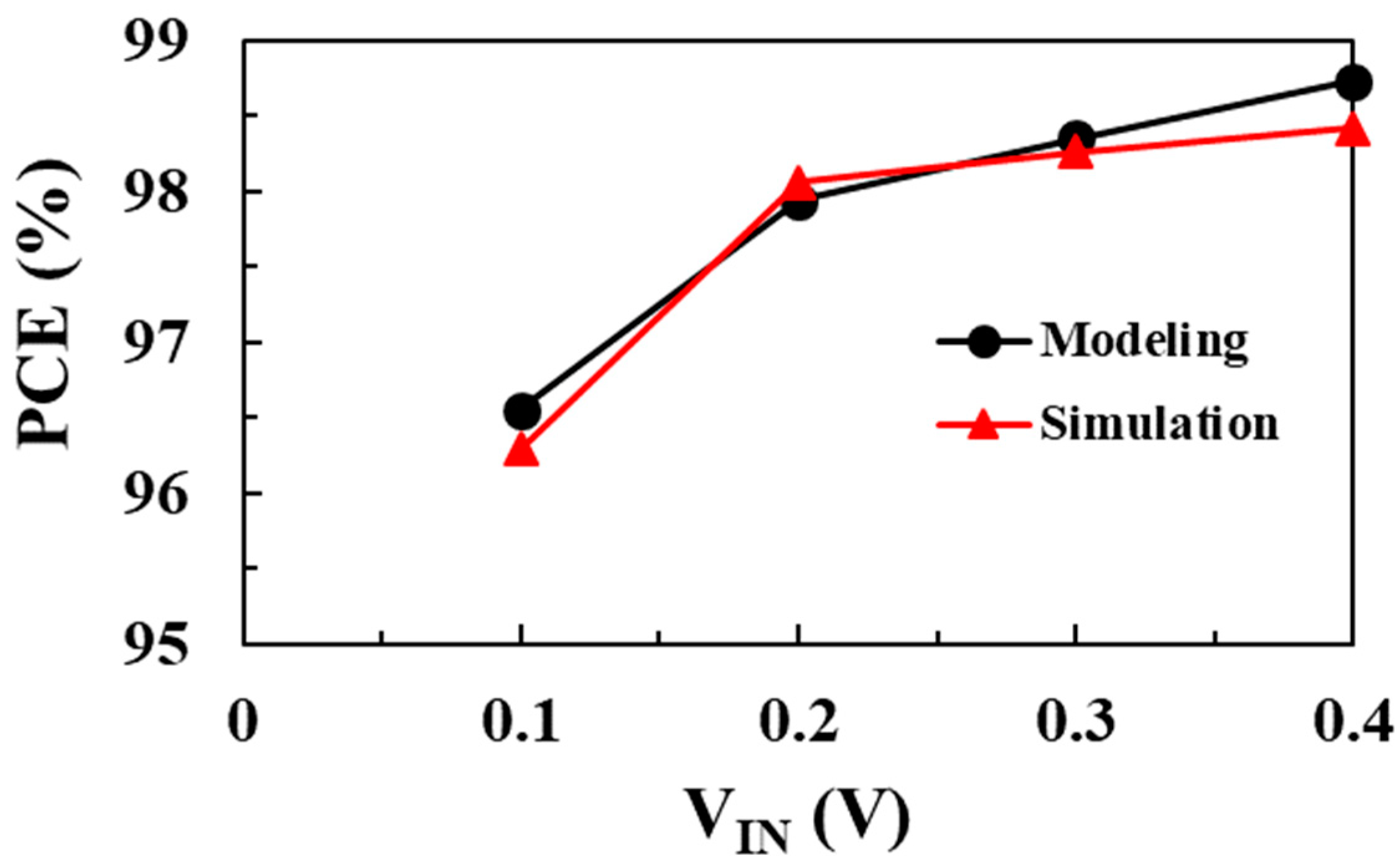

Figure 19 shows the PCE of the converter according to the input voltage and compares the circuit simulation results with the proposed modeling results when

VOUT = 1 V,

ILOAD = 1 mA, and

WM1 =

WM2 = 20 mm. Based on the proposed optimal design methodology to achieve the maximum PCE, the optimal values of inductance and peak inductor current are designed differently according to the input voltage. As the input voltage increases, the optimum inductance and peak inductor current to achieve the minimum total loss increase. At an input voltage of 0.1 V, a maximum PCE of 96.5% is achieved when

L is 6.8 μH and

IP is 29 mA. On the other hand, at an input voltage of 0.4 V, a maximum PCE of 98.4% is achieved when

L is 10 μH and

IP is 33 mA. The PCE modeling results achieved from the proposed efficiency optimization design method based on loss analysis and modeling are in good agreement with circuit simulation results over a wide input voltage range. By deriving the optimal design parameters including inductance and peak inductor current for different input voltages, the maximum PCE is achieved over a wide input voltage range.

Table 1 summarizes the performance of this work and compares with the state-of-the-art DC-DC boost converters for energy harvesting applications. The proposed boost converter for RF energy harvesting operates over a wide input voltage range and achieves a PCE of 96.5% at a low input voltage of 0.1 V and the highest peak efficiency of 98.4% at an input voltage of 0.4 V.