A Low-Power 12-Bit 20 MS/s Asynchronously Controlled SAR ADC for WAVE ITS Sensor Based Applications

Abstract

1. Introduction

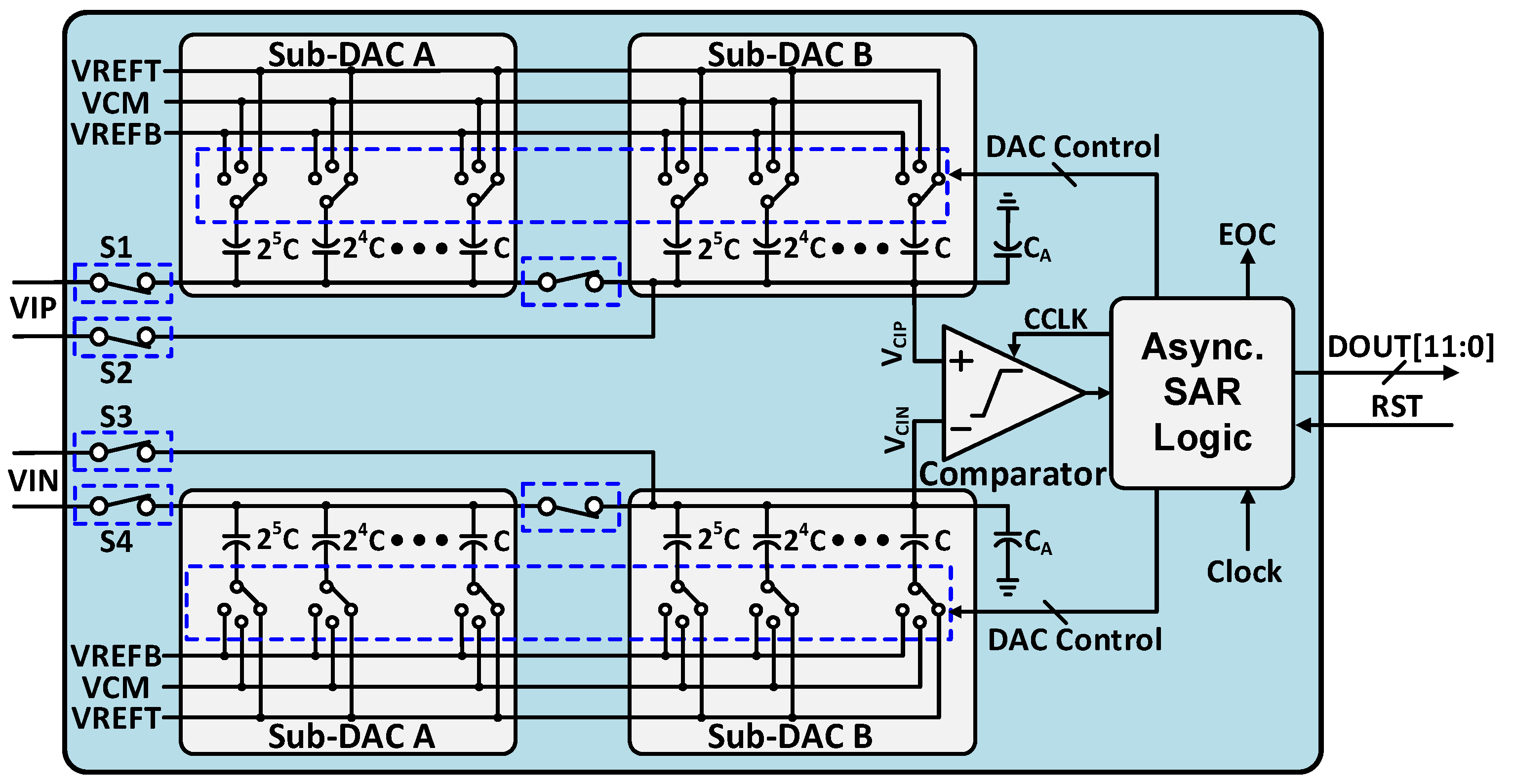

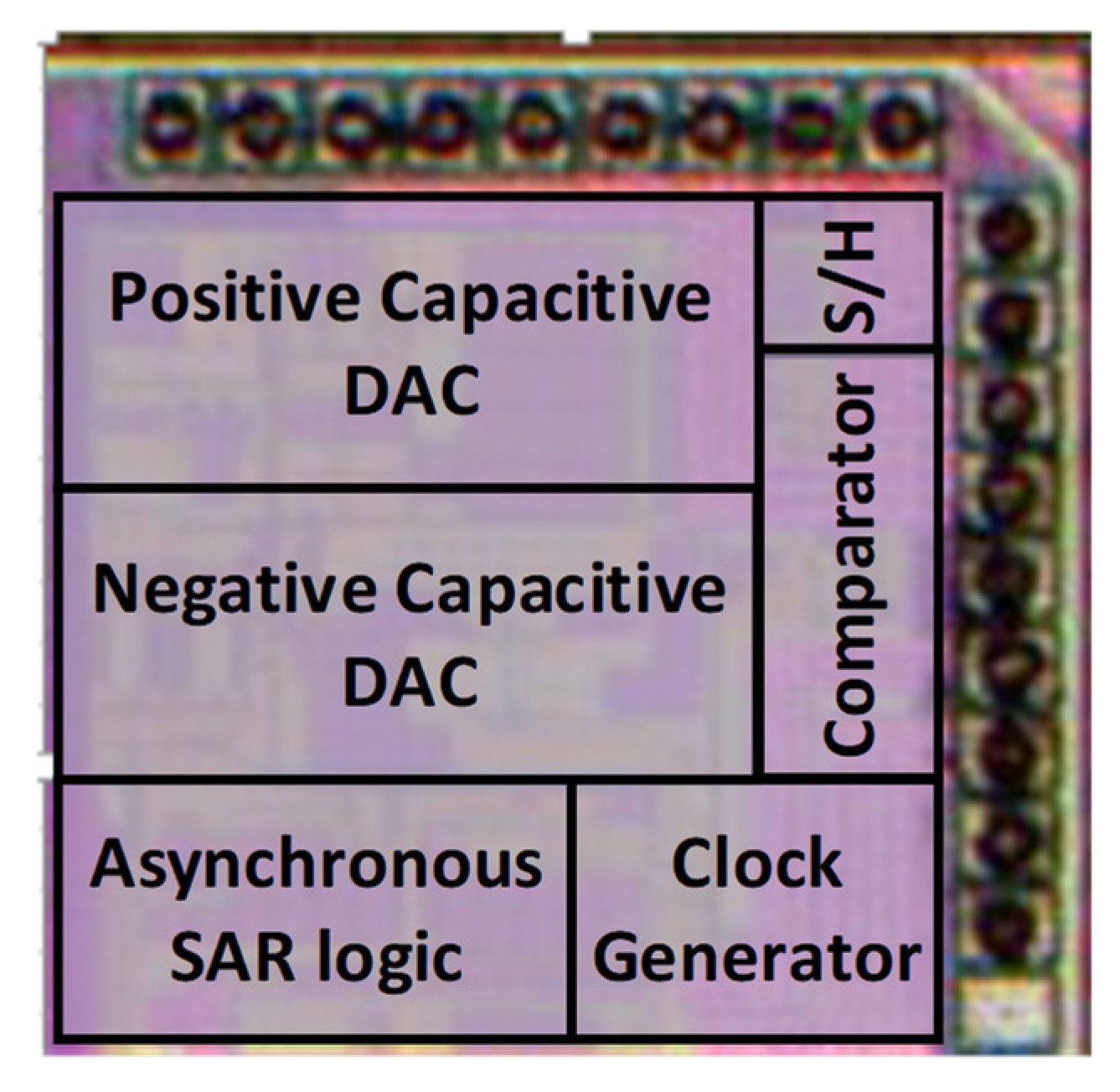

2. The Top-Block Diagram of Proposed ADC Architecture

3. Circuit Implementation

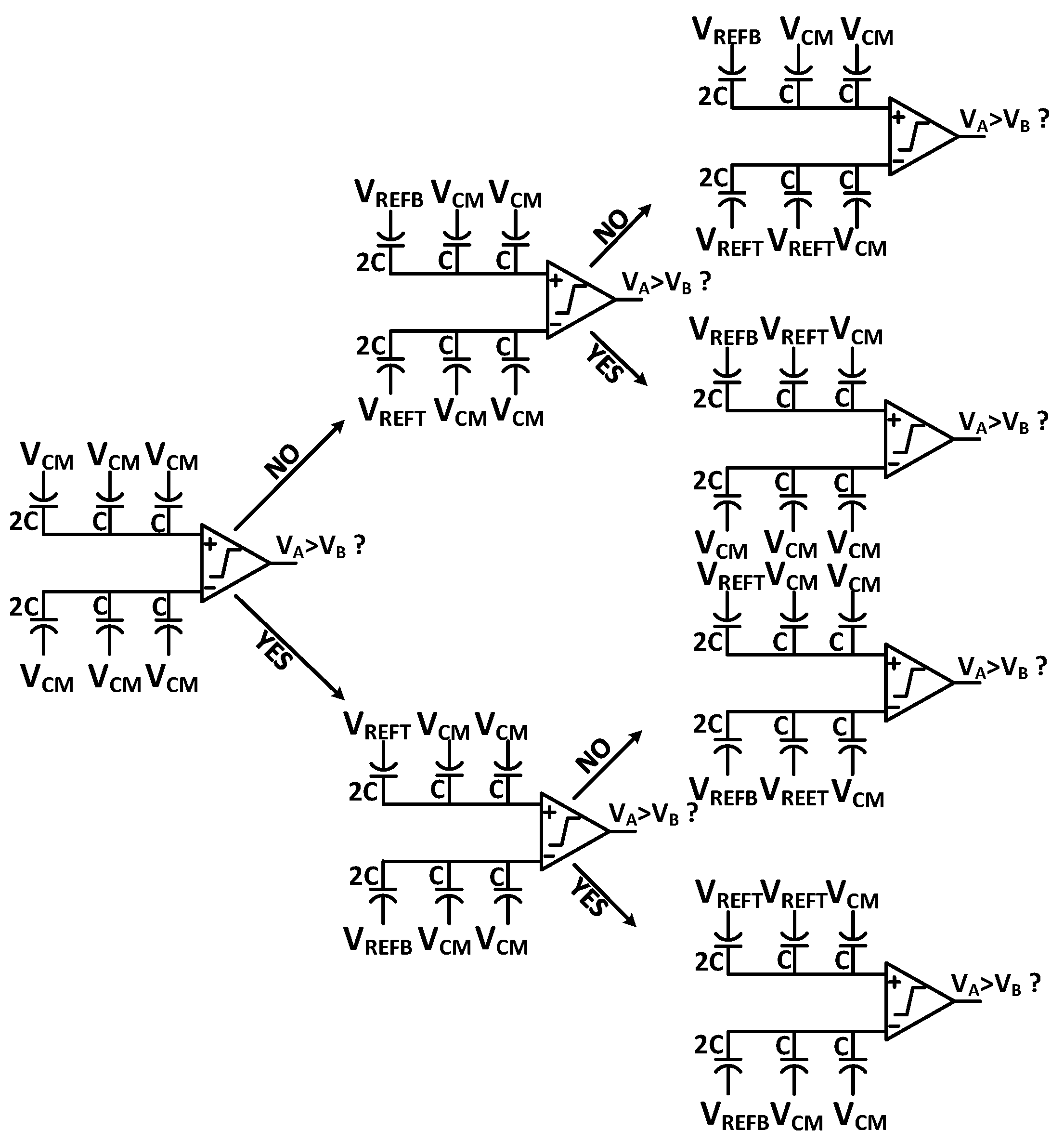

3.1. Capacitive DAC with Modified CMCR Switching Technique

- (1)

- LSB conversion by the whole sub-DACs.

- (2)

- MSB conversion by one sub-DAC.

3.2. Bootstrap Switch

3.3. Dynamic Latched Comparator

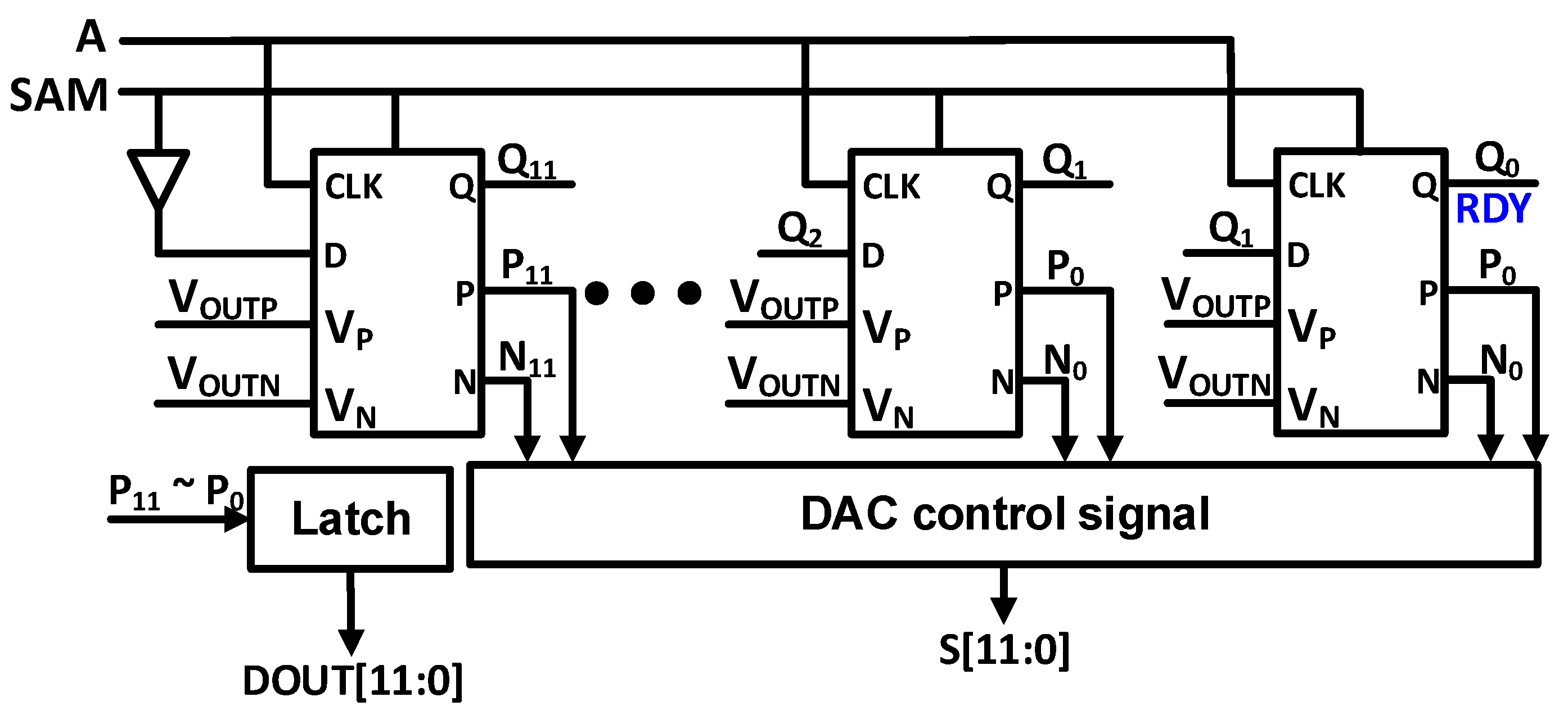

3.4. Asynchronous SAR Logic Processing

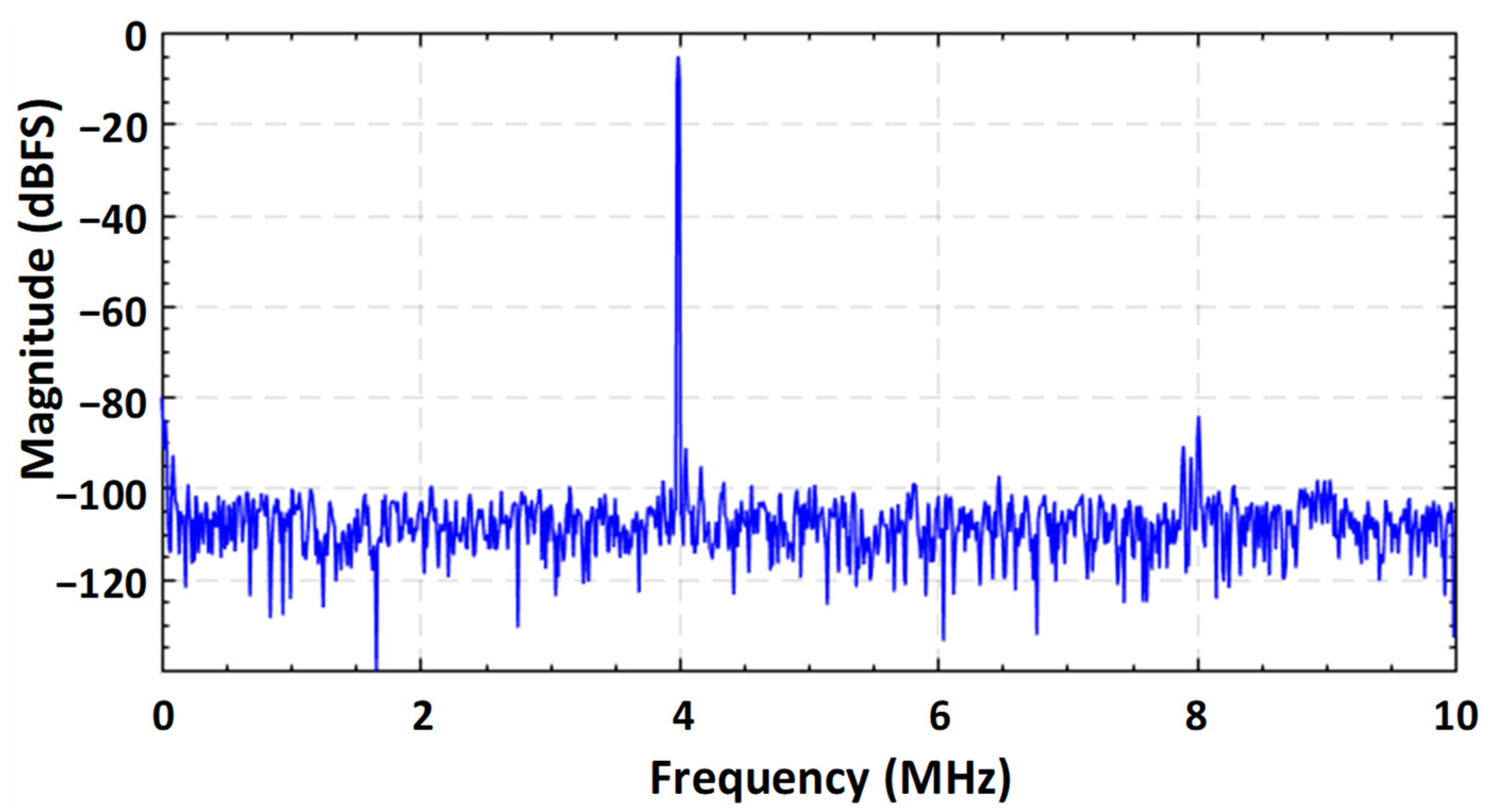

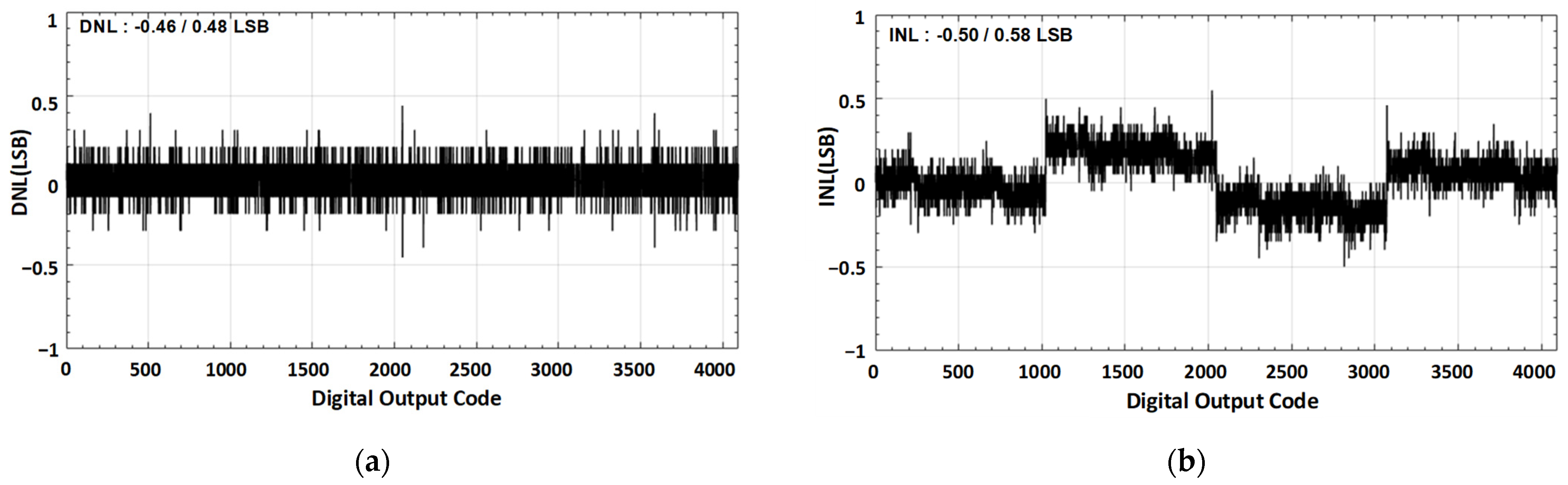

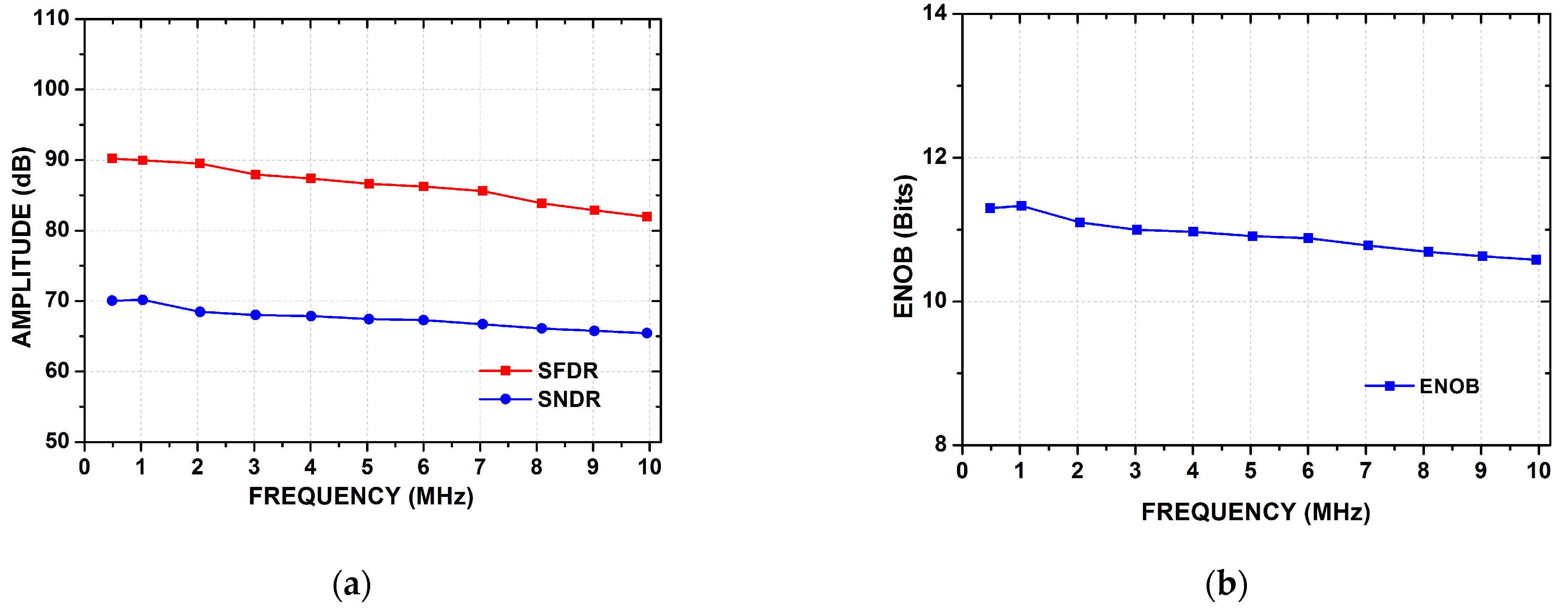

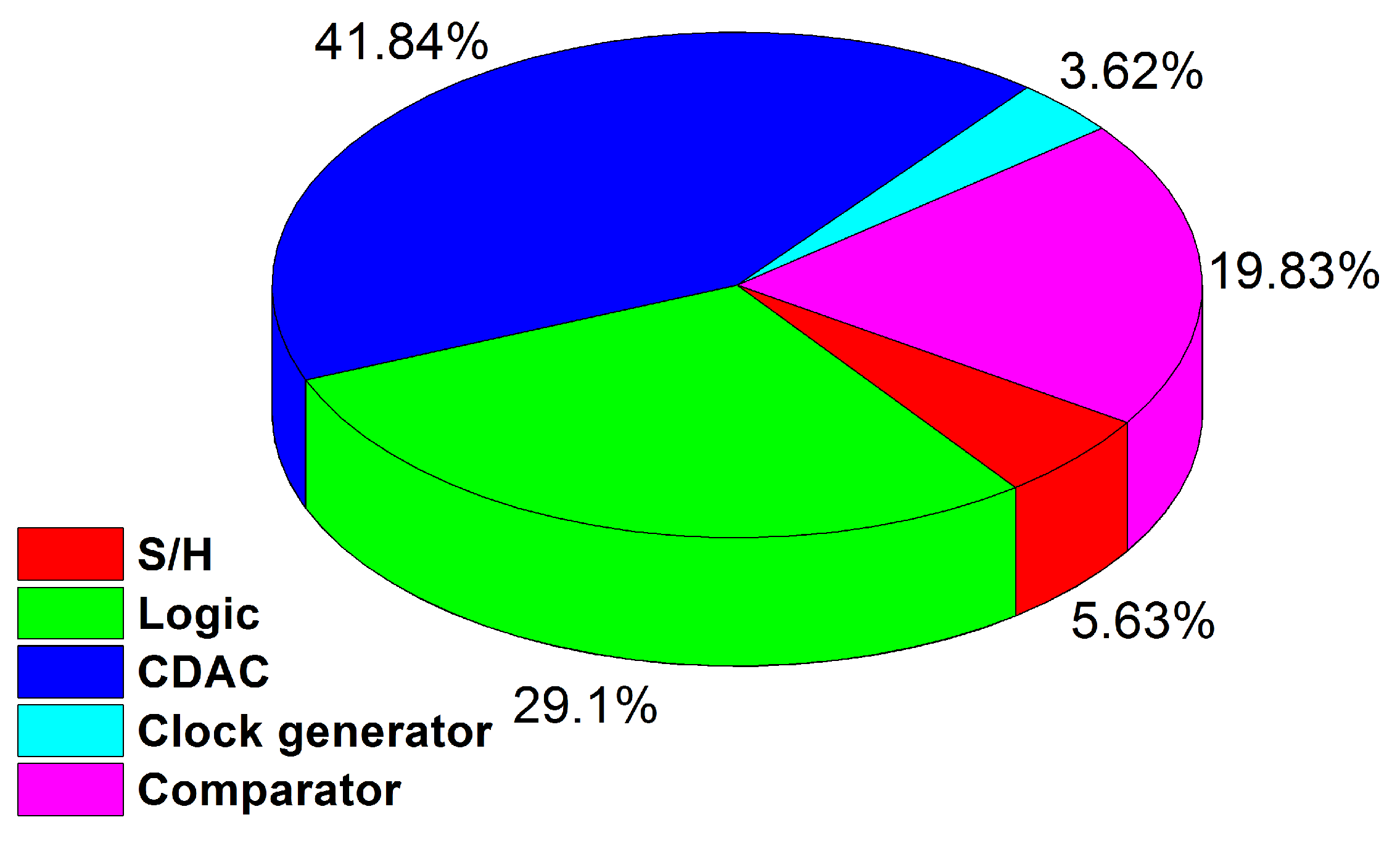

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Electronic Toll Collection-Dedicated Short Range Communication—Part 1: Physical Layer. China Nat. Standard GB/T 20851.1–2007, 19 March 2007.

- Kwon, K.; Choi, J.; Choi, J.; Lee, K.; Ko, J. A 5.8 GHz integrated cmos dedicated short range communication transceiver for the Korea/Japan electronic toll collection system. IEEE Trans. Microw. Theory 2010, 58, 2751–2763. [Google Scholar] [CrossRef]

- Ali, I.; Asif, M.; Rehman, M.R.U.; Khan, D.; Yingge, H.; Kim, S.J.; Pu, Y.; Yoo, S.-S.; Lee, K.-Y. A Highly Reliable, 5.8 GHz DSRC Wake-Up Receiver with an Intelligent Digital Controller for an ETC System. Sensors 2020, 20, 4012. [Google Scholar] [CrossRef] [PubMed]

- Bai, Z.; Kim, S.; Rad, R.E.; Lee, K. A 5.8 GHz Adaptive CMOS Image Rejection Mixer for DSRC Transceiver. In Proceedings of the 2020 International Conference on Electronics, Information, and Communication (ICEIC), Barcelona, Spain, 19–22 January 2020; pp. 1–3. [Google Scholar]

- Kim, S.J.; Kim, D.G.; Oh, S.J.; Lee, D.S.; Pu, Y.G.; Hwang, K.C.; Yang, Y.; Lee, K.Y. A Fully Integrated Bluetooth Low-Energy Transceiver with Integrated Single Pole Double Throw and Power Management Unit for IoT Sensors. Sensors 2019, 19, 2420. [Google Scholar] [CrossRef] [PubMed]

- Xia, B.; Valdes-Garcia, A.; Sanchez-Sinencio, E. A 10-bit 44-MS/s20-mW configurable time-interleaved pipeline ADC for a dual-mode802.11b/Bluetooth receiver. IEEE J. Solid-State Circuits 2006, 41, 530–539. [Google Scholar] [CrossRef]

- Harpe, P.; Zhang, Y.; Dolmans, G.; Philips, K.; de Groot, H. A 7-to-10 b 0-to-4 MS/s flexible SAR ADC with 6.5-to-16 fJ/conversion-step. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 19–23 February 2012; pp. 472–473. [Google Scholar]

- Tai, H.-Y.; Hu, Y.-S.; Chen, H.-W.; Chen, H.-S. 11.2 A 0.85 fJ/conversion-step 10 b 200 kS/s subranging SAR ADC in 40 nm CMOS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 196–197. [Google Scholar]

- Kapusta, R.; Shen, J.; Decker, S.; Li, H.; Ibaragi, E.; Zhu, H. A 14 b 80 MS/s SAR ADC With 73.6 dB SNDR in 65 nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 3059–3066. [Google Scholar] [CrossRef]

- Kramer, M.J.; Janssen, E.; Doris, K.; Murmann, B. A 14 b 35 MS/s SAR ADC Achieving 75 dB SNDR and 99 dB SFDR With Loop-Embedded Input Buffer in 40 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2891–2900. [Google Scholar] [CrossRef]

- Miki, T.; Morie, T.; Matsukawa, K.; Bando, Y.; Okumoto, T.; Obata, K.; Sakiyama, S.; Dosho, S. A 4.2 mW 50 MS/s 13 bit CMOS SAR ADC With SNR and SFDR Enhancement Techniques. IEEE J. Solid-State Circuits 2015, 50, 1372–1381. [Google Scholar] [CrossRef]

- Verbruggen, B.; Deguchi, K.; Malki, B.; Craninckx, J. A 70 dB SNDR 200 MS/s 2.3 mW dynamic pipelined SAR ADC in 28nm digital CMOS. In 2014 Symposium on VLSI Circuits Digest of Technical Papers; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2014; pp. 268–269. [Google Scholar]

- Van der Goes, F.; Ward, C.M.; Astgimath, S.; Yan, H.; Riley, J.; Zeng, Z.; Mulder, J.; Wang, S.; Bult, K. A 1.5 mW 68 dB SNDR 80 MS/s 2×interleavedpipelined SAR ADC in 28 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 2835–2845. [Google Scholar] [CrossRef]

- Lim, Y.; Flynn, M.P. A 1 mW 71.5 dB SNDR 50 MS/s 13 bit Fully Differential Ring Amplifier Based SAR-Assisted Pipeline ADC. IEEE J. Solid-State Circuits 2015, 50, 2901–2911. [Google Scholar] [CrossRef]

- Shen, Y.; Zhu, Z.; Liu, S.; Yang, Y. A Reconfigurable 10-to-12-b 80-to-20-MS/s Bandwidth Scalable SAR ADC. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 65, 51–60. [Google Scholar] [CrossRef]

- Chung, Y.-H.; Zeng, Q.-F.; Lin, Y.-S. A 12-bit SAR ADC with a DAC-Configurable Window Switching Scheme. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 67, 358–368. [Google Scholar] [CrossRef]

- Zhang, M.; Noh, K.; Fan, X.; Sanchez-Sinencio, E. A 0.8–1.2 V 10–50 MS/s 13-bit Subranging Pipelined-SAR ADC Using a Temperature-Insensitive Time-Based Amplifier. IEEE J. Solid-State Circuits 2017, 52, 2991–3005. [Google Scholar] [CrossRef]

- Martens, E.; Hershberg, B.; Craninckx, J. A 69-dB SNDR 300-MS/s Two-Time Interleaved Pipelined SAR ADC in 16-nm CMOS FinFET With Capacitive Reference Stabilization. IEEE J. Solid-State Circuits 2018, 53, 1161–1171. [Google Scholar] [CrossRef]

- Chung, Y.-H.; Yen, C.-W.; Tsai, P.-K. A 12-bit 10-MS/s SAR ADC with a binary-window DAC switching scheme in 180-nm CMOS. Int. J. Circuit Theory Appl. 2018, 46, 748–763. [Google Scholar] [CrossRef]

- Chung, Y.-H.; Yen, C.-W.; Tsai, P.-K.; Chen, B.-W. A 12-bit 40-MS/s SAR ADC with a Fast-Binary-Window DAC Switching Scheme. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 1989–1998. [Google Scholar] [CrossRef]

- Liu, S.; Shen, Y.; Zhu, Z. A 12-Bit 10 MS/s SAR ADC with High Linearity and Energy-Efficient Switching. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1616–1627. [Google Scholar] [CrossRef]

- Liu, C.-C.; Chang, S.-J.; Huang, G.-Y.; Lin, Y.-Z. A 10-bit 50-MS/s SAR ADC with a Monotonic Capacitor Switching Procedure. IEEE J. Solid-state Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Zhu, Y.; Chan, C.-H.; Chio, U.-F.; Sin, S.-W.; Martins, R.P.; Maloberti, F. A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 1111–1121. [Google Scholar] [CrossRef]

- Verma, D.; Shehzad, K.; Khan, D.; Ain, Q.U.; Kim, S.J.; Lee, D.; Pu, Y.G.; Lee, M.; Hwang, K.C.; Yang, Y.; et al. A Design of 8 fJ/Conversion-Step 10-bit 8 MS/s Low Power Asynchronous SAR ADC for IEEE 802.15.1 IoT Sensor Based Applications. IEEE Access 2020, 8, 85869–85879. [Google Scholar] [CrossRef]

- Shehzad, K.; Verma, D.; Khan, D.; Ain, Q.U.; Basim, M.; Kim, S.J.; Pu, Y.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. Design of a Low Power 10-b 8-MS/s Asynchronous SAR ADC with On-Chip Reference Voltage Generator. Electronics 2020, 9, 872. [Google Scholar] [CrossRef]

- Verma, D.; Shehzad, K.; Khan, D.; Kim, S.J.; Pu, Y.G.; Yoo, S.-S.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. A Design of Low-Power 10-bit 1-MS/s Asynchronous SAR ADC for DSRC Application. Electronics 2020, 9, 1100. [Google Scholar] [CrossRef]

- Abo, A.; Gray, P. A 1.5 V, 10-bit, 14 MS/s CMOS pipeline analog-to-digital converter. In 1998 Symposium on VLSI Circuits. Digest of Technical Papers (Cat. No.98CH36215); Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2002; Volume 34, pp. 599–606. [Google Scholar] [CrossRef]

- Van Elzakker, M.; van Tuijl, E.; Geraedts, P.; Schinkel, D.; Klumperink, E.; Nauta, B. A 10-bit charge-redistribution ADC consuming 1.9 W at 1 Ms/s. IEEE J. Solid-State Circuits 2010, 45, 1007–1015. [Google Scholar] [CrossRef]

- Yoshioka, M.; Ishikawa, K.; Takayama, T.; Tsukamoto, S. A 10-b 50-Ms/s 820-_WSAR ADC with on-chip digital calibration. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 410–416. [Google Scholar] [CrossRef] [PubMed]

| Parameter | [15] | [16] | [19] | [20] | [21] | This Work |

|---|---|---|---|---|---|---|

| Process (nm) | 180 | 180 | 180 | 180 | 180 | 65 |

| Supply Voltage (V) | 1.8 | 1.5 | 1.5 | 1.2 | 1.8 | 1 |

| Resolution (bit) | 12 | 12 | 12 | 12 | 12 | 12 |

| Sampling Rate (MS/s) | 20 | 20 | 10 | 40 | 10 | 20 |

| SNDR (dB) | 64.6 | 59.1 | 63.8 | 62.5 | 66.9 | 65.44 |

| ENOB (bits) | 10.44 | 9.52 | 10.31 | 10.09 | 10.82 | 10.58 |

| DNL (LSB) | −0.51/0.445 | −0.65/0.58 | 1.05 | 2.33 | 0.69 | −0.46/0.48 |

| INL (LSB) | −1.01/0.98 | −1.06/1.04 | 1.38 | 3.1 | 1.15 | −0.50/0.58 |

| Power Consumption (µW) | 1770 | 1220 | 600 | 1320 | 820 | 472.2 |

| FOM (fJ/conv. step) | 63.7 | 83 | 47.2 | 30.4 | 44.2 | 15.42 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shehzad, K.; Verma, D.; Khan, D.; Ain, Q.U.; Basim, M.; Kim, S.J.; Rikan, B.S.; Pu, Y.G.; Hwang, K.C.; Yang, Y.; et al. A Low-Power 12-Bit 20 MS/s Asynchronously Controlled SAR ADC for WAVE ITS Sensor Based Applications. Sensors 2021, 21, 2260. https://doi.org/10.3390/s21072260

Shehzad K, Verma D, Khan D, Ain QU, Basim M, Kim SJ, Rikan BS, Pu YG, Hwang KC, Yang Y, et al. A Low-Power 12-Bit 20 MS/s Asynchronously Controlled SAR ADC for WAVE ITS Sensor Based Applications. Sensors. 2021; 21(7):2260. https://doi.org/10.3390/s21072260

Chicago/Turabian StyleShehzad, Khuram, Deeksha Verma, Danial Khan, Qurat Ul Ain, Muhammad Basim, Sung Jin Kim, Behnam Samadpoor Rikan, Young Gun Pu, Keum Cheol Hwang, Youngoo Yang, and et al. 2021. "A Low-Power 12-Bit 20 MS/s Asynchronously Controlled SAR ADC for WAVE ITS Sensor Based Applications" Sensors 21, no. 7: 2260. https://doi.org/10.3390/s21072260

APA StyleShehzad, K., Verma, D., Khan, D., Ain, Q. U., Basim, M., Kim, S. J., Rikan, B. S., Pu, Y. G., Hwang, K. C., Yang, Y., & Lee, K.-Y. (2021). A Low-Power 12-Bit 20 MS/s Asynchronously Controlled SAR ADC for WAVE ITS Sensor Based Applications. Sensors, 21(7), 2260. https://doi.org/10.3390/s21072260