Power-Oriented Monitoring of Clock Signals in FPGA Systems for Critical Application

Abstract

1. Introduction

2. Related Works

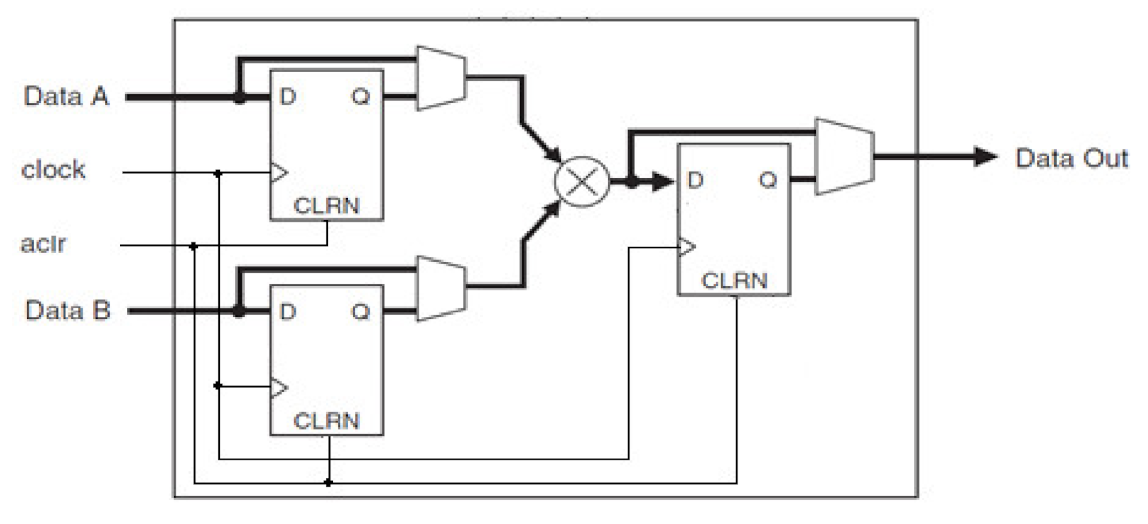

3. Logical and Power-Oriented Checkability

4. The Results of Experimental Studies

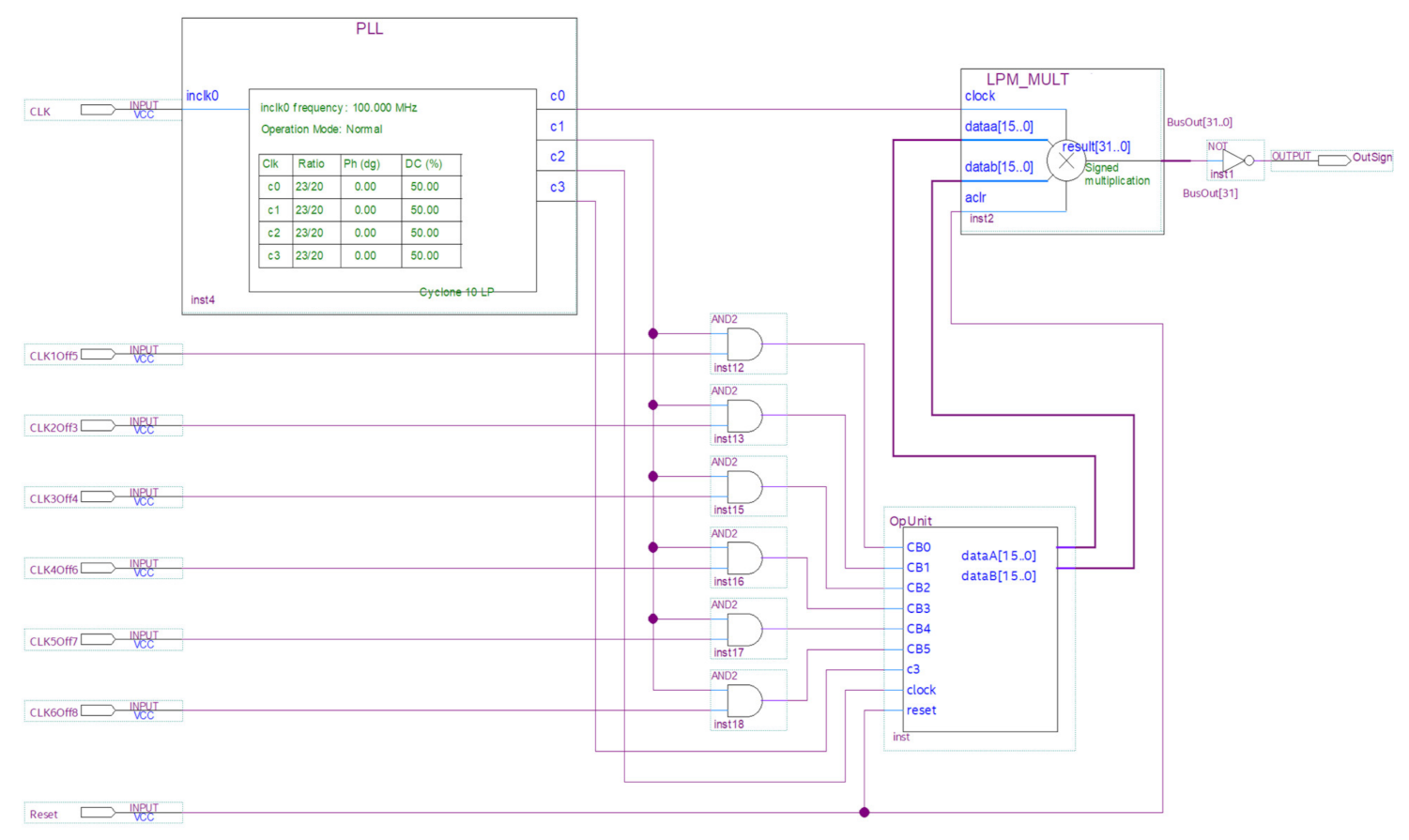

4.1. Experimental Conditions

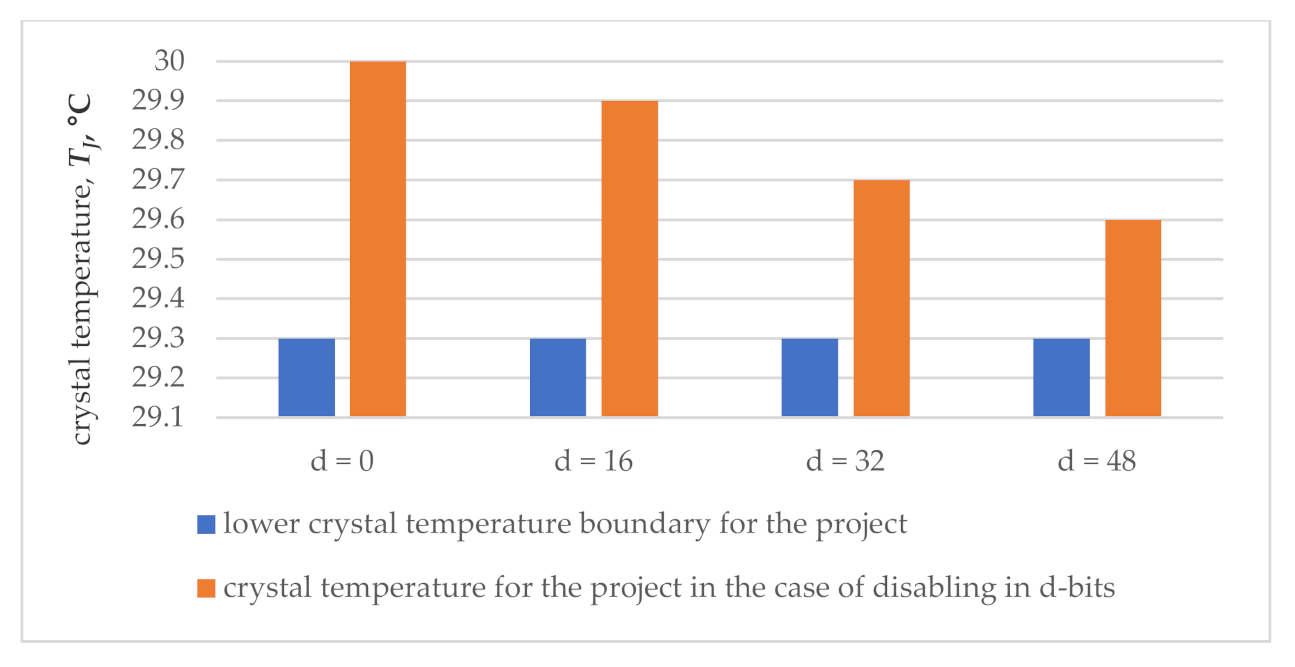

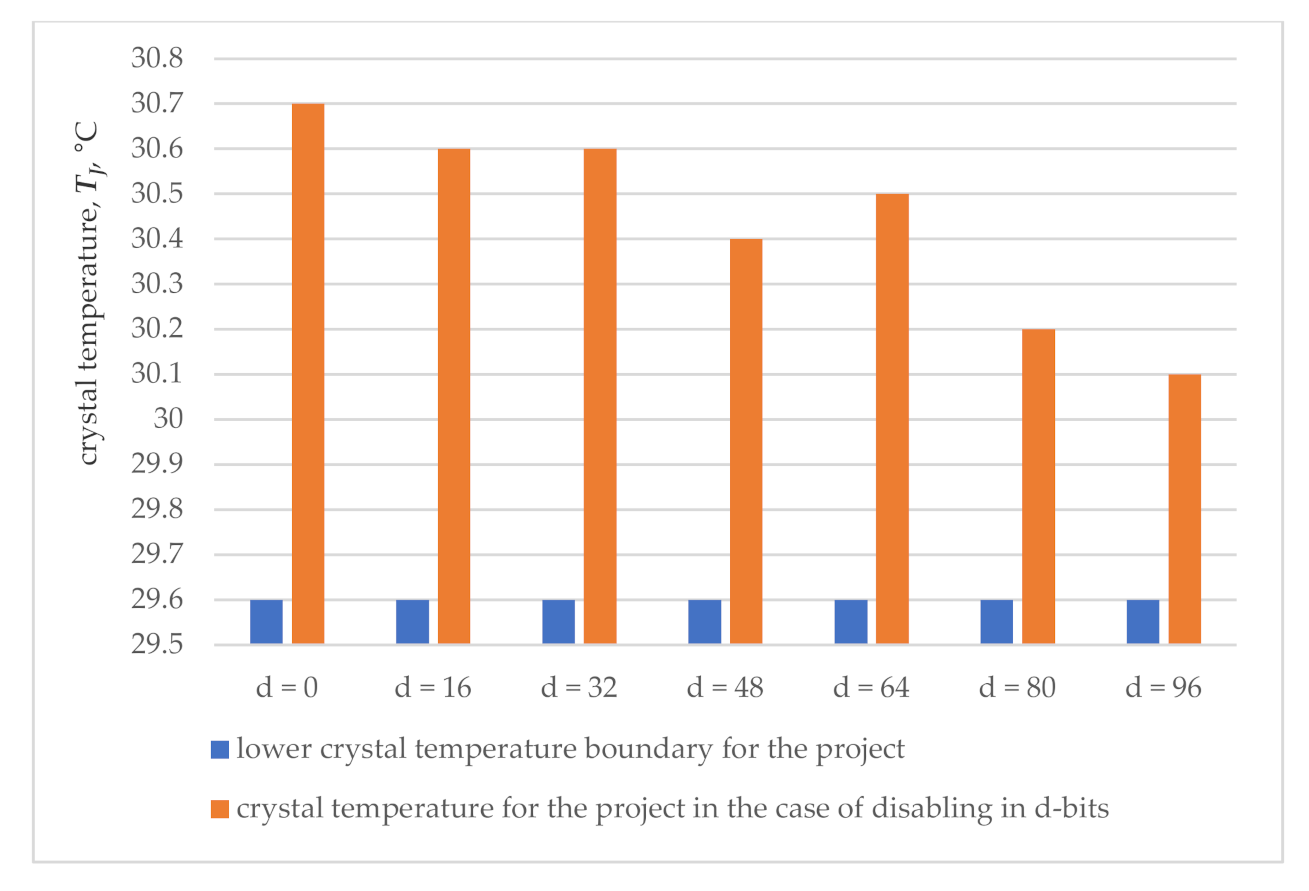

4.2. Investigating the Thermal Checkability and Monitoring the Circuit of FPGA System

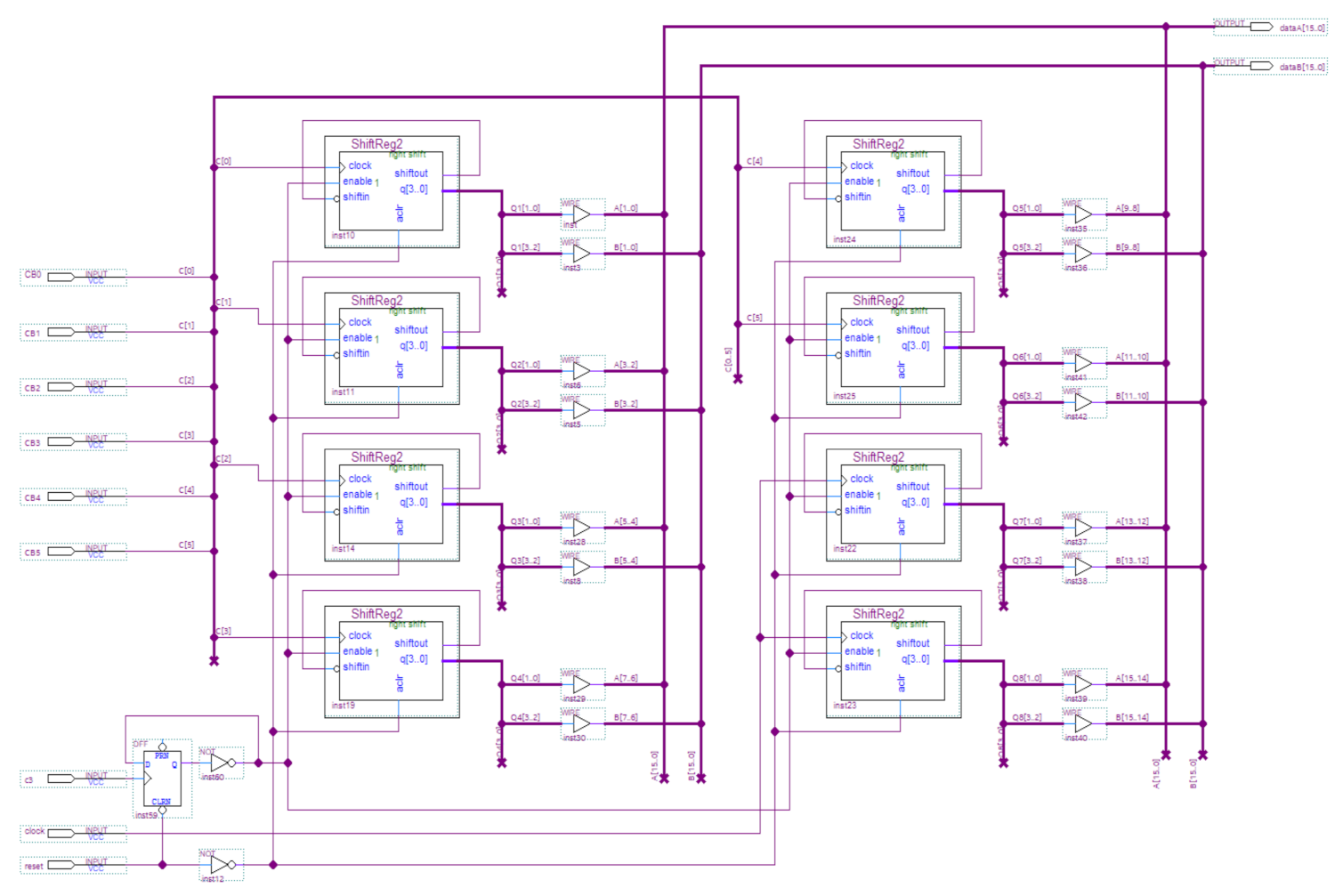

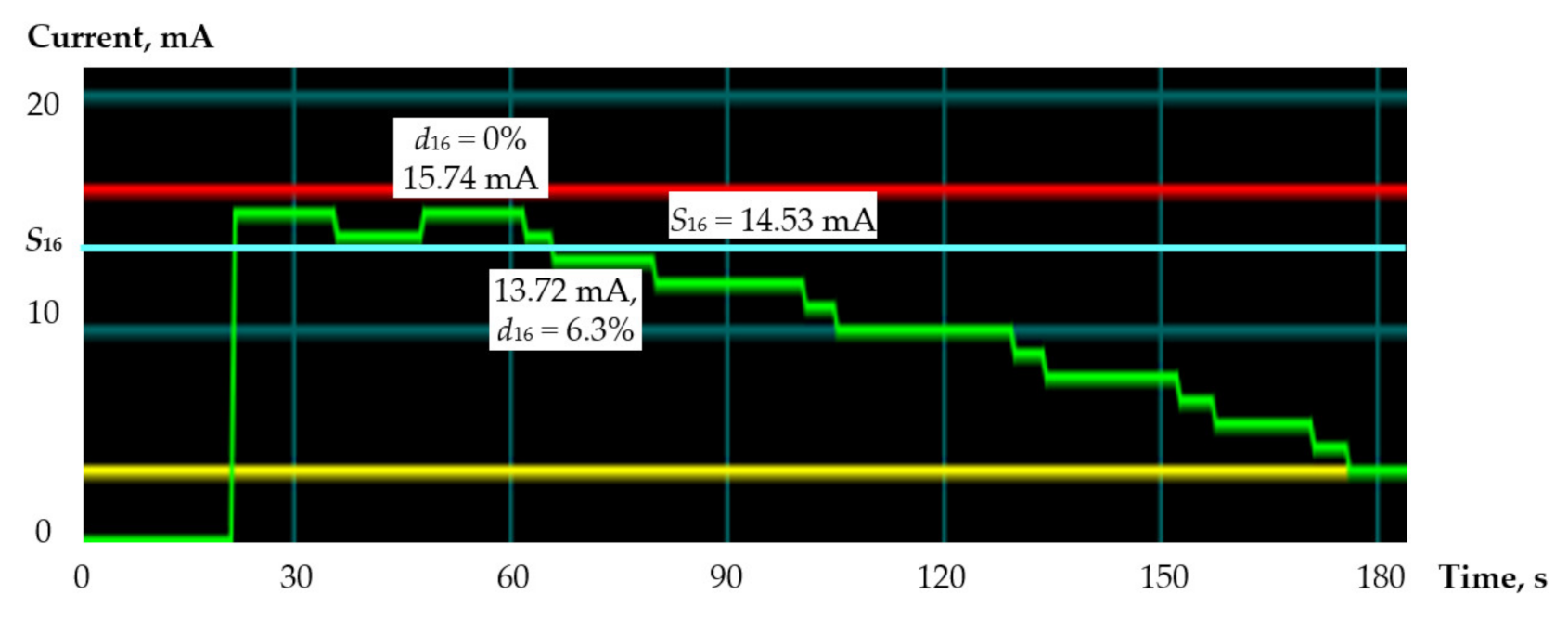

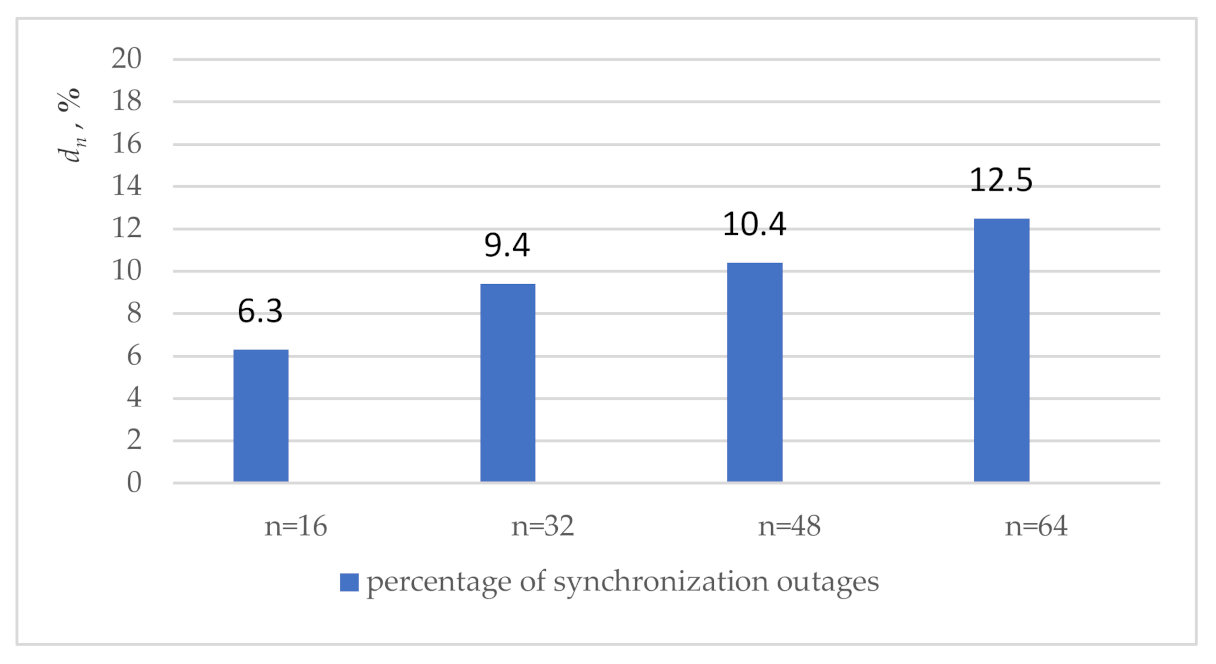

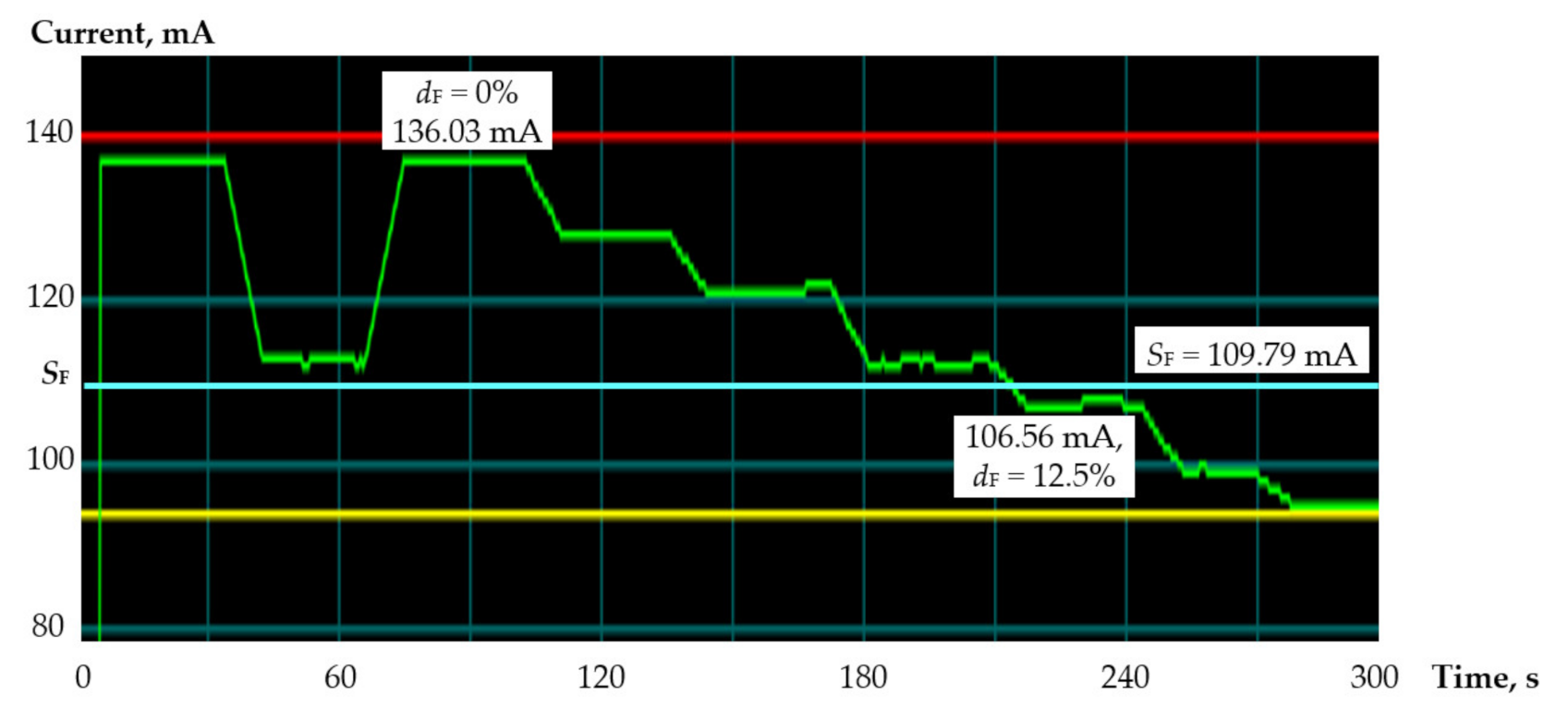

4.3. Investigating the Checkability of FPGA System and Its Circuit Monitoring by Current Consumption

- Target Intel Cyclone 10 LP FPGA chip: 10CL025YU256I7G [40];

- Programmable generator of clock pulses programmable clock generator;

- Subsystem for measuring the current consumed by the target microcircuit;

- Toggle switches and push buttons to control the experiment progress.

- Normal operation (mode 1);

- Operation at zero activity of information signals (mode 2);

- Operation under shutdown conditions of the operand register bits (mode 3).

- Normal operation;

- The zero-activity mode of the input signals, provided by stopping the formation of operands as well as a result of multiplication (the reset signal was supplied to the circuit and held for one minute);

- The mode of disconnecting the synchronization of Johnson counters, which form the bits 0..1, 0..3, 0..5, 0..7, 0..9, 0..11 and 0..11, 0..13, 0..15, 0..17, 0..19, 0..21, 0..22 of both operands for cases n = 16, 32, 48 and n = 64, respectively.

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Pauk, J.; Wasilewska, A.; Ihnatouski, M. Infrared Thermography Sensor for Disease Activity Detection in Rheumatoid Arthritis Patients. Sensors 2019, 19, 3444. [Google Scholar] [CrossRef] [PubMed]

- Bartels, C.; Zhang, C.; Payá-Vayá, G.; Blume, H. A Synthesizable Temperature Sensor on FPGA Using DSP-Slices for Reduced Calibration Overhead and Improved Stability. In Proceedings of the International Conference on Architecture of Computing Systems, Porto, Portugal, 24–27 March 2015; Volume 9017, pp. 161–172. [Google Scholar] [CrossRef]

- Enger, N. Care and Feeding of FPGA Power Supplies: A How and Why Guide to Success. Analog. Dialogue 2018, 52, 33–45. [Google Scholar]

- Ivanchenko, O.; Kharchenko, V.; Moroz, B.; Kabak, L.; Konovalenko, S. Risk Assessment of Critical Energy Infrastructure Considering Physical and Cyber Assets: Methodology and Models. In Proceedings of the 10th IEEE International Conference on Intelligent Data Acquisition and Advanced Computing Systems: Technology and Applications, Lviv, Ukraine, 20–21 September 2018; pp. 225–228. [Google Scholar] [CrossRef]

- Marvin, R. Risk Assessment. Common Cause Failures. Available online: https://www.ntnu.edu/documents/624876/1277591044/ccf.pdf/f435f724-469d-4492-860a-66eca10e6bd2 (accessed on 20 January 2020).

- Kharchenko, V.; Sachenko, A.; Kochan, V.; Fesenko, H. Reliability and Survivability Models of Integrated Drone-Based Systems for Post Emergency Monitoring of NPPs. In Proceeding of the IEEE International Conference on Information and Digital Technologies, Rzeszov, Poland, 5–7 July 2016; pp. 127–132. [Google Scholar] [CrossRef]

- IEC61508. Functional Safety of Electrical, Electronic, Programmable Electronic Safety Related Systems. General Requirements; Rep. IEC: Geneva, Switzerland, 2010. [Google Scholar]

- IEC61513. Nuclear Power Plants: Instrumentation & Control Systems Important to Safety. General Requirements for Systems; Rep. IEC: Geneva, Switzerland, 2001. [Google Scholar]

- Jung, J.; Ahmed, I. Development of FPGA-based reactor trip functions using systems engineering approach. Nucl. Eng. Technol. 2016, 48, 1047–1057. [Google Scholar] [CrossRef][Green Version]

- Smith, D.; Simpson, K. The Safety Critical Systems Handbook, 5th ed.; Butterworth-Heinemann: Oxford, UK, 2019. [Google Scholar]

- Edstrom, J.; Tilevich, E. Reusable and Extensible Fault Tolerance for RESTful Applications. In Proceedings of the 11th IEEE International Conference on Trust, Security and Privacy in Computing and Communications, Liverpool, UK, 25–27 June 2012. [Google Scholar] [CrossRef]

- Jhawar, R.; Piuri, V. Fault Tolerance and Resilience in Cloud Computing Environments. In Computer and Information Security Handbook; Morgan Kaufmann: Cambridge, MA, USA, 2017; pp. 165–181. [Google Scholar]

- Ren, Y.; Wang, C.; Hong, H. An All CMOS Temperature Sensor for Thermal Monitoring of VLSI Circuits. In Proceedings of the IEEE Circuits and Systems International Conference on Testing and Diagnosis, Chengdu, China, 28–29 April 2009; pp. 1–5. [Google Scholar] [CrossRef]

- Sarkany, Z.; Rencz, M. Design considerations to enhance thermal testability. In Proceedings of the IEEE Electronics Packaging Technology Conference, Singapore, 5–7 December 2012; pp. 148–152. [Google Scholar] [CrossRef]

- Altet, J.; Rubio, A. Thermal Testing of Integrated Circuits; Springer Science + Business Media: Dordrecht, The Netherlands, 2002. [Google Scholar] [CrossRef]

- Xilinx Power Estimator User Guide. Available online: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2019_2/ug440-xilinx-power-estimator.pdf (accessed on 20 April 2019).

- Intel Quartus Prime Standard Edition User Guide: Power Analysis and Optimization. 2018. Available online: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qps-power.pdf (accessed on 20 March 2019).

- Analog Devices Digital Temperature Sensors. Available online: https://www.analog.com/en/parametricsearch/11020 (accessed on 20 February 2020).

- Analog Devices Power Monitors. Available online: https://www.analog.com/en/parametricsearch/11099 (accessed on 20 February 2020).

- Intel FPGA Temperature Sensor IP Core User Guide. Available online: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_alttemp_sense.pdf (accessed on 20 February 2020).

- Metra, C.; Favalli, M.; Ricco, B. Concurrent Checking of Clock Signal Correctness. IEEE Design Test Comput. 1998, 15, 42–48. [Google Scholar] [CrossRef]

- Luo, P.; Fei, Y. Faulty Clock Detection for Crypto Circuits Against Differential Fault Analysis Attack. IACR Cryptol. ePrint Arch. 2016, 967, 1–8. [Google Scholar]

- Li, G.M.; Richmond, G.J.; Raman, S. Circuit and Method for Monitoring the Status of a Clock Signal. U.S. Patent 7,454,645, 18 November 2008. [Google Scholar]

- Chakrabarty, K.; Swaminathan, S. Built-in self-testing of high-performance circuits using twisted-ring counters. In Proceedings of the IEEE International Symposium on Circuits and Systems, Geneva, Switzerland, 28–31 May 2000. [Google Scholar] [CrossRef]

- IEEE Std1500-2005. Standard Testability Method for Embedded Core-Based IC; IEEE: New York, NY, USA, 2005. [Google Scholar] [CrossRef]

- Drozd, O.; Kharchenko, V.; Rucinski, A.; Kochanski, T.; Garbos, R.; Maevsky, D. Development of Models in Resilient Computing. In Proceedings of the IEEE Conference on Dependable Systems, Leeds, UK, 5–7 June 2019. [Google Scholar] [CrossRef]

- Hiromoto, R. Parallelism and complexity of a small-world network model. Int. J. Comput. 2016, 15, 72–83. [Google Scholar]

- Palagin, A.; Opanasenko, V. The implementation of extended arithmetics on FPGA-based structures. In Proceedings of the IDAACS International Conference, Bucharest, Romania, 21–23 September 2017. [Google Scholar] [CrossRef]

- Murugesan, S.; Gangadharan, G. Harnessing Green IT. Principles and Practices; Wiley and Sons Ltd.: Hoboken, NJ, USA, 2012. [Google Scholar]

- Tyurin, S.; Kamenskih, A. Green Logic: Models, Methods, Algorithms. In Green IT Engineering: Concepts, Models, Complex Systems Architectures. Studies in Systems, Decision and Control; Springer: Berlin, Germany, 2017; Volume 74, pp. 69–86. [Google Scholar] [CrossRef]

- Drozd, A.; Antoshchuk, S.; Drozd, J.; Zashchoklin, K.; Drozd, M.; Kuznietsov, N.; Al-Dhabi, M.; Nikul, V. Checkable FPGA Design: Energy Consumption, Throughput and Trustworthiness. In Green IT Engineering: Social, Business and Industrial Applications; Springer: Berlin, Germany, 2019; Volume 171, pp. 74–94. [Google Scholar] [CrossRef]

- Final Report on the August 14, 2003 Blackout in the United States and Canada: Causes and Recommendations. Available online: https://www3.epa.gov/region1/npdes/merrimackstation/pdfs/ar/AR-1165.pdf (accessed on 20 January 2020).

- The True Toll of the Chernobyl Disaster. Available online: https://www.bbc.com/future/article/20190725-will-we-ever-know-chernobyls-true-death-toll (accessed on 20 January 2020).

- Nicolaidis, M.; Zorian, Y.; Pradhan, D. On-Line Testing for VLSI. J. Electron. Test. Theory Appl. 1998, 12, 7–159. [Google Scholar] [CrossRef]

- Metra, C.; Schiano, L.; Favalli, M.; Ricco, B. Self-Checking scheme for the on-line testing of power supply noise. In Proceedings of the Design, Automation and Test in Europe Conference, Paris, France, 4–8 March 2002; pp. 832–836. [Google Scholar]

- Székely, V.; Márta, C.; Rencz, M.; Benedek, Z.; Courtois, B. Design for Thermal Testability (DFTT) and a CMOS Realization. In Proceedings of the 1st Therminic Workshop, Grenoble, France, 25–26 September 1995. [Google Scholar]

- Székely, V.; Rencz, M.; Karam, J.M.; Lubaszewski, M.; Courtois, B. Thermal Monitoring of Self-Checking Systems. J. Electron. Test. 1998, 12, 81–92. [Google Scholar] [CrossRef]

- Velusamy, S.; Huang, W.; Lach, J.; Stan, M.; Skadron, K. Monitoring Temperature in FPGA based SoCs. In Proceedings of the International conference on Computer Design: VLSI in Computers & Processors, San Jose, CA, USA, 2–5 October 2005; pp. 634–641. [Google Scholar]

- Intel FPGA Integer Arithmetic IP Cores User Guide. Available online: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_lpm_alt_mfug.pdf (accessed on 20 February 2020).

- Intel Cyclone 10 LP Core Fabric and General Purpose I/Os Handbook. Available online: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-10/c10lp-51003.pdf (accessed on 31 August 2020).

- Intel Quartus Prime Standard Edition User Guide. Available online: https://www.intel.com/content/dam/altera-www/global/en_US/pdfs/literature/ug/ug-qps-getting-started.pdf (accessed on 31 August 2020).

- PowerPlay Power Analysis. Quartus II Handbook Version 13.1.0. Available online: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/qts/qts_qii53013.pdf (accessed on 20 April 2019).

- Renbi, A.; Lindh, L. Power and energy efficiency evaluation for HW and SW implementation of nxn matrix multiplication on Altera FPGAs. In Proceedings of the 6th FPGAworld Conference, Stockholm, Sweden, 10 September 2009; pp. 45–51. [Google Scholar] [CrossRef]

- Sachenko, A.; Kochan, V.; Turchenko, V.; Tymchyshyn, V.; Vasylkiv, N. Intelligent nodes for distributed sensor network. In Proceedings of the IEEE Instrumentation and Measurement Technology Conference, Venice, Italy, 24–26 May 1999; pp. 1479–1484. [Google Scholar]

- Analog Devices LTC2986. Available online: https://www.analog.com/en/products/ltc2986.html#product-overview (accessed on 31 August 2020).

- Drozd, O.; Antoniuk, V.; Drozd, M.; Karpinskyi, V.; Bykovyy, P. Power-consumption-oriented checkability for FPGA-based components of safety-related systems. Int. J. Comput. 2019, 18, 118–126. [Google Scholar]

- Intel® Cyclone® 10 LP FPGA Evaluation Kit User Guide. Available online: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-c10-lp-eval-kit.pdf (accessed on 31 August 2020).

- Mangard, S.; Popp, T.; Gammel, B. Side-Channel Leakage of Masked CMOS Gates. In CT-RSA 2005, LNCS; Springer: Berlin/Heidelberg, Germany, 2005; Volume 3376, pp. 351–365. [Google Scholar] [CrossRef]

- Drozd, A.; Drozd, J.; Antoshchuk, S.; Antonyuk, V.; Zashcholkin, K.; Drozd, M.; Titomir, O. Green Experiments with FPGA. In Green IT Engineering: Components, Networks and Systems Implementation; Springer: Berlin, Germany, 2017; Volume 105, pp. 219–239. [Google Scholar] [CrossRef]

- Vikas, D. A review on glitch reduction techniques. Int. J. Res. Eng. Technol. 2014, 3, 145–148. [Google Scholar]

| d | d,% | PD, mW | PDCD, mW | PDCS, mW | PDIO, mW | TJ, °C |

|---|---|---|---|---|---|---|

| 0 | 0 | 166.16 | 18.61 | 73.25 | 74.30 | 30.0 |

| 16 | 12.5 | 163.96 | 17.06 | 73.25 | 73.65 | 29.9 |

| 32 | 25.0 | 157.17 | 11.33 | 73.22 | 72.62 | 29.7 |

| 48 | 37.5 | 153.05 | 7.99 | 73.21 | 71.85 | 29.6 |

| d | d,% | PD, mW | PDCD, mW | PDCS, mW | PDIO, mW | TJ, °C |

|---|---|---|---|---|---|---|

| 0 | 0 | 189.72 | 38.25 | 73.40 | 78.07 | 30.7 |

| 16 | 6.3 | 187.61 | 37.17 | 73.39 | 77.05 | 30.6 |

| 32 | 12.5 | 185.15 | 34.87 | 73.38 | 76.90 | 30.6 |

| 48 | 18.8 | 180.92 | 31.22 | 73.37 | 76.32 | 30.4 |

| 64 | 25.0 | 176.56 | 28.10 | 73.36 | 75.10 | 30.3 |

| 80 | 31.3 | 173.87 | 26.02 | 73.35 | 74.51 | 30.2 |

| 96 | 37.5 | 171.42 | 24.99 | 73.34 | 73.09 | 30.1 |

| d | d16,% | I16, mA | d32,% | I32, mA | d48,% | I48, mA |

|---|---|---|---|---|---|---|

| 0 | 0 | 15.74 | 0 | 20.99 | 0 | 29.47 |

| 4 | 6.3 | 13.72 | 3.1 | 18.97 | 2.1 | 27.85 |

| 8 | 12.5 | 12.51 | 6.3 | 16.95 | 4.2 | 26.24 |

| 12 | 18.8 | 10.49 | 9.4 | 15.34 | 6.3 | 24.62 |

| 16 | 25.0 | 8.88 | 12.5 | 13.32 | 8.3 | 22.20 |

| 20 | 31.3 | 6.86 | 15.6 | 11.30 | 10.4 | 20.18 |

| 24 | 37.5 | 5.25 | 18.8 | 8.88 | 12.5 | 18.16 |

| d | d64,% | I64, mA | d | d64,% | I64, mA |

|---|---|---|---|---|---|

| 0 | 0 | 54.49 | 24 | 9.4 | 41.98 |

| 4 | 1.6 | 53.28 | 28 | 10.9 | 39.36 |

| 8 | 3.1 | 51.26 | 32 | 12.5 | 37.13 |

| 12 | 4.7 | 49.84 | 36 | 14.1 | 34.31 |

| 16 | 6.3 | 47.23 | 40 | 15.6 | 32.29 |

| 20 | 7.8 | 44.40 | 44 | 17.2 | 30.27 |

| d | dF,% | IF, mA | d | dF,% | IF, mA |

|---|---|---|---|---|---|

| 0 | 0 | 136.03 | 4 | 12.5 | 106.56 |

| 1 | 3.1 | 127.95 | 5 | 15.6 | 103.74 |

| 2 | 6.3 | 121.50 | 6 | 18.8 | 96.07 |

| 3 | 9.4 | 111.81 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Drozd, O.; Nowakowski, G.; Sachenko, A.; Antoniuk, V.; Kochan, V.; Drozd, M. Power-Oriented Monitoring of Clock Signals in FPGA Systems for Critical Application. Sensors 2021, 21, 792. https://doi.org/10.3390/s21030792

Drozd O, Nowakowski G, Sachenko A, Antoniuk V, Kochan V, Drozd M. Power-Oriented Monitoring of Clock Signals in FPGA Systems for Critical Application. Sensors. 2021; 21(3):792. https://doi.org/10.3390/s21030792

Chicago/Turabian StyleDrozd, Oleksandr, Grzegorz Nowakowski, Anatoliy Sachenko, Viktor Antoniuk, Volodymyr Kochan, and Myroslav Drozd. 2021. "Power-Oriented Monitoring of Clock Signals in FPGA Systems for Critical Application" Sensors 21, no. 3: 792. https://doi.org/10.3390/s21030792

APA StyleDrozd, O., Nowakowski, G., Sachenko, A., Antoniuk, V., Kochan, V., & Drozd, M. (2021). Power-Oriented Monitoring of Clock Signals in FPGA Systems for Critical Application. Sensors, 21(3), 792. https://doi.org/10.3390/s21030792