Intelligent Electromagnetic Sensors for Non-Invasive Trojan Detection

Abstract

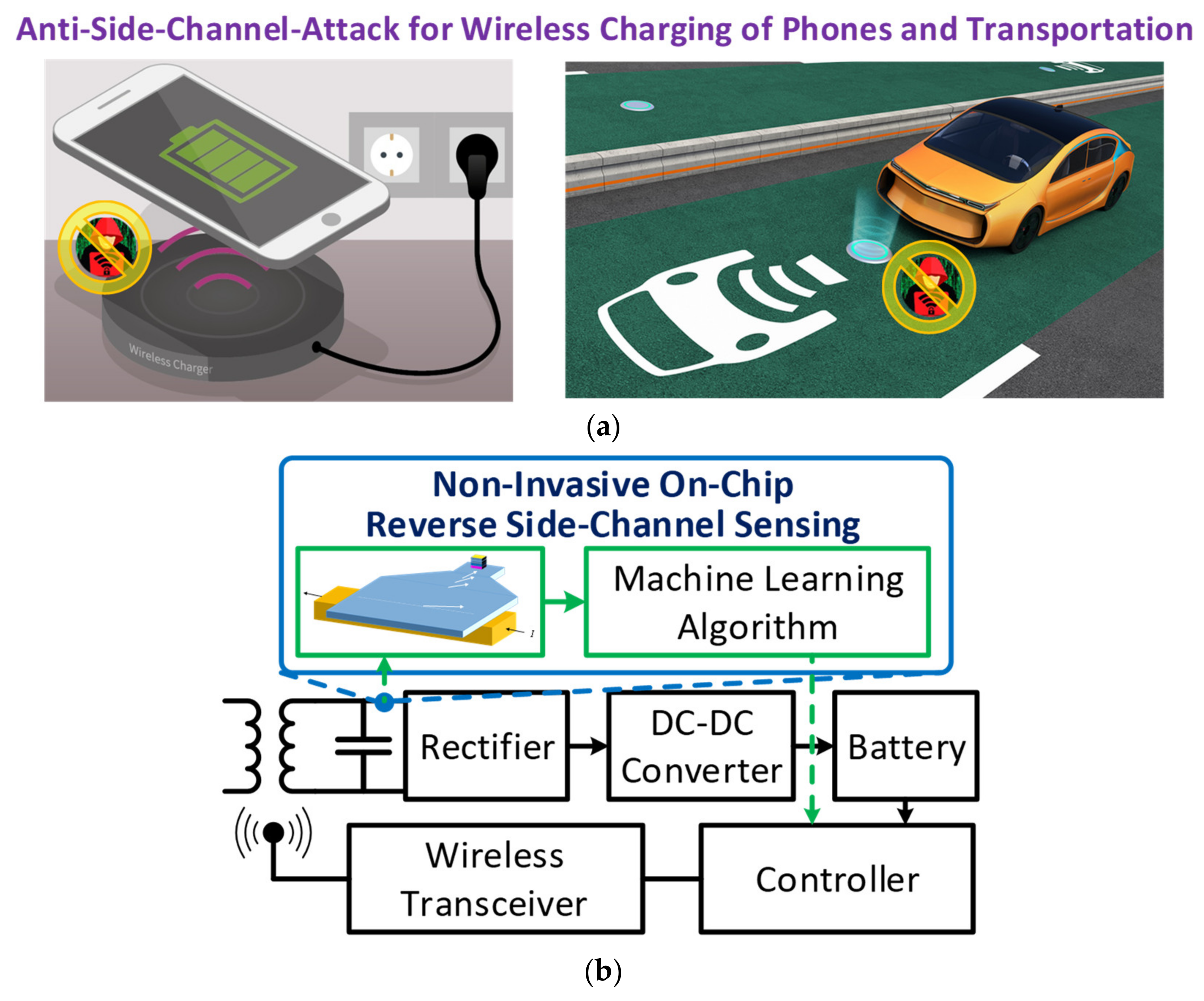

:1. Introduction

2. Relevant Work

2.1. Survey of Hardware Trojans

2.1.1. Hardware Trojan Taxonomy and Insertion

2.1.2. Analog Circuit Trojans

2.2. Hardware Trojan Detection

2.2.1. Side-Channel Detection

2.2.2. IC Current Sensing for Hardware Trojan Detection

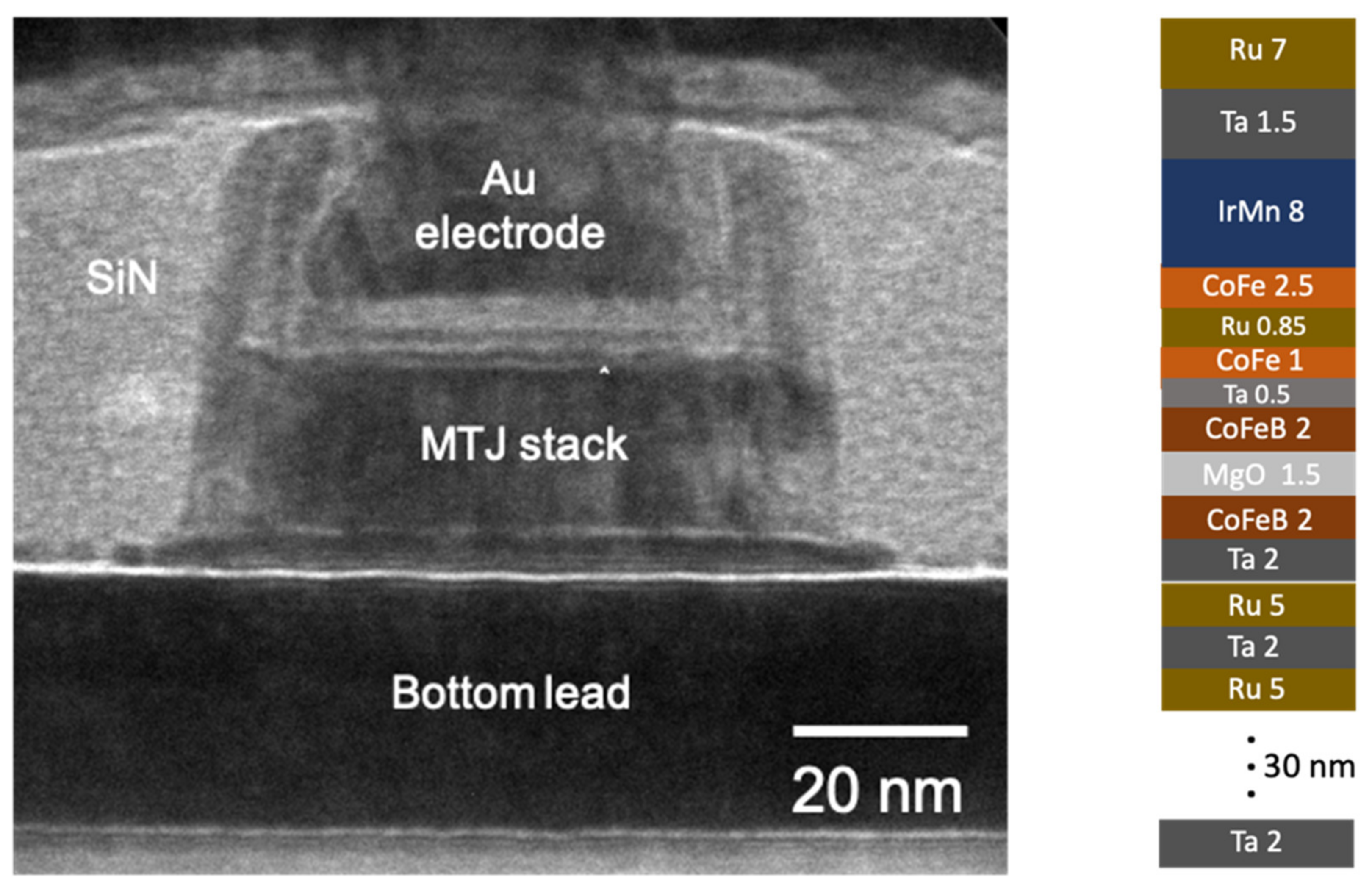

3. On-Chip Magnetic Tunnel Junction (MTJ) Based Sensors for Instant Device Power/Current and EM Emission Monitoring

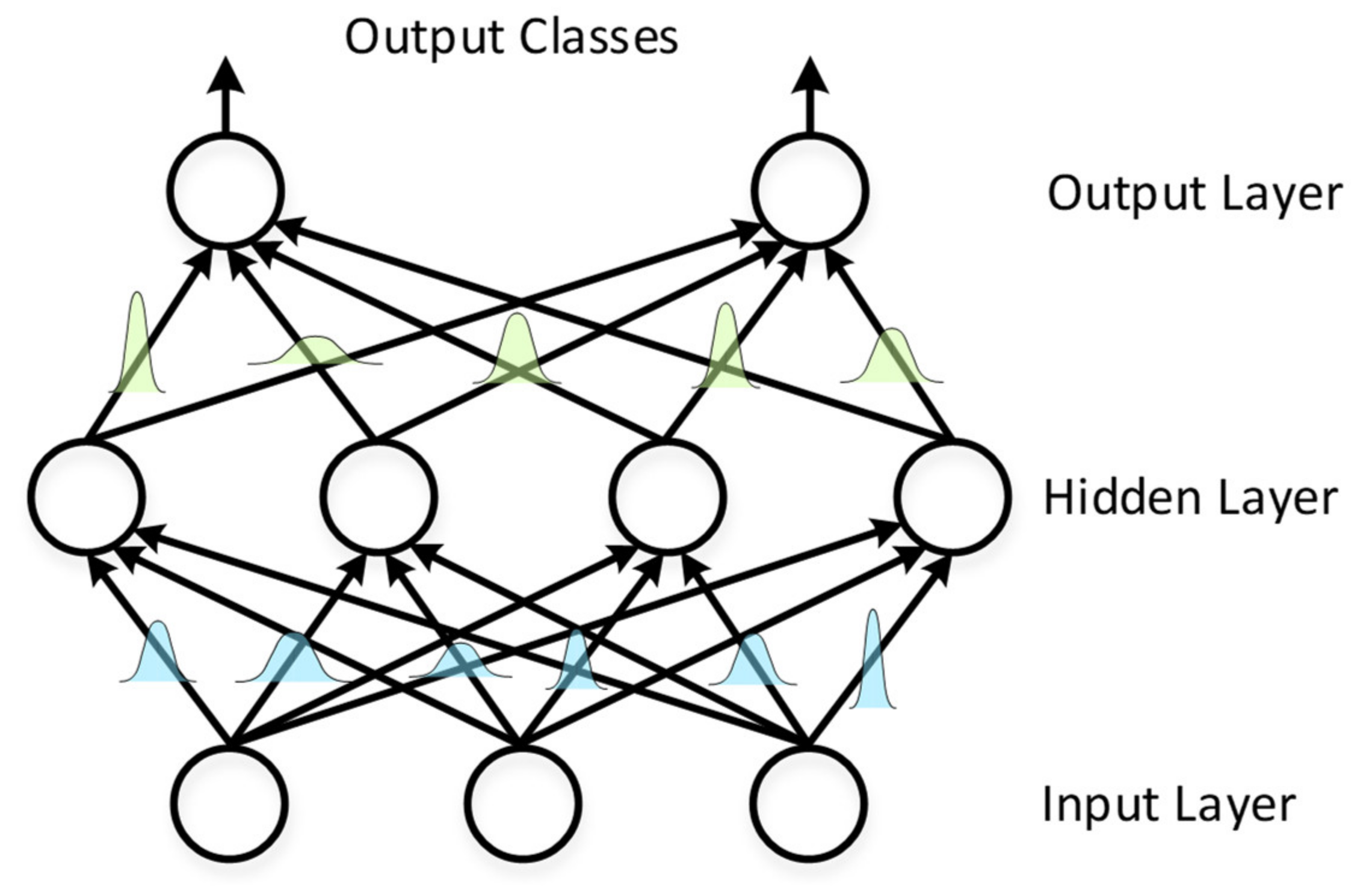

4. Machine Learning Algorithms for Real-Time Threat-and-Vulnerability Detection

4.1. Bayesian Neural Networks

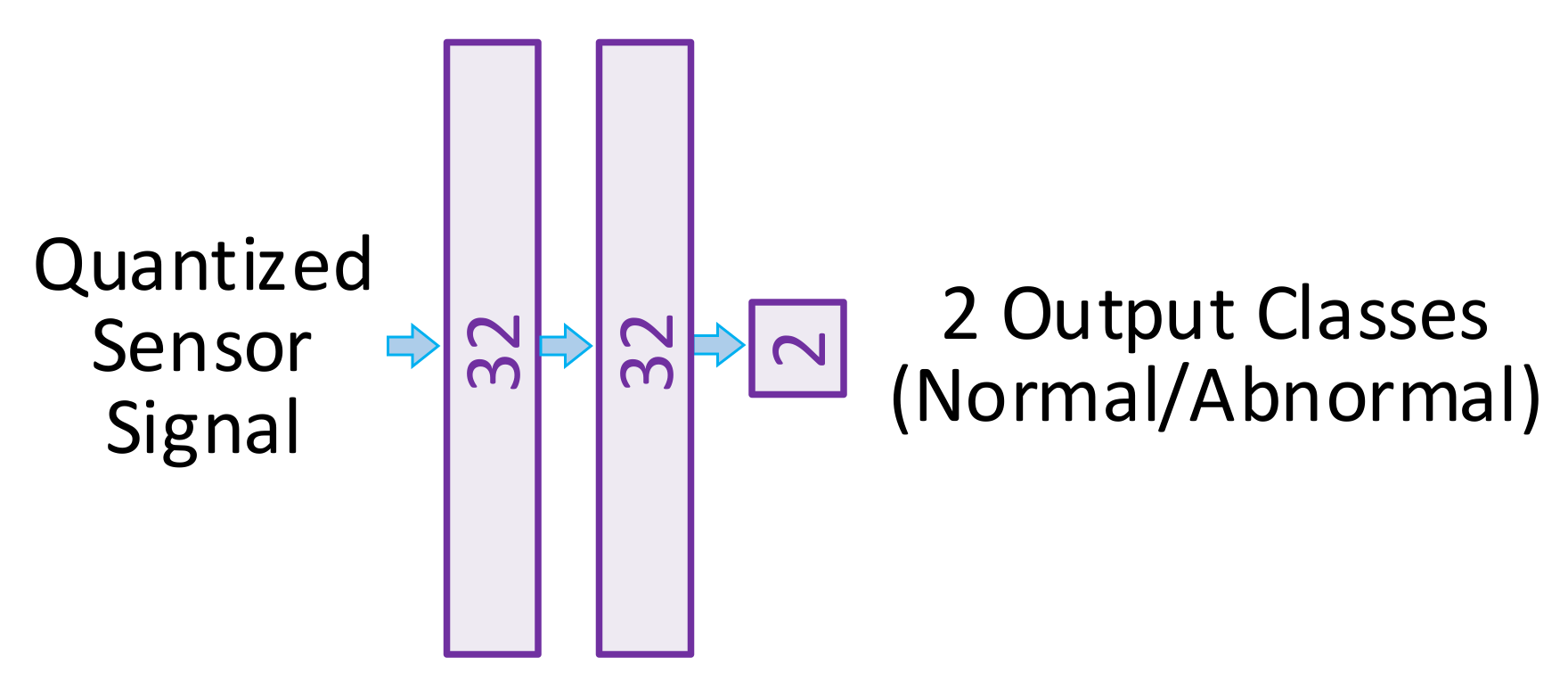

4.2. BNN Architecture and Optimization

5. Experimental Results

5.1. Fabracation of the MTJ Sensors

5.1.1. Fabrication

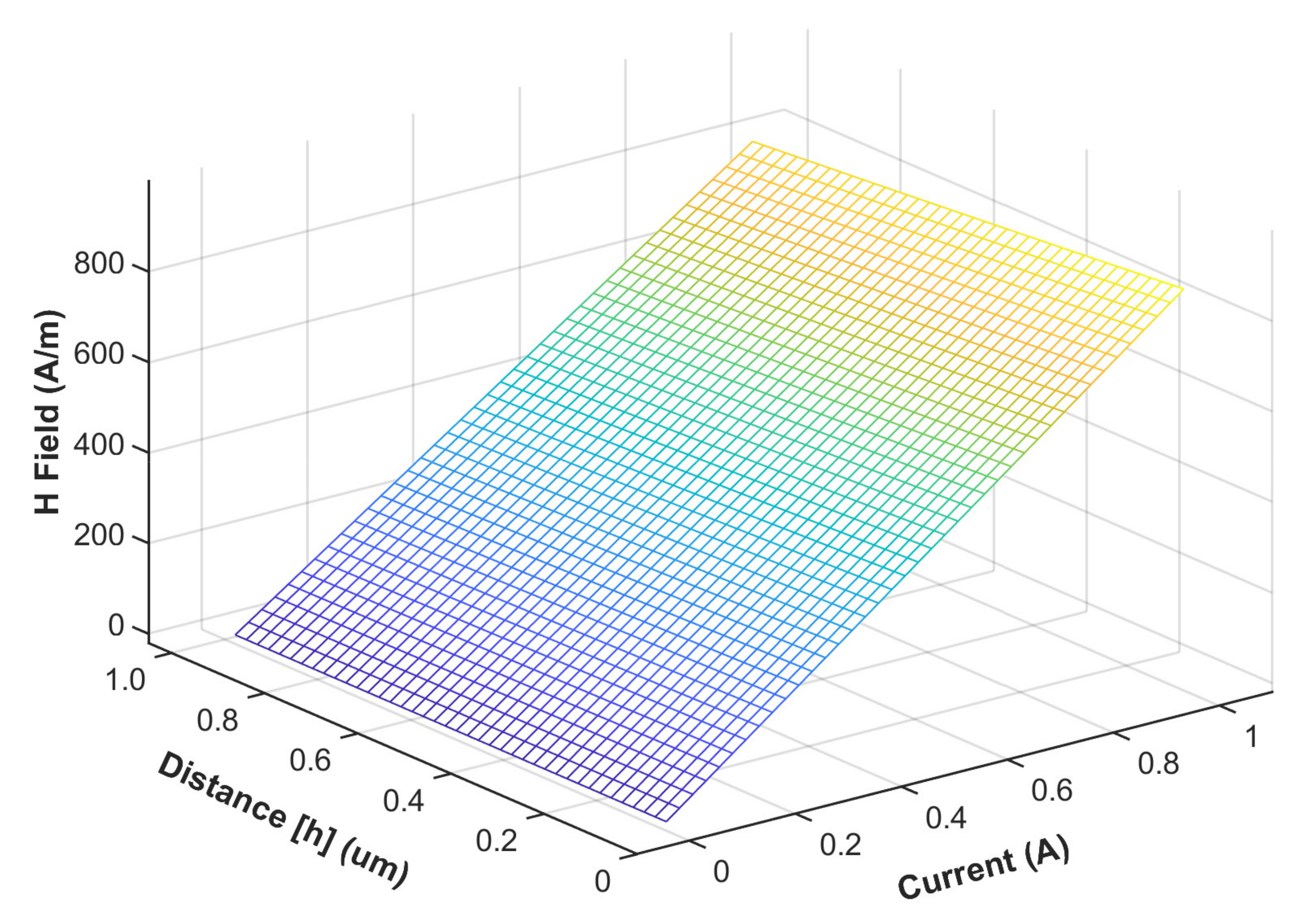

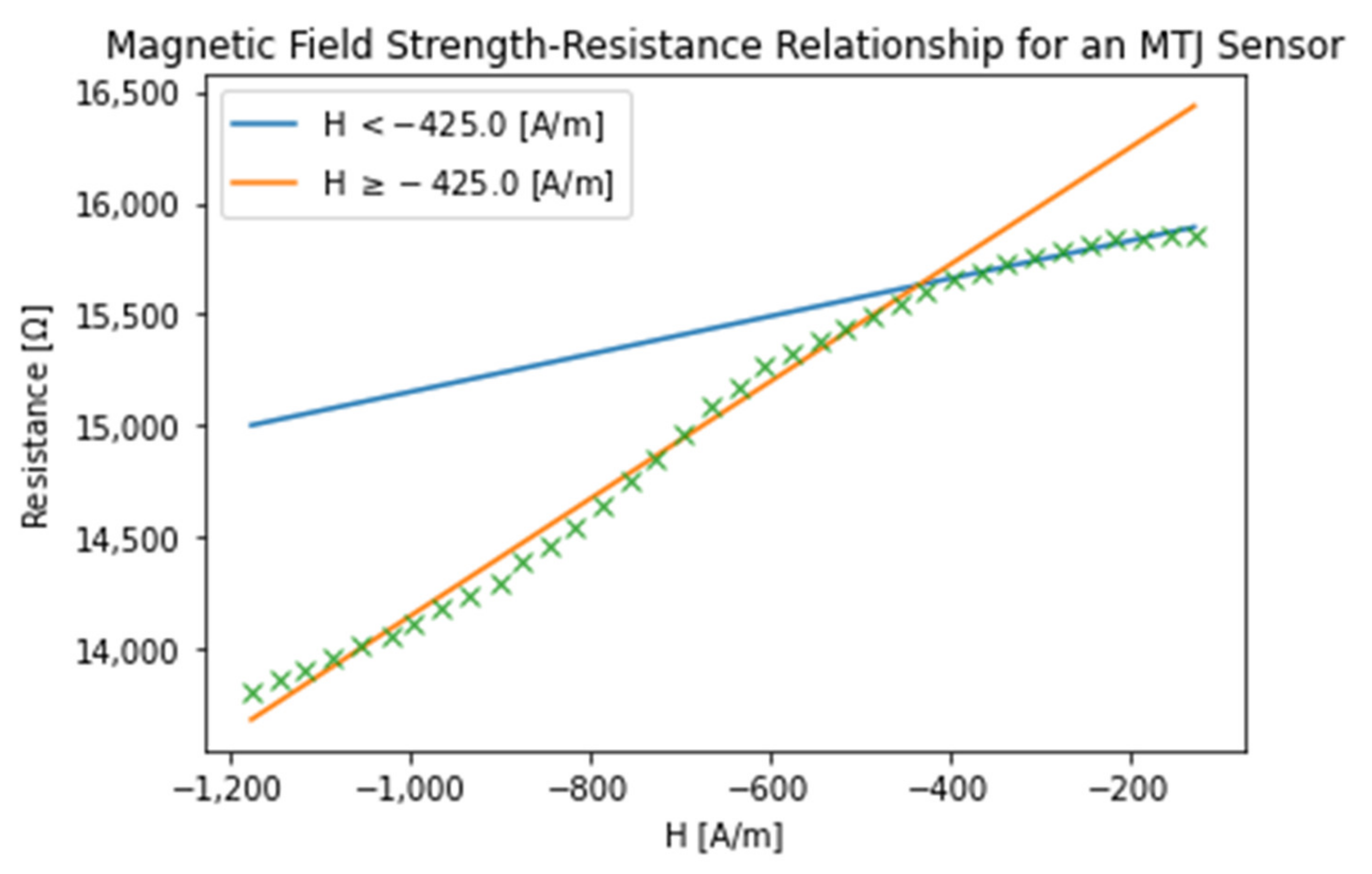

5.1.2. MTJ Measurement Results

5.1.3. Modeling for Cadence Simulation

5.2. Attacker Models and Evalution Results

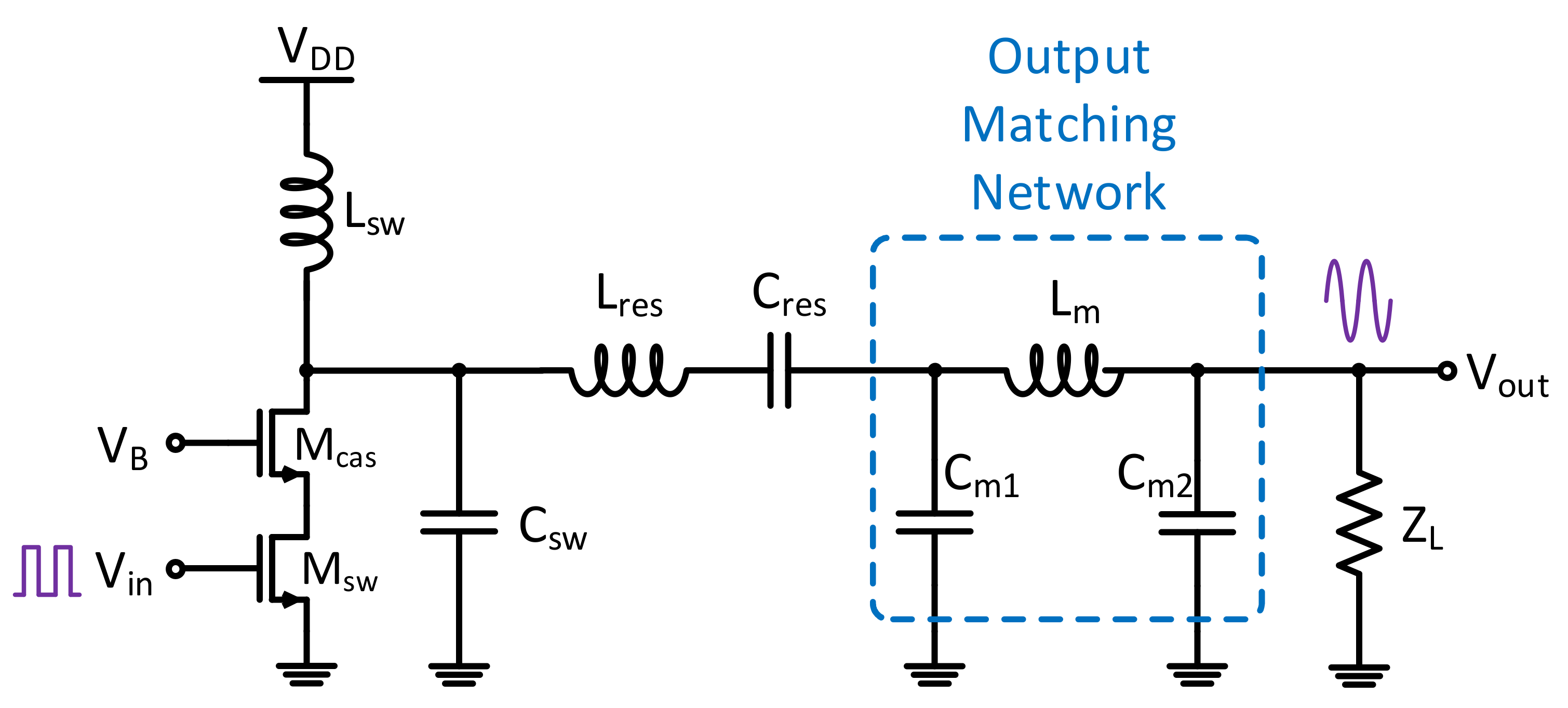

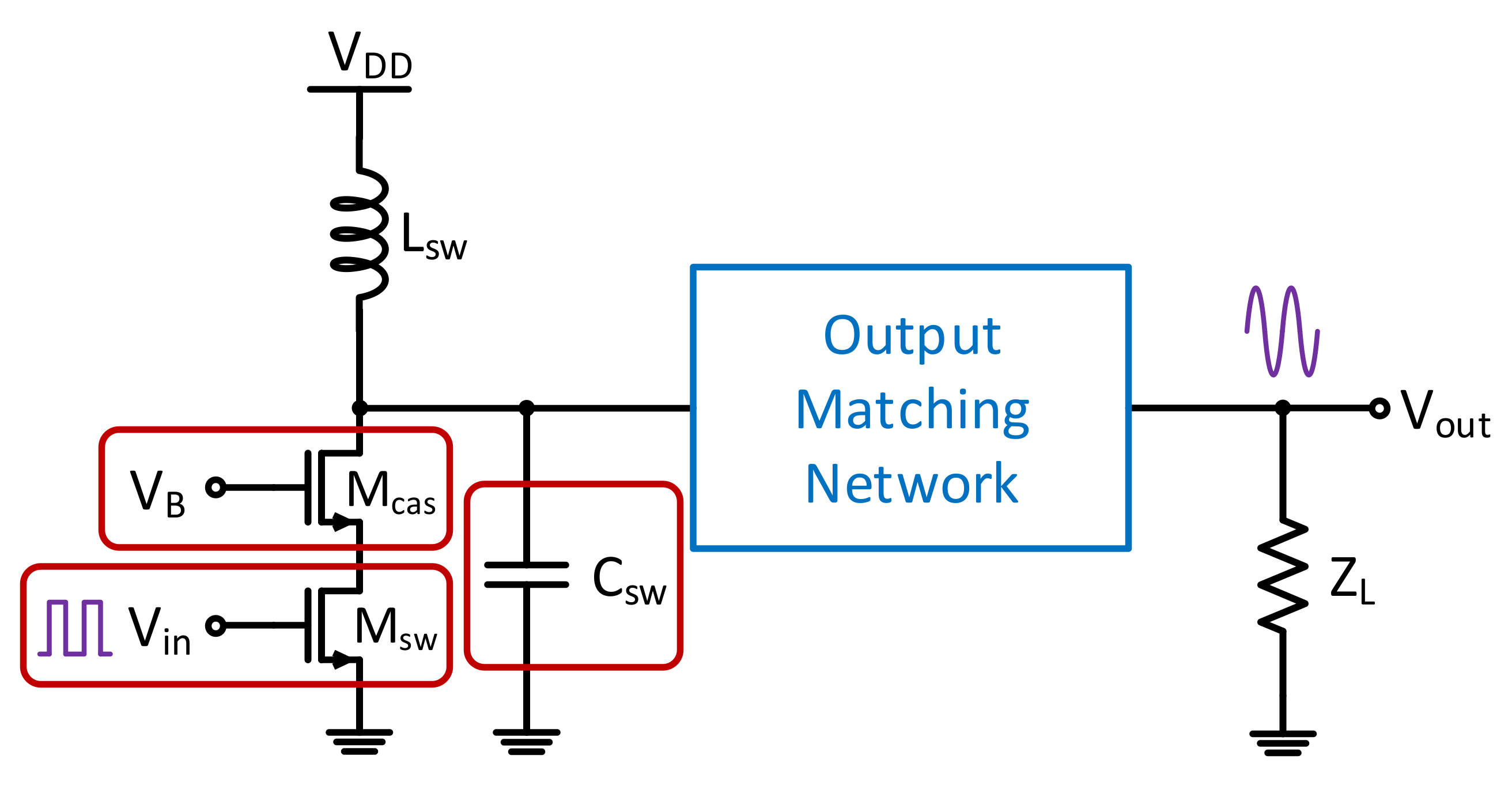

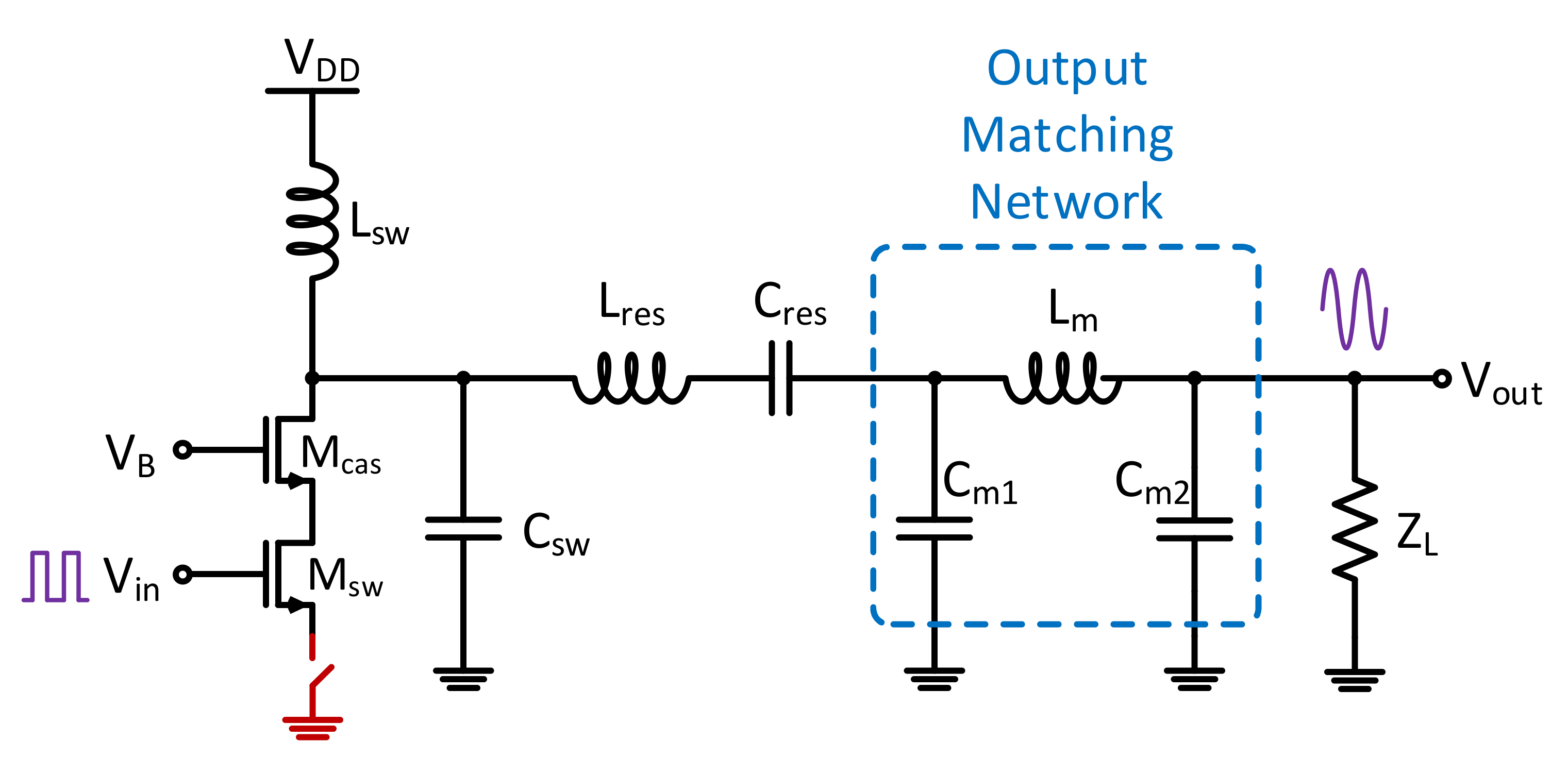

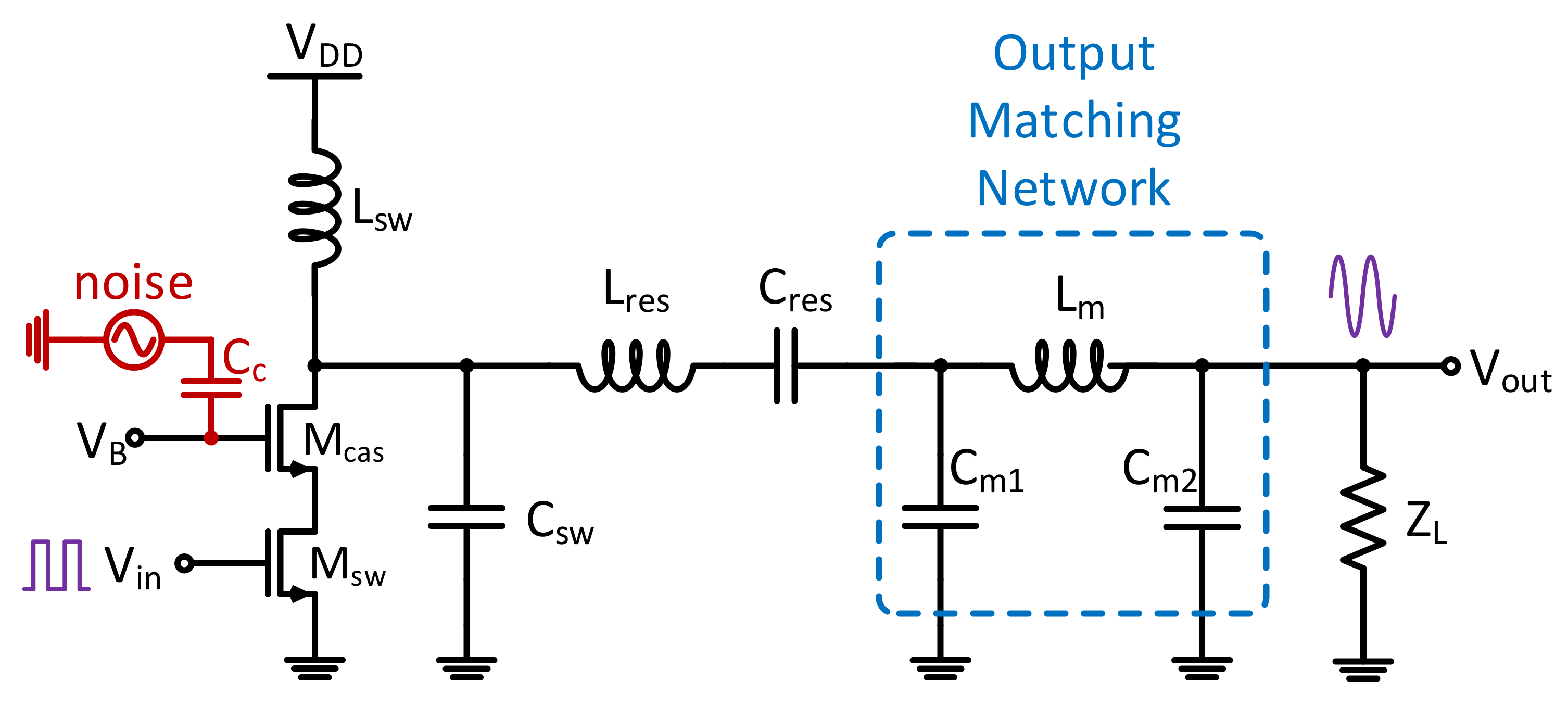

5.2.1. Power Amplifier Designs

5.2.2. Attacker Models on PA Designs

5.2.3. Evaluation Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Erfani, R.; Marefat, F.; Sodagar, A.M.; Mohseni, P. Modeling and experimental validation of a capacitive link for wireless power transfer to biomedical implants. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 923–927. [Google Scholar] [CrossRef]

- Erfani, R.; Marefat, F.; Sodagar, A.M.; Mohseni, P. Modeling and characterization of capacitive elements with tissue as dielectric material for wireless powering of neural implants. IEEE Trans. Neural Syst. Rehabil. Eng. 2018, 26, 1093–1099. [Google Scholar] [CrossRef] [PubMed]

- Erfani, R.; Marefat, F.; Sodagar, A.M.; Mohseni, P. Transcutaneous capacitive wireless power transfer (C-WPT) for biomedical implants. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Popovic, Z.; Falkenstein, E.A.; Costinett, D.; Zane, R. Low-power far-field wireless powering for wireless sensors. Proc. IEEE 2013, 101, 1397–1409. [Google Scholar] [CrossRef]

- Huang, K.; Lau, V.K.N. Enabling wireless power transfer in cellular networks: Architecture, modeling and deployment. IEEE Trans. Wirel. Commun. 2014, 13, 902–912. [Google Scholar] [CrossRef] [Green Version]

- Huang, K.; Zhou, X. Cutting the last wires for mobile communications by microwave power transfer. IEEE Commun. Mag. 2015, 53, 86–93. [Google Scholar] [CrossRef] [Green Version]

- Xie, L.; Shi, Y.; Hou, Y.T.; Lou, A. Wireless power transfer and applications to sensor networks. IEEE Wirel. Commun. 2013, 20, 140–145. [Google Scholar]

- Massa, A.; Oliveri, G.; Viani, F.; Rocca, P. Array designs for long-distance wireless power transmission: State-of-the-art and innovative solutions. Proc. IEEE 2013, 101, 1464–1481. [Google Scholar] [CrossRef] [Green Version]

- Futuristic Roads May Make Recharging Electric Cars A Thing of the Past. Available online: https://www.nbcnews.com/mach/mach/futuristic-roads-may-make-recharging-electric-cars-thing-past-ncna766456 (accessed on 31 October 2021).

- Defense Science Board, Department of Defense. Report of the Defense Science Board Task Force on High Performance Microchip Supply; Defense Science Board, Department of Defense: Washington, DC, USA, 2005.

- Krieg, C.; Dabrowski, A.; Hobel, H.; Krombholz, K.; Weippl, E. Hardware Malware; Morgan & Claypool Publishers: San Rafael, CA, USA, 2013. [Google Scholar]

- Vosatka, J. Introduction to hardware trojans. In The Hardware Trojan War: Attacks, Myths, and Defenses; Bhunia, S., Tehranipoor, M.M., Eds.; Springer International Publishing: Cham, Switzerland, 2018; pp. 15–51. [Google Scholar]

- Chakraborty, R.S.; Narasimhan, S.; Bhunia, S. Hardware Trojan: Threats and emerging solutions. In Proceedings of the 2009 IEEE International High Level Design Validation and Test Workshop, San Francisco, CA, USA, 4–6 November 2009. [Google Scholar]

- Lin, L.; Burleson, W.; Paar, C. MOLES: Malicious off-chip leakage enabled by side-channels. In Proceedings of the 2009 IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 2–5 November 2009. [Google Scholar]

- Narasimhan, S.; Wang, X.; Du, D.; Chakraborty, R.S.; Bhunia, S. TeSR: A robust temporal self-referencing approach for hardware trojan detection. In Proceedings of the 2011 IEEE International Symposium on Hardware-Oriented Security and Trust, San Diego, CA, USA, 5–6 June 2011. [Google Scholar]

- Tehranipoor, M.; Koushanfar, F. A survey of hardware trojan taxonomy and detection. IEEE Des. Test Comput. 2010, 27, 10–25. [Google Scholar] [CrossRef]

- Becker, G.T.; Regazzoni, F.; Paar, C.; Burleson, W.P. Stealthy dopant-level hardware trojans: Extended version. J. Cryptogr. Eng. 2014, 4, 19–31. [Google Scholar] [CrossRef]

- Yang, K.; Hicks, M.; Dong, Q.; Austin, T.; Sylvester, D. A2: Analog malicious hardware. In Proceedings of the 2016 IEEE Symposium on Security and Privacy (SP), San Jose, CA, USA, 23–25 May 2016. [Google Scholar]

- Subramani, K.S.; Helal, N.; Antonopoulos, A.; Nosratinia, A.; Makris, Y. Amplitude-modulating analog/rf hardware trojans in wireless networks: Risks and remedies. IEEE Trans. Inf. Forensics Secur. 2020, 15, 3497–3510. [Google Scholar] [CrossRef]

- Subramani, K.S.; Antonopoulos, S.; Abotabl, A.A.; Nosratinia, A.; Makris, Y. ACE: Adaptive channel estimation for detecting analog/RF trojans in WLAN transceivers. In Proceedings of the 2017 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Irvine, CA, USA, 12–16 November 2017. [Google Scholar]

- Chang, D.; Bakkaloglu, B.; Ozev, S. Enabling unauthorized RF transmission below noise floor with no detectable impact on primary communication performance. In Proceedings of the 2015 IEEE 33rd VLSI Test Symposium (VTS), Napa, CA, USA, 27–29 April 2015. [Google Scholar]

- Liu, Y.; Jin, Y.; Nosratinia, A.; Makris, Y. Silicon demonstration of hardware trojan design and detection in wireless cryptographic ICs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 1506–1519. [Google Scholar] [CrossRef]

- Jin, Y.; Maliuk, D.; Makris, Y. Hardware trojan detection in analog/rf integrated circuits. In Secure System Design and Trustable Computing; Chang, C.-H., Potkonjak, M., Eds.; Springer International Publishing: Cham, Switzerland, 2016; pp. 241–268. [Google Scholar]

- Wang, Q.; Chen, D.; Geiger, R.L. Transparent side channel trigger mechanism on analog circuits with PAAST hardware trojans. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018. [Google Scholar]

- Wang, W.; Geiger, R.L.; Chen, D. Hardware trojans embedded in the dynamic operation of analog and mixed-signal circuits. In Proceedings of the 2015 IEEE National Aerospace and Electronics Conference (NAECON), Dayton, OH, USA, 16–19 June 2015. [Google Scholar]

- Wang, Y.-T.; Wang, W.; Chen, D.; Geiger, R.L. Hardware trojan state detection for analog circuits and systems. In Proceedings of the 2014 IEEE National Aerospace and Electronics Conference (NAECON), Dayton, OH, USA, 24–27 June 2014. [Google Scholar]

- Gungor, B.; Yazici, M.; Salman, E.; Gurbuz, Y. Establishing a covert communication channel in rf and mm-wave circuits. In Proceedings of the 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Springfield, MA, USA, 9–12 August 2020. [Google Scholar]

- Zhou, B.; Aksoylar, A.; Vigil, K.; Adato, R.; Tan, J.; Goldberg, B.; Ünlü, M.S.; Joshi, A. Hardware trojan detection using backside optical imaging. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2021, 40, 24–37. [Google Scholar] [CrossRef]

- Kocher, P.; Jaffe, J.; Jun, B. Differential power analysis. Advances in Cryptology—Crypto’99. In Proceedings of the 19th Annual International Cryptology Conference, Santa Barbara, CA, USA, 15–19 August 1999. [Google Scholar]

- Brier, E.; Clavier, C.; Olivier, F. Correlation power analysis with a leakage model. In Proceedings of the 6th International Workshop on Cryptographic Hardware and Embedded Systems (CHES), Boston, MA, USA, 11–13 August 2004. [Google Scholar]

- Kocher, P.C. Timing attacks on implementations of Diffie-Hellman, RSA, DSS, and other systems. In Proceedings of the 16th Annual International Cryptology Conference, Santa Barbara, CA, USA, 18–22 August 1996. [Google Scholar]

- Kocher, P.; Jaffe, J.; Jun, B.; Rohatgi, P. Introduction to differential power analysis. J. Cryptogr. Eng. 2011, 1, 5–27. [Google Scholar] [CrossRef] [Green Version]

- NSA Tempest Series. Available online: http://cryptome.org/#NSA--TS (accessed on 31 October 2021).

- Gandolfi, K.; Mourtel, C.; Olivier, F. Electromagnetic attacks: Concrete results. In Cryptographic Hardware and Embedded Systems—CHES 2001; Springer: Berlin/Heidelberg, Germany, 2001; Volume 2162, pp. 251–261. [Google Scholar]

- Quisquater, J.-J.; Samyde, D. ElectroMagnetic Analysis (EMA): Measures and counter-measures for smart cards. Smart Card Program. Secur. 2001, 2140, 200–210. [Google Scholar]

- Balasch, J.; Gierlichs, B.; Verbauwhede, I. Electromagnetic circuit fingerprints for Hardware Trojan detection. In Proceedings of the IEEE International Symposium on Electromagnetic Compatibility (EMC), Dresden, Germany, 16–22 August 2015. [Google Scholar]

- Du, D.; Narasimhan, S.; Chakraborty, R.S.; Bhunia, S. Self-referencing: A scalable side-channel approach for hardware trojan detection. In Proceedings of the 12th International Workshop on Cryptographic Hardware and Embedded Systems, Santa Barbara, CA, USA, 17–20 August 2010. [Google Scholar]

- Wang, L.; Xie, H.; Luo, H. Malicious circuitry detection using transient power analysis for IC security. In Proceedings of the 2013 International Conference on Quality, Reliability, Risk, Maintenance and Safety Engineering (QR2MSE), Chengdu, China, 15–18 July 2013. [Google Scholar]

- Agrawal, D.; Baktir, S.; Karakoyunlu, D.; Rohatgi, P.; Sunar, B. Trojan detection using IC fingerprinting. In Proceedings of the 2007 IEEE Symposium on Security and Privacy (SP’07), Berkeley, CA, USA, 20–23 May 2007. [Google Scholar]

- Cimino, M.; Lapuyade, H.; De Matos, M.; Taris, T.; Deval, Y.; Begueret, J.B. A Robust 130nm-CMOS built-in current sensor dedicated to rf applications. In Proceedings of the Eleventh IEEE European Test Symposium (ETS’06), Southampton, UK, 21 May 2006. [Google Scholar]

- Le Phan, K.; Boeve, H.; Vanhelmont, F.; Ikkink, T.; Talen, W. Geometry optimization of TMR current sensors for on-chip IC testing. IEEE Trans. Magn. 2005, 41, 3685–3687. [Google Scholar] [CrossRef]

- Dąbek, M.; Wiśniowski, P.; Kalabińskia, P.; Wrona, J.; Moskaltsova, A.; Cardoso, S.; Freitas, P.P. Tunneling magnetoresistance sensors for high fidelity current waveforms monitoring. Sens. Actuators A Phys. 2016, 251, 142–147. [Google Scholar] [CrossRef]

- Le Phan, K.; Boeve, H.; Vanhelmont, F.; Ikkink, T.; de Jong, F.; de Wilde, H. Tunnel magnetoresistive current sensors for IC testing. Sens. Actuators A Phys. 2006, 129, 69–74. [Google Scholar] [CrossRef]

- Lee, C.F.; Mok, P.K.T. On-chip current sensing technique for cmos monolithic switch-mode power converter. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Scottsdale, AZ, USA, 26–29 May 2002. [Google Scholar]

- Lee, C.F.; Mok, P.K.T. A Monolithic current-mode CMOS DC-DC converter with on-chip current-sensing technique. IEEE J. Solid-State Circuits 2004, 39, 3–14. [Google Scholar] [CrossRef]

- Somerville, T.A. High Side Current Sense Amplifier. U.S. Patent 5,627,494, 6 May 1997. [Google Scholar]

- Marschalkowski, E.; Malcolm, J. Current Sensing Circuit for DC/DC Buck Converters. U.S. Patent 6,992,473, 31 January 2006. [Google Scholar]

- Bromberg, D.M.; Sumbul, H.E.; Zhu, J.-G.; Pileggi, L. All-magnetic magnetoresistive random access memory based on four terminal mCell device. J. Appl. Phys. 2015, 117, 17B510. [Google Scholar] [CrossRef]

- Bromberg, D.M.; Moneck, M.T.; Sokalski, V.M.; Zhu, J.; Pileggi, L.; Zhu, J.-G. Experimental demonstration of four-terminal magnetic logic device with separate read- and write-paths. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014. [Google Scholar]

- Bromberg, D.M.; Morris, D.H.; Pileggi, L.; Zhu, J.-G. Novel STT-MTJ device enabling all-metallic logic circuits. IEEE Trans. Magn. 2012, 48, 3215–3218. [Google Scholar] [CrossRef]

- Sokalski, V.; Bromberg, D.M.; Moneck, M.T.; Yang, E.; Zhu, J.-G. Increased perpendicular TMR in FeCoB/MgO/FeCoB magnetic tunnel junctions by seedlayer modifications. IEEE Trans. Magn. 2013, 49, 4383–4385. [Google Scholar] [CrossRef]

- Morris, D.H.; Bromberg, D.M.; Zhu, J.-G.; Pileggi, L. mLogic: Ultra-low voltage non-volatile logic circuits using STT-MTJ devices. In Proceedings of the 49th Annual ACM Design Automation Conference, San Francisco, CA, USA, 3–7 June 2012. [Google Scholar]

- Reig, C.; Cardoso, S.; Mukhopadhyay, S.C. Giant Magnetoresistance (GMR) Sensors from Basis to State-of-the-Art Applications; Springer: Berlin/Heidelberg, Germany, 2013. [Google Scholar]

- Xu, J.; Shen, Y.; Chen, E.; Chen, V. Bayesian neural networks for identification and classification of radio frequency transmitters using power amplifiers’ nonlinearity signatures. IEEE Open J. Circuits Syst. 2021, 2, 457–471. [Google Scholar] [CrossRef]

- Takenaga, T.; Tsuzaki, Y.; Furukawa, T.; Yoshida, C.; Yamazaki, Y.; Hatada, A.; Nakabayashi, M.; Iba, Y.; Takahashi, A.; Noshiro, H.; et al. Scalable sensing of interconnect current with magnetic tunnel junctions embedded in Cu interconnects. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 11–15 December 2013. [Google Scholar]

| Trojan Type | Accuracy |

|---|---|

| Source switch trojan | 96% |

| Parasitic capacitance trojan | 85% |

| Noise trojan | 100% |

| Combined trojans of all types | 95% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, E.; Kan, J.; Yang, B.-Y.; Zhu, J.; Chen, V. Intelligent Electromagnetic Sensors for Non-Invasive Trojan Detection. Sensors 2021, 21, 8288. https://doi.org/10.3390/s21248288

Chen E, Kan J, Yang B-Y, Zhu J, Chen V. Intelligent Electromagnetic Sensors for Non-Invasive Trojan Detection. Sensors. 2021; 21(24):8288. https://doi.org/10.3390/s21248288

Chicago/Turabian StyleChen, Ethan, John Kan, Bo-Yuan Yang, Jimmy Zhu, and Vanessa Chen. 2021. "Intelligent Electromagnetic Sensors for Non-Invasive Trojan Detection" Sensors 21, no. 24: 8288. https://doi.org/10.3390/s21248288

APA StyleChen, E., Kan, J., Yang, B.-Y., Zhu, J., & Chen, V. (2021). Intelligent Electromagnetic Sensors for Non-Invasive Trojan Detection. Sensors, 21(24), 8288. https://doi.org/10.3390/s21248288