Analytical Optimal Load Calculation of RF Energy Rectifiers Based on a Simplified Rectifying Model †

Abstract

:1. Introduction

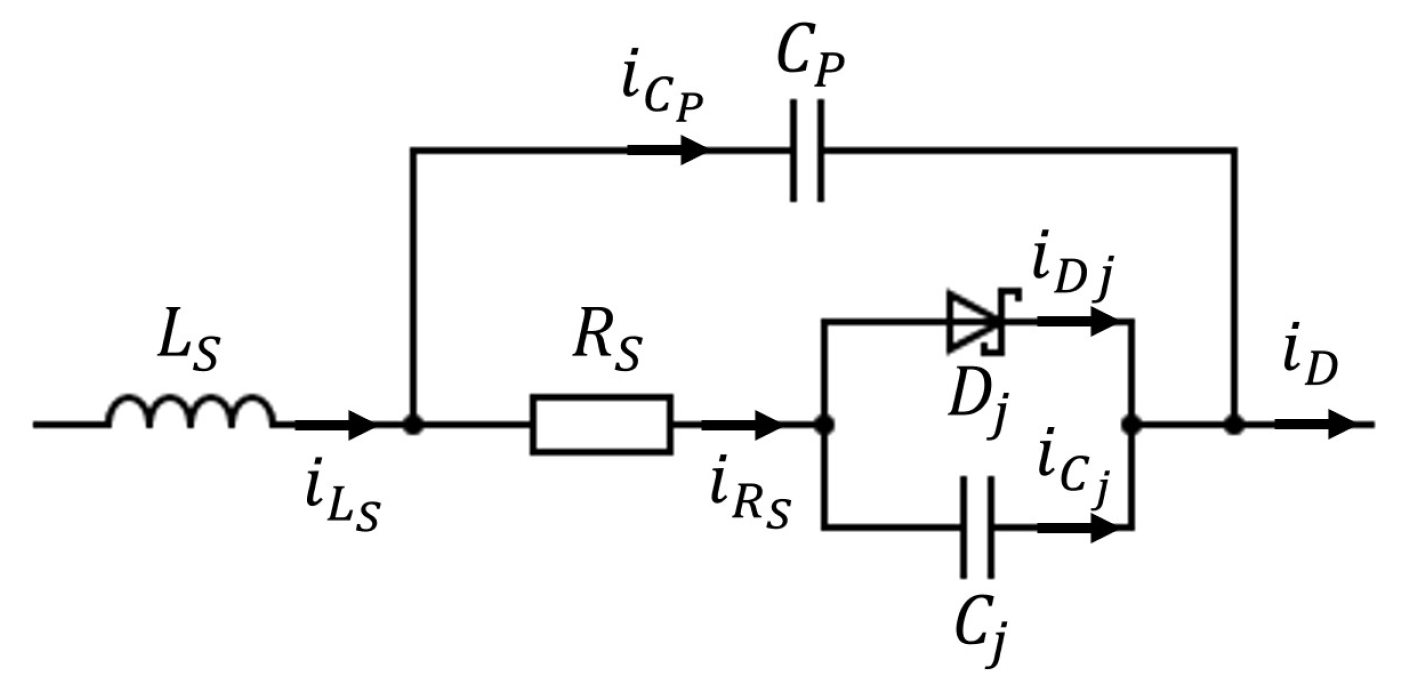

2. Analytical Rectification Model

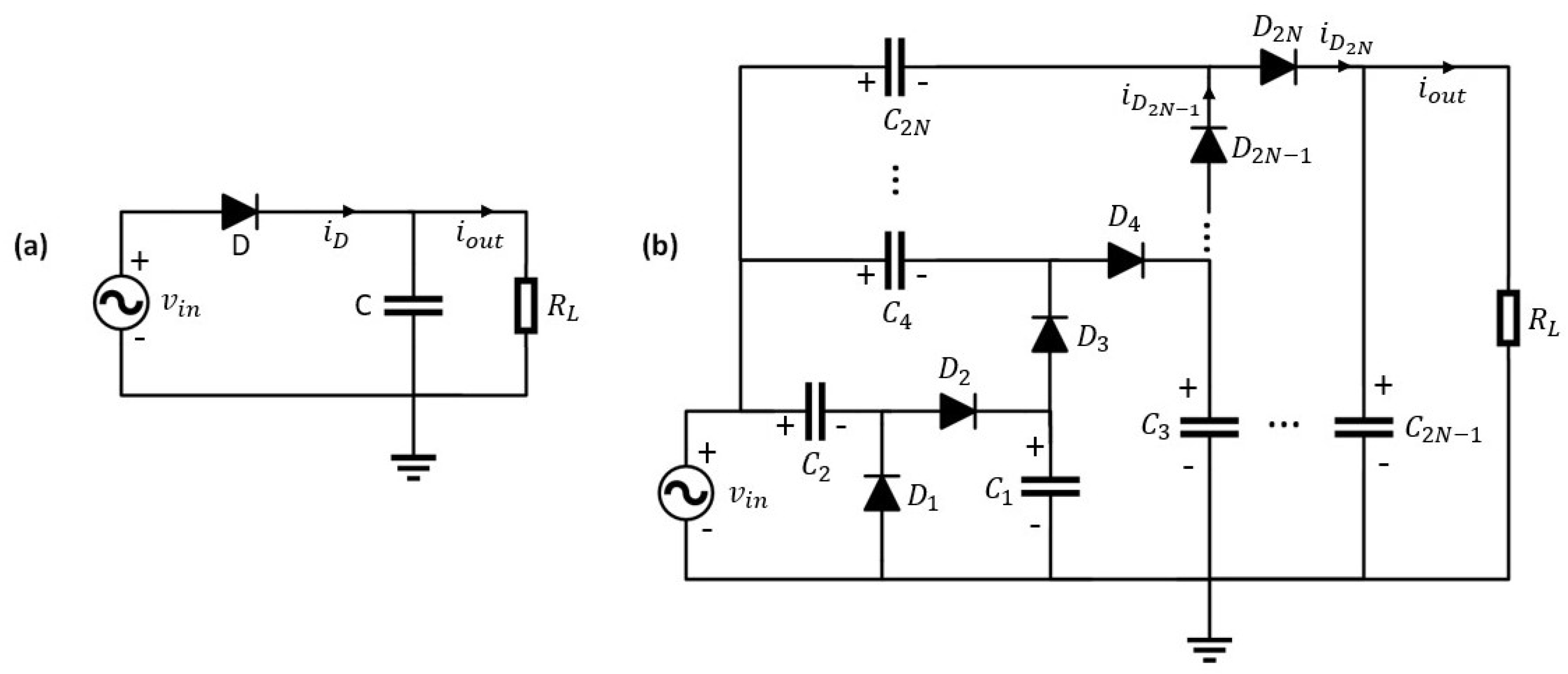

2.1. Half-Wave Rectification Model

2.2. N-Stage Voltage-Multiplier Rectification Model

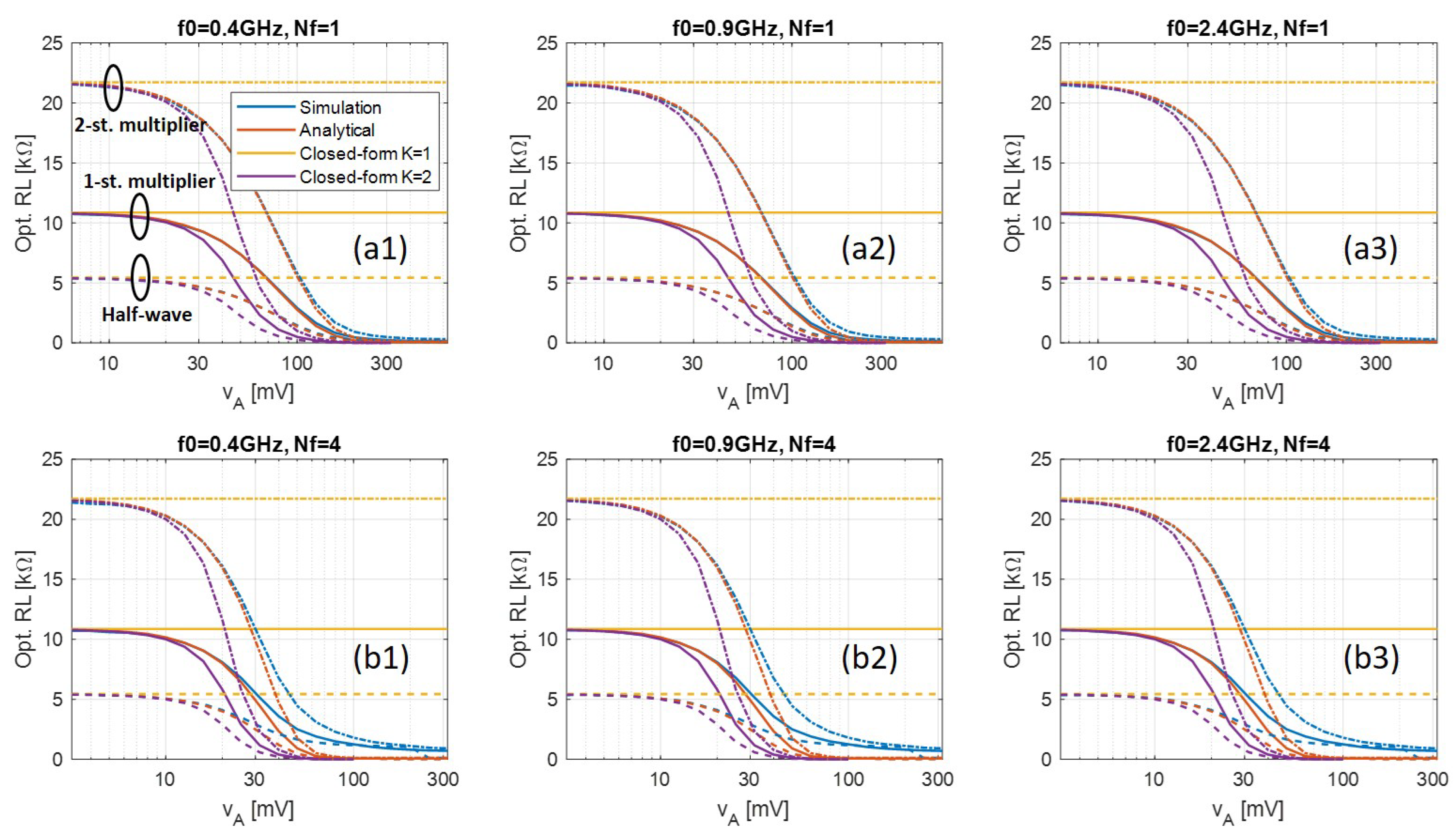

3. Calculation of Optimal Load Resistance

3.1. Problem Formulation

3.2. Closed-Form Approximations for Low Input Power

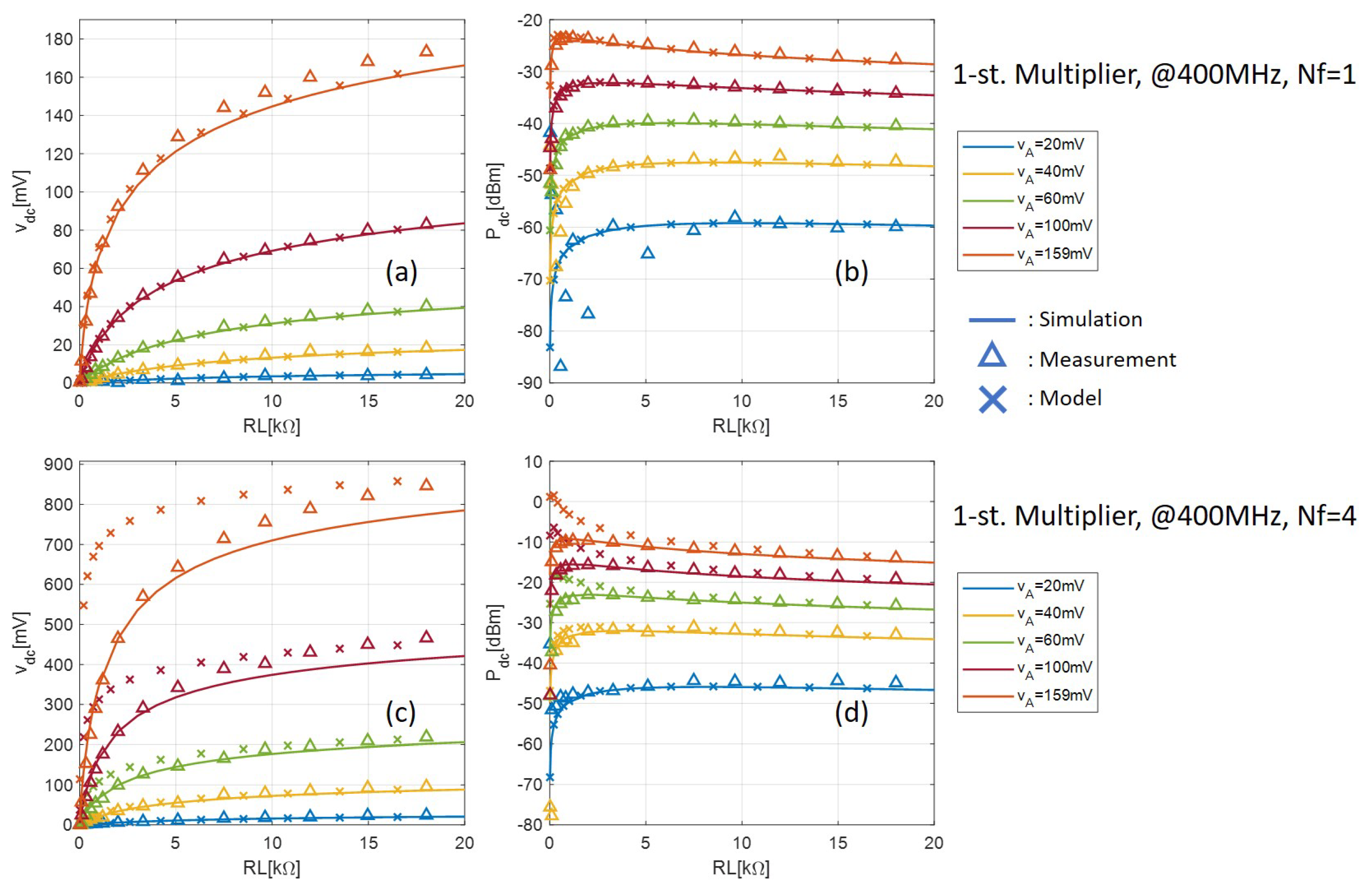

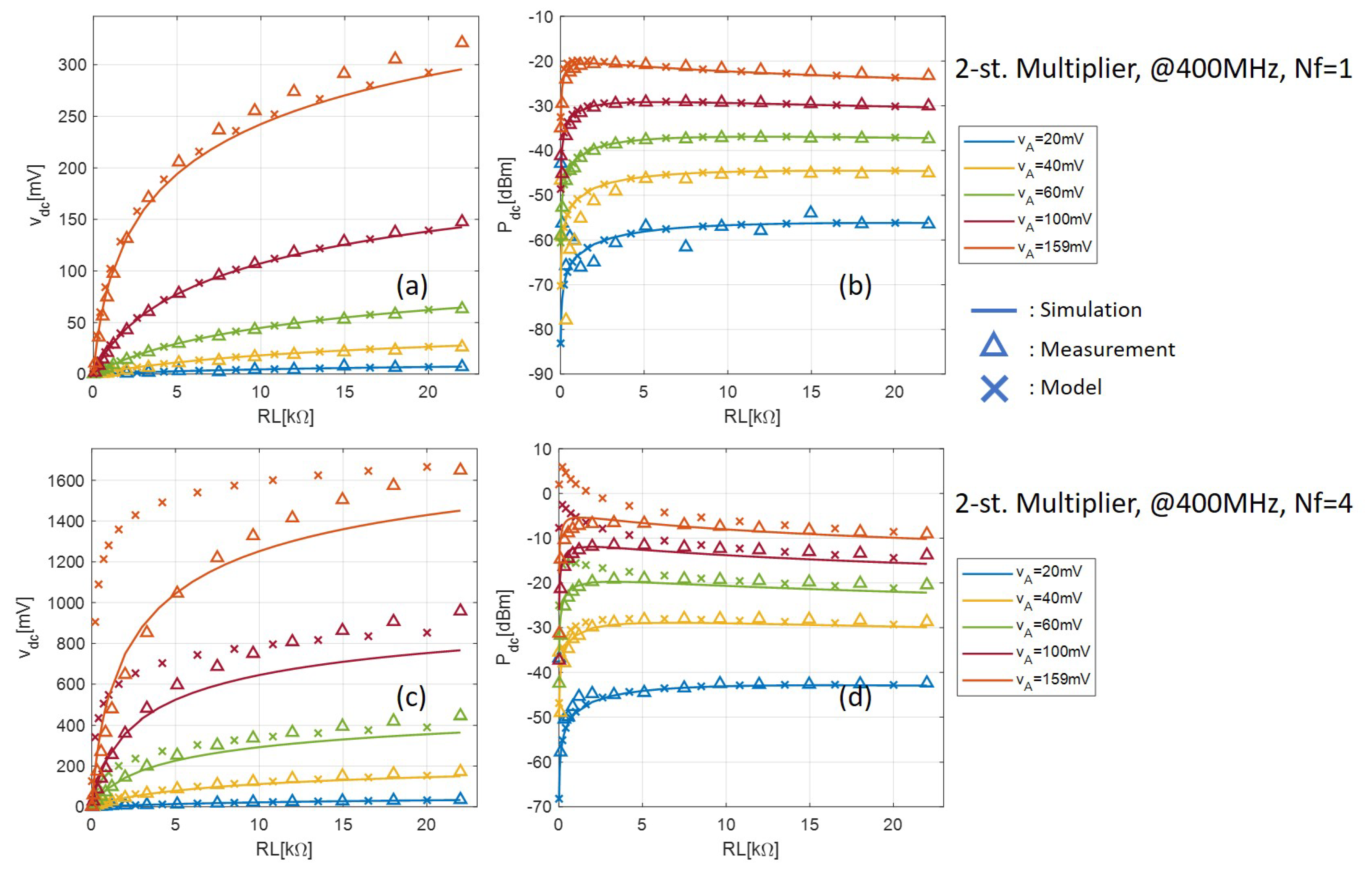

4. Validation and Discussions

4.1. Simulation Setup and Results

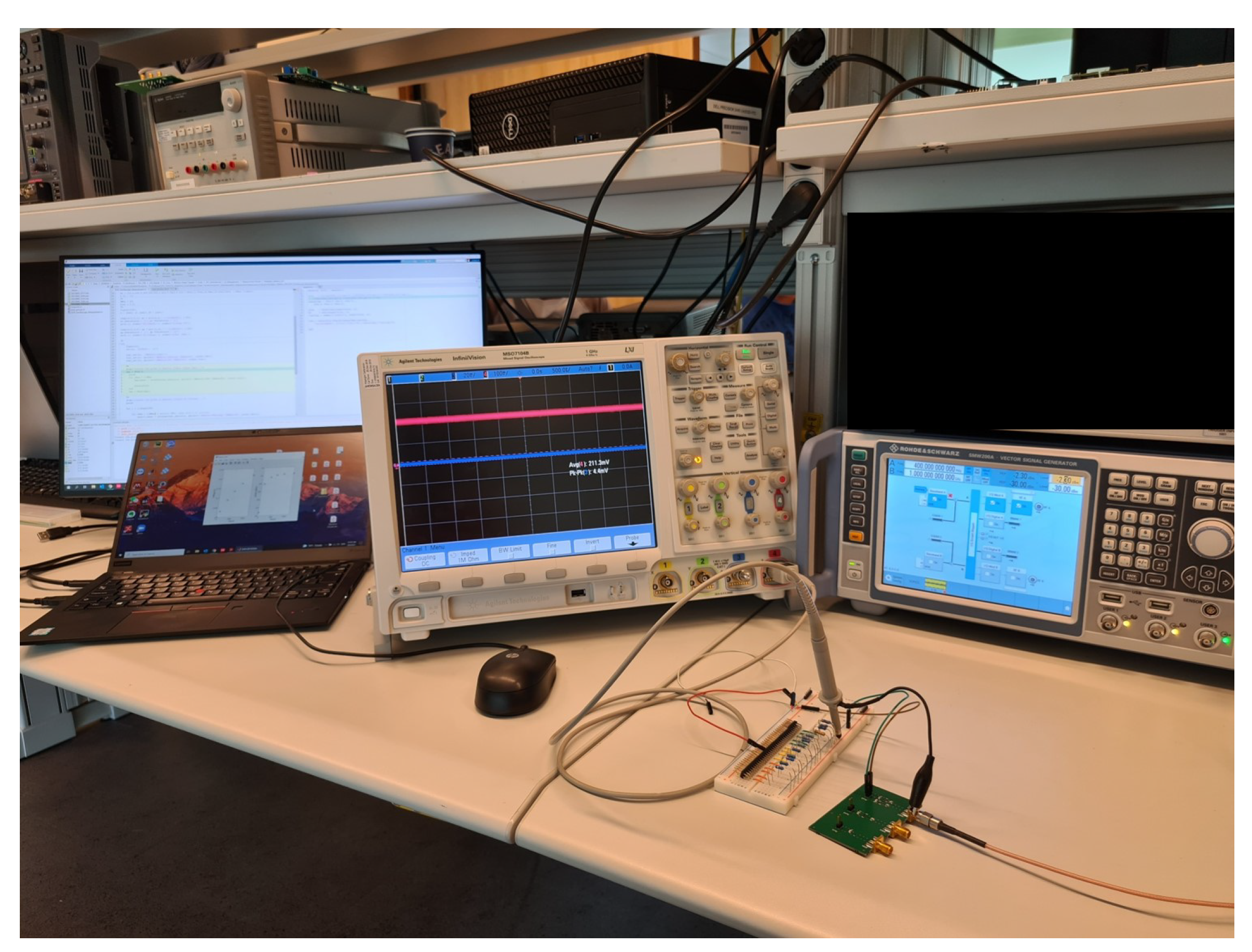

4.2. Measurement Setup

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Zhang, Z.; Pang, H.; Georgiadis, A.; Cecati, C. Wireless power transfer—An overview. IEEE Trans. Ind. Electron. 2018, 66, 1044–1058. [Google Scholar] [CrossRef]

- Li, S.; Mi, C.C. Wireless power transfer for electric vehicle applications. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 3, 4–17. [Google Scholar]

- Clerckx, B.; Costanzo, A.; Georgiadis, A.; Carvalho, N.B. Toward 1G mobile power networks: RF, signal, and system designs to make smart objects autonomous. IEEE Microw. Mag. 2018, 19, 69–82. [Google Scholar] [CrossRef]

- Ouda, M.H.; Mitcheson, P.; Clerckx, B. Optimal operation of multitone waveforms in low RF-power receivers. In Proceedings of the 2018 IEEE Wireless Power Transfer Conference (WPTC), Montreal, QC, Canada, 3–7 June 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–4. [Google Scholar]

- Boaventura, A.; Collado, A.; Carvalho, N.B.; Georgiadis, A. Optimum behavior: Wireless power transmission system design through behavioral models and efficient synthesis techniques. IEEE Microw. Mag. 2013, 14, 26–35. [Google Scholar] [CrossRef]

- Pflug, H.W.; Keyrouz, S.; Visser, H.J. Far-field energy harvesting rectifier analysis. In Proceedings of the 2016 IEEE Wireless Power Transfer Conference (WPTC), Aveiro, Portugal, 5–6 May 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 1–4. [Google Scholar]

- Maas, S.A. Nonlinear Microwave and RF Circuits; Artech House: Boston, MA, USA, 2003. [Google Scholar]

- McSpadden, J.O.; Fan, L.; Chang, K. Design and experiments of a high-conversion-efficiency 5.8-GHz rectenna. IEEE Trans. Microw. Theory Tech. 1998, 46, 2053–2060. [Google Scholar] [CrossRef]

- Gao, S.P.; Zhang, H.; Ngo, T.; Guo, Y. Lookup-table-based automated rectifier synthesis. IEEE Trans. Microw. Theory Tech. 2020, 68, 5200–5210. [Google Scholar] [CrossRef]

- Yoo, T.W.; Chang, K. Theoretical and experimental development of 10 and 35 GHz rectennas. IEEE Trans. Microw. Theory Tech. 1992, 40, 1259–1266. [Google Scholar] [CrossRef]

- Guo, J.; Zhang, H.; Zhu, X. Theoretical analysis of RF-DC conversion efficiency for class-F rectifiers. IEEE Trans. Microw. Theory Tech. 2014, 62, 977–985. [Google Scholar] [CrossRef]

- Gu, X.; Guo, L.; Hemour, S.; Wu, K. Optimum temperatures for enhanced power conversion efficiency (PCE) of zero-bias diode-based rectifiers. IEEE Trans. Microw. Theory Tech. 2020, 68, 4040–4053. [Google Scholar] [CrossRef]

- Gu, X.; Hemour, S.; Wu, K. Wireless Powered Sensors for Battery-Free IoT Through Multi-Stage Rectifier. In Proceedings of the 2020 XXXIIIrd General Assembly and Scientific Symposium of the International Union of Radio Science, Rome, Italy, 29 August–5 September 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1–4. [Google Scholar]

- Bolos, F.; Blanco, J.; Collado, A.; Georgiadis, A. RF energy harvesting from multi-tone and digitally modulated signals. IEEE Trans. Microw. Theory Tech. 2016, 64, 1918–1927. [Google Scholar] [CrossRef]

- Hemour, S.; Zhao, Y.; Lorenz, C.H.P.; Houssameddine, D.; Gui, Y.; Hu, C.M.; Wu, K. Towards low-power high-efficiency RF and microwave energy harvesting. IEEE Trans. Microw. Theory Tech. 2014, 62, 965–976. [Google Scholar] [CrossRef]

- Lorenz, C.H.P.; Hemour, S.; Wu, K. Physical mechanism and theoretical foundation of ambient RF power harvesting using zero-bias diodes. IEEE Trans. Microw. Theory Tech. 2016, 64, 2146–2158. [Google Scholar] [CrossRef]

- Boaventura, A.S.; Carvalho, N.B. Maximizing DC power in energy harvesting circuits using multisine excitation. In Proceedings of the 2011 IEEE MTT-S International Microwave Symposium, Baltimore, MD, USA, 5–10 June 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 1–4. [Google Scholar]

- Clerckx, B.; Bayguzina, E. Waveform design for wireless power transfer. IEEE Trans. Signal Process. 2016, 64, 6313–6328. [Google Scholar] [CrossRef] [Green Version]

- Moghadam, M.R.V.; Zeng, Y.; Zhang, R. Waveform optimization for radio-frequency wireless power transfer. In Proceedings of the 2017 IEEE 18th International Workshop on Signal Processing Advances in Wireless Communications (SPAWC), Sapporo, Japan, 3–6 July 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1–6. [Google Scholar]

- Morsi, R.; Jamali, V.; Ng, D.W.K.; Schober, R. On the capacity of SWIPT systems with a nonlinear energy harvesting circuit. In Proceedings of the 2018 IEEE International Conference on Communications (ICC), Kansas City, MO, USA, 20–24 May 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–7. [Google Scholar]

- Kim, K.W.; Lee, H.S.; Lee, J.W. Waveform design for fair wireless power transfer with multiple energy harvesting devices. IEEE J. Sel. Areas Commun. 2018, 37, 34–47. [Google Scholar] [CrossRef]

- Varasteh, M.; Rassouli, B.; Clerckx, B. Wireless information and power transfer over an AWGN channel: Nonlinearity and asymmetric Gaussian signaling. In Proceedings of the 2017 IEEE Information Theory Workshop (ITW), Kaohsiung, Taiwan, 6–10 November 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 181–185. [Google Scholar]

- Zawawi, Z.B.; Huang, Y.; Clerckx, B. Multiuser wirelessly powered backscatter communications: Nonlinearity, waveform design, and SINR-energy tradeoff. IEEE Trans. Wirel. Commun. 2018, 18, 241–253. [Google Scholar] [CrossRef] [Green Version]

- Yao, L.; Dolmans, G.; Romme, J. On the Analytical Optimal Load Resistance of RF Energy Rectifier. In Proceedings of the 2021 IEEE Wireless Power Transfer Conference (WPTC), San Diego, CA, USA, 1–4 June 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 1–4. [Google Scholar]

- SMS7630-040LF: 0402 Surface Mount Zero Bias Detector Schottky Diode. Available online: https://datasheet.octopart.com/SMS7630-040LF-Skyworks-Solutions-datasheet-8832283.pdf (accessed on 24 September 2021).

- Banwell, T.C. Bipolar transistor circuit analysis using the Lambert W-function. IEEE Trans. Circuits Syst. Fundam. Theory Appl. 2000, 47, 1621–1633. [Google Scholar] [CrossRef]

- De Vita, G.; Iannaccone, G. Design criteria for the RF section of UHF and microwave passive RFID transponders. IEEE Trans. Microw. Theory Tech. 2005, 53, 2978–2990. [Google Scholar] [CrossRef]

- Cunningham, W.J. Introduction to Nonlinear Analysis; McGraw-Hill: New York, NY, USA, 1958. [Google Scholar]

- Le Polozec, X. Input Impedance of Series Schottky Diode Detector at Low and High Power. 2015. Available online: https://www.researchgate.net/publication/277323751_Input_Impedance_of_Series_Schottky_Diode_Detector_at_Low_and_High_Power (accessed on 24 September 2021).

- Simscape: Model and Simulate Multi Domain Physical Systems. Available online: http://www.mathworks.com/products/simscape (accessed on 24 September 2021).

| N | M | |||||||

|---|---|---|---|---|---|---|---|---|

| SMS7630 | 5 A | 20 | 0.14 pF | 0.51 V | 0.05 nH | 0.005 pF | ||

| HSMS285x | 3 A | 25 | 0.18 pF | 0.35 V | 2 nH | 0.08 pF |

| R1 | R2 | R3 | R4 | R5 | R6 | R7R8 | R7 | |

| Value [] | 16.2 | 100.3 | 328 | 558 | 822 | 1.2 k | 1.99 k | 3.29 k |

| R8 | R9 | R11 R14 | R10 | R11 | R12 | R13 | R14 | |

| Value [] | 5.1 k | 7.49 k | 9.63 k | 11.97 k | 14.96 k | 18.01 k | 22 k | 26 k |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yao, L.; Dolmans, G.; Romme, J. Analytical Optimal Load Calculation of RF Energy Rectifiers Based on a Simplified Rectifying Model. Sensors 2021, 21, 8038. https://doi.org/10.3390/s21238038

Yao L, Dolmans G, Romme J. Analytical Optimal Load Calculation of RF Energy Rectifiers Based on a Simplified Rectifying Model. Sensors. 2021; 21(23):8038. https://doi.org/10.3390/s21238038

Chicago/Turabian StyleYao, Lichen, Guido Dolmans, and Jac Romme. 2021. "Analytical Optimal Load Calculation of RF Energy Rectifiers Based on a Simplified Rectifying Model" Sensors 21, no. 23: 8038. https://doi.org/10.3390/s21238038

APA StyleYao, L., Dolmans, G., & Romme, J. (2021). Analytical Optimal Load Calculation of RF Energy Rectifiers Based on a Simplified Rectifying Model. Sensors, 21(23), 8038. https://doi.org/10.3390/s21238038