1. Introduction

Discontinuous conduction mode (DCM) appears in current unidirectional DC-DC elementary switching converters such as buck, boost or buck-boost, whose switch consists of a transistor (usually a MOSFET or an IGBT) and diode, when the inductor current becomes zero in the diode conduction subinterval. The diode turns OFF and a third subinterval appears in which both transistor and diode are OFF [

1,

2]. In these converters a continuous conduction mode (CCM) is easily achieved by using synchronous switching, that is, replacing the diode with a transistor and applying complementary switching signals to the resulting current-bidirectional half-bridge structure [

1,

2].

However, the unidirectional switch is easier to implement and sometimes DCM operation is preferred because it reduces problems related to the diode reverse recovery current [

3]. Further, DCM operation in boost and buck-boost converters has been proposed to eliminate the right half-plane zero that can limit the voltage control loop bandwidth [

3]. In addition, paralleling DCM converters (with or without interleaving) is achieved naturally without a dedicated control strategy [

4].

In single phase AC-DC power factor correction (PFC) applications based on the boost converter, the inductor current becomes discontinuous in the vicinity of the zero-crossings of the line voltage. In fact, some PFC circuits are intentionally designed to always operate in DCM to simplify their control law [

3,

5,

6,

7,

8] or to reduce the switching loss and the power consumption [

9]. The loss free resistor characteristics of the buck-boost converter operating in DCM exhibits a resistive input impedance naturally providing PFC, however because of the discontinuous nature of the buck-boost input current it is sometimes replaced by higher order structures with a series-inductor at its input, such as Single-Ended Primary-Inductor converter (SEPIC) and Ćuk converters [

10,

11].

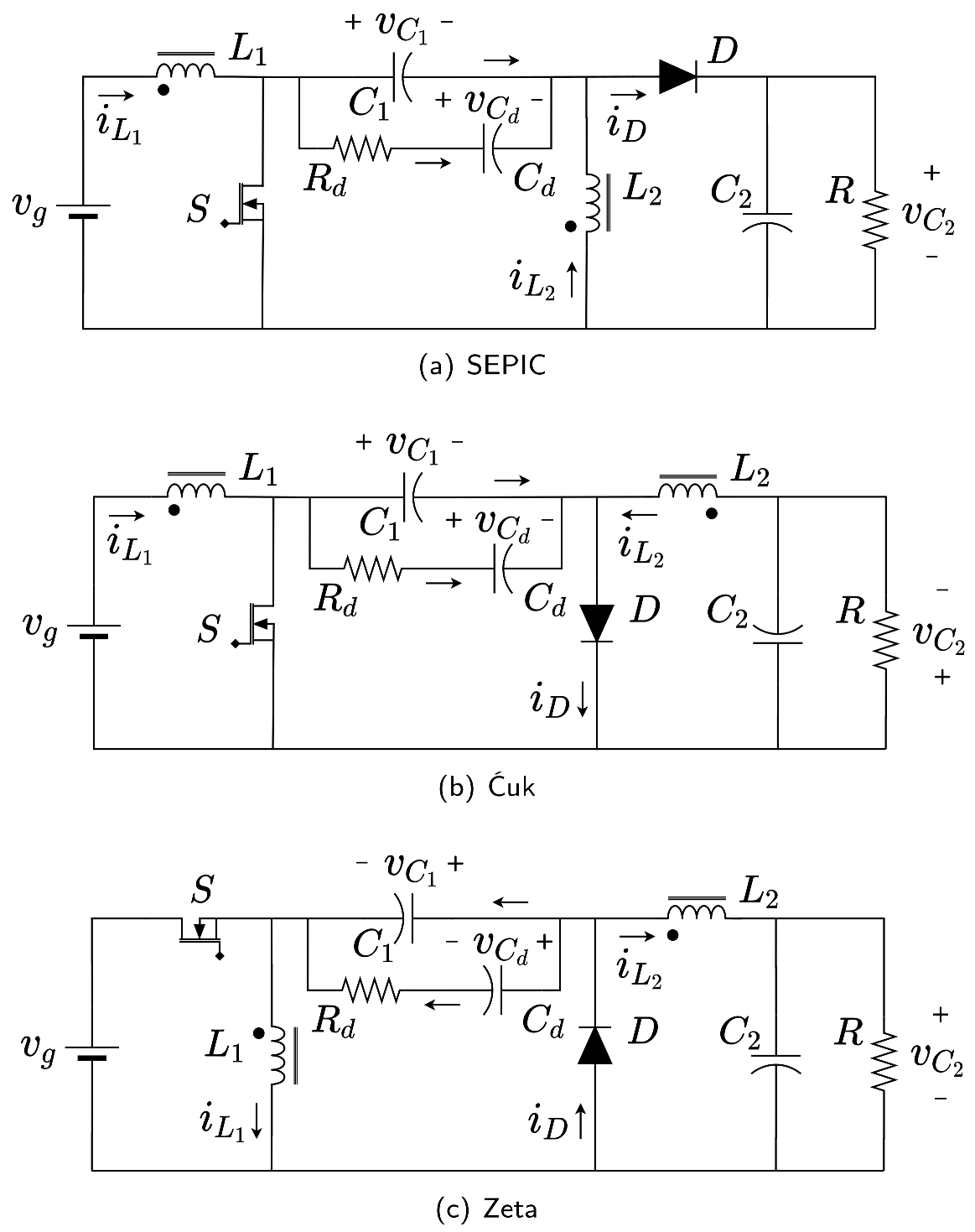

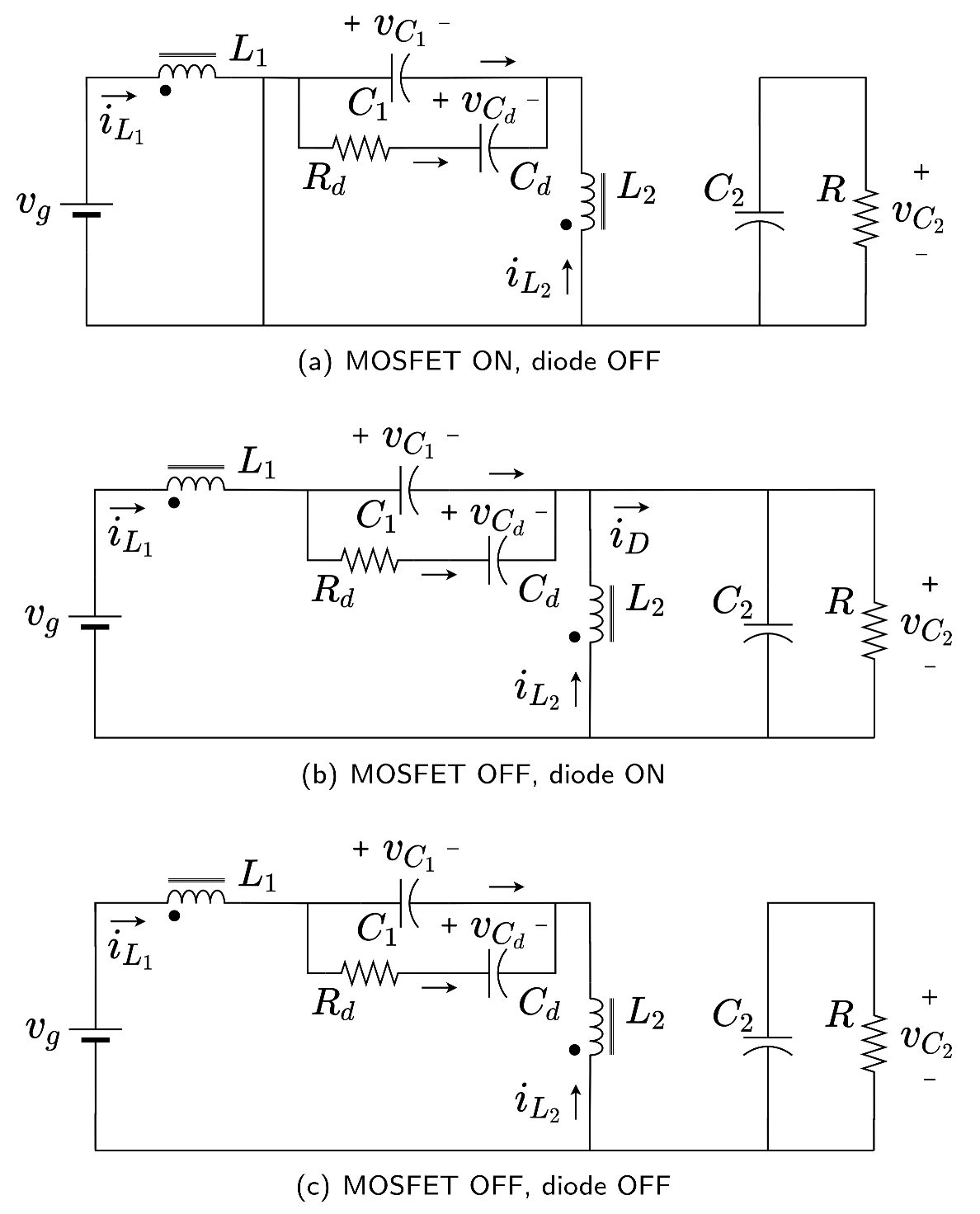

Zeta converter is another high order step-up/step-down topology with a switch in series at its input, reason why it has received less attention [

12]. The switching cell of the SEPIC, Ćuk and Zeta converters can be easily derived from the buck-boost cell. It has two inductors and an additional intermediate capacitor in addition to the transistor and diode. Since the intermediate and the additional output filter capacitors are usually designed to operate with small voltage ripples, a high frequency transformer can also be added to the basic topologies to provide electrical isolation between the power grid and the load. Because of their high order, all these step-up/step-down converters (SEPIC, Ćuk and Zeta) can exhibit several discontinuous conduction modes [

13]. The most usual DCM operation occurs when the diode turns OFF without the MOSFET still turning ON. At this instant, the sum of the two inductor currents which corresponds to the diode current becomes zero [

14].

In the literature there are many applications of high order converters such as the basic and modified versions from SEPIC, Ćuk and Zeta topologies operating in DCM. The applications include renewable energies, supplying LED loads, electronic systems, motor drives and electrical vehicles, among others. In the case of the SEPIC converter, it has been the most used in applications like three phase rectifier [

11], low power and high power factor correctors [

10,

15,

16], interleaved with coupled inductors [

4], PFC with higher output voltage [

17] and DC-DC conversion with high voltage gain [

18]. In the case of the Ćuk converter the most common applications are bridgeless PFCs [

15,

19,

20] and motor drives [

21]. A particular high-order topology combines Ćuk and SEPIC converters to be used in a switched reluctance motor drive [

22]. Isolated SEPIC and Ćuk converters are usually in two-stages buck-boost inverters [

23]. Finally, in the case of the Zeta converter, there are applications reported in topics such as renewable sources [

24], power supplies [

25] and electric vehicle battery chargers [

26].

The dynamic analysis of the converters is an important topic to design controllers that guarantee the correct operation of the systems. Therefore, it is important to have dynamic models that accurately reproduce the behavior of the switched converter. Modelling methodologies in DCM have been addressed by following analytical or equivalent circuit approaches. On the one hand, the main analytical approach, proposed by Ćuk and Middlebrook, is based on a unified representation of state spaces [

2]. This analytical methodology has been used also in high-order converters [

3,

14,

27,

28]. On the other hand, the equivalent circuit methodology is an approach which is known in literature as generalized switch averaging technique, first proposed by Vorperian [

6]. This methodology applies directly to converters in DCM having a canonical three-terminal switch-cell constituted by the active and passive switch pair. Connecting the canonical cell to a single inductor conforms the core of the well-known basic converters buck, boost and buck-boost. The canonical cell also appears in the Ćuk converter but not in the SEPIC and Zeta converters. The direct application of Vorperian’s analysis methodology requires the converter to have a common-common configuration for the DCM switch. An example of this methodology is the model of the modified Zeta converter presented in [

29].

Analytical and equivalent circuit approaches can be used to obtain reduced or full-order models as is proposed in a complete analysis with comparisons of both approaches in [

3]. The main feature of reduced-order models is that they are only capable of accurately predicting the converter dynamics at low frequencies. For instance, the model presented in [

27] can accurately predict small-signal responses up to one-tenth of the switching frequency.

After an intense search of high-order converters in the literature, it is concluded that the scientific community is more focused on the application than on the modelling of high order converter operating in DCM. The motivation of this research emerges from the fact that the methodology proposed in [

28] to model the DCM of the Ćuk converter does not work properly in the case of the SEPIC converter in DCM. There were problems to identify a key current component denoted as

in the differential equation of the intermediate capacitor voltage. In this work, a novel full-order method based on including explicitly the diode average current in the system equations is proposed. The diode average current is obtained for the SEPIC converter by means of a graphical procedure adapted from the procedure followed for the Ćuk converter in [

28] and for the interleaved converters in [

30]. The use of the diode average current allows us to extend easily the model developed for the SEPIC converter to the Ćuk and Zeta converters. In fact, it provides better results for the Ćuk converter than using the model in [

28]. In practice, it is a common procedure to magnetically couple the inductors to reduce from two to one the magnetic core to implement both inductors [

31]. Another typical procedure is adding a damping network to improve the transient converter behavior. The damping network is a simple way to minimize the settling time and suppress current and voltage spikes preserving the semiconductor devices. It is also well known that the addition of a damping network in parallel to some capacitors considerably improves the converter’s dynamics (see Chapter 16 in [

1]). Another example of the improvement of a converter’s dynamics can be found in [

32], where the use of magnetic coupling and a damping network moves the right half plane zeroes to the left half plane in a similar high-order switched converter operating in CCM. The prize to pay for the mentioned improvements is a slightly reduced conversion efficiency due to the added resistive losses in the damping network. In all the cases, the model proposed in this work can also be easily adapted to versions of the SEPIC, Ćuk and Zeta converters depicted in

Figure 1 in which the inductors are magnetically coupled and/or an

damping network is added in parallel to the intermediate capacitor. The main benefits of the proposed methodology are listed below:

Because it is based in simple graphical representations of inductor’s and diode current waveforms it is easy to understand and apply;

Provides a full-order model that can be particularized to any of the three high-order step up/down switching converters with or without positive/negative magnetic coupling between inductors and damping networks in the intermediate capacitor;

The three converters and its variants can be analyzed in the classical forms depicted in

Figure 1, where the MOSFET and diode do not share any common node. To apply Vorperian’s method, which also provides full-order models, the structures of two of the converters must be modified to a “common–common” configuration of the DCM switch.

This paper is a contribution to full-order modeling of the SEPIC, Zeta, and Ćuk DCM converters, and it includes simulation, hardware-in-the-loop, and experiments in power circuits to validate the obtained models. Most works in the literature perform only theoretical analysis and simulations. The remainder of the article is organized as follows:

Section 2 proposes the modelling procedure, first in a detailed way for the SEPIC converter, and later its generalization to Ćuk and Zeta converters. The model performance in terms of frequency and transient responses are verified in

Section 3 by comparing the theoretical predictions with ideal simulations of the switched converters using PSIM software. In addition, hardware-in-the-loop tests and experimental results are presented. Finally, the conclusions and proposal for future works are discussed in

Section 4.

3. Results

Comparisons between the theoretical and the switched models in time and frequency domains are presented in this section by means of PSIM simulations, hardware-in-the-loop (HIL) tests and experimental results. A description of the nomenclature used is presented below:

Theoretical results: these are results in the time or frequency domains obtained from the transfer functions of the small-signal models;

Switched results: they are obtained from simulations in the PSIM software;

Hardware-in-the-loop results: measurements carried out on the hardware-in-the-loop tools (PLECS RT-box 1, Interface and Texas Instruments LAUNCHXL-F28069M);

Experimental results: direct measurements in a real proof-of-concept reconfigurable prototype of high-order converters.

In order to explore the scope of the proposed theoretical model, the three high-order converter structures have been used with different magnetic couplings: null, positive and negative. A base set of circuit parameters has been proposed for all three converters. Some parameters were intentionally changed to analyze the response under non-fulfillment of design criteria (high voltage ripple capacitors or inductor currents without triangular waveform).

It is relevant to clarify the notation used to present the results. Until now in this paper, average values nomenclature has been used to express variables from the theoretical model according to equation ; where is an average value, X is a steady state value, and is the small signal value. Thereby , , , represent theoretical model variables and , , , will be used to denote switched model variables.

3.1. Component Description

The selection criteria for the inductors is to keep a fixed value of the self inductance with or without magnetic coupling. The value of and have been selected equal to H. Additionally, the inductors selection fulfills a compromise between a high operating margin in DCM and an acceptable current ripple. A mutual inductance of H is achieved with the chosen inductors array, so a coupling factor of is obtained. The mutual inductance can be considered positive or negative depending on the component ports connection. In some cases it has been considered that there is no coupling between and ().

The values of the capacitors

and

were selected considering the criteria of reduced size and approximately constant average voltage. Capacitor values of

F ensure peak-to-peak ripple capacitor voltage amplitudes less than 4%. Regarding the damping network, its values have been selected, taking into account the guidelines provided in [

32]. A capacitor ten times larger than the intermediate one has been selected while the series resistor has been adjusted by simulation so that it ensures a sufficient damping of the internal dynamics. The selected values were

for

and

F for

. The load resistance has also been selected as

to ensure DCM at the operation points considered in the study.

Three parameter sets have been defined for the proposed model validation. They are summarized in

Table 3. Because of a temporary unavailability of the initially selected loosely-coupled magnetic components [

31], an almost equivalent arrangement using Coilcraft’s Hexa-Path perfectly magnetic coupled inductors and other non-coupled inductors has been used. A description of each arrangement is given below:

Test-1: Base set formed by coupled inductors , with mutual inductance M, capacitors and and a load resistor R;

Test-2: Corresponds with Test-1 but with damping network;

Test-3: Corresponds with Test-1 with an intermediate capacitor reduced ten times. This test has been defined to study the proposed model under a high voltage ripple condition.

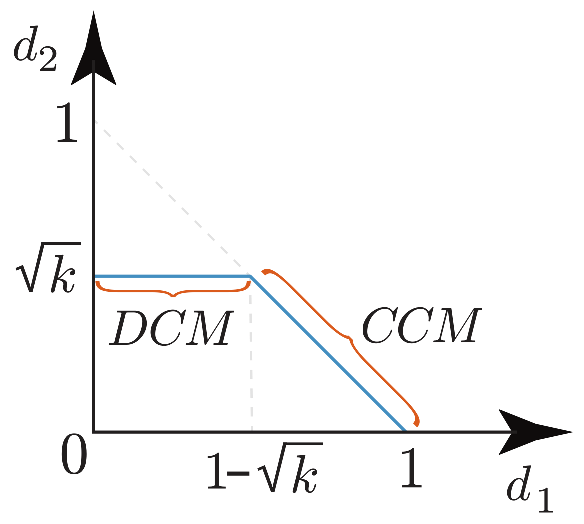

3.2. Operation Points

Taking into account the three high-order converter structures and the three possible types of coupling (positive, negative or zero), three case studies have been defined to verify the performance of the proposed full-order model in a broad enough way. The case studies are: Ćuk without magnetic coupling between the inductors, SEPIC with positive magnetic coupling and Zeta with negative magnetic coupling. The operating points listed in

Table 4 are obtained by replacing in the theoretical expressions the base set of circuit parameters (Test-1) and the simulation parameters (

V,

,

kHz). In this table the constant (

k) allows determining the conduction mode in which the converter operates. This value is less than

, and therefore the converters operate in DCM, as it is verified for all presented cases. Finally, it is satisfied that

in steady state.

3.3. Transfer Functions

Table 5,

Table 6 and

Table 7 includes the theoretical transfer functions of inductor currents and capacitor voltages that have been considered in time and frequency domain analysis. In this work, transfer functions can be a function of the input voltage or the duty cycle. The transfer functions can be of 4 or 5 order depending on the addition of the damping network in the topologies. In

Table 5,

Table 6 and

Table 7, it can be seen that the transfer function of

is the only one that has all its zeros in the left half-plane in all cases. The other transfer functions have at least one zero in the right half-plane. Another important finding is seen in the analysis of the damping network effect. In the absence of the damping network, the transfer function presents a pair of complex poles with a very small real part

and very little damped. In fact, they are the dominant poles. With a damping network, the effect of these poles is well damped and the dominant pole becomes a real pole with value of 4012. From the point of view of pole analysis, there is a good damping.

3.4. Time Domain Responses

3.4.1. Small Signal Response

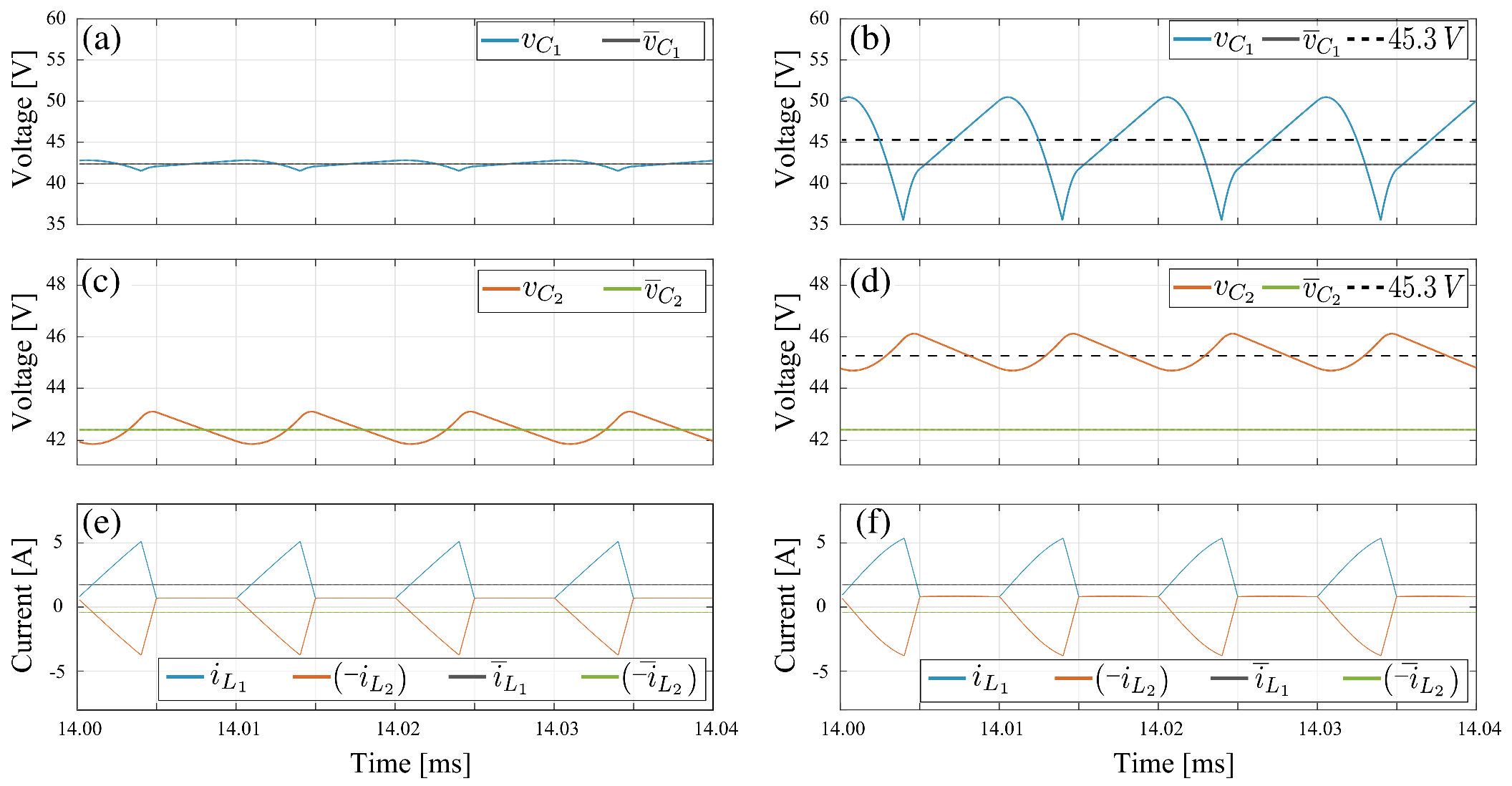

The objective in small signal is to verify the correspondence between switched and theoretical model responses. The structure used in this comparison is the Ćuk converter without magnetic coupling with the parameter set for the power circuit Test-1. To obtain the results depicted in

Figure 6, a reference change in the input voltage of 1 V has been applied. The input voltage

changes from 9 V to 10 V at

ms and decreases again to 9 V at

ms. The theoretical model results correspond to a linearized model for the operating point

V. In

Figure 6a, the averaged model currents have a constant behavior, except during transitions where a small disturbance occurs, but the steady state condition is quickly reached. In

Figure 6b it can be observed that the average voltages of the proposed model follow the behavior of the switched model even after the disturbance. The magnitudes obtained by the theoretical model for

V are approximately equal to the operating point values listed in

Table 4. Currents and voltages averaged values of both switched and theoretical model for

V and

V are given in

Table 8. These results validate the good performance of the theoretical model calculated for

V condition to approximate the average values of the responses obtained from the switched simulations for

V and

V. The relative error (RE) were less than

% in all cases. The results show that the

V condition is a small signal operation as had been supposed before.

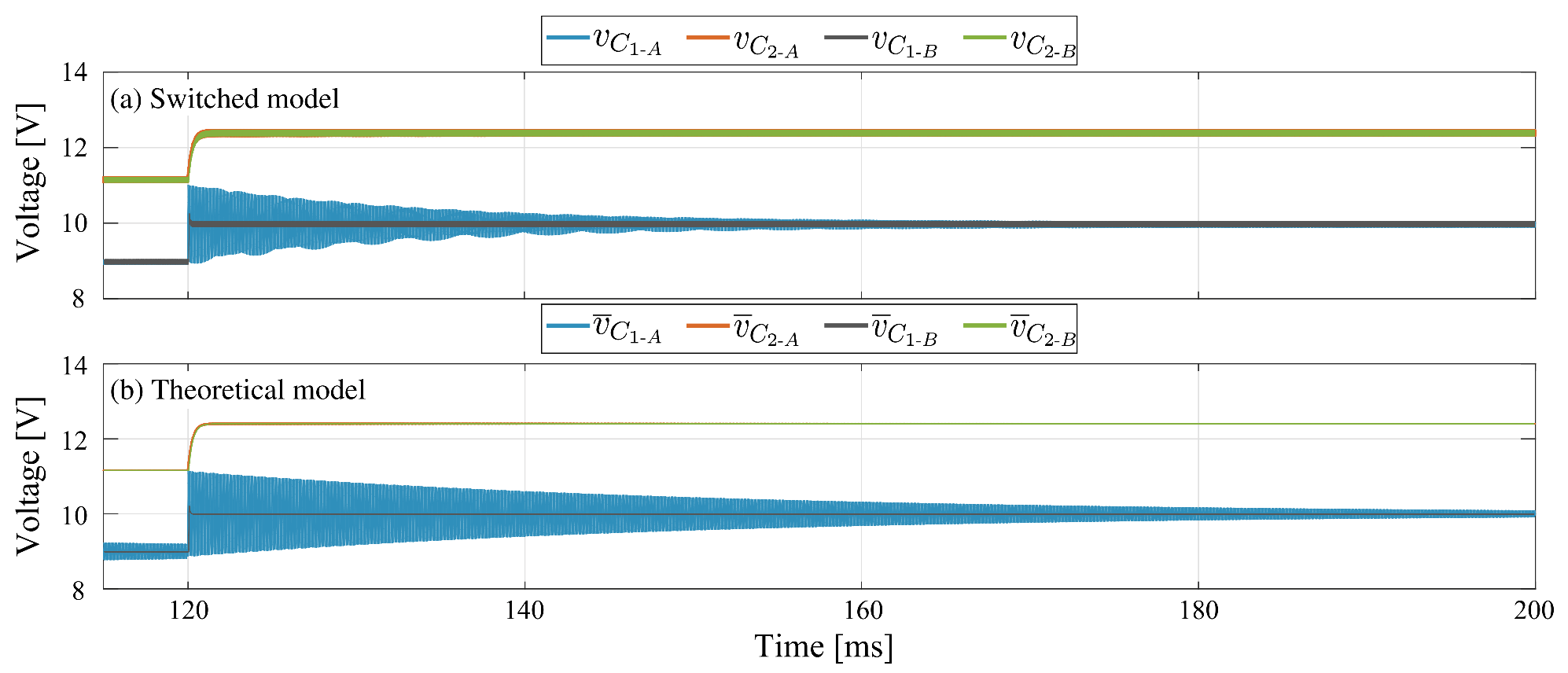

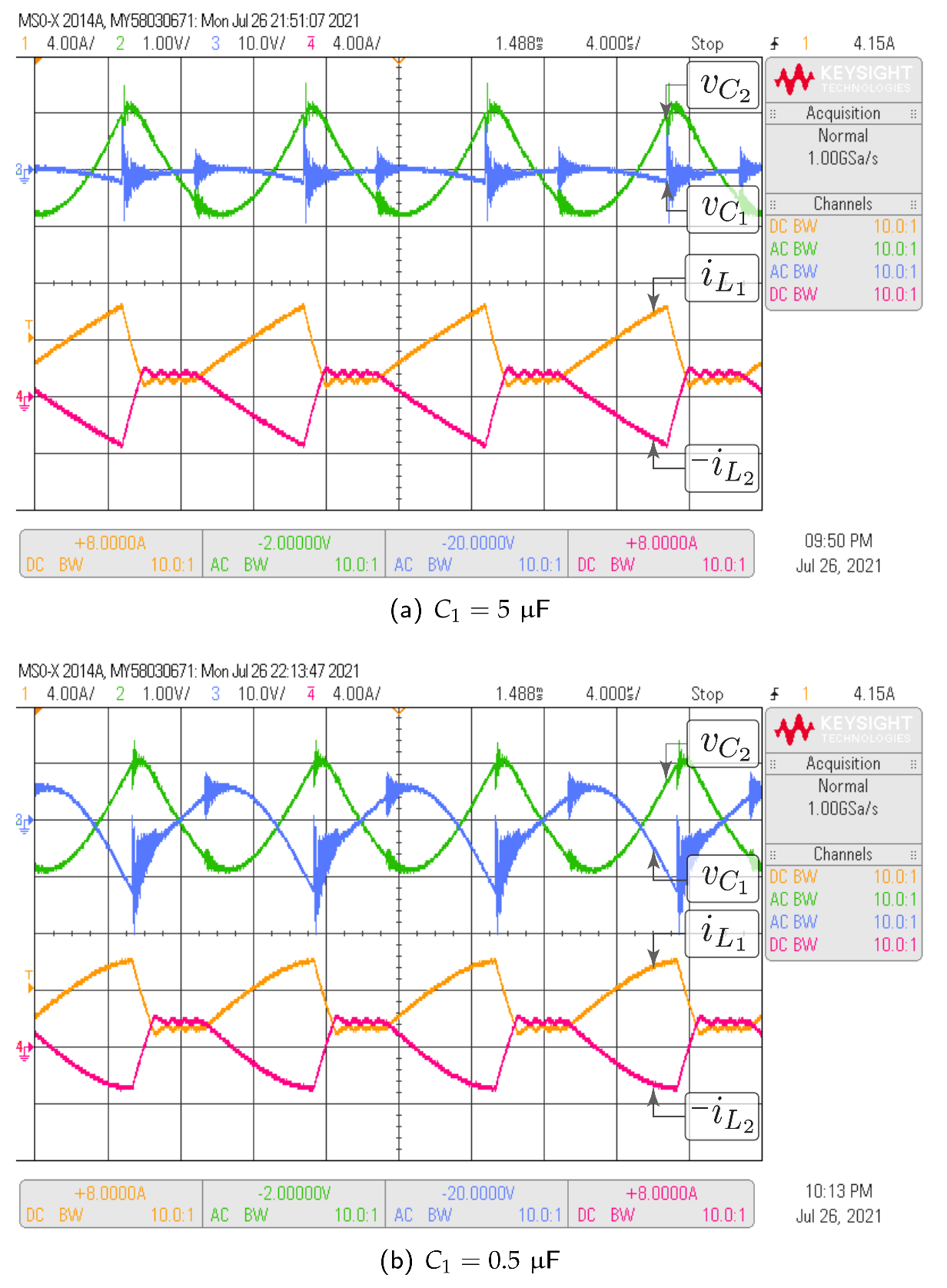

3.4.2. Damping Network Effect

A damping network can be used in parallel with the intermediate capacitor to decrease the settling time. In the analysis carried out in this work, the SEPIC converter was the topology that, without a damping network, requires the longest time to reach a steady state. For this reason, the positive-coupled SEPIC converter was used specifically to analyze the damping network effect on the capacitors voltage. Two parameter sets have been used in the simulation: Test-1 for response without damping network and Test-2 for the analysis of the damping network effect. Switched and theoretical model responses are depicted in

Figure 7a,b. In the presented results, the input voltage changes from 9 V to 10 V at time

ms. The direct effect of the damping network is observed in the intermediate capacitor voltage. In the absence of the damping network, the voltage requires a significant settling time (in the order of 80 ms) to reach steady state. On the other hand, with the addition of the damping network, the settling time is minimal. These behaviors are equivalent in both switched and theoretical models. It can be verified in graphs from

Figure 7 that the theoretical model of average values also has an equivalent performance to the switched model when the damping network is added to the power circuit of the higher-order converter.

3.4.3. Non-Fulfillment of Design Criteria

The topology considered in this case is the negative-coupled Zeta converter. The purpose of this analysis is to show that, when the low ripple condition is not fulfilled in the capacitors, the theoretical averaged model does not approximate accurately the switched model. In this section, the Test-1 and Test-3 parameter sets have been considered. The difference is that the value of

passed from

F in Test-1 to

F in Test-3. Derating the capacitor by a factor of 10 times is a violation of the design criteria of approximately constant capacitor voltage. Note that in the Zeta converter the averaged voltages in

and

are equal. According to

Table 4 this value is

V. It can be verified in

Figure 8 that

and

are equal to the theoretical value in all cases, since the operation point in steady state does not depend of the capacitor values. It is also observed that for the condition

F the average values of the switched model voltages are approximately equal to the theoretical model values. When the capacitor

changes to

F two situations are evident: (i) the voltage ripple in

increases from

under design conditions to

, while the ripple of

remains constant, (ii) the average values voltages in

and

for the switched model increase and differ from the theoretical model values.

In

Figure 8d, it is observed that

does not correspond to the average value of

. It can also be easily verified by area analysis in

Figure 8d, that

does not correspond to the average value of

. In fact the new average value of

and

is

V. It is concluded that the theoretical model values do not correspond with the average value of the switched model, which increased by

V with the decrement in

capacitor. An important comment on the currents comparison in

Figure 8 is about their waveform shapes. In

Figure 8e both currents,

and

, have a piecewise linear function of triangular shape while in

Figure 8f, the triangular waveform is not completely linear. Logically the capacitors ripple increment affects the currents triangular shape, which also demonstrates that in the high voltage ripple condition the theoretical model does not faithfully reproduce the switched model results.

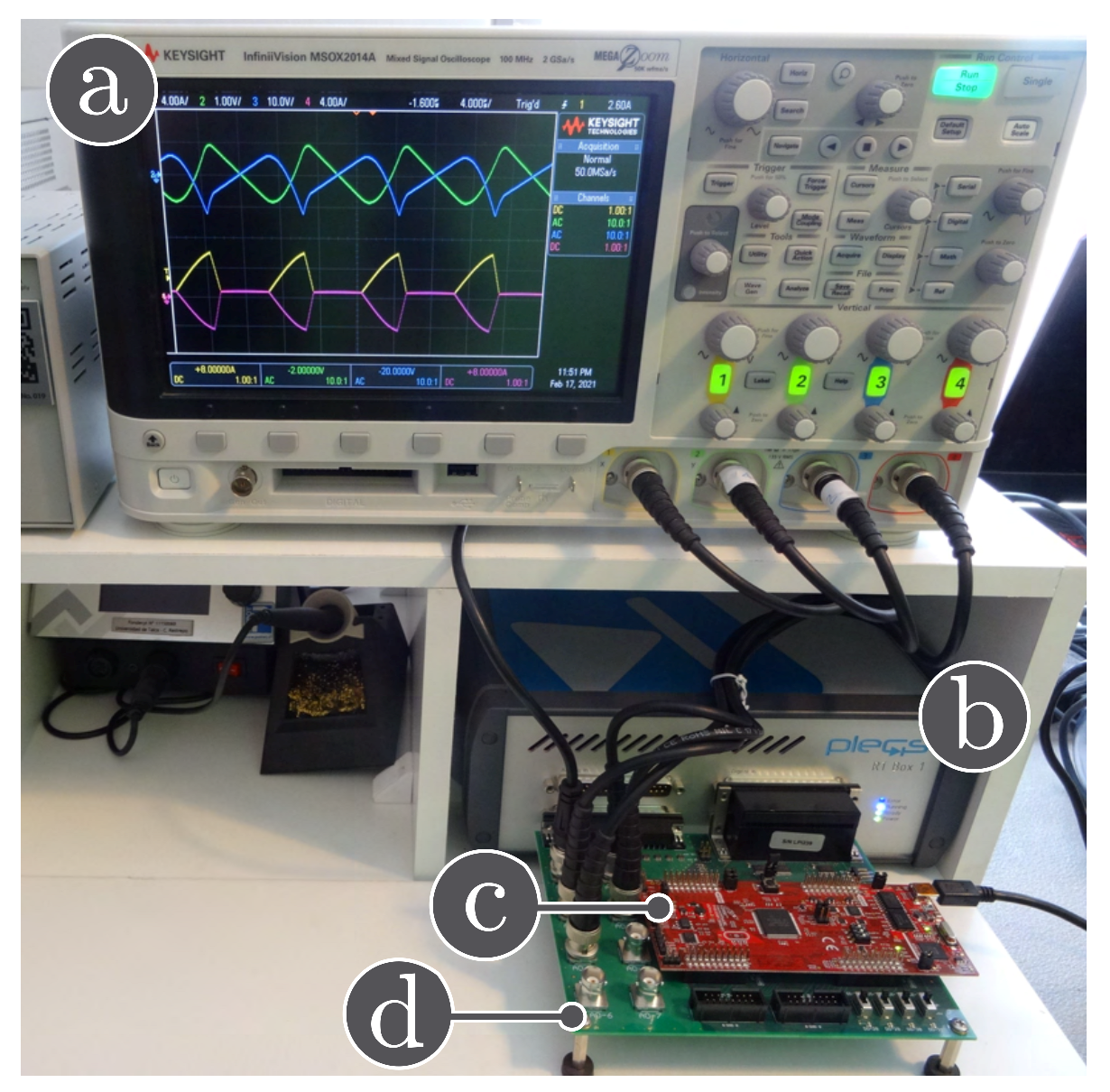

3.4.4. HIL Validation

Nowadays, the use of Hardware-in-the-loop (HIL) tools to validate the controllers performance is more popular [

33]. In this paper, different tests have been carried out in HIL to validate the simulation results in the high-order switched DC-DC converters previously presented by means of the experimental setup shown in

Figure 9. The HIL testing system consists of:

A TI 28069M LaunchPad;

An RT Box LaunchPad Interface;

A laptop with the PLECS software;

An oscilloscope Keysight MSOX2014A,

where the evaluation kit, a TI 28069M LaunchPad (the red board), is connected to the RT Box via an RT Box LaunchPad Interface (the green board). The differente high-order switched DC-DC converters has been modelled using PLECS RT Box 1. In this way, the converter duty cycle has been generated using TI 28069M LaunchPad, which is a Texas Instrument microcontroller.

In this subsection, the HIL test is presented with the goal of validating the time domain responses presented in the previous subsections.

Figure 10 shows the HIL test to compare the proposed model and the simulation of the switched model using PSIM of the Ćuk converter without coupled inductors shown in

Figure 6. In addition, the HIL test to validate the proposed model and the simulation of the switched model using PSIM of the SEPIC converter with positive magnetic coupling shown in

Figure 7 is presented in

Figure 11. Finally, the proposed model and simulation in

Figure 8 correspond with the the HIL test of the Zeta converter with negative magnetic coupling shown in

Figure 12. A good agreement between the model, the switching simulations and the HIL results is observed in all the cases. Therefore, the proposed procedure models correctly the considered high order step-up and down converter topologies (SEPIC, Ćuk or Zeta) operating in DCM.

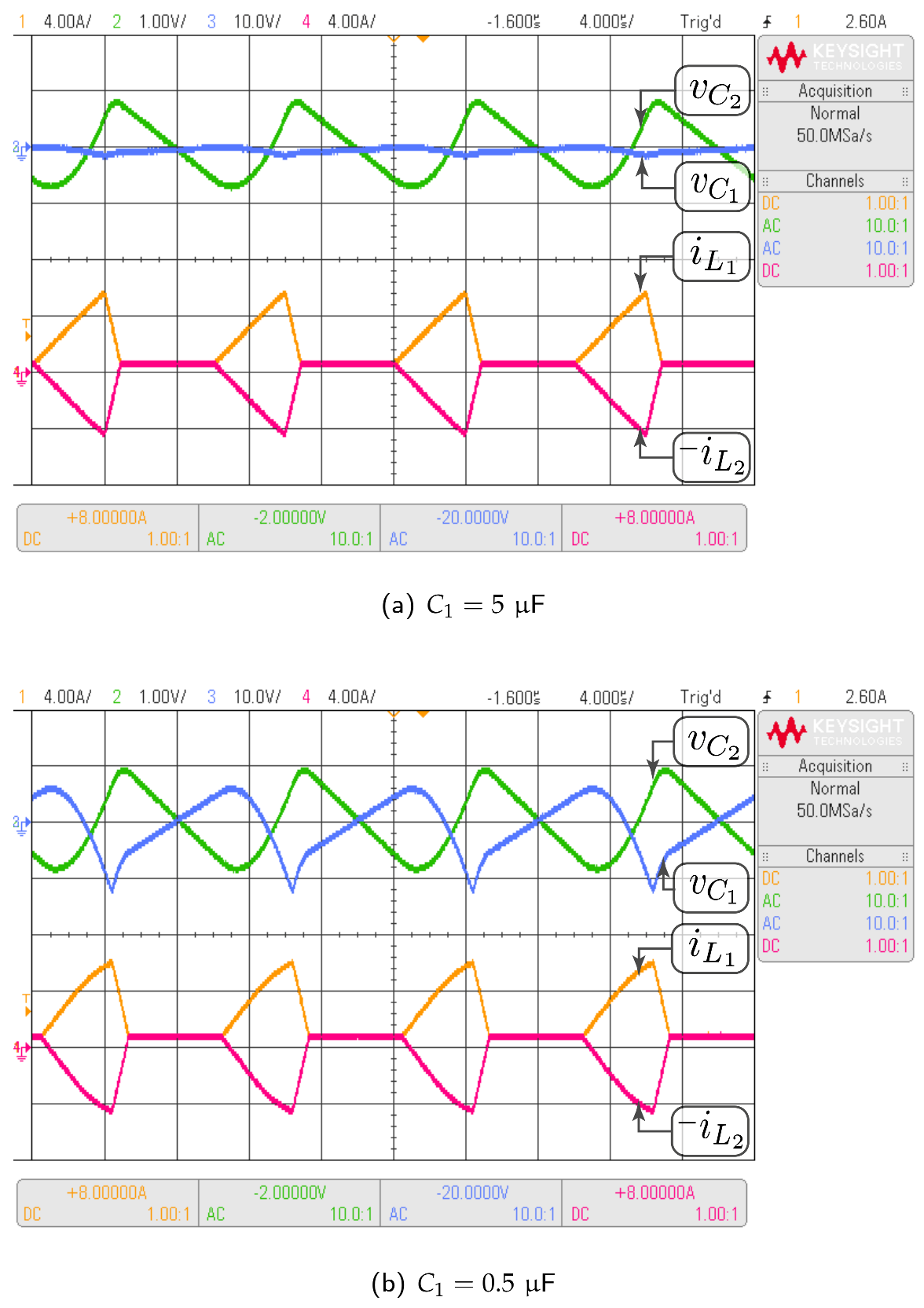

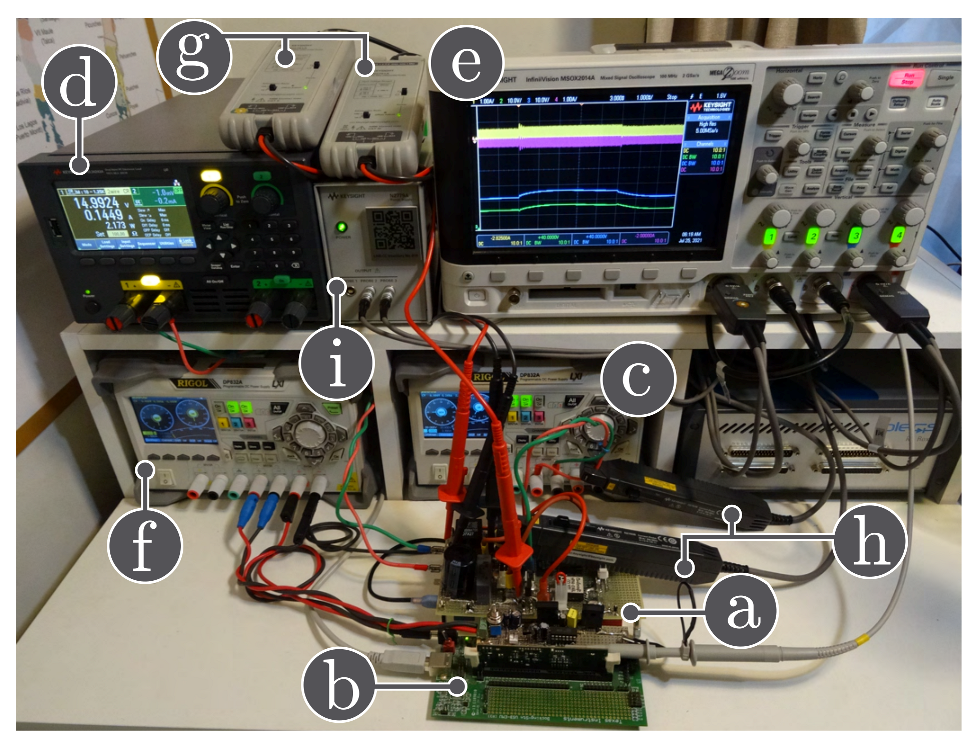

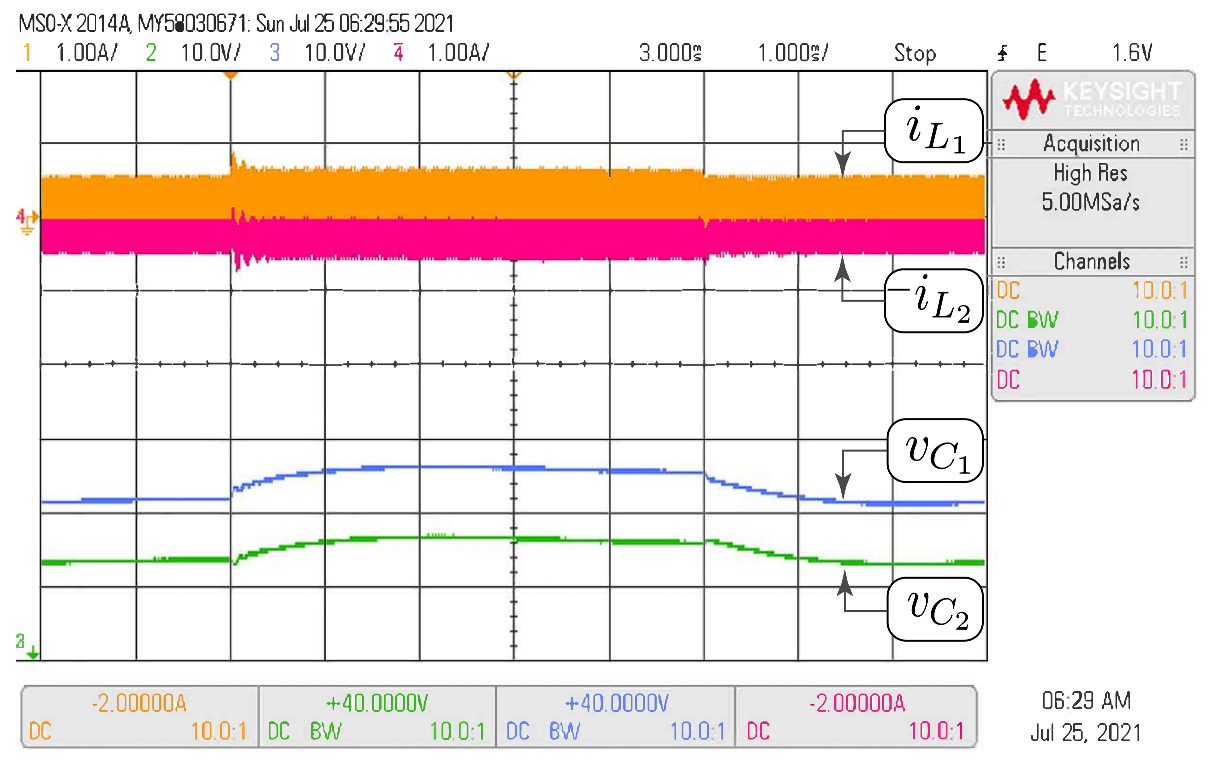

3.4.5. Experimental Results

A reconfigurable power converter was built to validate the theoretical models and the HIL results. Its design allows the implementation of any topology and any magnetic coupling. The components description of the power converter is presented in

Table 9. Considering the reconfigurable characteristic of the power converter, series and parallel interconnections between inductors or capacitors have been done to obtain the closest values to the parameters listed in

Table 3. The components configurations are given below:

Coupled inductors: the arrangement to obtain the inductors with magnetic coupling consist of two perfectly magnetic coupled inductors of

H with two external inductors of

H. The result is two coupled inductors with a mutual inductance of

H and equal self inductance of

H. The inductors arrangement and its equivalent circuit are shown in

Figure 13;

Non-coupled inductors: it is a series arrangement of inductors of 47 H and H;

Intermediate capacitor F: 5 capacitors of 100 nF connected in parallel;

Intermediate capacitor 5 F: 2 capacitors of 10 F connected in series;

Damping network capacitor 50 F: 5 capacitors of 10 F connected in parallel.

The same tests carried out with HIL have been performed with the converter prototype. The experimental setup of the power circuit is shown in

Figure 14. Voltage and current waveforms for a Ćuk converter without magnetic coupling are shown in

Figure 15. The effect of the damping network in the SEPIC converter with positive magnetic coupling is shown in

Figure 16. Finally, the results of the Zeta converter with negative magnetic coupling are shown in

Figure 17. The waveforms in

Figure 15 and

Figure 16 show good agreement with waveforms in

Figure 10 and

Figure 11. The results shown in

Figure 17 have some distortion due to resonances with parasitic capacitances, but they are similar to the ideal waveforms shown in

Figure 12.

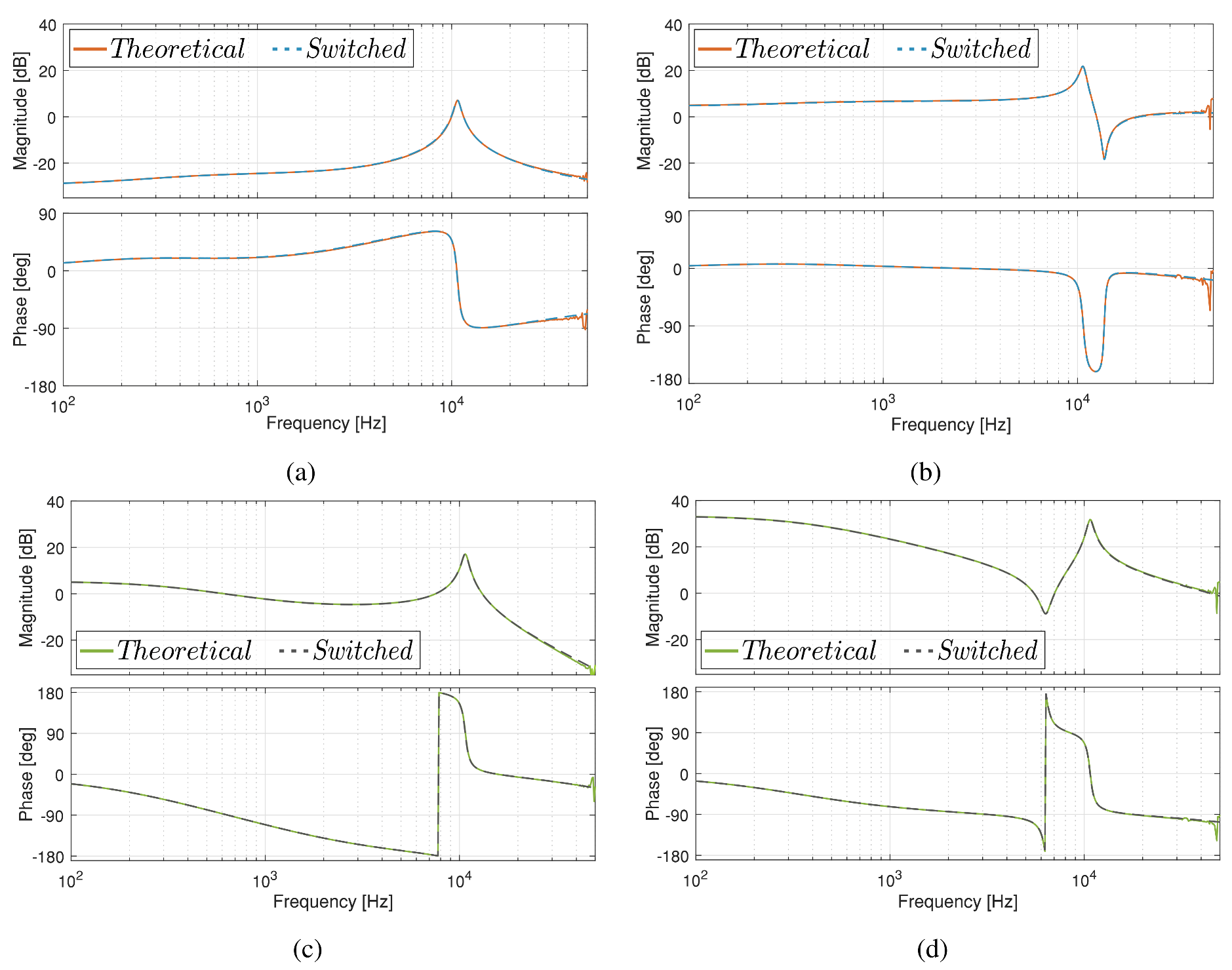

3.5. Frequency Domain Responses

The Ćuk converter without magnetic coupling has been used to analyze the theoretical model’s performance. The same topology was used in the small signal validation. The variables selected for this analysis are one current and one voltage, specifically

and

. To obtain broad information on the frequency domain response, transfer functions were considered a function of the input voltage and the duty cycle, which are included in

Table 5. The lower limit of the frequency analysis is 100 Hz and the upper limit is 50 kHz, a value that corresponds to half the switching frequency. It is observed in all the bode plots shown in

Figure 18 that the theoretical model is equivalent to the switched model response. Another common feature is a resonance that occurs at approximately 10 kHz.

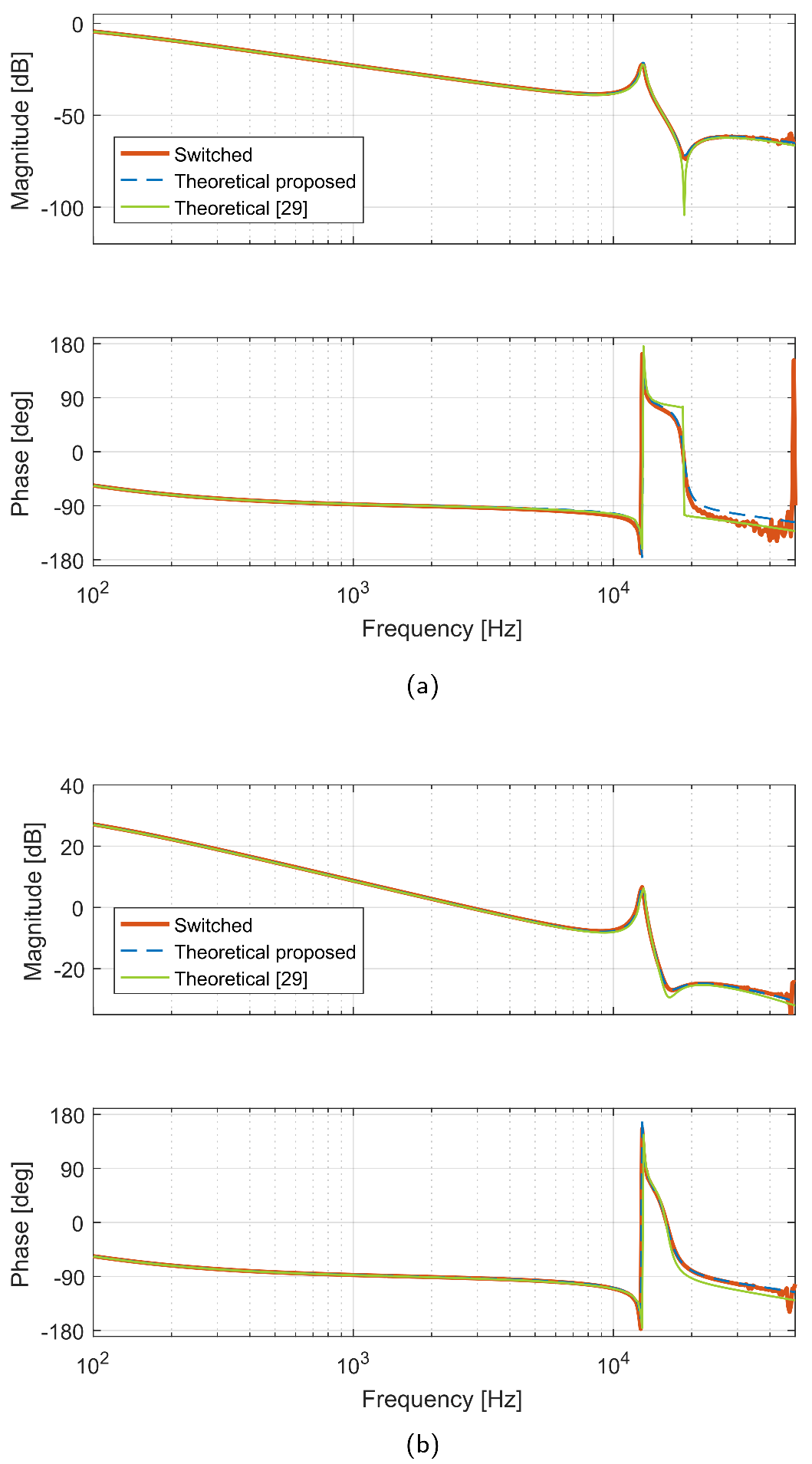

3.6. Frequency Domain Validation

Another way to validate the good performance of the proposed methodology is by comparing results with the generalized switch averaging technique [

6] in a specific case using frequency responses. To make a fair comparison with the literature, a full-order dynamic model of a Zeta converter in DCM presented in [

29] was chosen. The power circuit parameters used to calculate the transfer functions and to obtain the frequency responses are the same as those proposed in [

29]. The transfer functions obtained with both methodologies are given in

Table 10. Note that all of the models are fourth order transfer functions and the numerator polynomial is second order. The corresponding frequency responses are shown in

Figure 19. Both theoretical responses show a good agreement of the frequency response of the switched model up to a frequency about

of the switching one. Note that frequency response of reduced-order models is usually considered accurate up to about 1/20–1/10 of the switching frequency.