Digital Impedance Emulator for Battery Measurement System Calibration

Abstract

:1. Introduction

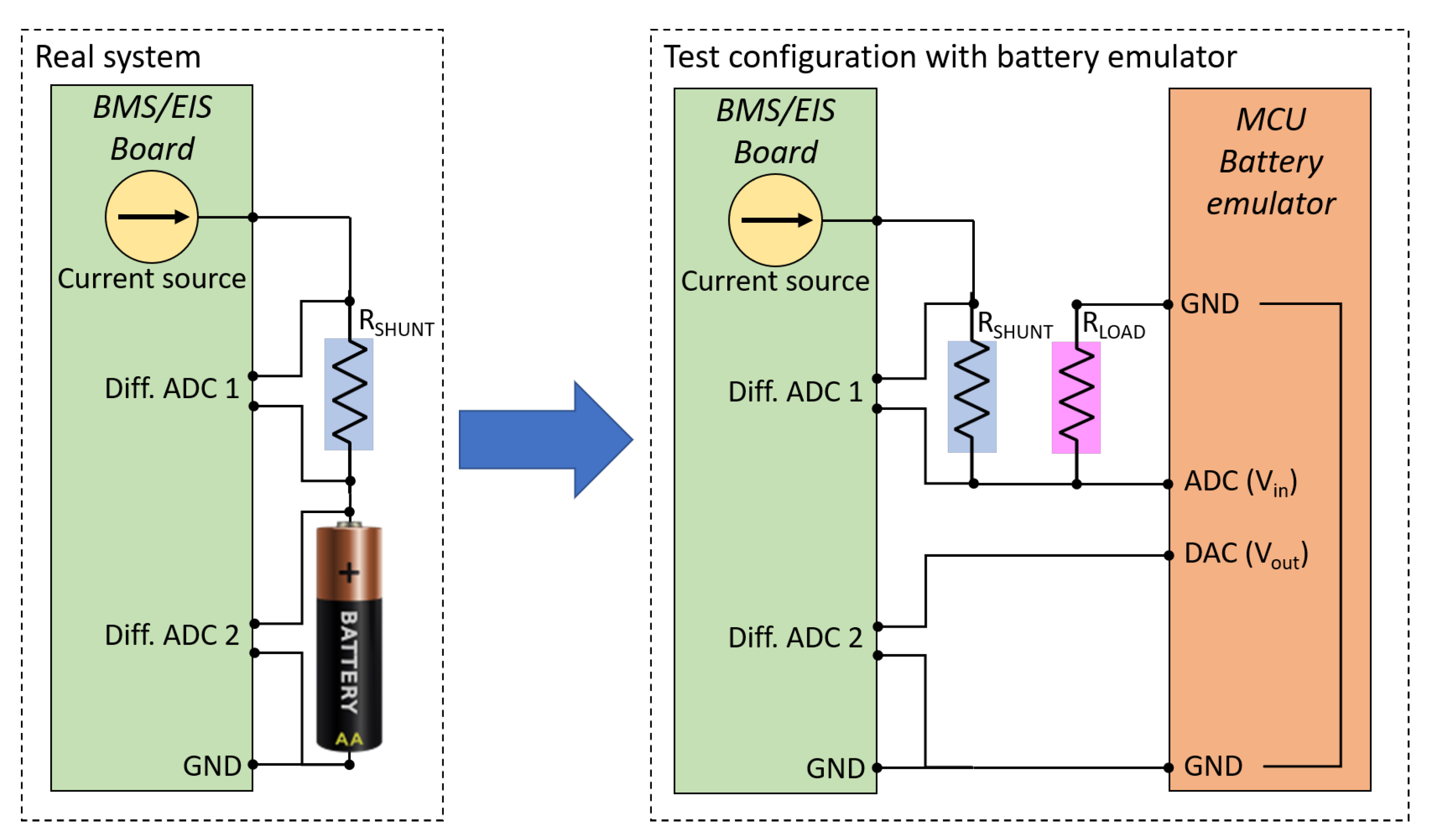

2. General Overview of the Impedance Emulation Method

3. Design of the Fir Filter

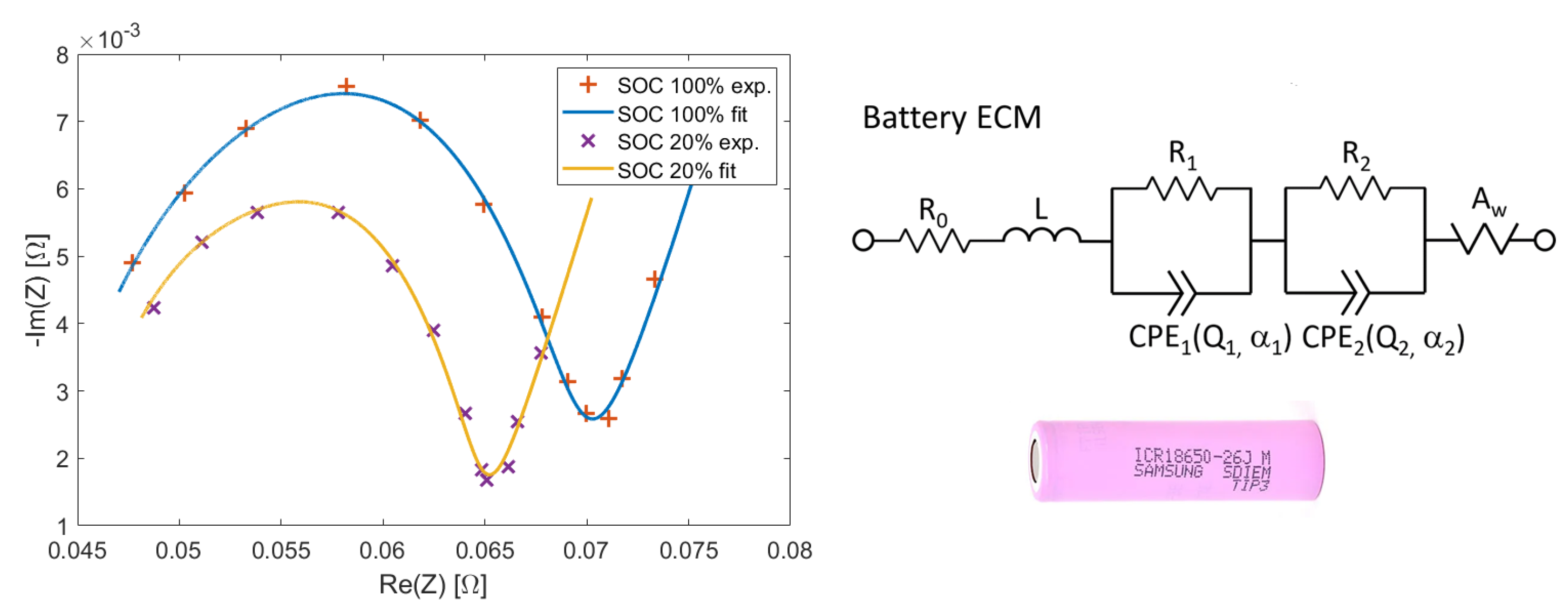

- Modeling the impedance of a battery. Since the aim of the filter is to emulate a real battery, it has been designed to reproduce an experimental impedance. An analytical model facilitates the design process, and allows for more control, thus, the measured impedance has been fitted to an equivalent circuit model.

- Choosing the number of samples and the sampling rate. This has to be done according to the frequency range of interest for the impedance, and with the memory capacity and the clock frequency of the MCU.

- Definition of the impulse response. It has been derived from the impedance curve in the frequency domain by an Inverse DFT.

- A numerical simulation of the filter response. This has been performed on MATLAB in order to verify that the model is correct.

3.1. Step 1: Modeling the Impedance of the Battery

3.2. Step 2: Choosing the Number of Samples and the Sampling Rate

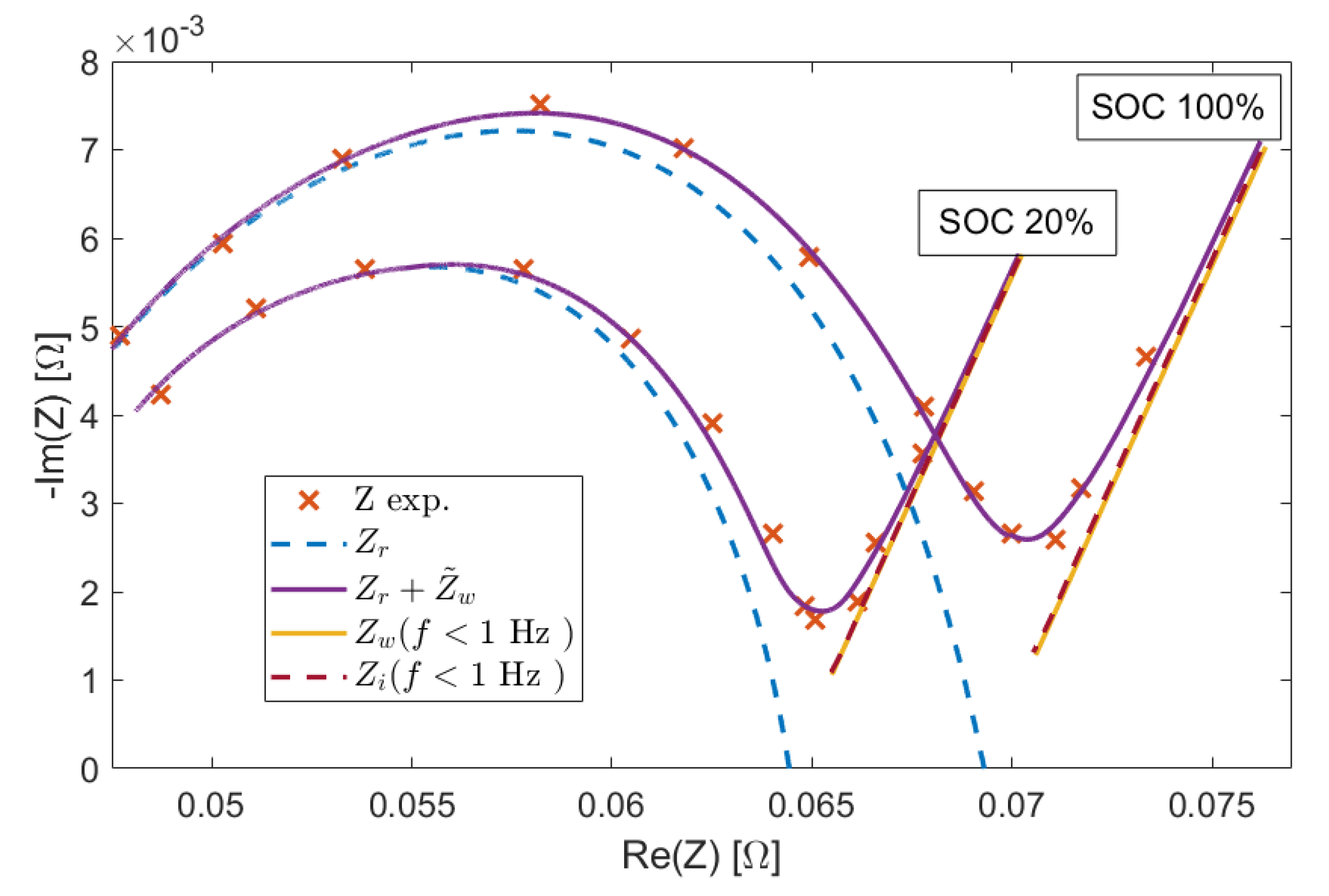

3.3. Step 3: Definition of the Impulse Response

3.4. Step 4: A Numerical Simulation of the Filter Response

- A simulated signal is acquired by the EIS equipment at a sampling rate , and by the emulator at sampling rate . ADC signal quantization is simulated;

- The signal is computed by summing (2), and the DAC output is synthesized as a Zero-Order-Hold signal (ZOH);

- The acquisition of by the EIS equipment at sampling rate is simulated. The impedance is estimated as the ratio of the DFTs of and .

3.4.1. Simulation Stage 1

3.4.2. Simulation Stage 2

3.4.3. Simulation Stage 3

3.4.4. Simulation Results and Discussion

4. Experimental Implementation

4.1. Implementation of the Impedance Emulator on an MCU

4.2. The Acquisition System

5. Results and Discussion

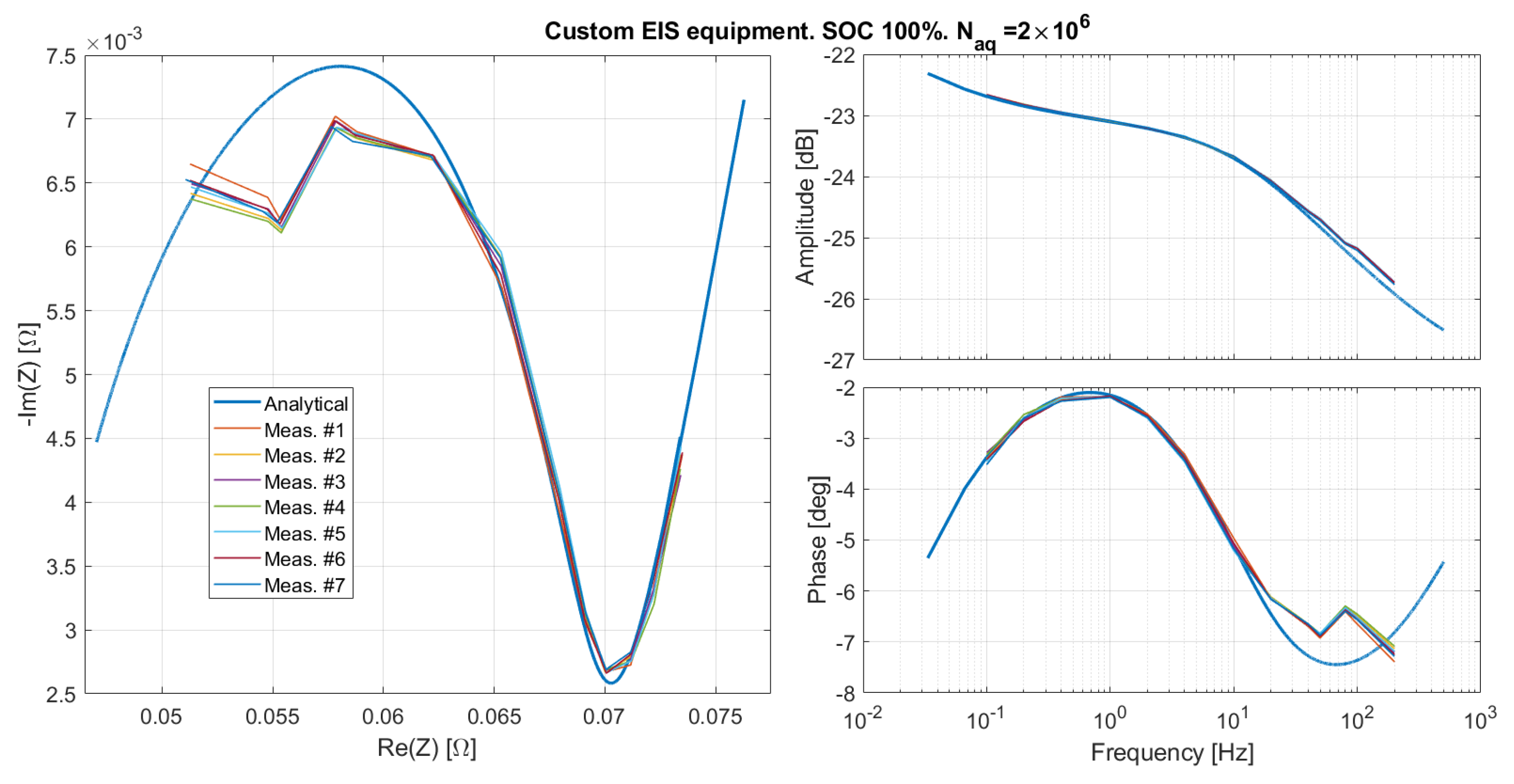

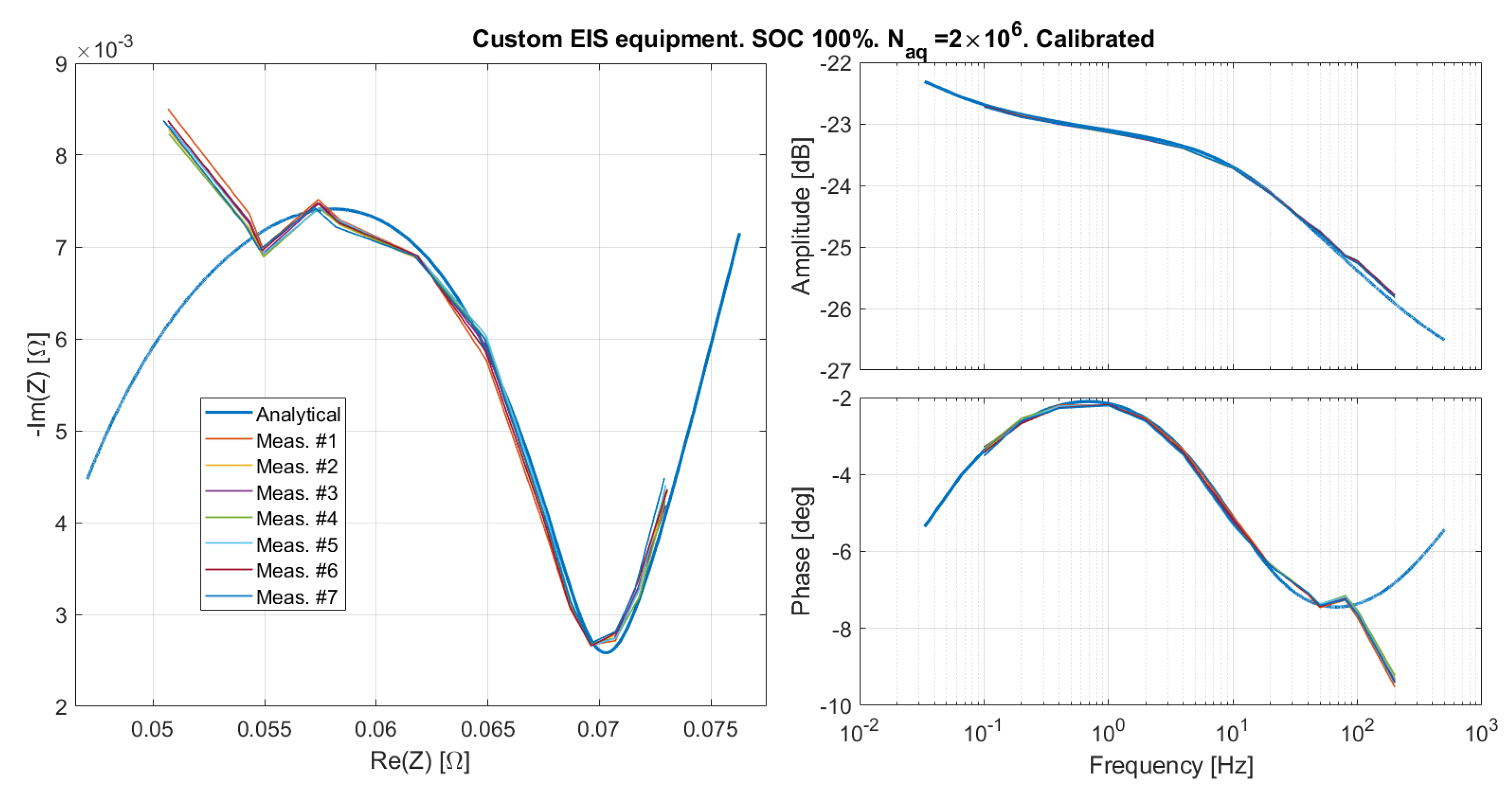

5.1. Results Obtained on the Custom EIS Measurement System

- Phase calibration. Let us consider the column vector of the measured phases , where the index m is used to indicate each one of the repeated measurements, and the vector defined by arranging all the in a single column, . Let us also consider the analogous vector of the expected phases computed analitically. Finally, the column vector of all the frequencies repeated many times on a column as the number of repeated measurements (i.e., , and have the same number of elements). The difference between the measured and the expected phase can then be written as the following linear system in the single unknown :The least-squares solution is s. Only the frequencies up to 100 Hz were included in the equation system.

- Amplitude calibration. Since the ADCs of the acquisition system and of the emulator are different, and can produce different results on equal signals, in general, the amplitude has to be calibrated. As above, let us consider the column vector of the measured amplitudes , then again the single column arrangement , and finally the vector of the expected amplitudes computed analytically. The amplitude correction is given by a calibration constant determined by the following linear system:The least-squares solution is , very close to 1. Indeed, in this case, as it can be seen in Figure 10, the amplitudes were already well matching the expected curve even without calibration.

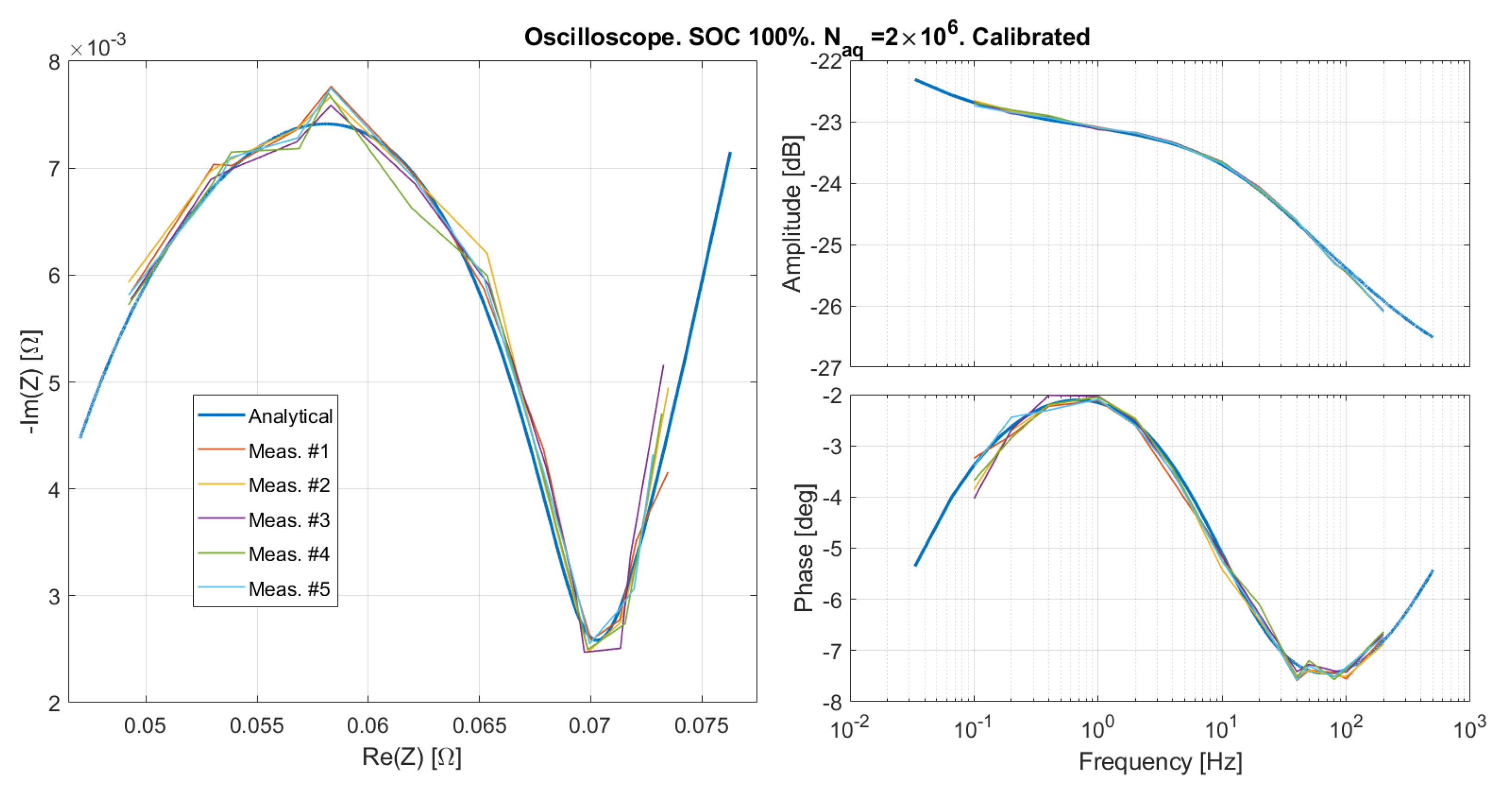

Results Obtained on the Oscilloscope

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Appendix A. Sampling the DAC Signal

References

- Tran, M.-K.; Fowler, M. A Review of Lithium-Ion Battery Fault Diagnostic Algorithms: Current Progress and Future Challenges. Algorithms 2020, 13, 62. [Google Scholar] [CrossRef] [Green Version]

- Guha, A.; Patra, A. Online estimation of the electrochemical impedance spectrum and remaining useful life of lithium-ion batteries. IEEE Trans. Instrum. Meas. 2018, 67, 1836–1849. [Google Scholar] [CrossRef]

- Babaeiyazdi, I.; Rezaei-Zare, A.; Shokrzadeh, S. State of charge prediction of EV Li-ion batteries using EIS: A machine learning approach. Energy 2021, 223, 120116. [Google Scholar] [CrossRef]

- Galeotti, M.; Cinà, L.; Giammanco, C.; Cordiner, S.; Di Carlo, A. Performance analysis and SOH (state of health) evaluation of lithium polymer batteries through electrochemical impedance spectroscopy. Energy 2015, 89, 678–686. [Google Scholar] [CrossRef]

- Koleti, U.R.; Dinh, T.Q.; Marco, J. A new on-line method for lithium plating detection in lithium-ion batteries. J. Power Sources 2020, 451, 227798. [Google Scholar] [CrossRef]

- Wang, X.; Wei, X.; Zhu, J.; Dai, H.; Zheng, Y.; Xu, X.; Chen, Q. A Review of Modeling, Acquisition, and Application of Lithium-ion Battery Impedance for Onboard Battery Management. eTransportation 2020, 7, 100093. [Google Scholar] [CrossRef]

- Komsiyska, L.; Buchberger, T.; Diehl, S.; Ehrensberger, M.; Hanzl, C.; Hartmann, C.; Hölzle, M.; Kleiner, J.; Lewerenz, M.; Liebhart, B.; et al. Critical Review of Intelligent Battery Systems: Challenges, Implementation, and Potential for Electric Vehicles. Energies 2021, 14, 5989. [Google Scholar] [CrossRef]

- Gong, Z.; Liu, Z.; Wang, Y.; Gupta, K.; da Silva, C.; Liu, T.; Zheng, Z.H.; Zhang, W.P.; van Lammeren, J.P.M.; Bergveld, H.J.; et al. IC for online EIS in automotive batteries and hybrid architecture for high-current perturbation in low-impedance cells. In Proceedings of the APEC 2018, San Antonio, TX, USA, 4–8 March 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1922–1929. [Google Scholar] [CrossRef]

- Carbonnier, H.; Barde, H.; Riga, L.; Carre, A. Electrochemical Impedance Spectroscopy for Online Satellite Battery Monitoring Using Square Wave Excitation. In Proceedings of the 2019 European Space Power Conference (ESPC), Côte d’Azur, France, 30 September–4 October 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Crescentini, M.; De Angelis, A.; Ramilli, R.; De Angelis, G.; Tartagni, M.; Moschitta, A.; Traverso, P.A.; Carbone, P. Online EIS and Diagnostics on Lithium-Ion Batteries by Means of Low-Power Integrated Sensing and Parametric Modeling. IEEE Trans. Instrum. Meas. 2021, 70, 1–11. [Google Scholar] [CrossRef]

- De Angelis, A.; Buchicchio, E.; Santoni, F.; Moschitta, A.; Carbone, P. Practical Broadband Measurement of Battery EIS. In Proceedings of the 2021 IEEE International Workshop on Metrology for Automotive (MetroAutomotive), Bologna, Italy, 1–2 July 2021; pp. 25–29. [Google Scholar] [CrossRef]

- Olarte, J.; Martínez de Ilarduya, J.; Zulueta, E.; Ferret, R.; Fernández-Gámiz, U.; Lopez-Guede, J.M. A Battery Management System with EIS Monitoring of Life Expectancy for Lead–Acid Batteries. Electronics 2021, 10, 1228. [Google Scholar] [CrossRef]

- Allen, J. Simulation and Test Systems for Validation of Electric Drive and Battery Management Systems. In Proceedings of the SAE Technical Paper, SAE 2012 Aerospace Electronics and Avionics Systems Conference, Phoenix, AZ, USA, 30 October–1 November 2012. [Google Scholar] [CrossRef]

- Fleischer, C.; Sauer, D.U.; Barreras, J.V.; Schaltz, E.; Christensen, A.E. Development of software and strategies for Battery Management System testing on HIL simulator. In Proceedings of the 2016 Eleventh International Conference on Ecological Vehicles and Renewable Energies (EVER), Monte Carlo, Monaco, 6–8 April 2016; pp. 1–12. [Google Scholar] [CrossRef]

- Huesca-Nieto, E.A.; Villa-Villaseñor, N.; López-Hernández, J. Arbitrary Waveform Generation Based on Direct Digital Synthesis for Automotive Battery Voltage Transient Simulation. In Proceedings of the 2020 IEEE International Autumn Meeting on Power, Electronics and Computing (ROPEC), Ixtapa, Mexico, 4–6 November 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Bui, T.M.N.; Niri, M.F.; Worwood, D.; Dinh, T.Q.; Marco, J. An Advanced Hardware-in-the-Loop Battery Simulation Platform for the Experimental Testing of Battery Management System. In Proceedings of the 2019 23rd International Conference on Mechatronics Technology (ICMT), Salerno, Italy, 23–26 October 2019; pp. 1–6. [Google Scholar] [CrossRef] [Green Version]

- Barreras, J.V.; Swierczynski, M.; Schaltz, E.; Andreasen, S.J.; Fleisher, C.; Sauer, D.U.; Elkær, A. Functional analysis of Battery Management Systems using multi-cell HIL simulator. In Proceedings of the 2015 Tenth International Conference on Ecological Vehicles and Renewable Energies (EVER), 31 March–2 April 2015; pp. 1–10. [Google Scholar] [CrossRef] [Green Version]

- Barreras, J.V.; Fleischer, C.; Christensen, A.E.; Swierczynski, M.; Schaltz, E.; Andreasen, S.J.; Sauer, D.U. An Advanced HIL Simulation Battery Model for Battery Management System Testing. IEEE Trans. Ind. Appl. 2016, 52, 5086–5099. [Google Scholar] [CrossRef]

- Buccolini, L.; Orcioni, S.; Longhi, S.; Conti, M. Cell Battery Emulator for Hardware-in-the-Loop BMS Test. In Proceedings of the 2018 IEEE International Conference on Environment and Electrical Engineering and 2018 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I&CPS Europe), Palermo, Italy, 12–15 June 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Vergori, E.; Mocera, F.; Somà, A. Battery Modelling and Simulation Using a Programmable Testing Equipment. Computers 2018, 7, 20. [Google Scholar] [CrossRef] [Green Version]

- Di Rienzo, R.; Roncella, R.; Morello, R.; Baronti, F.; Saletti, R. Low-cost modular battery emulator for battery management system testing. In Proceedings of the 2018 IEEE International Conference on Industrial Electronics for Sustainable Energy Systems (IESES), Hamilton, New Zealand, 31 January–2 February 2018. [Google Scholar] [CrossRef] [Green Version]

- Overney, F.; Jeanneret, B. Calibration of an LCR-Meter at Arbitrary Phase Angles Using a Fully Automated Impedance Simulator. Proc. IEEE Trans. Instrum. Meas. 2017, 66, 1516–1523. [Google Scholar] [CrossRef]

- Haykin, S.; Van Veen, B. Signals and Systems, 2nd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2002. [Google Scholar]

- Santoni, F.; De Angelis, A.; Moschitta, A.; Carbone, P. Analysis of the Uncertainty of EIS Battery Data Fitting to an Equivalent Circuit Model. In Proceedings of the 2021 IEEE 6th International forum on Research and Technology for Society and Industry (RTSI), Online Forum, 6–9 September 2021. [Google Scholar]

- Vinagre, B.M.; Podlubny, I.; Hernández, A.; Feliu, V. Some approximations of fractional order operators used in control theory and applications. Fract. Calc. Appl. Anal. 2000, 3, 231–248. [Google Scholar]

| Feature | Value |

|---|---|

| ADC range | 3 V, unipolar |

| ADC resolution | 12 bit |

| ADC sampling rate | 1000 Sa/s |

| ADC sample & hold time | 125 s |

| DAC range | 0–3 V |

| DAC resolution | 12 bit |

| Number of samples N | 30,000 |

| CPU cores | 2 |

| CPU clock frequency | 200 MHz |

| Feature | EIS Equipment/Keysight DAQ | Bench Oscilloscope |

|---|---|---|

| ADC1 range | 5 V, bipolar | 1.2 V, bipolar |

| ADC2 range | 1.25 V, bipolar | 0.12 V, bipolar |

| ADC1/2 resolution | 16 bit | 8 bit |

| ADC1/2 sampling rate | 10 and 100 kSa/s | 10 and 100 kSa/s |

| Number of samples | 2 MSa | 2 and 5 MSa |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Santoni, F.; De Angelis, A.; Moschitta, A.; Carbone, P. Digital Impedance Emulator for Battery Measurement System Calibration. Sensors 2021, 21, 7377. https://doi.org/10.3390/s21217377

Santoni F, De Angelis A, Moschitta A, Carbone P. Digital Impedance Emulator for Battery Measurement System Calibration. Sensors. 2021; 21(21):7377. https://doi.org/10.3390/s21217377

Chicago/Turabian StyleSantoni, Francesco, Alessio De Angelis, Antonio Moschitta, and Paolo Carbone. 2021. "Digital Impedance Emulator for Battery Measurement System Calibration" Sensors 21, no. 21: 7377. https://doi.org/10.3390/s21217377

APA StyleSantoni, F., De Angelis, A., Moschitta, A., & Carbone, P. (2021). Digital Impedance Emulator for Battery Measurement System Calibration. Sensors, 21(21), 7377. https://doi.org/10.3390/s21217377