A New Current-Shaping Technique Based on a Feedback Injection Mechanism to Reduce VCO Phase Noise

Abstract

:1. Introduction

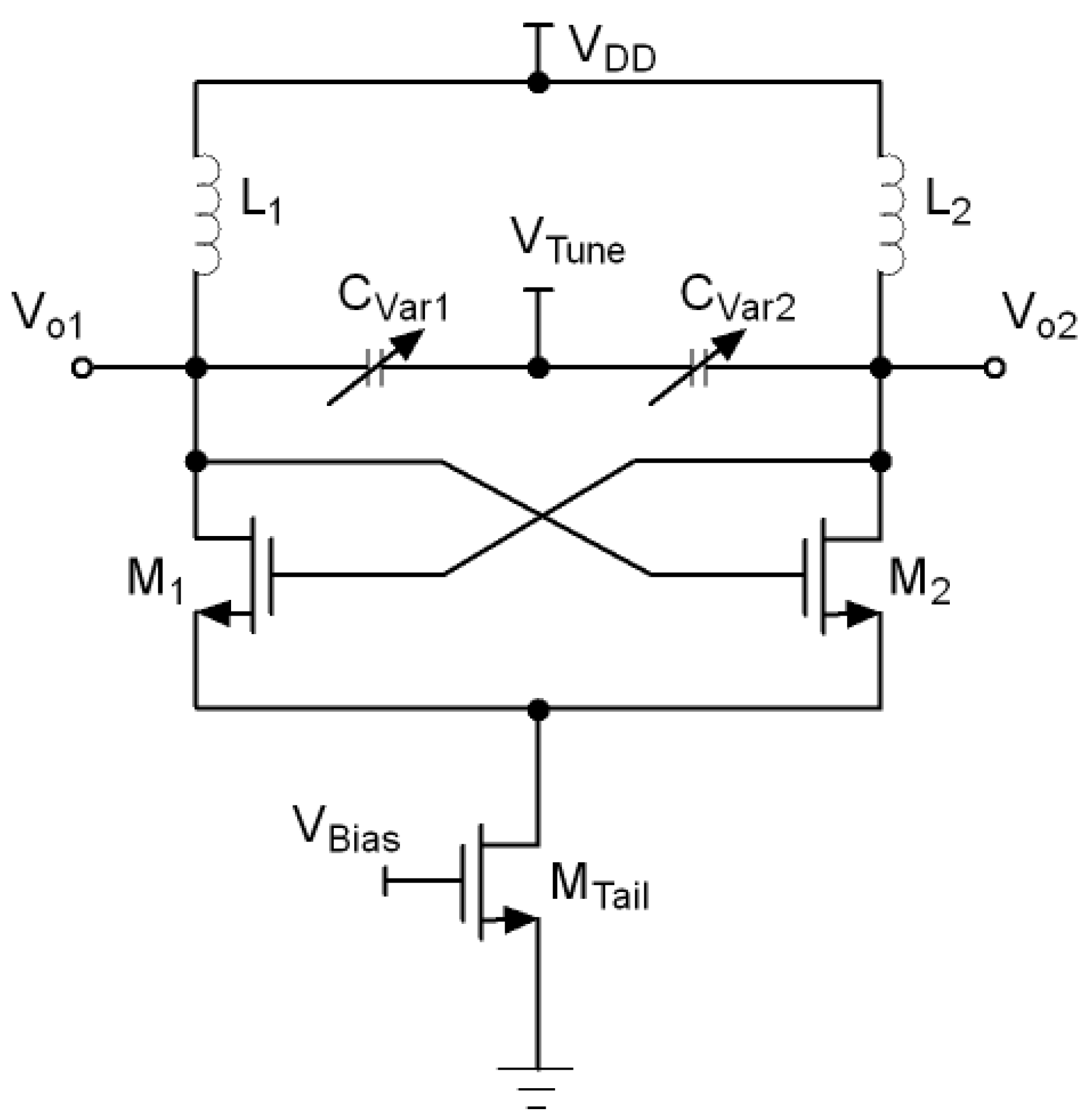

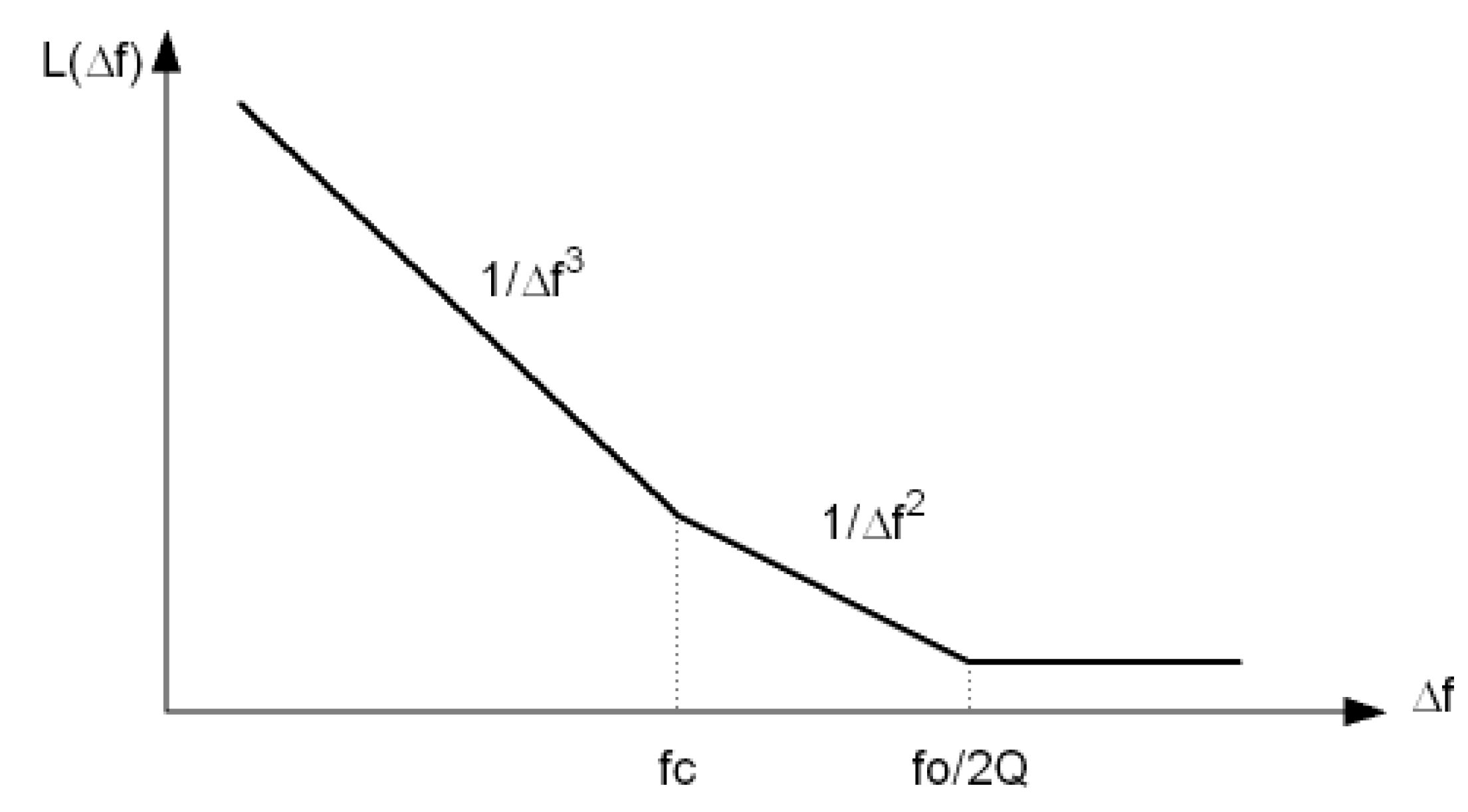

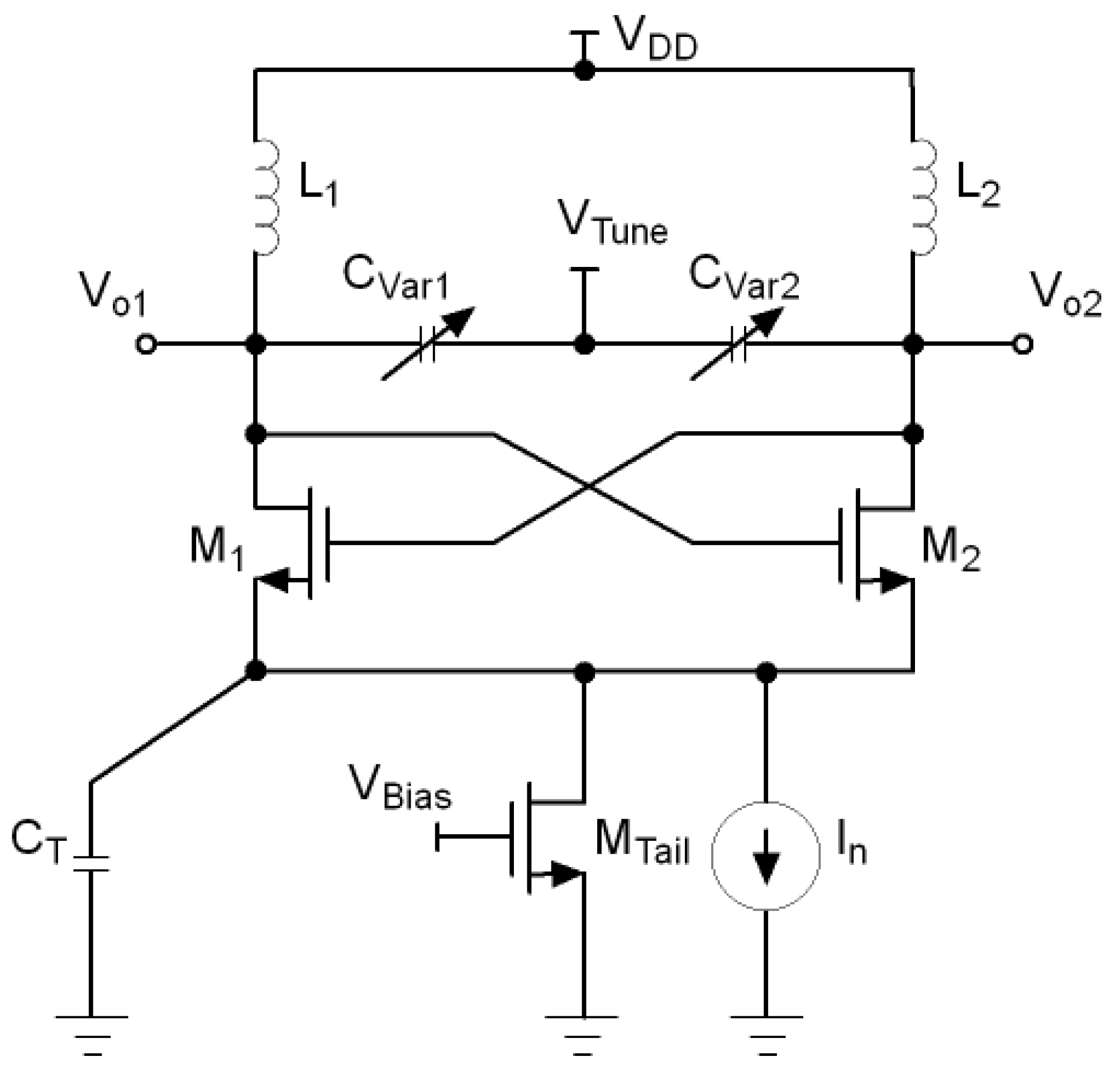

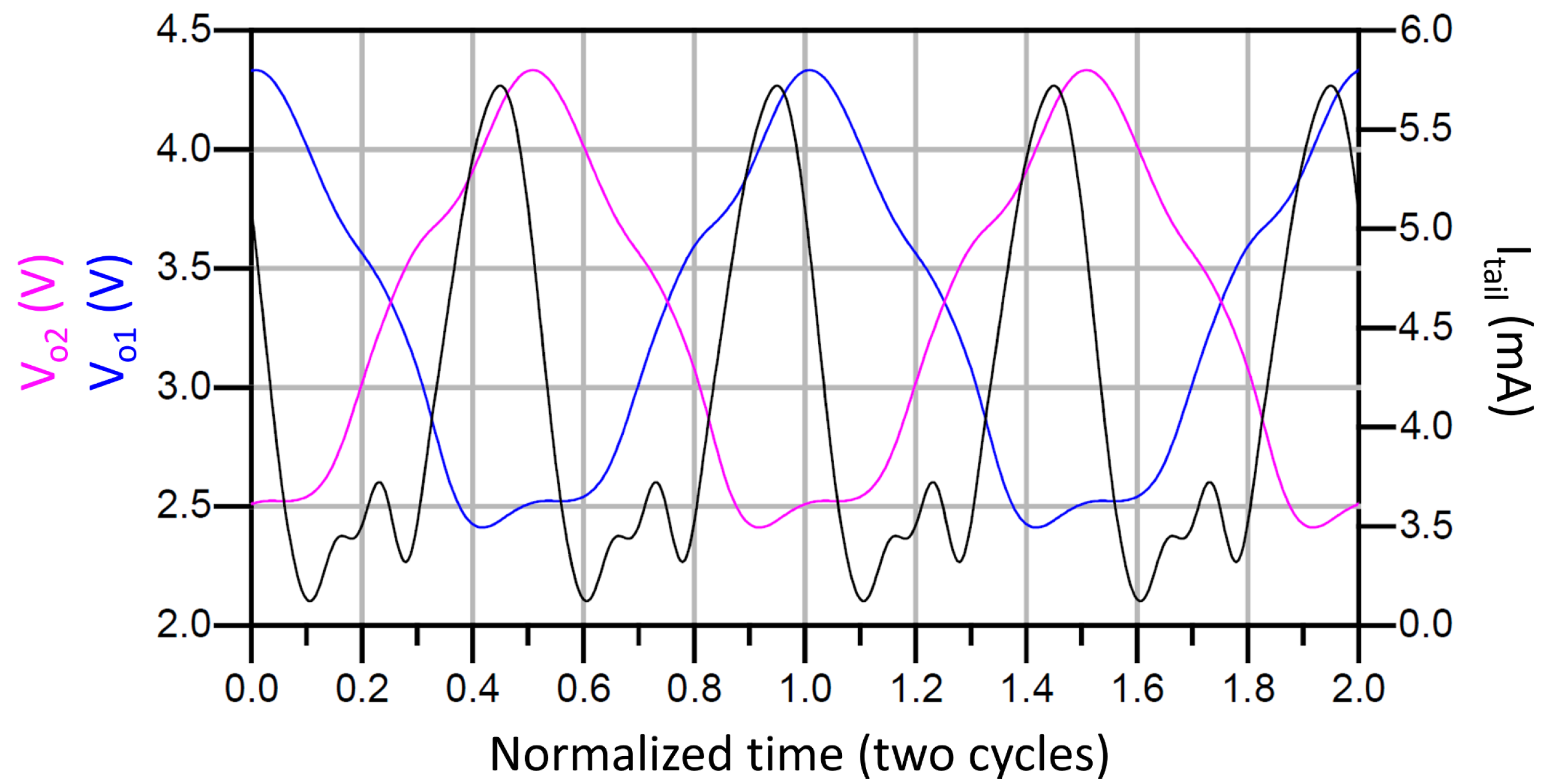

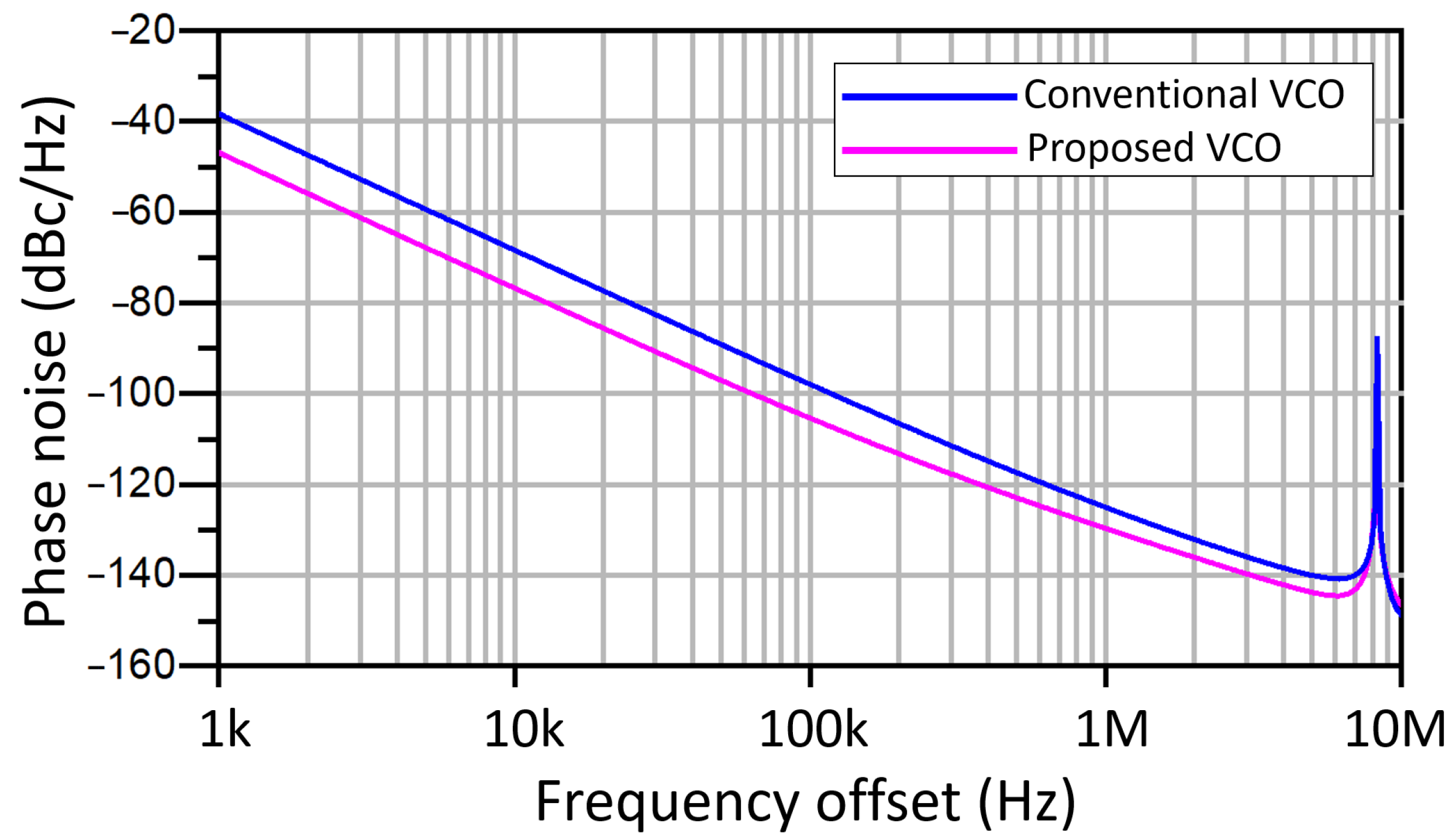

2. Current-Shaping Biasing Techniques

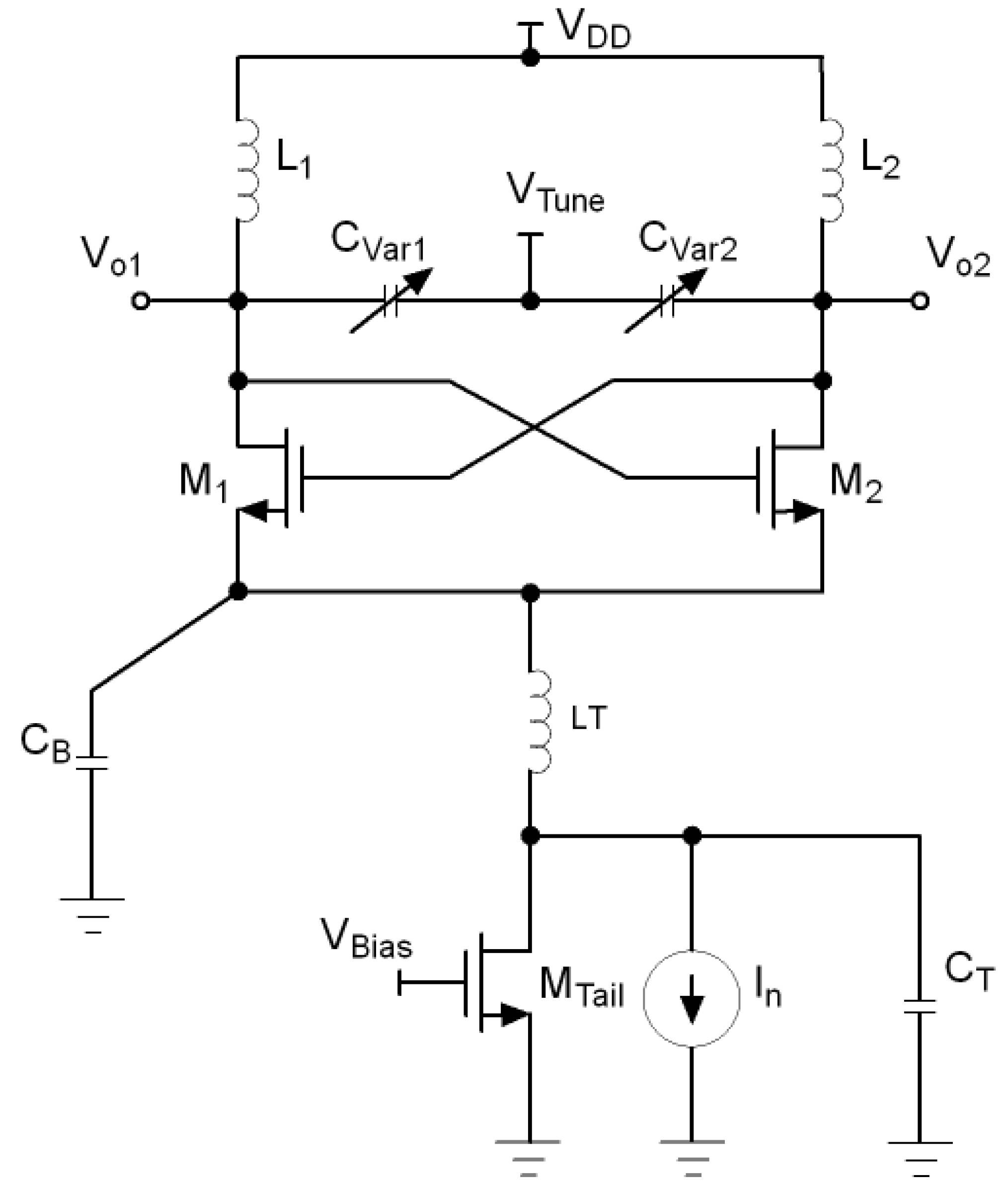

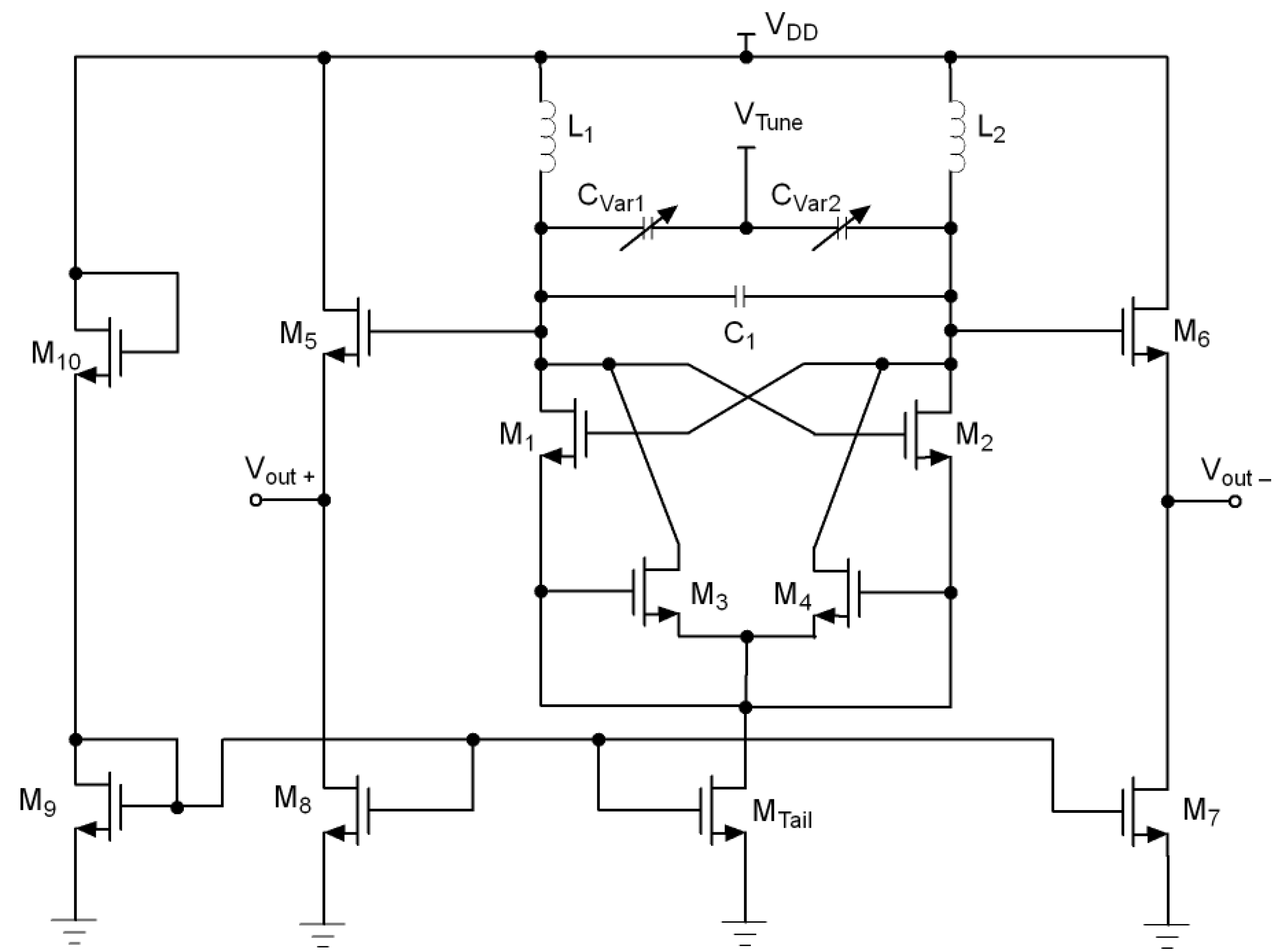

3. Proposed Topology

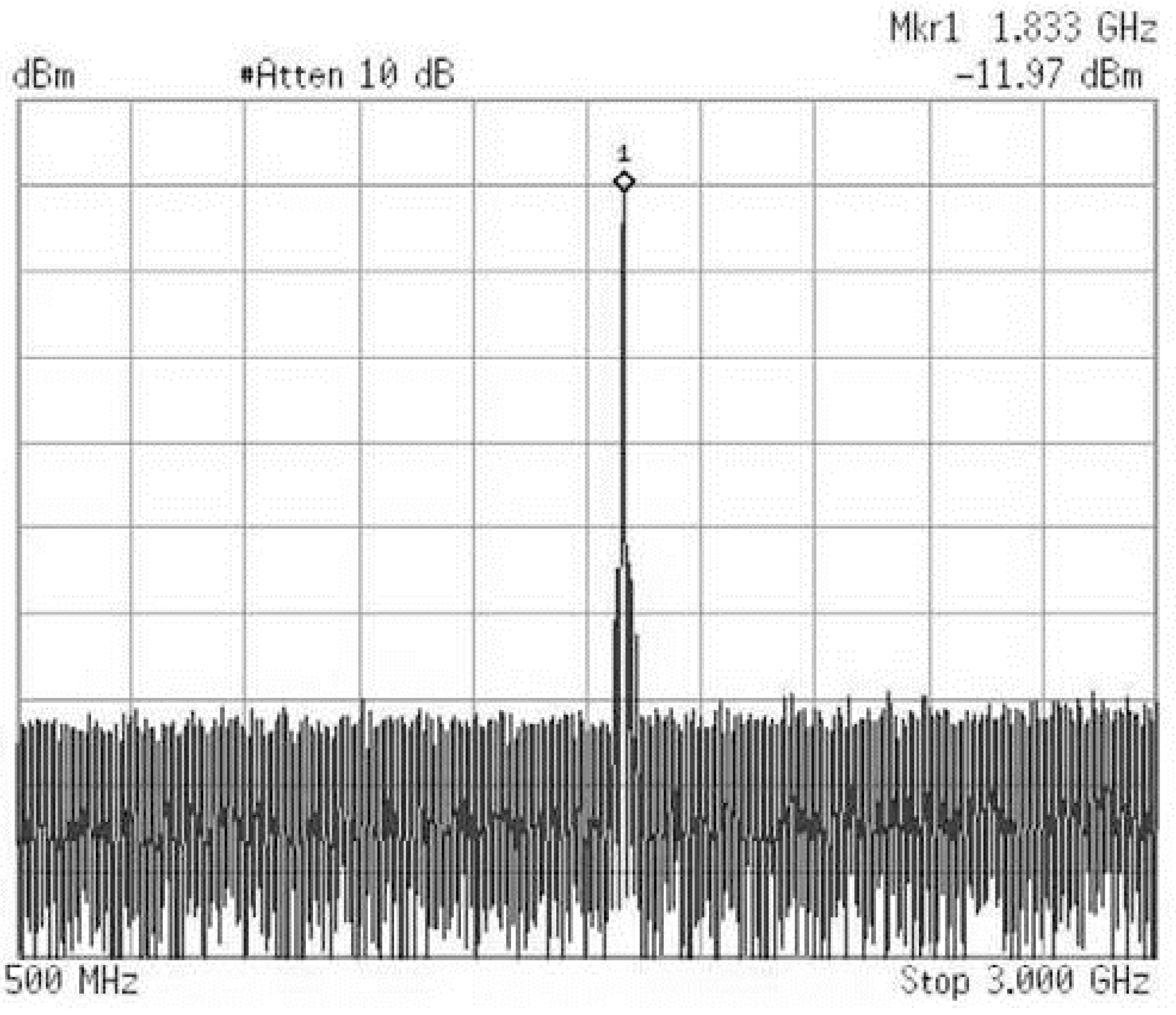

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| ACM | Advanced Compact MOSFET |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| F | Noise Factor |

| Figure of Merit | |

| LC-VCO | Inductor-Capacitor Voltage Controlled Oscillator |

| ISF | Impulse Sensitivity Function |

| MOM | Metal-Oxide-Metal |

| PLL | Phase Locked Loop |

| Q | Quality Factor |

| VCO | Voltage-Controlled Oscillator |

| WSNs | Wireless Sensor Networks |

References

- Kopta, V.; Enz, C.C. A 4-GHz Low-Power, Multi-User Approximate Zero-IF FM-UWB Transceiver for IoT. IEEE J. Solid-State Circuits 2019, 54, 2462–2474. [Google Scholar] [CrossRef]

- Wang, K.; Otis, B.; Wang, Z. A 580-μW 2.4-GHz ZigBee Receiver Front End With Transformer Coupling Technique. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 174–176. [Google Scholar] [CrossRef]

- Li, D.; Liu, D.; Kang, C.; Zou, X. A Low Power Low Phase Noise Oscillator for MICS Transceivers. Sensors 2017, 17, 140. [Google Scholar] [CrossRef]

- Selvakumar, A.; Zargham, M.; Liscidini, A. Sub-mW Current Re-Use Receiver Front-End for Wireless Sensor Network Applications. IEEE J. Solid-State Circuits 2015, 50, 2965–2974. [Google Scholar] [CrossRef]

- Wong, A.C.W. A 1V 5 mA Multimode IEEE 802.15.6/Bluetooth Low-Energy WBAN Transceiver for Biotelemetry Applications. IEEE J. Solid-State Circuits 2013, 48, 186–198. [Google Scholar] [CrossRef]

- Thabet, H.; Meillère, S.; Masmoudi, M. A low power consumption CMOS differential-ring VCO for a wireless sensor. Analog Integr. Circ. Sig. Process 2012, 73, 731–740. [Google Scholar] [CrossRef]

- Italia, A.; Ippolito, C.M.; Palmisano, G. A 1-mW 1.13–1.9 GHz CMOS LC-VCO Using Shunt-Connected Switched-Coupled Inductors. IEEE Trans. Circuits Syst. I Reg. Pap. 2012, 59, 1145–1155. [Google Scholar] [CrossRef]

- Zhang, X.; Mukhopadhyay, I.; Dokania, R.; Apsel, A.B. A 46-μW Self-Calibrated Gigahertz VCO for Low-Power Radios. IEEE Trans. Circuits Syst. II Exp. Briefs 2011, 58, 847–851. [Google Scholar] [CrossRef]

- Khemchandani, S.L.; del Pino Suarez, J.; Diaz Ortega, R.; Hernandez, A. A fully integrated single core VCO with a wide tuning range for DVB-H. Microw. Opt. Technol. Lett. 2009, 51, 1338–1343. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics, 2nd ed.; Prentice Hall Communications Engineering and Emerging Technologies Series; Prentice Hall: New York, NY, USA, 2011. [Google Scholar]

- Quintero, A.; Cardes, F.; Perez, C.; Buffa, C.; Wiesbauer, A.; Hernandez, L. A VCO-Based CMOS Readout Circuit for Capacitive MEMS Microphones. Sensors 2019, 19, 4126. [Google Scholar] [CrossRef] [Green Version]

- Elhadidy, O.; Elkholy, M.; Helmy, A.A.; Palermo, S.; Entesari, K. A CMOS Fractional-N PLL-Based Microwave Chemical Sensor With 1.5% Permittivity Accuracy. IEEE Trans. Microw. Theory Tech. 2013, 61, 3402–3416. [Google Scholar] [CrossRef]

- Laemmle, B.; Schmalz, K.; Scheytt, J.C.; Weigel, R.; Kissinger, D. A 125-GHz Permittivity Sensor With Read-Out Circuit in a 250-nm SiGe BiCMOS Technology. IEEE Trans. Microw. Theory Tech. 2013, 61, 2185–2194. [Google Scholar] [CrossRef]

- Jamal, F.I. Low-Power Miniature K-Band Sensors for Dielectric Characterization of Biomaterials. IEEE Trans. Microw. Theory Tech. 2017, 65, 1012–1023. [Google Scholar] [CrossRef]

- Tseng, S.T.; Kao, Y.H.; Peng, C.C.; Liu, J.Y.; Chu, S.C.; Hong, G.F.; Chu, T.S. A 65-nm CMOS Low-Power Impulse Radar System for Human Respiratory Feature Extraction and Diagnosis on Respiratory Diseases. IEEE Trans. Microw. Theory Tech. 2016, 64, 1029–1041. [Google Scholar] [CrossRef]

- Park, J.-H.; Yang, J.-R. Two-Tone Continuous-Wave Doppler Radar Based on Envelope Detection Method. Microw. Opt. Technol. Lett. 2020, 62, 3146–3150. [Google Scholar] [CrossRef]

- Sim, J.Y.; Park, J.-H.; Yang, J.-R. Vital-Signs Detector Based on Frequency-Shift Keying Radar. Sensors 2020, 20, 5516. [Google Scholar] [CrossRef] [PubMed]

- Kang, C.-W.; Moon, H.; Yang, J.-R. Switched-Biasing Techniques for CMOS Voltage-Controlled Oscillator. Sensors 2021, 21, 316. [Google Scholar] [CrossRef] [PubMed]

- Lesson, D.B. A simple model of feedback oscillator noise spectrum. Proc. IEEE 1966, 54, 329–330. [Google Scholar] [CrossRef] [Green Version]

- Heng, C.; Bansal, A.; Cheng, S.J. Techniques for improving CMOS VCO performance. In Proceedings of the 2009 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Singapore, 9 January–11 December 2009; pp. 182–189. [Google Scholar] [CrossRef]

- Soltanian, B.; Kinget, P.R. Tail Current-Shaping to Improve Phase Noise in LC Voltage-Controlled Oscillators. IEEE J. Solid-State Circuits 2006, 41, 1792–1802. [Google Scholar] [CrossRef]

- Mazzanti, A.; Andreani, P. Class-C Harmonic CMOS VCOs, With a General Result on Phase Noise. IEEE J. Solid-State Circuits 2008, 43, 2716–2729. [Google Scholar] [CrossRef]

- Hegazi, E.; Sjoland, H.; Abidi, A. A filtering technique to lower LC oscillator phase noise. IEEE J. Solid-State Circuits 2001, 36, 1921–1930. [Google Scholar] [CrossRef] [Green Version]

- Lin, Y.; To, K.H.; Hamel, J.S.; Huang, W.M.A. Fully integrated 5 GHz CMOS VCOs with on chip low frequency feedback circuit for 1/f induced phase noise suppression. In Proceedings of the 28th European Solid-State Circuits Conference, Florence, Italy, 24–26 September 2002; Volume 36, pp. 551–554. [Google Scholar] [CrossRef] [Green Version]

- Heng, C.; Bansal, A.; Zheng, Y. Design of 1.94-GHz CMOS Noise-Cancellation VCO. IEEE Trans. Microw. Theory Tech. 2011, 59, 368–374. [Google Scholar] [CrossRef]

- Huang, T.; Tseng, Y. A 1 V 2.2 mW 7 GHz CMOS Quadrature VCO Using Current-Reuse and Cross-Coupled Transformer-Feedback Technology. IEEE Microw. Wirel. Compon. Lett. 2008, 18, 698–700. [Google Scholar] [CrossRef]

- Boon, C.C.; Tseng, M.A.; Yeo, K.S.; Ma, J.G.; Zhang, K.L. RF CMOS low-phase-noise LC oscillator through memory reduction tail transistor. IEEE Trans. Circuits Syst. II Exp. Briefs 2004, 51, 85–90. [Google Scholar] [CrossRef]

- Jannesari, A.; Kamarei, M. Sinusoidal shaping of the ISF in LC oscillators. Int. J. Circuit Theory Appl. 2008, 36, 757–768. [Google Scholar] [CrossRef]

- Hsieh, J.; Lin, K. A 0.7-mW LC Voltage-Controlled Oscillator Leveraging Switched Biasing Technique for Low Phase Noise. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1307–1310. [Google Scholar] [CrossRef]

- Jafari, B.; Sheikhaei, S. Low phase noise LC-VCO with sinusoidal tail current-shaping using cascode current source. AEU-Int. J. Electron. Commun. 2018, 83, 1434–8411. [Google Scholar] [CrossRef]

- Shen, I.; Huang, T.; Jou, C.F. A Low Phase Noise Quadrature VCO Using Symmetrical Tail Current-Shaping Technique. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 399–401. [Google Scholar] [CrossRef]

- Sadr, M.N.H.R.; Dousti, M.; Hajghassem, H. Phase noise and transconductance improvement in monolithic differential LC-VCOs. Int. J. Electron. 2011, 98, 1333–1345. [Google Scholar] [CrossRef]

- Kinget, P. Integrated GHz Voltage Controlled Oscillators; Springer US: Boston, MA, USA, 1999; pp. 353–381. ISBN 978-1-4419-5101-4. [Google Scholar]

- González Ramírez, D.; Lalchand Khemchandani, S.; del Pino, J.; Mayor-Duarte, D.; San Miguel-Montesdeoca, M.; Mateos-Angulo, S. Single event transients mitigation techniques for CMOS integrated VCOs. Microelectron. J. 2018, 73, 37–42. [Google Scholar] [CrossRef]

- Shasidharan, P.; Ramiah, H.; Rajendran, J. A 2.2 to 2.9 GHz Complementary Class-C VCO with PMOS Tail-Current Source. Feedback Achieving—120 dBc/Hz Phase Noise at 1 MHz Offset. IEEE Access 2019, 7, 91325–91336. [Google Scholar] [CrossRef]

- Chen, N.; Diao, S.; Huang, L.; Lin, F. Reduction of 1/f3 Phase Noise in LC Oscillator with Improved Self-Switched Biasing. Analog Integr. Circuits Signal Process 2015, 84, 19–27. [Google Scholar] [CrossRef]

- Mostajeran, A.; Bakhtiar, M.S.; Afshari, E. A 2.4 GHz VCO with FOM of 190 dBc/Hz at 10 kHz-to −2 MHz Offset Frequencies in 0.13 μm CMOS Using an ISF Manipulation Technique. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Narayanan, A.T.; Okada, K. A Pulse-Tail-Feedback LC-VCO with 700 Hz Flicker Noise Corner and −195 dBc FoM. IEICE Trans. Electron. 2019, E102, 595–606. [Google Scholar] [CrossRef] [Green Version]

- Min, B.-H.; Hyun, S.-B.; Yu, H.-K. Low Voltage CMOS LC-VCO with Switched Self-Biasing. ETRI J. 2009, 31, 755–764. [Google Scholar] [CrossRef]

- Lee, H.S.; Kang, D.M.; Cho, S.J.; Byeon, C.W.; Park, C.S. Low-Power, Low-Phase-Noise Gm-Boosted 10-GHz VCO with Center-Tap Transformer and Stacked Transistor. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1710–1714. [Google Scholar] [CrossRef]

- Musa, A.; Murakami, R.; Sato, T.; Chaivipas, W.; Okada, K.; Matsuzawa, A. A Low Phase Noise Quadrature Injection Locked Frequency Synthesizer for MM-Wave Applications. IEEE J. Solid-State Circuits 2011, 46, 2635–2649. [Google Scholar] [CrossRef]

| Component | Value |

|---|---|

| M1 & M2 | Wfinger = 1 m, L = 200 nm, Multiplicity = 20 |

| M3 & M4 | Wfinger = 8 m, L = 360 nm, Multiplicity = 30 |

| M5 & M6 | Wfinger = 530 nm, L = 100 nm, Multiplicity = 8 |

| M7 & M8 | Wfinger = 530 nm, L = 100 nm, Multiplicity = 8 |

| M9 | Wfinger = 600 nm, L = 250 nm, Multiplicity = 10 |

| M10 | Wfinger = 500 nm, L = 100 nm, Multiplicity = 14 |

| CVAR1 & CVAR1 | CMAX = 3.824 pF |

| L1 & L2 | L = 1.15 nH, Q = 14@2.2 GHz, 1.5 turns |

| C1 | C = 1.364 pF |

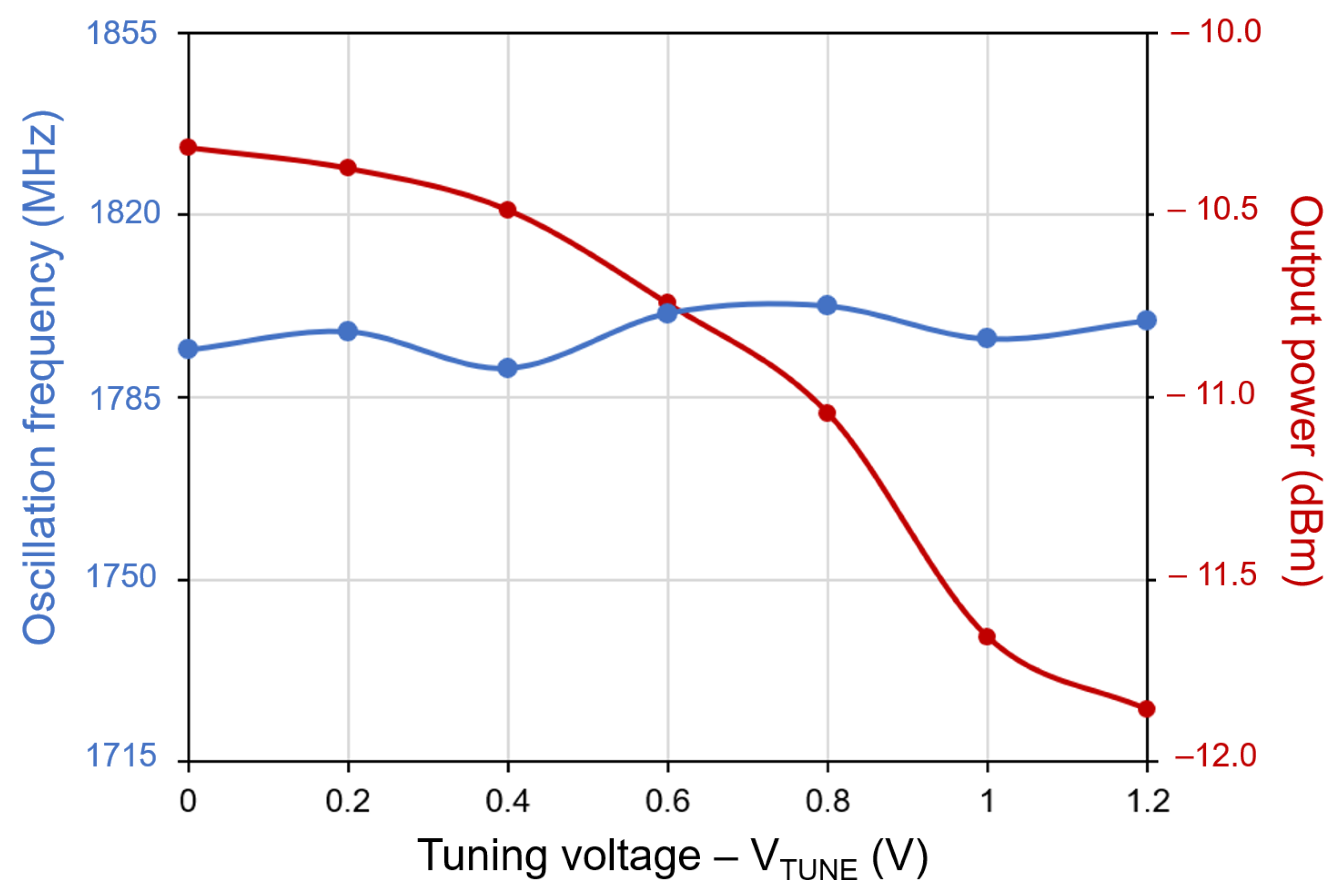

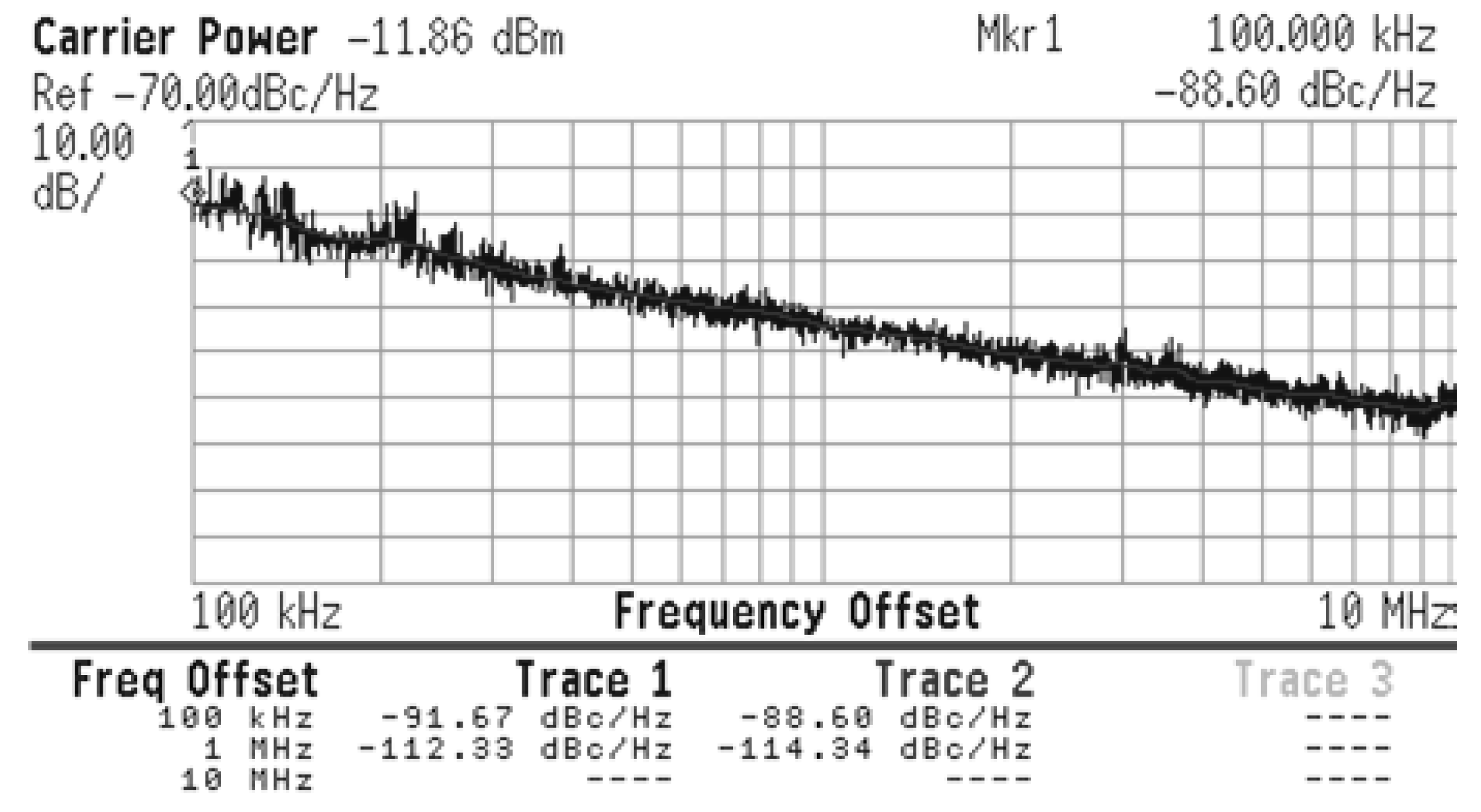

| Frequency Offset | Simulated Phase Noise | Measured Phase Noise |

|---|---|---|

| 100 kHz | −85 dBc/Hz | −86.6 dBc/Hz |

| 1 MHz | −111.5 dBc/Hz | −112.2 dBc/Hz |

| 5 MHz | −130 dBc/Hz | −125.5 dBc/Hz |

| Ref. | Year | Bias Scheme | Process | VCO | Supply | Freq. | Tuning | PN@1 MHz | Power | Area | FoM@1 MHz |

|---|---|---|---|---|---|---|---|---|---|---|---|

| (nm) | Type | (V) | (GHz) | Range (%) | (dBc/Hz) | (mW) | (mm) | (dBc/Hz) | |||

| [35] | 2019 | Self-biasing w. fixed DC | 180 | CMOS-LC | 1.2 | 2.45 | 28.6 | −120 | 1.73 | 0.938 | −185 |

| [29] | 2019 | Self-biasing w. fixed DC | 180 | CMOS-LC | 0.8 | 1.4 | 18 | −123 | 0.7 | 2.706 | −187 |

| [36] | 2015 | Self-biasing w. fixed DC | 180 | CMOS-LC | 1.2 | 2.55 | 9.2 | −123 | 3.2 | 0.332 * | −186 |

| [37] | 2015 | Self-biasing w. fixed DC | 130 | CMOS-LC | 1.4 | 2.4 | 1.7 | −128 | 4.2 | 0.092 * | −190 |

| [38] | 2019 | Self-biasing w. adaptative DC | 180 | CMOS-LC | 1.2 | 4.55 | 4.3 | −123 | 1.35 | 0.979 | −195 |

| [39] | 2009 | Self-biasing w. adaptative DC | 130 | NMOS-LC | 0.6 | 4.85 | 10.2 | −117 | 3.9 | 0.723 | −185 |

| [40] | 2020 | Self-biasing w. fixed DC | 65 | NMOS-LC | 0.45 | 10.4 | 13.6 | −115 | 2.7 | 0.660 | −191 |

| [41] | 2011 | Self-biasing w. fixed DC | 65 | NMOS-LC | 1.2 | 20 | 17 | −107 | 19.2 | 0.800 | −180 |

| This work | 2021 | Feedback injection curr. | 90 | NMOS-LC | 1.2 | 1.77 | 6.2 | −112 | 3.96 | 0.638 | −171 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

del Pino Suárez, F.J.; Khemchandani, S.L. A New Current-Shaping Technique Based on a Feedback Injection Mechanism to Reduce VCO Phase Noise. Sensors 2021, 21, 6583. https://doi.org/10.3390/s21196583

del Pino Suárez FJ, Khemchandani SL. A New Current-Shaping Technique Based on a Feedback Injection Mechanism to Reduce VCO Phase Noise. Sensors. 2021; 21(19):6583. https://doi.org/10.3390/s21196583

Chicago/Turabian Styledel Pino Suárez, Francisco Javier, and Sunil Lalchand Khemchandani. 2021. "A New Current-Shaping Technique Based on a Feedback Injection Mechanism to Reduce VCO Phase Noise" Sensors 21, no. 19: 6583. https://doi.org/10.3390/s21196583

APA Styledel Pino Suárez, F. J., & Khemchandani, S. L. (2021). A New Current-Shaping Technique Based on a Feedback Injection Mechanism to Reduce VCO Phase Noise. Sensors, 21(19), 6583. https://doi.org/10.3390/s21196583