Mitigation of Single-Event Effects in SiGe-HBT Current-Mode Logic Circuits

Abstract

1. Introduction

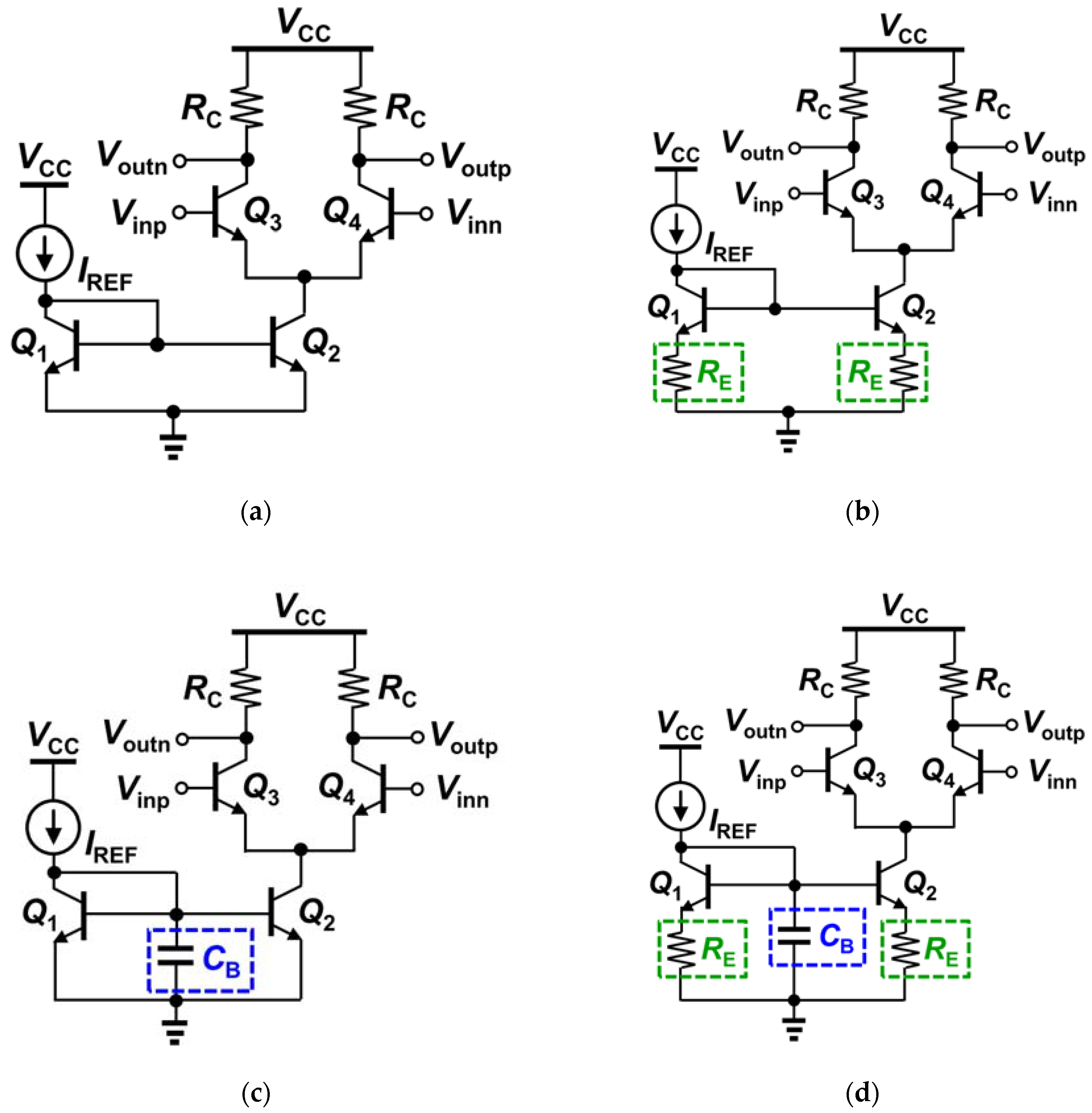

2. Current-Mode Logic Circuits

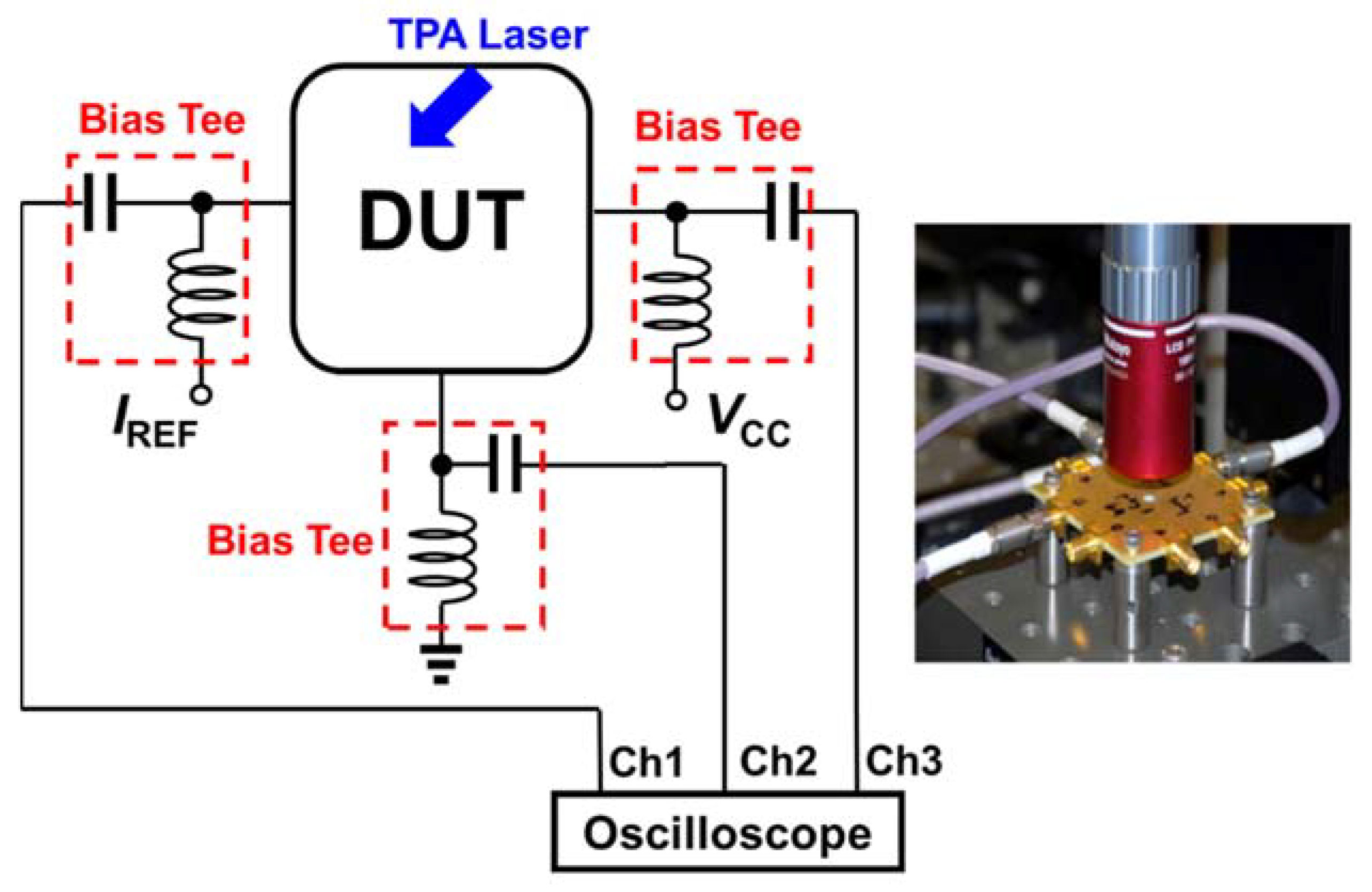

3. Measurement Setup

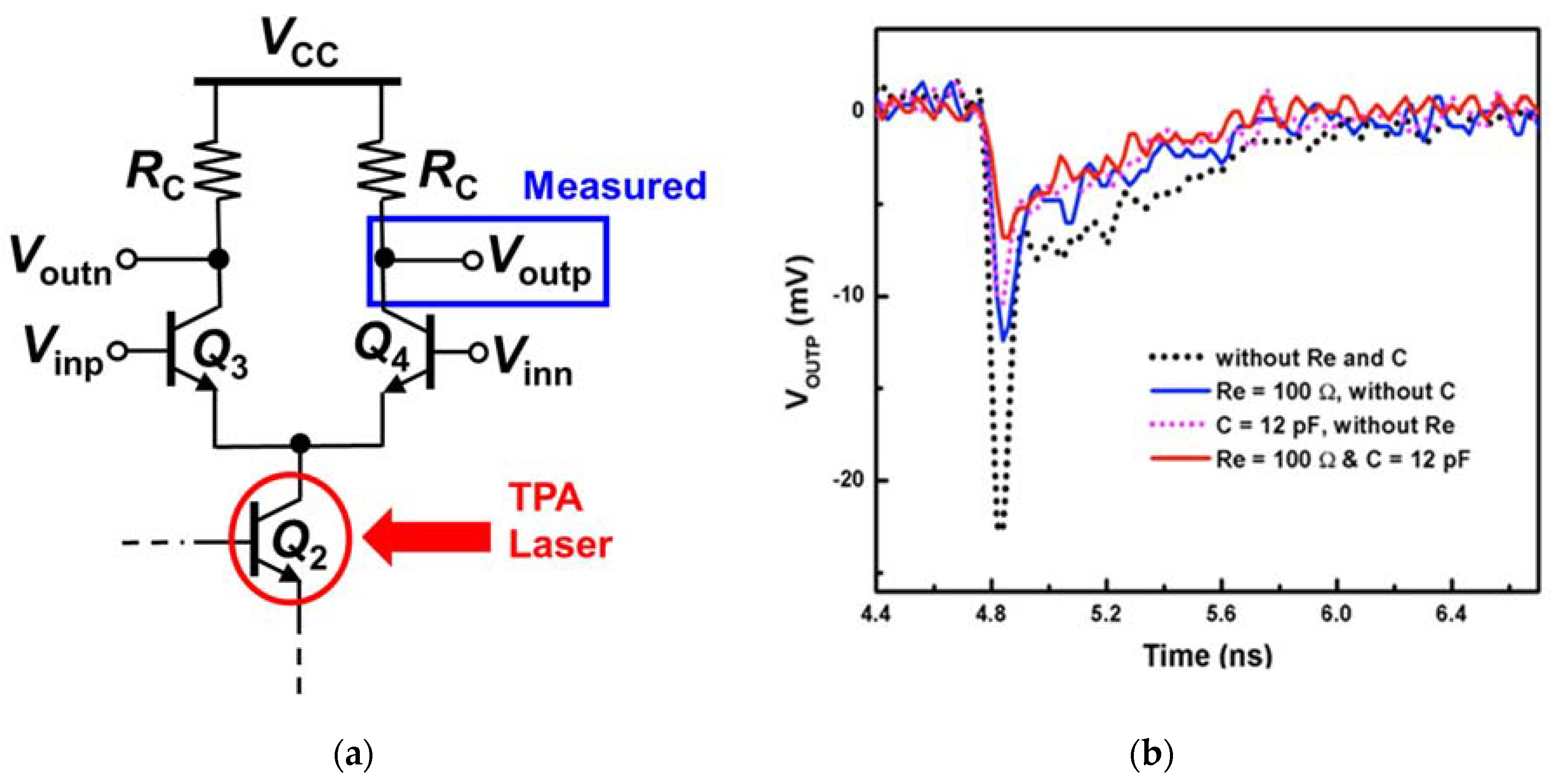

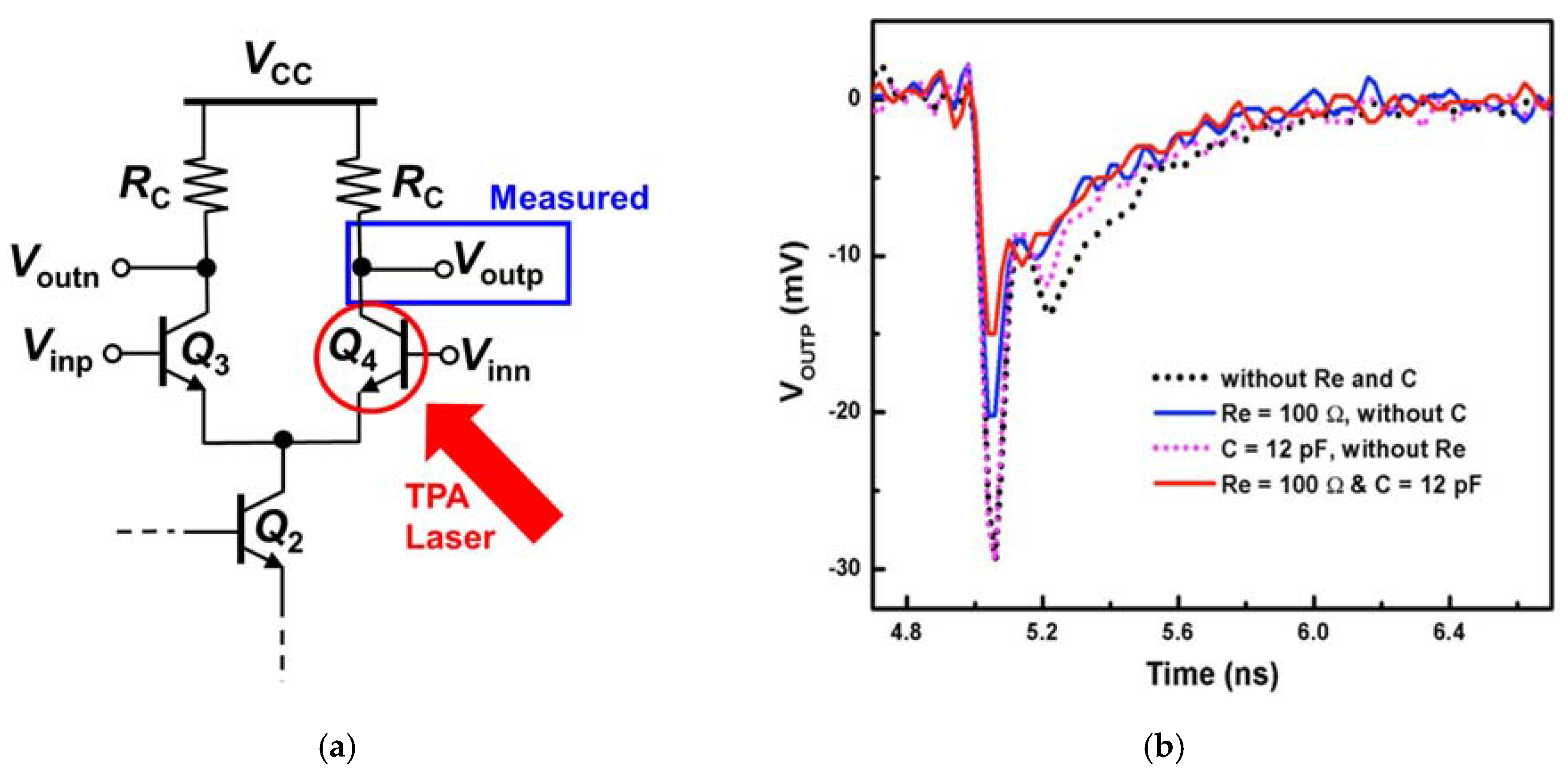

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Cressler, J.D. On the potential of SiGe HBTs for extreme environment electronics. Proc. IEEE 2005, 93, 1559–1582. [Google Scholar] [CrossRef]

- Sutton, A.K.; Gnana Prakash, A.P.; Jun, B.; Zhao, E.; Bellini, M.; Pellish, J.; Diestelhorst, R.M.; Carts, M.A.; Phan, A.; Ladbury, R.; et al. An investigation of dose rate and source dependent effects in 200 GHz SiGe HBTs. IEEE Trans. Nucl. Sci. 2006, 53, 3166–3174. [Google Scholar] [CrossRef]

- Cressler, J.D.; Hamilton, M.C.; Krithivasan, R.; Ainspan, H.; Groves, R.; Niu, G.; Zhang, S.; Jin, Z.; Marshall, C.J.; Marshall, P.W.; et al. Proton radiation response of SiGe HBT analog and RF circuits and passives. IEEE Trans. Nucl. Sci. 2001, 48, 2238–2243. [Google Scholar] [CrossRef]

- Najafizadeh, L.; Bellini, M.; Prakash, A.P.G.; Espinel, G.A.; Cressler, J.D.; Marshall, P.W.; Marshall, C.J. Proton tolerance of SiGe precision voltage references for extreme temperature range electronics. IEEE Trans. Nucl. Sci. 2006, 53, 3210–3216. [Google Scholar] [CrossRef]

- England, T.D.; Diestelhorst, R.M.; Kenyon, E.W.; Cressler, J.D.; Ramachandran, V.; Alles, M.; Reed, R.; Berger, R.; Garbos, R.; Blalock, B.; et al. A new approach to designing electronic systems for operation in extreme environments: Part II—The SiGe remote electronics unit. IEEE Aerosp. Electron. Syst. Mag. 2012, 27, 29–41. [Google Scholar] [CrossRef]

- Howard, D.C.; Saha, P.K.; Shankar, S.; Diestelhorst, R.M.; England, T.D.; Lourenco, N.E.; Kenyon, E.; Cressler, J.D. An 8–16 GHz SiGe low noise amplifier with performance tuning capability for mitigation of radiation-induced performance loss. IEEE Trans. Nucl. Sci. 2012, 59, 2837–2846. [Google Scholar] [CrossRef]

- Lourenco, N.E.; Schmid, R.L.; Moen, K.A.; Phillips, S.D.; England, T.D.; Cressler, J.D.; Pekarik, J.; Adkisson, J.; Camillo-Castillo, R.; Cheng, P.; et al. Total dose and transient response of SiGe HBTs from a new 4th-generation, 90 nm SiGe BiCMOS technology. In Proceedings of the 2012 IEEE Radiation Effects Data Workshop, Tucson, AZ, USA, 16–20 July 2012; pp. 1–5. [Google Scholar] [CrossRef]

- Cressler, J.D.; Mantooth, H.A. Extreme Environment Electronics; CRC Press: Boca Raton, FL, USA, 2012. [Google Scholar]

- Zhang, Z.; Chen, L.; Djahanshahi, H. A SEE Insensitive CML Voltage Controlled Oscillator in 65 nm CMOS. In Proceedings of the 2018 IEEE Canadian Conference on Electrical & Computer Engineering (CCECE), Quebec City, QC, Canada, 13–16 May 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Díez-Acereda, V.; L Khemchandani, S.; del Pino, J.; Mateos-Angulo, S. RHBD Techniques to Mitigate SEU and SET in CMOS Frequency Synthesizers. Electronics 2019, 8, 690. [Google Scholar] [CrossRef]

- Jung, S.; Lourenco, N.E.; Song, I.; Oakley, M.A.; England, T.D.; Arora, R.; Cardoso, A.S.; Roche, N.J.-H.; Khachatrian, A.; McMorrow, D.; et al. An investigation of single-event transients in C-SiGe HBT on SOI current mirror circuits. IEEE Trans. Nucl. Sci. 2014, 61, 3193–3200. [Google Scholar] [CrossRef]

- Jung, S.; Song, I.; Fleetwood, Z.E.; Raghunathan, U.; Lourenco, N.E.; Oakley, M.A.; Wier, B.R.; Roche, N.J.-H.; Khachatrian, A.; McMorrow, D.; et al. The role of negative feedback effects on single-event transients in SiGe HBT analog circuits. IEEE Trans. Nucl. Sci. 2015, 62, 2599–2605. [Google Scholar] [CrossRef]

- Loveless, T.D.; Massengill, L.W.; Holman, W.T.; Bhuva, B.L. Modeling and mitigating single-event transients in voltage-controlled oscillators. IEEE Trans. Nucl, Sci. 2007, 54, 2561–2567. [Google Scholar] [CrossRef]

- Kruckmeyer, K.; Rennie, R.L.; Ramachandran, V. Use of code error and beat frequency test method to identify single event upset sensitive circuits in a 1 GHz analog to digital converter. IEEE Trans. Nucl. Sci. 2008, 55, 2013–2018. [Google Scholar] [CrossRef]

- Sun, Y.; Fu, J.; Wang, Y.; Zhou, W.; Liu, Z.; Li, X.; Shi, Y. Experimental study of bias dependence of pulsed laser-induced single-event transient in SiGe HBT. Microelectron. Reliab. 2016, 65, 41–46. [Google Scholar] [CrossRef]

- Zhang, T.; Wei, X.; Niu, G.; Cressler, J.D.; Marshall, P.W.; Reed, R.A. A mechanism versus SEU impact analysis of collector charge collection in SiGe HBT current mode logic. IEEE Trans. Nucl. Sci. 2009, 56, 3071–3077. [Google Scholar] [CrossRef]

- Marshall, P.W.; Carts, M.A.; Campbell, A.; McMorrow, D.; Buchner, S.; Stewart, R.; Randall, B.; Gilbert, B.; Reed, R.A. Single event effects in circuit-hardened SiGe HBT logic at gigabit per second data rates. IEEE Trans. Nucl. Sci. 2000, 47, 2669–2674. [Google Scholar] [CrossRef]

- Pellish, J.A.; Reed, R.A.; Schrimpf, R.D.; Alles, M.L.; Varadharajaperumal, M.; Niu, G.; Sutton, A.K.; Diestelhorst, R.M.; Espinel, G.; Krithivasan, R.; et al. Substrate engineering concepts to mitigate charge collection in deep trench isolation technologies. IEEE Trans. Nucl. Sci. 2006, 53, 3298–3305. [Google Scholar] [CrossRef]

- Armstrong, S.E.; Blaine, R.W.; Holman, W.T.; Massengill, L.W. Single-event vulnerability of mixed-signal circuit interfaces. In Proceedings of the 2011 12th European Conference on Radiation and its Effects on Components and Systems, Sevilla, Spain, 19–23 September 2011; pp. 485–488. [Google Scholar] [CrossRef]

- Lourenco, N.E.; Ildefonso, A.; Tzintzarov, G.N.; Fleetwood, Z.E.; Motoki, K.; Paki, P.; Kaynak, M.; Cressler, J.D. Single-event upset mitigation in a complementary SiGe HBT BiCMOS technology. IEEE Trans. Nucl. Sci. 2018, 65, 231–238. [Google Scholar] [CrossRef]

- Sutton, A.K.; Bellini, M.; Cressler, J.D.; Pellish, J.A.; Reed, R.A.; Marshall, P.W.; Niu, G.; Vizkelethy, G.; Turowski, M.; Raman, A. An evaluation of transistor-layout RHBD techniques for SEE mitigation in SiGe HBTs. IEEE Trans. Nucl. Sci. 2007, 54, 2044–2052. [Google Scholar] [CrossRef]

- Varadharajaperumal, M.; Niu, G.; Wei, X.; Zhang, T.; Cressler, J.D.; Reed, R.A.; Marshall, P.W. 3-D Simulation of SEU hardening of SiGe HBTs using shared dummy collector. IEEE Trans. Nucl. Sci. 2007, 54, 2330–2337. [Google Scholar] [CrossRef]

- Krithivasan, R.; Marshall, P.W.; Nayeem, M.; Sutton, A.K.; Kuo, W.-M.; Haugerud, B.M.; Najafizadeh, L.; Cressler, J.D.; Carts, M.A.; Marshall, C.J.; et al. Application of RHBD techniques to SEU hardening of third-generation SiGe HBT logic circuits. IEEE Trans. Nucl. Sci. 2006, 53, 3400–3407. [Google Scholar] [CrossRef]

- Phillips, S.D.; Moen, K.A.; Lourenco, N.E.; Cressler, J.D. Single-event response of the SiGe HBT operating in inverse-mode. IEEE Trans. Nucl. Sci. 2012, 59, 2682–2690. [Google Scholar] [CrossRef]

- Thrivikraman, T.K.; Wilcox, E.; Phillips, S.D.; Cressler, J.D.; Marshall, C.; Vizkelethy, G.; Dodd, P.; Marshall, P. Design of digital circuits using inverse-mode cascode SiGe HBTs for single event upset mitigation. IEEE Trans. Nucl. Sci. 2010, 57, 3582–3587. [Google Scholar] [CrossRef]

- Phillips, S.D.; Thrivikraman, T.; Appaswamy, A.; Sutton, A.K.; Cressler, J.D.; Vizkelethy, G.; Dodd, P.; Reed, R.A. A Novel Device Architecture for SEU Mitigation: The Inverse-mode cascode SiGe HBT. IEEE Trans. Nucl. Sci. 2009, 56, 3393–3401. [Google Scholar] [CrossRef]

- Messenger, G.C. Collection of charge on junction nodes from ion tracks. IEEE Trans. Nucl. Sci. 1982, 29, 2024–2031. [Google Scholar] [CrossRef]

- Black, D.A.; Robinson, W.H.; Wilcox, I.Z.; Limbrick, D.B.; Black, J.D. Modeling of single event transients with dual double-exponential current sources: Implications for logic cell characterization. IEEE Trans. Nucl. Sci. 2015, 62, 1540–1549. [Google Scholar] [CrossRef]

- Song, I.; Jung, S.; Lourenco, N.E.; Raghunathan, U.S.; Fleetwood, Z.E.; Zeinolabedinzadeh, S.; Gebremariam, T.B.; Inanlou, F.; Roche, N.J.-H.; Khachatrian, A.; et al. Design of radiation-hardened RF low-noise amplifiers using inverse-mode SiGe HBTs. IEEE Trans. Nucl. Sci. 2014, 61, 3218–3225. [Google Scholar] [CrossRef]

- Ildefonso, A.; Song, I.; Tzintzarov, G.N.; Fleetwood, Z.E.; Lourenco, N.E.; Wachter, M.T.; Cressler, J.D. Modeling single-event transient propagation in a SiGe BiCMOS direct-conversion receiver. IEEE Trans. Nucl. Sci. 2017, 64, 2079–2088. [Google Scholar] [CrossRef]

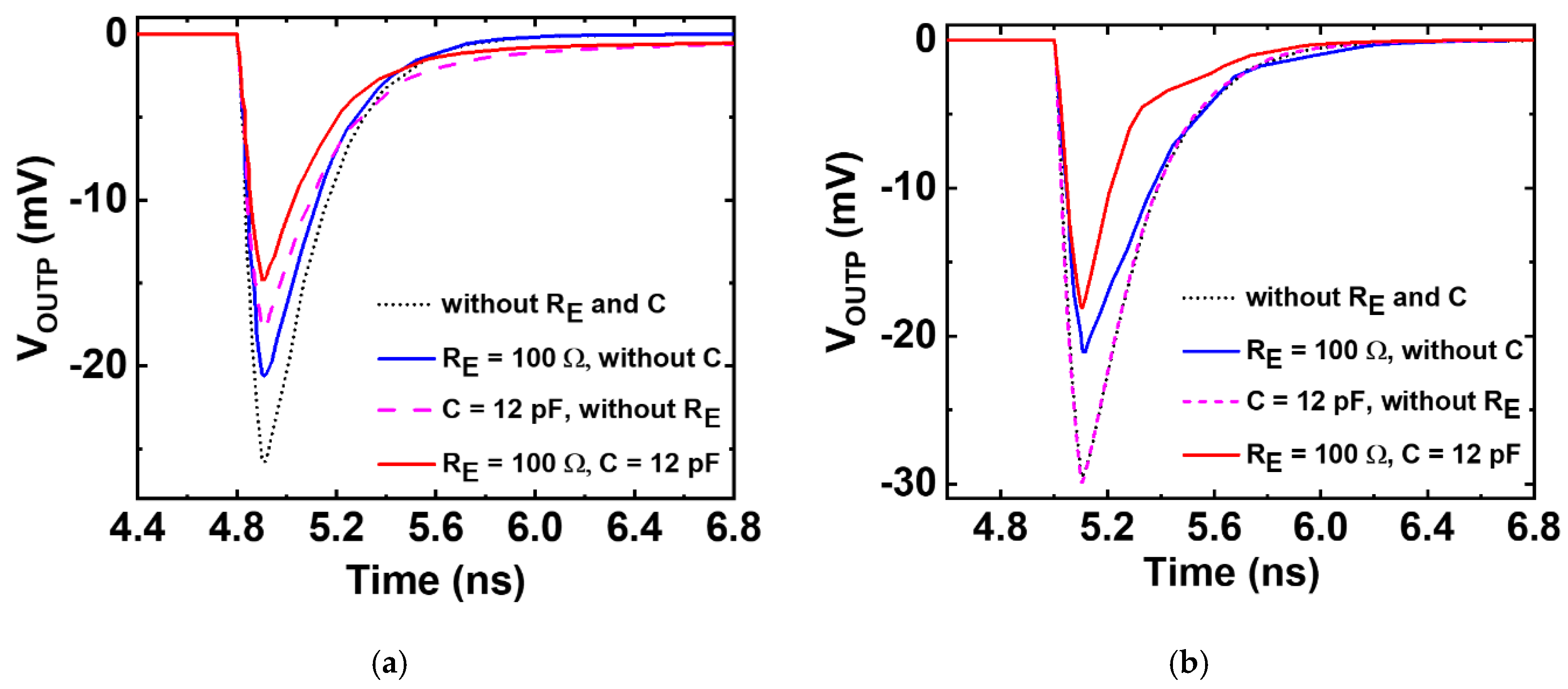

| Normalized 3-dB Bandwidth | Normalized Chip Area * | SET Generation | Normalized Transient Peak | |

|---|---|---|---|---|

| Control No RE and C | 1 x | 1 | CM + (Q2) | 1 |

| Diff-pair (Q4) | 1 | |||

| RE = 100 Ω, C = 0 pF | 1.02 | 2.4 | CM (Q2) | 0.50 |

| Diff-pair (Q4) | 0.65 | |||

| RE = 0 Ω, C = 12 pF | 1 | 13.5 | CM (Q2) | 0.50 |

| Diff-pair (Q4) | 1 | |||

| RE = 100 Ω, C = 12 pF | 1.02 | 14.8 | CM (Q2) | 0.30 |

| Diff-pair (Q4) | 0.50 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sarker, M.A.R.; Jung, S.; Ildefonso, A.; Khachatrian, A.; Buchner, S.P.; McMorrow, D.; Paki, P.; Cressler, J.D.; Song, I. Mitigation of Single-Event Effects in SiGe-HBT Current-Mode Logic Circuits. Sensors 2020, 20, 2581. https://doi.org/10.3390/s20092581

Sarker MAR, Jung S, Ildefonso A, Khachatrian A, Buchner SP, McMorrow D, Paki P, Cressler JD, Song I. Mitigation of Single-Event Effects in SiGe-HBT Current-Mode Logic Circuits. Sensors. 2020; 20(9):2581. https://doi.org/10.3390/s20092581

Chicago/Turabian StyleSarker, Md Arifur R., Seungwoo Jung, Adrian Ildefonso, Ani Khachatrian, Stephen P. Buchner, Dale McMorrow, Pauline Paki, John D. Cressler, and Ickhyun Song. 2020. "Mitigation of Single-Event Effects in SiGe-HBT Current-Mode Logic Circuits" Sensors 20, no. 9: 2581. https://doi.org/10.3390/s20092581

APA StyleSarker, M. A. R., Jung, S., Ildefonso, A., Khachatrian, A., Buchner, S. P., McMorrow, D., Paki, P., Cressler, J. D., & Song, I. (2020). Mitigation of Single-Event Effects in SiGe-HBT Current-Mode Logic Circuits. Sensors, 20(9), 2581. https://doi.org/10.3390/s20092581